### Advance Information

## 1M x 1 CMOS Dynamic RAM Page Mode

### ELECTRICALLY TESTED PER: MPG511000A

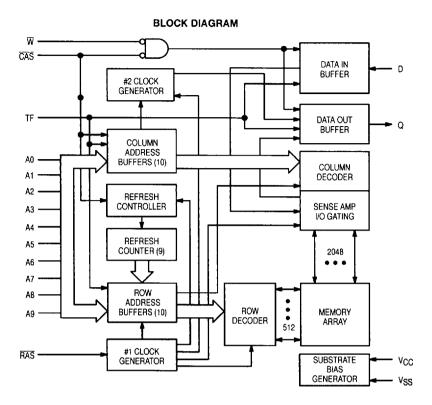

The 511000A is a 1.0μ CMOS high-speed, dynamic random access memory. It is organized as 1,048,576 one-bit words and fabricated with CMOS silicon-gate process technology. Advanced circuit design and fine line processing provide high performance, improved reliability, and low cost.

The 511000A requires only 10 address lines; row and column address inputs are multiplexed. The 511000A is available in a 300 mil, 18 lead ceramic DIL and in a 350 x 675 mil, 20/26 lead surface-mount LCC package.

- · Three-State Data Output

- Common I/O with Early Write

- Fast Page Mode

- Test Mode

- TTL-Compatible Inputs and Output

- RAS Only Refresh

- CAS Before RAS Refresh

- · Hidden Refresh

- 512 Cycle Refresh: 511000A = 8 ms

- Unlatched Data Out at Cycle End Allows Two Dimensional Chip Selection

Fast Access Time (t<sub>RAC</sub>):511000A-8 = 80 ns (Max)

511000A-9 = 90 ns (Max) 511000A-11 = 110 ns (Max)

511000A-12 = 120 ns (Max)

Low Active Power Dissipation: 511000A-8 = 495 mW (Max)

511000A-9 = 440 mW (Max) 511000A-11 = 385 mW (Max) 511000A-12 = 330 mW (Max)

Low Standby Power Dissipation: 511000A = 11 mW (Max, TTL Levels)

511000A = 11 mW (Max, CMOS Levels)

511000A

# Commercial Plus and Mil/Aero Applications

#### AVAILABLE AS

1) JAN: N/A

2) SMD: N/A

3) 883: 511000A-XX/BXAJC X = CASE OUTLINE AS FOLLOWS:

PACKAGE: DIL: V

LCC: U

XX = Speed in ns (8, 9, 11, 12)

The letter "M" appears after the speed on LCC.

| F | PIN NAMES                                                                                                                                                           |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D | Address Inputs Data Input Data Output Data Output Read/Write Enable Row Address Strobe Column Address Strobe Power (+5 V) Ground Test Function Enable No Connection |

### ABSOLUTE MAXIMUM RATINGS

| Rating                                         | Symbol                             | Value          | Unit |  |

|------------------------------------------------|------------------------------------|----------------|------|--|

| Power Supply Voltage                           | Vcc                                | - 1.0 to +7.0  | V    |  |

| Voltage Relative to VSS for Any Pin Except VCC | V <sub>in</sub> , V <sub>out</sub> | - 1.0 to +7.0  | ٧    |  |

| Test Function Input Voltage                    | V <sub>in(TF)</sub>                | - 1.0 to +10.5 | V    |  |

| Data Out Current                               | l <sub>out</sub>                   | 50             | mA   |  |

| Power Dissipation                              | PD                                 | 1.0            | W    |  |

| Operating Temperature Range                    | TA                                 | -55 to +125    | °C   |  |

| Storage Temperature Range                      | T <sub>sta</sub>                   | -65 to +150    | °C   |  |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit

This document contains information on a new product. Specifications and information herein are subject to change without notice.

MOTOROLA SC {MEMORY/ASI LSE D

|          | PIN ASSIGNMENTS       |                         |        |                      |     |    |    |        |                |                       |                         |  |                |

|----------|-----------------------|-------------------------|--------|----------------------|-----|----|----|--------|----------------|-----------------------|-------------------------|--|----------------|

| Function | Case<br>680-06<br>DIL | Case<br>756E-01<br>LCCC |        | Burn-In<br>Condition |     |    |    | -      |                | Case<br>680-06<br>DIL | Case<br>756E-01<br>LCCC |  | n-In<br>dition |

|          |                       |                         | Static | Dynamic              |     |    |    | Static | Dynamic        |                       |                         |  |                |

| D        | 1                     | 1                       | High   | A21                  | A4  | 10 | 14 | Low    | 1/2 A3         |                       |                         |  |                |

| W        | 2                     | 2                       | High   | Ā20                  | A5  | 11 | 15 | Low    | 1/2 A4         |                       |                         |  |                |

| RAS      | 3                     | 3                       | High   | 1.6µs<br>4µs         | A6  | 12 | 16 | Low    | 1/2 A5         |                       |                         |  |                |

| TF       | 4                     | 4                       | Gnd    | Gnd                  | A7  | 13 | 17 | Low    | 1/2 A6         |                       |                         |  |                |

| A0       | 5                     | 9                       | Low    | 250kHz               | A8  | 14 | 22 | Low    | 1/2 A7         |                       |                         |  |                |

| A1       | 6                     | 10                      | Low    | 1/2 A0               | A9  | 15 | 23 | Low    | 1/2 A8         |                       |                         |  |                |

| A2       | 7                     | 11                      | Low    | 1/2 A1               | CAS | 16 | 24 | High   | 0.8µs<br>1.2µs |                       |                         |  |                |

| А3       | 8                     | 12                      | Low    | 1/2 A2               | Q   | 17 | 25 | TP-VCC | TP-VCC         |                       |                         |  |                |

| Vcc      | 9                     | 13                      | Vcc    | Vcc                  | VSS | 18 | 26 | Gnd    | Gnd            |                       |                         |  |                |

### DC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>CC</sub> = 5.0 V  $\pm$ 10%, T<sub>A</sub> = -55 to +125°C, Unless Otherwise Noted)

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                | Symbol          | Min                   | Тур | Max                   | Unit | Notes |

|------------------------------------------|-----------------|-----------------------|-----|-----------------------|------|-------|

| Supply Voltage (Operating Voltage Range) | Vcc             | 4.5                   | 5.0 | 5.5                   | ٧    | 1     |

|                                          | VSS             | 0                     | 0   | 0                     |      |       |

| Logic High Voltage, All Inputs           | VIH             | 2.4                   |     | 6.5                   | ٧    | 1     |

| Logic Low Voltage, All Inputs            | V <sub>IL</sub> | -1.0                  |     | 0.8                   | ٧    | 1     |

| Test Function Input High Voltage         | VIH (TF)        | V <sub>CC</sub> + 4.5 | _   | 10.5                  | ٧    | 1     |

| Test Function Input Low Voltage          | VIL (TF)        | -1.0                  |     | V <sub>CC</sub> + 1.0 | ٧    | 1     |

### DC CHARACTERISTICS

### MOTOROLA SC {MEMORY/ASI 65E D

| Characteristic                                                                                                                                                                                                            | Symbol              | Min                | Max                  | Unit | Notes |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|----------------------|------|-------|

| V <sub>CC</sub> Power Supply Current<br>511000A-8, t <sub>RC</sub> = 150 ns<br>511000A-9, t <sub>RC</sub> = 170 ns<br>511000A-11, t <sub>RC</sub> = 200 ns<br>511000A-12, t <sub>RC</sub> = 220 ns                        | ICC1                | _<br>_<br>_        | 90<br>80<br>70<br>60 | mA   | 2     |

| $V_{CC}$ Power Supply Current (Standby) ( $\overline{RAS} = \overline{CAS} = V_{IH}$ )                                                                                                                                    | ICC2                |                    | 4.0                  | mA   |       |

| $v_{CC}$ Power Supply Current During $\overline{RAS}$ only Refresh Cycles $(\overline{CAS}=v_{IH})$ 511000A-8, $t_{RC}$ = 150 ns 511000A-9, $t_{RC}$ = 170 ns 511000A-11, $t_{RC}$ = 200 ns 511000A-12, $t_{RC}$ = 220 ns | ICC3                | _<br>_<br>_<br>_   | 90<br>80<br>70<br>60 | mA   | 2     |

| $V_{CC}$ Power Supply Current During Fast Page Mode Cycle ( $\overline{RAS}$ = $V_{IL}$ ) 511000A-8, tpC = 45 ns 511000A-9, tpC = 50 ns 511000A-11, tpC = 60 ns 511000A-12, tpC = 65 ns                                   | ICC4                | <u>-</u><br>-<br>- | 70<br>60<br>50<br>40 | mA   | 2,3   |

| V <sub>CC</sub> Power Supply Current (Standby) ( <del>RAS</del> = <del>CAS</del> = V <sub>CC</sub> -0.2V)                                                                                                                 | ICC5                |                    | 2.0                  | mA   |       |

| $V_{CC}$ Power Supply Current During $\overline{CAS}$ Before $\overline{RAS}$ Refresh Cycle 511000A-8, $t_{RC}$ = 150 ns 511000A-9, $t_{RC}$ = 170 ns 511000A-11, $t_{RC}$ = 200 ns 511000A-12, $t_{RC}$ = 220 ns         | ICC6                |                    | 90<br>80<br>70<br>60 | mA   | 2     |

| Input Leakage Current (Except TF) (0 V $\leq$ V <sub>in</sub> $\leq$ 6.5 V)                                                                                                                                               | llkg(l)             | -10                | 10                   | μА   |       |

| Input Leakage Current (TF) (0 V $\leq$ Vin(TF) $\leq$ VCC + 0.5 V)                                                                                                                                                        | l <sub>lkg(l)</sub> | -10                | 10                   | μА   |       |

| Output Leakage Current ( $\overline{CAS} = V_{IH}$ , 0 V $\leq V_{Out} \leq 5.5 \text{ V}$ )                                                                                                                              | likg(O)             | -10                | 10                   | μА   |       |

| Test Function Input Current ( $V_{CC} + 4.5 \text{ V} \le V_{in(TF)} \le 10.5 \text{ V}$ )                                                                                                                                | lin(TF)             | _                  | 1.0                  | mA   |       |

| Output High Voltage ( $I_{OH} = -5 \text{ mA}$ )                                                                                                                                                                          | VOH                 | 2.4                |                      | V    |       |

| Output Low Voltage (I <sub>OL</sub> = 4.2 mA)                                                                                                                                                                             | VOL                 |                    | 0.4                  | ٧    |       |

### **CAPACITANCE** (f = 1.0 MHz, $T_A$ = 25°C, $V_{CC}$ = 5 V, Periodically Sampled Rather Than 100% Tested)

| Parameter                                        |                 | Symbol | Max | Unit | Notes |

|--------------------------------------------------|-----------------|--------|-----|------|-------|

| Input Capacitance                                | A0-A9, D        | Cin    | 5.0 | pF   | 4     |

|                                                  | RAS, CAS, W, TF |        | 7.0 | pF   | 4     |

| Output Capacitance (CAS = VIH to Disable Output) | Q               | Cout   | 7.0 | pF   | 4     |

### NOTES:

- 1. All voltages referenced to VSS.

- 2. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

- 3. Measured with one address transition per page mode cycle.

- 4. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation:  $C = I\Delta t/\Delta V$ .

AC OPERATING CONDITIONS AND CHARACTERISTICS (V $_{CC}$  = 5.0 V  $\pm$ 10%, T $_{A}$  = -55 to +125°C, Unless Otherwise Noted)

### READ, WRITE, AND READ-WRITE CYCLES

| Parameter                                       | Syn                 | nbol             | 5110 | 000A-8  | 5110 | 000A-9   | 5110 | 00A-11        | 5110 | 00A-12                                           | $\neg$ |               |

|-------------------------------------------------|---------------------|------------------|------|---------|------|----------|------|---------------|------|--------------------------------------------------|--------|---------------|

| - arameter                                      | Standard            | Alt.             | Min  | Max     | Min  | Max      | Min  | Max           | Min  | Max                                              | Unit   | Notes         |

| Random Read or<br>Write Cycle Time              | †RELREL             | tRC              | 150  | _       | 170  | _        | 200  | -             | 220  | _                                                | ns     | 5-10          |

| Read-Write Cycle<br>Time                        | †RELREL             | tRWC             | 175  | -       | 195  |          | 230  | <del>  </del> | 245  | <del>  </del>                                    | ns     | 5-10          |

| Page Mode Cycle<br>Time                         | <sup>t</sup> CELCEL | <sup>†</sup> PC  | 45   | _       | 50   | _        | 60   | _             | 65   | <del>                                     </del> | ns     | 5-9           |

| Page Mode Read-<br>Write Cycle Time             | †CELCEL             | tPRWC            | 70   | T       | 75   | _        | 90   | _             | 95   | _                                                | ns     | 5-9           |

| Access Time from RAS                            | tRELQV              | <sup>t</sup> RAC | _    | 80      |      | 90       | _    | 110           |      | 120                                              | ns     | 5-9<br>11, 12 |

| Access Time from CAS                            | †CELQV              | tCAC             | _    | 25      | _    | 25       | _    | 25            | _    | 25                                               | ns     | 5-9<br>11, 13 |

| Access Time from<br>Column Address              | <sup>t</sup> AVQV   | †AA              |      | 40      | _    | 45       | _    | 55            | _    | 60                                               | ns     | 5-9<br>11, 14 |

| Access Time from<br>Precharge CAS               | <sup>t</sup> CEHQV  | <sup>t</sup> CPA | -    | 40      | _    | 45       | _    | 55            | _    | 60                                               | ns     | 5-9,          |

| CAS to Output in<br>Low-Z                       | †CELQX              | <sup>t</sup> CLZ | 0    | _       | 0    | _        | 0    | -             | 0    | _                                                | ns     | 5-9,<br>11    |

| Output Buffer and<br>Turn-Off Delay             | <sup>t</sup> CEHQZ  | <sup>t</sup> OFF | 0    | 20      | 0    | 20       | 0    | 20            | 0    | 20                                               | ns     | 5-9,<br>15    |

| Transition Time (Rise and Fall)                 | tŢ                  | t <sub>T</sub>   | 3    | 50      | 3    | 50       | 3    | 50            | 3    | 50                                               | ns     | 5-9           |

| RAS Precharge Time                              | <sup>t</sup> REHREL | tRP              | 60   | _       | 70   | <b> </b> | 80   |               | 90   | <u> </u>                                         | ns     | 5-9           |

| RAS Pulse Width                                 | <sup>†</sup> RELREH | tRAS             | 80   | 10,000  | 90   | 10,000   | 110  | 10,000        | 120  | 10,000                                           | ns     | 5-9           |

| RAS Pulse Width<br>(Fast Page Mode)             | <sup>t</sup> RELREH | †RASP            | 80   | 100,000 | 90   | 100,000  | 110  | 100,000       | 120  | 10,000                                           | ns     | 5-9           |

| RAS Hold Time                                   | tCELREH             | <sup>t</sup> RSH | 20   | _       | 20   |          | 25   |               | 25   | <del>  </del>                                    | ns     | 5-9           |

| CAS Hold Time                                   | <sup>†</sup> RELCEH | tcsH             | 80   |         | 90   |          | 110  |               | 120  |                                                  | ns     | 5-9           |

| CAS Pulse Width                                 | <sup>†</sup> CELCEH | tCAS             | 25   | 10,000  | 25   | 10,000   | 30   | 10,000        | 35   | 10,000                                           | ns     | 5-9           |

| RAS to CAS Delay<br>Time                        | <sup>t</sup> RELCEL | <sup>‡</sup> RCD | 25   | 60      | 25   | 70       | 30   | 80            | 35   | 95                                               | ns     | 5-9,<br>16    |

| RAS to Column<br>Address Delay Time             | tRELAV              | <sup>t</sup> RAD | 15   | 40      | 15   | 45       | 20   | 55            | 20   | 60                                               | ns     | 5-9           |

| CAS to RAS<br>Precharge Time                    | <sup>†</sup> CEHREL | <sup>t</sup> CRP | 5    | -       | 5    | _        | 5    | _             | 5    |                                                  | ns     | 5-9           |

| CAS Precharge Time<br>(Page Mode Cycle<br>Only) | <sup>†</sup> CEHCEL | tCP              | 10   |         | 10   | _        | 10   | -             | 10   | _                                                | ns     | 5-9           |

| Row Address Setup<br>Time                       | <sup>t</sup> AVREL  | <sup>t</sup> ASR | 0    | _       | 0    | _        | 0    |               | 0    | _                                                | ns     | 5-9           |

| Row Address Hold<br>Time                        | <sup>t</sup> RELAX  | <sup>t</sup> RAH | 10   | _       | 15   | _        | 15   |               | 15   |                                                  | ns     | 5-9           |

| Column Address<br>Setup Time                    | <sup>t</sup> AVCEL  | †ASC             | 0    | _       | 0    |          | 0    |               | 0    | _                                                | ns     | 5-9           |

MOTOROLA SC {MEMORY/ASI LSE D

### READ, WRITE, AND READ-WRITE CYCLES (continued)

|                                                 | Symt                | ool               | 51100 | 0A-8 | 51100 | 0A-9 | 51100 | 0A-11       | 51100 | 0A-12 | Unit | Notes      |

|-------------------------------------------------|---------------------|-------------------|-------|------|-------|------|-------|-------------|-------|-------|------|------------|

| Parameter                                       | Standard            | Alt.              | Min   | Max  | Min   | Max  | Min   | Max         | Min   | Max   | Jan. |            |

| Column Address<br>Hold Time                     | †CELAX              | <sup>†</sup> CAH  | 15    | _    | 20    | _    | 20    | _           | 20    |       | ns   | 5-9        |

| Column Address Hold Time Referenced to RAS      | <sup>†</sup> RELAX  | tar .             | 60    | _    | 65    | _    | 80    | _           | 85    | _     | ns   | 5-9        |

| Column Address to<br>RAS Lead Time              | <sup>t</sup> AVREH  | <sup>t</sup> RAL  | 40    |      | 45    |      | 55    | -           | 60    | _     | ns   | 5-9        |

| Read Command<br>Setup Time                      | tWHCEL              | <sup>t</sup> RCS  | 0     | -    | 0     | _    | 0     | _           | 0     |       | ns   | 5-9        |

| Read Command<br>Hold Time<br>Referenced to CAS  | <sup>†</sup> CEHWX  | <sup>t</sup> RCH  | 0     | _    | 0     | _    | 0     | _           | 0     |       | ns   | 5-9,<br>18 |

| Read Command<br>Hold Time<br>Referenced to RAS  | <sup>†</sup> REHWX  | tRRH              | 0     |      | 0     | _    | 0     | _           | 0     | _     | ns   | 5-9,<br>18 |

| Write Command<br>Hold Time<br>Referenced to CAS | <sup>t</sup> CELWH  | tWCH              | 15    | _    | 20    | _    | 20    | <del></del> | 20    |       | ns   | 5-9        |

| Write Command<br>Hold Time<br>Referenced to RAS | <sup>t</sup> RELWH  | twcR              | 60    |      | 65    |      | 80    |             | 85    | _     | ns   | 5-9        |

| Write Command<br>Pulse Width                    | tWLWH               | tWP               | 15    | _    | 20    | _    | 20    |             | 20    | _     | ns   | 5-9        |

| Write Command to RAS Lead Time                  | tWLREH              | tRWL              | 20    |      | 20    |      | 25    |             | 25    |       | ns   | 5-9        |

| Write Command to CAS Lead Time                  | tWLCEH              | <sup>t</sup> CWL  | 20    |      | 20    | _    | 25    |             | 25    |       | ns   | 5-9        |

| Data In Setup Time                              | tDVCEL              | tDS               | 0     |      | 0     |      | 0     |             | 0     | -     | ns   | 5-9,<br>19 |

| Data In Hold Time                               | tCELDX              | <sup>t</sup> DH   | 15    | _    | 20    |      | 20    |             | 20    |       | ns   | 5-9,<br>19 |

| Data In Hold Time<br>Referenced to RAS          | <sup>t</sup> RELDX  | <sup>t</sup> DHR  | 60    | _    | 70    | _    | 85    |             | 90    |       | ns   | 5-9        |

| Refresh Period<br>511000A                       | <sup>t</sup> RVRV   | <sup>t</sup> RFSH | _     | 8.0  |       | 8.0  |       | 8.0         |       | 8.0   | ms   | 5-9        |

| Write Command<br>Setup Time                     | tWLCEL              | twcs              | 0     |      | 0     | _    | 0     |             | 0     | _     | ns   | 5-9<br>20  |

| CAS to Write Delay                              | †GELWL              | tCMD              | 20    | _    | 25    |      | 25    |             | 25    | _     | ns   | 5-9<br>20  |

| RAS to Write Delay                              | <sup>t</sup> RELWL  | tRWD              | 80    |      | 90    |      | 110   |             | 120   | _     | ns   | 5-9<br>20  |

| Column Address to<br>Write Delay Time           | <sup>†</sup> AVWL   | tAWD              | 40    | _    | 45    | _    | 55    |             | 60    |       | ns   | 5-9<br>20  |

| CAS Setup Time for CAS Before RAS Refresh       | <sup>t</sup> RELCEL | <sup>t</sup> CSR  | 10    |      | 10    |      | 10    | _           | 10    | _     | ns   | 5-9        |

| CAS Hold Time for<br>CAS Before RAS<br>Refresh  | †RELCEH             | t <sub>CHR</sub>  | 30    | _    | 30    | -    | 30    | _           | 30    | _     | ns   | 5-9        |

MOTOROLA SC {MEMORY/ASI 65E D

### READ, WRITE, AND READ-WRITE CYCLES (continued)

| Parameter                                           | Symbol              |                   | 511000A-8 |     | 51100 | 511000A-9 |     | 511000A-11 |     | 0A-12    | T    |       |

|-----------------------------------------------------|---------------------|-------------------|-----------|-----|-------|-----------|-----|------------|-----|----------|------|-------|

| Fatameter                                           | Standard            | Alt.              | Min       | Max | Min   | Max       | Min | Max        | Min | Max      | Unit | Notes |

| CAS Precharge to CAS Active Time                    | <sup>†</sup> REHCEL | tRPC              | 0         | _   | 0     | _         | 0   |            | 0   | _        | ns   | 5-9   |

| CAS Precharge Time for CAS Before RAS Counter Test  | <sup>†</sup> CEHCEL | <sup>†</sup> CPT  | 40        | _   | 40    | _         | 50  | _          | 50  | _        | ns   | 5-9   |

| CAS Precharge Time                                  | <sup>†</sup> CEHCEL | t <sub>CPN</sub>  | 30        | _   | 30    |           | 40  | _          | 40  | <u> </u> | ns   | 5-9   |

| Test Mode Enable<br>Setup Time<br>Referenced to RAS | †TEHREL             | t <sub>TES</sub>  | 0         |     | 0     | _         | 0   | _          | 0   | _        | ns   | 5-9   |

| Test Mode Enable<br>Hold Time<br>Referenced to RAS  | <sup>†</sup> REHTEL | <sup>†</sup> TEHR | 0         | _   | 0     | _         | 0   | _          | 0   | _        | ns   | 5-9   |

| Test Mode Enable<br>Hold Time<br>Referenced to CAS  | <sup>†</sup> CEHTEL | <sup>†</sup> TEHC | 0         | _   | 0     | _         | 0   | _          | 0   | _        | ns   | 5-9   |

#### NOTES:

- 5. VIH min and VIL max are reference levels for measuring timing of input signals. Transition times are measures between VIH and VIL.

- 6. An initial pause of 200 µs is required after power-up followed by 8 RAS cycles before proper device operation is guaranteed.

- The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals

must transition between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>II</sub> and V<sub>IH</sub>) in a monotonic manner.

- 8. AC measurements  $t_T = 5.0$  ns.

- 9. TF pin must be at V<sub>1L</sub> or open if not used.

- The specifications for t<sub>RC</sub> (min) and t<sub>RWC</sub> (min) are used only to indicate cycle time at which proper operation over the full temperature range –55°C ≤ T<sub>A</sub> ≤ 125°C.

- Measured with a current load equivalent to 2 TTL (~200 μA, +4 mA) loads and 100 pF with the data output trip points set at VOH = 2.0 V and VOI = 0.8 V.

- Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max).

- Assumes that t<sub>RCD</sub> ≥ t<sub>RCD</sub> (max).

- 14. Assumes that t<sub>RAD</sub> ≥ t<sub>RAD</sub> (max).

- 15. tOFF (max) defines the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

MOTOROLA SC (MEMORY/AST 65E D

- Operation within the t<sub>RCD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 17. Operation within the t<sub>RAD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RAD</sub> (max) is specified as a reference point only; if t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub> (max), then access time is controlled exclusively by t<sub>AA</sub>.

- 18. Either tare or tach must be satisfied for a read cycle.

- These parameters are referenced to CAS leading edge in random write cycles and to W leading edge in delayed write or read-write cycles.

- 20. tWCS, tRWD, tCWD, and tAWD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; if tWCS ≥ tWCS (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if tCWD ≥ tCWD (min), ttwD ≥ tRWD (min), and tAWD ≥ tAWD (min), the cycle is a read-write cycle and the data out will contain data read from the selected cell. If neither of these sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

toff -

VALID DATA

#### **READ CYCLE** — trc tRP ٧<sub>H</sub>-- tras -RAS VIL-<sup>t</sup>CPN tcsh. t<sub>RCD</sub> <sup>t</sup>RSH **tCRP** CAS V<sub>IL</sub>-<sup>t</sup>AR †RAD t<sub>RAL</sub> <sup>t</sup>CAH VIH - Z ROW ADDRESS COLUMN ADDRESS ADDRESSES V<sub>IL</sub>-<sup>t</sup>RAH **TRRH** trcs + $v_{\text{IH}}$ – ← tcac →

tcız 🕇

t<sub>RAC</sub>

- HIGH Z -

VoH-

Vol-

Q (DATA OUT)

#### **EARLY WRITE CYCLE tRP** VIH-†RAS RAS VIL-<sup>t</sup>CPN t<sub>RCD</sub> **t**RSH **t**CRP <sup>†</sup>CSH **tCRP** VIH-CAS V<sub>IL</sub> -<sup>t</sup>AR t<sub>RAL</sub> <sup>t</sup>RAD †ASR tCAH †ASC V<sub>IH</sub>-COLUMN ADDRESS ROW ADDRESS ADDRESSES V<sub>IL</sub>t<sub>CWL</sub> - twch twcs t<sub>RWL</sub> tWCR tos -VIH-D (DATA IN) t<sub>DHR</sub> V<sub>OH</sub> ~ - HIGH Z Q (DATA OUT) VOL-MOTOROLA SC {MEMORY/ASI LSE D

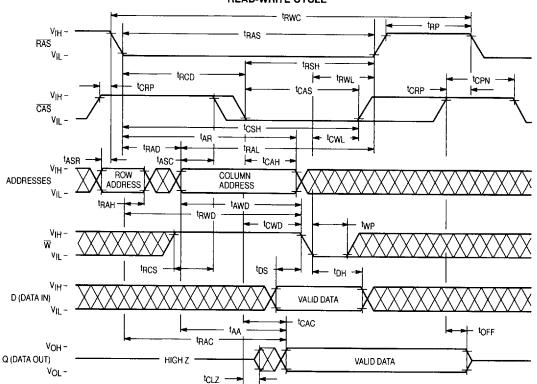

### READ-WRITE CYCLE

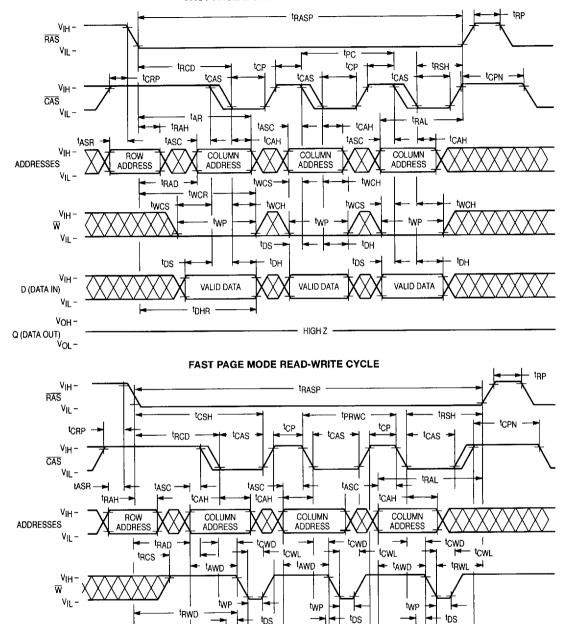

### **FAST PAGE MODE READ CYCLE**

COMMERCIAL PLUS AND MIL/AERO APPLICATIONS MEMORY DATA

### FAST PAGE MODE EARLY WRITE CYCLE

COMMERCIAL PLUS AND MIL/AERO APPLICATIONS MEMORY DATA

OFF 🔫

tos

tCAC →

t<sub>RAC</sub>

V<sub>IH</sub> -

VOH-

Vol-

D (DATA IN)

Q (DATA OUT)

†DH

<sup>t</sup>CPA

<sup>t</sup>DH

<sup>t</sup>CPA

DATA

toff →

- tcac

VALID

DATA

toff 🕶 🛏

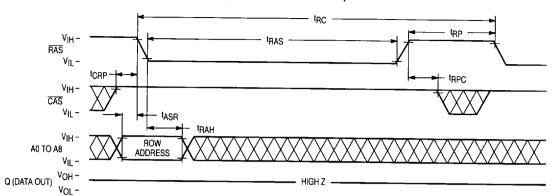

### RAS ONLY REFRESH CYCLE (W and A9 are Don't Care)

### MOTOROLA SC {MEMORY/ASI LSE D

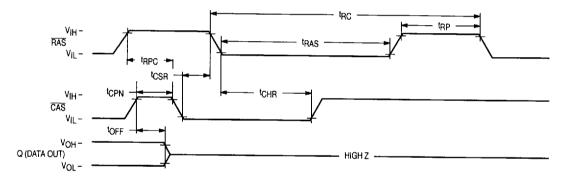

### CAS BEFORE RAS REFRESH CYCLE (W and A0 to A9 are Don't Care)

COMMERCIAL PLUS AND MIL/AERO APPLICATIONS MEMORY DATA

### CAS BEFORE RAS REFRESH COUNTER TEST CYCLE

MOTOROLA SC {MEMORY/ASI LSE D

### **DEVICE INITIALIZATION**

On power-up an initial pause of 200 microseconds is required for the internal substrate generator to establish the correct bias voltage. This must be followed by a minimum of eight active cycles of the row address strobe (clock) to initialize all dynamic nodes within the RAM. During an extended inactive state (greater than 8 milliseconds with the device powered up), a wake up sequence of eight active cycles is necessary to assure proper operation.

### ADDRESSING THE RAM

The ten address pins on the device are time multiplexed at the beginning of a memory cycle by two clocks, row address strobe (RAS) and column address strobe (CAS), into two separate 10-bit address fields. A total of twenty address bits, ten rows and ten columns, will decode one of the 1,048,576 bit locations in the device. RAS active (VIL) transition is followed by CAS active transition (after tRCD minimum delay) for all read or write cycles. The delay between RAS and CAS active transitions, referred to as the multiplex window, gives a system designer flexibility in setting up the external addresses into the RAM.

The external  $\overline{\text{CAS}}$  signal is ignored until an internal  $\overline{\text{RAS}}$  signal is available. This "gate" feature on the external  $\overline{\text{CAS}}$  clock enables the internal  $\overline{\text{CAS}}$  line as soon as the row addressholdtime (tRAH) specification is met (and definest RCD minimum). The multiplex window can be used to absorb skew delays in switching the address bus from row to column addresses and in generating the  $\overline{\text{CAS}}$  clock.

There are two other variations in addressing the 1M RAM: RAS only refresh cycle and CAS before RAS refresh cycle. Both are discussed in separate sections that follow.

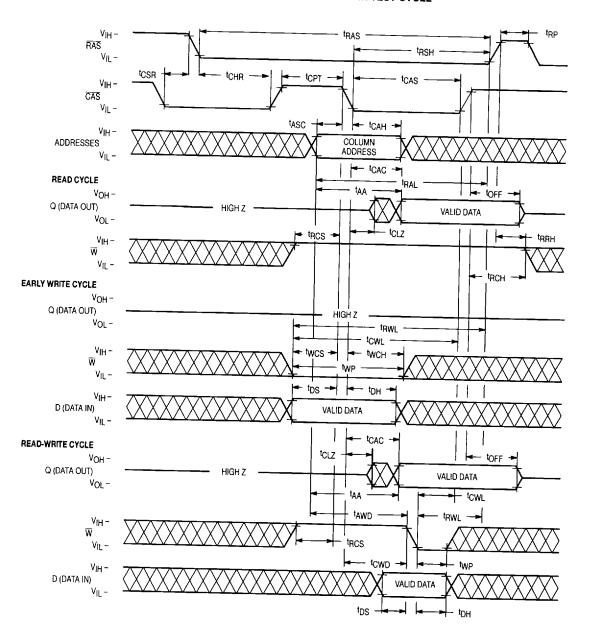

### **READ CYCLE**

The DRAM may be read with four different cycles: "normal" random read cycle, page mode read cycle, read-write cycle, and page mode read-write cycle. The normal read cycle is outlined here, while the other cycles are discussed in separate sections.

The normal read cycle begins as described in ADDRESSING THE RAM, with  $\overline{RAS}$  and  $\overline{CAS}$  active transitions latching the desired bit location. The write  $\overline{(W)}$  input level must be high  $\overline{(V)_{H}}$ ,  $\overline{t_{RCS}}$  (minimum) before the  $\overline{CAS}$  active transition, to enable read mode.

Both the RAS and CAS clocks trigger a sequence of events which are controlled by several delayed internal clocks. The internal clocks are linked in such a manner that the read access time of the device is independent of the address multiplex window. However, CAS must be active before or at tRCD maximum to guarantee valid data out (Q) at tRAC (access time from RAS active transition). If the tRCD maximum is exceeded, read access time is determined by the CAS clock active transition (tCAC).

The RAS and CAS clocks must remain active for a minimum time of tras and tcAs respectively, to complete the read cycle. W must remain high throughout the cycle, and for time transfer transition, respectively, to maintain the data at that bit location. Once RAS transitions to inactive, it must remain inactive for a minimum time of transfer to precharge the internal device circuitry for the next active cycle.

Q is valid, but not latched, as long as the  $\overline{\text{CAS}}$  clock is active. When the  $\overline{\text{CAS}}$  clock transitions to inactive, the output will switch to High Z.

### WRITE CYCLE

The user can write to the DRAM with any of four cycles; early write, late write, page mode early write, and page mode read-write. Early and late write modes are discussed here, while page mode write operations are covered in another section.

A write cycle begins as described in **ADDRESSING THE RAM**. Write mode is enabled by the transition of  $\overline{W}$  to active (VIL). Early and late write modes are distinguished by the active transition of  $\overline{W}$ , with respect to  $\overline{CAS}$ . Minimum active time transition of  $\overline{W}$ , and precharge time transition of  $\overline{W}$  write mode, as in the read mode.

An early write cycle is characterized by  $\overline{W}$  active transition at minimum time twcs before  $\overline{CAS}$  active transition. Data in (D) is referenced to  $\overline{CAS}$  in an early write cycle.  $\overline{RAS}$  and  $\overline{CAS}$  clocks must stay active for tRWL and tCWL, respectively, after the start of the early write operation to complete the cycle.

Q remains High Z throughout an early write cycle because  $\overline{W}$  active transition precedes or coincides with  $\overline{CAS}$  active transition, keeping data-out buffers disabled. This feature can be utilized on systems with a common I/O bus, provided all writes are performed with early write cycles, to prevent bus contention.

A late write cycle occurs when  $\overline{W}$  active transition is made after  $\overline{CAS}$  active transition.  $\overline{W}$  active transition could be delayed for almost 10 microseconds after  $\overline{CAS}$  active transition, (tRCD+tCWD+tRWL+2tT)  $\leq$  tRAS, if other timing minimums(tRCD.tRWL, andtT) are maintained. Disreferenced to  $\overline{W}$  active transition in a late write cycle. Output buffers are enabled by  $\overline{CAS}$  active transition but Q may be indeterminate—see note 16 of AC operating conditions table.  $\overline{RAS}$  and  $\overline{CAS}$  must remain active for tRWL and tCWL, respectively, after  $\overline{W}$  active transition to complete the write cycle.

### **READ-WRITE CYCLE**

A read-write cycle performs a read and then a write at the same address, during the same cycle. This cycle is basically a late write cycle, as discussed in the **WRITE CYCLE** section, except  $\overline{W}$  must remain high for tCWD minimum after the  $\overline{CAS}$  active transition, to guarantee valid Q before writing the bit.

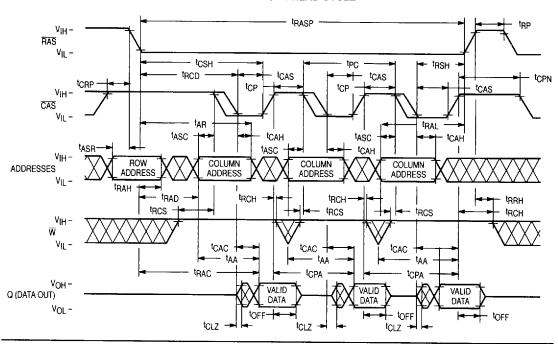

### PAGE MODE CYCLES

Page mode allows fast successive data operations at all 2048 column locations on a selected row of the 1M dynamic RAM. Read access time in page mode (tCAC) is typically half the regular RAS clock access time, tRAC. Page mode operation consists of keeping RAS active while toggling CAS between VIH and VIL. The row is latched by RAS active transition, while each CAS active transition allows selection of a new column location on the row.

A page mode cycle is initiated by a normal read, write, or read-write cycle, as described in prior sections. Once the timing requirements for the first cycle are met, CAS transitions to inactive for minimum of tcp, while RAS remains low (V<sub>IL</sub>). The second CAS active transition while RAS is low initiates the first page mode cycle (tpc or tpRWC). Either a read, write, or read-write operation can be performed in a page mode cycle,

subject to the same conditions as in normal operation (previously described). These operations can be intermixed in consecutive page mode cycles and performed in any order. The maximum number of consecutive page mode cycles is limited by tRASP. Page mode operation is ended when RAS transitions to inactive, coincident with or following CAS inactive transition.

### REFRESH CYCLES

The dynamic RAM design is based on capacitor charge storage for each bit in the array. This charge degrades with time and temperature, thus each bit must be periodically refreshed (recharged) to maintain the correct bit state. Bits in the 511000A require refresh every 8 milliseconds.

Refresh is accomplished by cycling through the 512 row addresses in sequence within the specified refresh time. All the bits on a row are refreshed simultaneously when the row is addressed. Distributed refresh implies a row refresh every 15.6 microseconds for the 511000A. Burst refresh, a refresh of all 512 rows consecutively, must be performed every 8 milliseconds on the 511000A.

A normal read, write, or read-write operation to the RAM will refresh all the bits (2048) associated with the particular row decoded. Three other methods of refresh, RAS-only refresh, CAS before RAS refresh, and hidden refresh are available on this device for greater system flexibility.

### RAS-Only Refresh

RAS-only refresh consists of RAS transition to active. latching the row address to be refreshed, while CAS remains high (VIH) throughout the cycle. An external counter is employed to ensure all rows are refreshed within the specified limit.

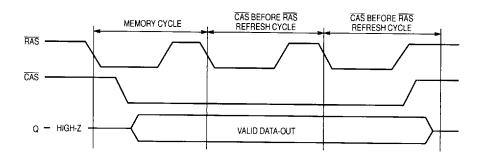

### CAS Before RAS Refresh

CAS before RAS refresh is enabled by bringing CAS active before RAS. This clock order activates an internal refresh

counter that generates the row address to be refreshed. External address lines are ignored during the automatic refresh cycle. The output buffer remains at the same state it was in during the previous cycle (hidden refresh).

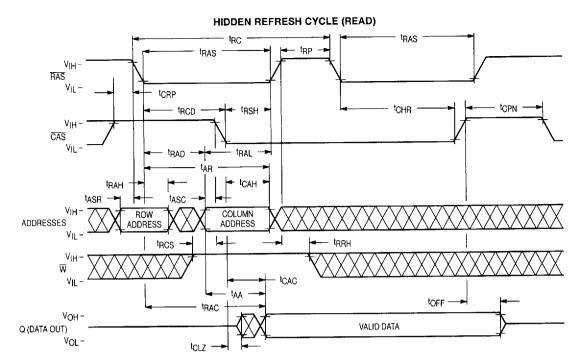

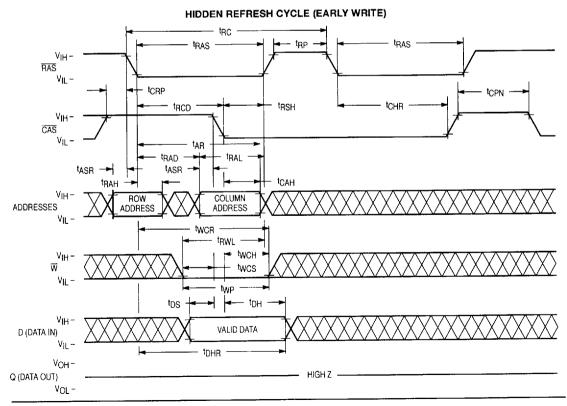

### Hidden Refresh

Hidden refresh allows cycles to occur while maintaining valid data at the output pin. Holding CAS active at the end of a read or write cycle, while RAS cycles inactive for tRP and back to active, starts the hidden refresh. This is essentially the execution of a CAS before RAS refresh from a cycle in progress (see Figure 1).

### **CAS BEFORE RAS REFRESH COUNTER TEST**

The internal refresh counter of this device can be tested with a CAS before RAS refresh counter test. This test is performed with a read-write operation. During the test, the internal refresh counter generates the row address, while the external address supplies the column address. The entire array is refreshed after 512 cycles, as indicated by the check data written in each row. See CAS before RAS refresh counter test cycle timing diagram.

The test can be performed after a minimum of eight CAS before RAS initialization cycles. Test procedure:

- 1. Write "0"s into all memory cells with normal write mode.

- 2. Select a column address, read "0" out and write "1" into the cell by performing the CAS before RAS refresh counter test, read-write cycle. Repeat this operation 512 times.

- 3. Read the "1"s which were written in step 2 in normal read mode.

- 4. Using the same starting column address as in step 2, read "1" out and write "0" into cell by performing the CAS before RAS refresh counter test, read-write cycle. Repeat this operation 512 times.

- 5. Read "0"s which were written in step 4 in normal read mode.

- 6. Repeat steps 1 to 5 using complement data.

Figure 1. Hidden Refresh Cycle

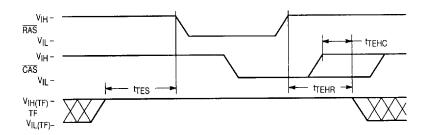

### **TEST MODE**

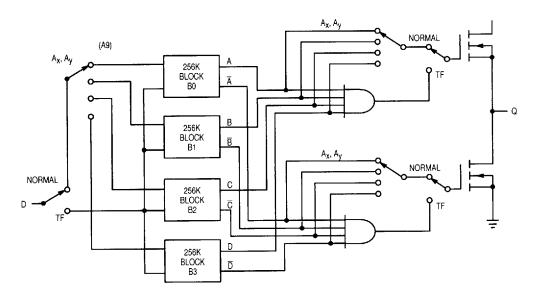

Internal organization of this device (256K x 4) allows it to be tested as if it were a 256K x 1 DRAM. Only nine of the ten addresses (A0-A8) are used in test mode; A9 is internally disabled. A test mode write cycle writes data, D (data in), to a bit in each of the four 256K x 1 blocks (B0-B3), in parallel. A test mode read cycle reads a bit in each of the four blocks. If data is the same in all four bits, Q (data out) is the same as the data in each bit. If data is not the same in all four bits, Q is high Z. See truth table and block diagram.

Test mode can be used in any timing cycle, including page mode cycles. The test mode function is enabled by holding the "TF" pin on "super voltage" for the specified period (tTES, tTEHR, tTEHC; see Test Mode Cycle). "Super voltage" = V<sub>CC</sub> + 4.5 V

where

$4.5V < V_{CC} < 5.5 V$  and maximum voltage = 10.5 V. A9 is ignored in test mode. In normal operation, the "TF" pin must either be connected to VIL, or left open.

**TEST MODE TRUTH TABLE**

| D | В0 | B1         | B2         | В3 | Q      |

|---|----|------------|------------|----|--------|

| 0 | 0  | 0          | 0          | 0  | 0      |

| _ |    | I<br>Any ( | ı<br>Other |    | High-Z |

### MOTOROLA SC {MEMORY/ASI 65E D

### **TEST MODE CYCLE**

### **TEST FUNCTION BLOCK DIAGRAM**