|          |                                                                  |       |                    |   |            |           |      |     |          | A        | EVIS | SION | IS       |       |             |              | -                  |              |       |      |      |    |      |      |          |

|----------|------------------------------------------------------------------|-------|--------------------|---|------------|-----------|------|-----|----------|----------|------|------|----------|-------|-------------|--------------|--------------------|--------------|-------|------|------|----|------|------|----------|

| LTR      |                                                                  |       |                    |   |            |           | DES  | CRI | ЭΠО      | N        |      |      |          |       |             |              |                    | DA           | ΓE (Y | R-MO | -DA) | Π  | APPI | ROVE | D        |

|          |                                                                  |       |                    |   |            |           |      |     |          |          |      |      |          |       |             |              |                    |              |       |      |      |    |      |      |          |

| REV      |                                                                  | 丄     |                    |   |            | L         |      |     |          | L        |      |      | <u> </u> |       |             |              | Ш                  |              |       |      |      |    |      |      |          |

| SHEET    |                                                                  | _     | <u> </u>           | _ |            | <u> </u>  |      |     | <u> </u> |          |      |      | L        | L     |             | <u> </u>     | Ц                  |              |       |      |      |    |      |      |          |

| REV      |                                                                  | ┵     | ļ_                 |   |            | <u> </u>  | _    |     | <u> </u> | <u> </u> |      |      | L.       | _     |             |              | Ш                  |              |       | L    |      |    |      |      |          |

| SHEET    | 22                                                               | 23    | <u> </u>           | Щ |            |           |      |     |          | <u> </u> |      |      |          | L_    | <u> </u>    |              | Ш                  |              |       |      |      |    | L    |      |          |

| REV STA  |                                                                  |       | EV                 |   |            |           | _    | Щ   |          | <u> </u> | _    |      |          |       |             |              |                    |              |       |      |      |    |      |      |          |

|          |                                                                  | Si    | HEET               |   | 1          | 2         | 3    | 4   | 5        | 6        | 7    | 8    | 9        | 10    | 11          | 12           | 13                 | 14           | 15    | 16   | 17   | 18 | 19   | 20   | 21       |

| PMIC N/A | \                                                                |       |                    |   | PRE        | PARE      | D BY |     | يرد      | _        | 1    |      | ĺ        |       |             |              |                    |              |       |      |      |    |      |      |          |

| STAN     |                                                                  |       | D                  | 1 | CHECKED BY |           |      |     |          | 1        |      | DEF  | ENSI     | DAY   | TON         | ONIC<br>, OH | :S SI<br>10 4!<br> | JPPL<br>5444 | Y CE  | NTE  | R    |    |      |      |          |

|          | LITAI                                                            |       |                    | ŀ | ABBROOK BY |           |      |     |          | - ,      | IICR | OCIF | RCUI.    | TS, D | IGI         | TAL          | , CN               | 10S -        | 16.   | -BIT | SLT  | CF |      |      |          |

| DF       | RAWI                                                             | NG    |                    |   | The Solo   |           |      |     |          | M        | IICR | OPRO | OCES:    | SOR,  | MON         | IOL I        | ŤHĬĊ               | SI           | Lico  | )N   | ~_1  | ~  |      |      |          |

|          | THIS DRAWING IS AVAILABLE OR USE BY ALL DEPARTMENTS  10 MAY 1000 |       |                    |   |            | $\dagger$ | SIZE | Т   | c        | AGE CO   | OF.  |      | Т        |       |             |              |                    |              |       |      |      |    |      |      |          |

| AND A    | GENCIES                                                          | OF TI | OF THE 19 MAY 1989 |   |            |           |      | A   |          |          | 726  | _    |          | 1     | <b>59</b> ( | 62           | -89                | <b>3</b> 51  | 7     |      |      |    |      |      |          |

| AMSC N   |                                                                  | DEFE  | NSE                | ſ | REV        | ISION     | LEV  | EL  |          |          |      |      | 1        |       | HE          |              | 1                  |              | (     | OF   |      |    | 23   |      | $\dashv$ |

• U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/69911

5962-E1153

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

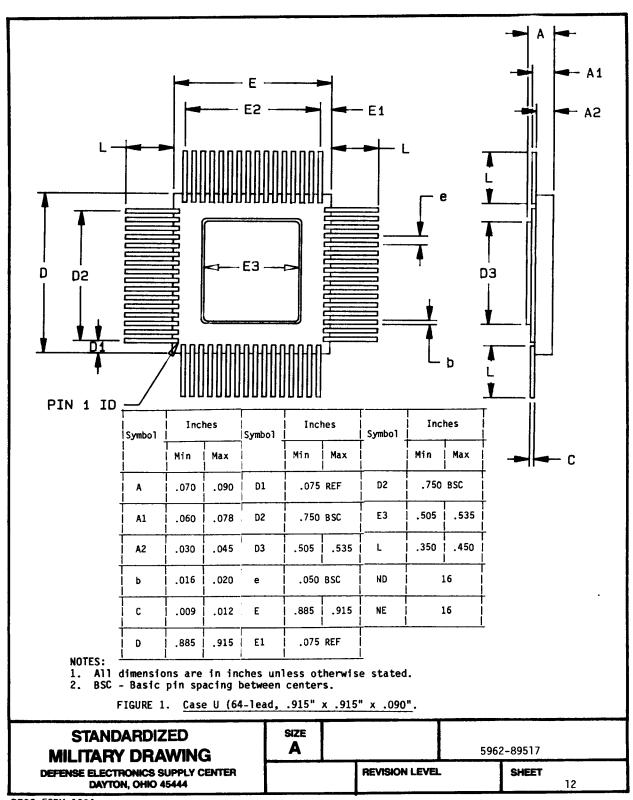

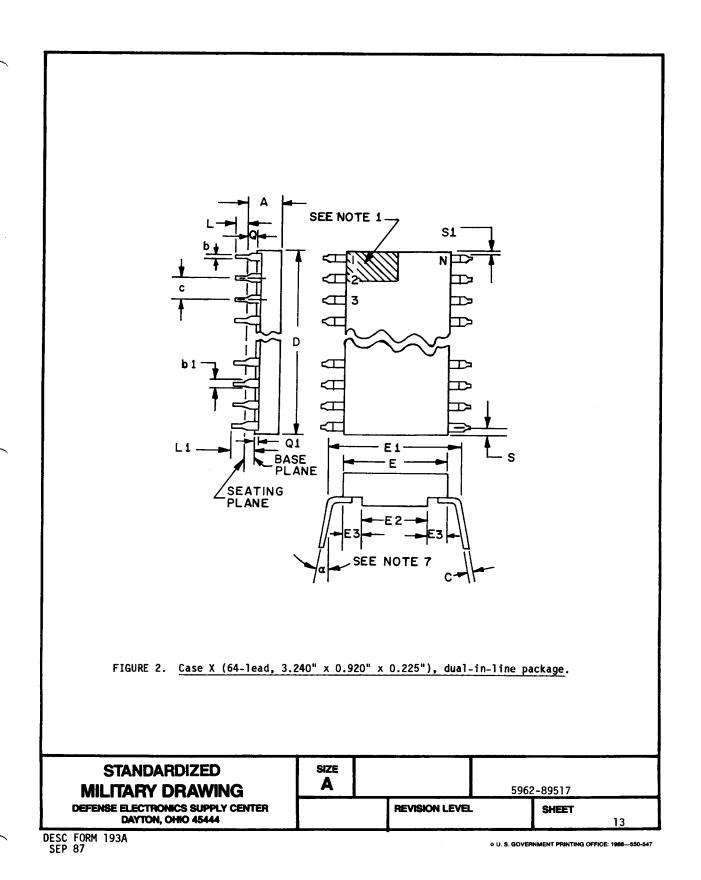

## 1. SCOPE 1.1 Scope. This drawing describes device requirements for class B microcircuits in accordance with $1.\overline{2.1}$ of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". 1.2 Part number. The complete part number shall be as shown in the following example: 5962-89517 Drawing number Device type Case outline Lead finish per (1.2.1)(1.2.2)MIL-M-38510 1.2.1 Device types. The device types shall identify the circuit function as follows: Device type Generic number Circuit function Cycle time 01 7C9101-45 16-bit microprocessor slice 45 ns 02 7C9101-35 16-bit microprocessor slice 35 ns 1.2.2 Case outlines. The case outlines shall be as designated in appendix C of MIL-M-38510, and as follows: Outline letter Case outline See figure 1 (64-lead, .915" x .915" x .090"), quad flat package See figure 2 (64-lead, 3.240" x .920" x .225"), dual-in-line package C-7 (68-terminal, .962" x .962" x .120"), square chip carrier package P-BC (68-pin, 1.135" x 1.135" x 345"), pin grid array U X 7 1.3 Absolute maximum ratings. -0.5 V dc to +7.0 V dc -0.5 V dc to +7.0 V dc Supply voltage range ---------DC voltage applied to outputs in high Z state - - --3.0 V dc to +7.0 V dc 30 mA 1.0 W +300°C Thermal resistance, junction-to-case ( $\theta_{JC}$ ): Case U -----22°C/W 28°C/W See MIL-M-38510, appendix C +175°C -65°C to +150°C 1.4 Recommended operating conditions. 1/ Must withstand the added PD due to short circuit test; e.g., $I_{OS}$ .

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

5962-89517

REVISION LEVEL

SHEET

2

DESC FORM 193A SEP 87

**☆** U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

# 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

- Microcircuits, General Specification for.

STANDARD

MILITARY

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices"

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

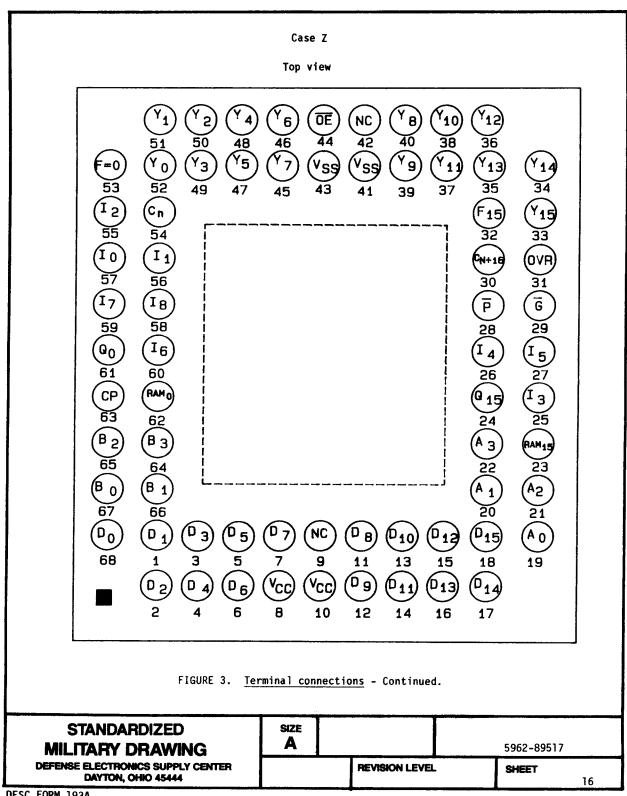

- 3.2.1 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 3.

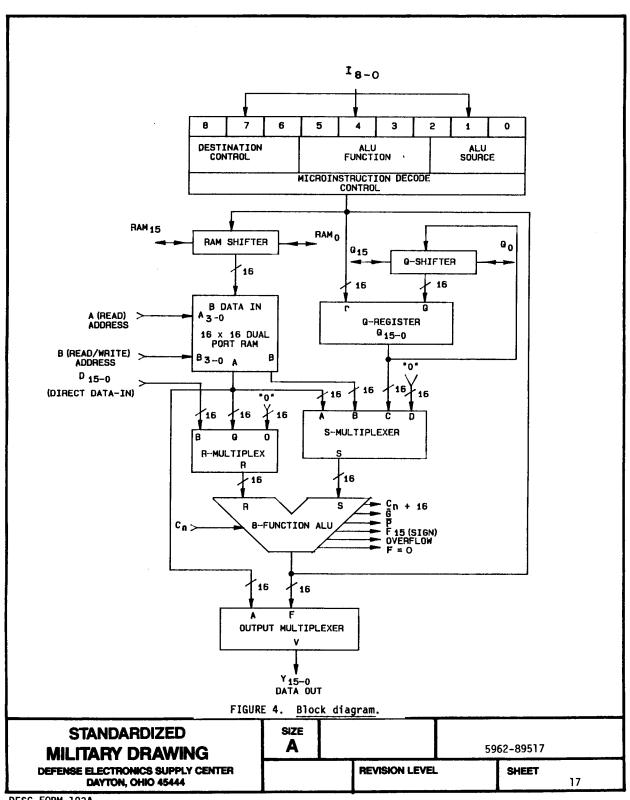

- 3.2.2 Functional block diagram. The functional block diagram shall be as specified on figure 4.

- 3.2.3 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- $3.4\,$  Marking. Marking shall be in accordance with MIL-STD-883 (see  $3.1\,$  herein). The part shall be marked with the part number listed in  $1.2\,$  herein. In addition, the manufacturer's part number may also be marked as listed in  $6.5\,$  herein.

- 3.5 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-EC\$ shall be required in accordance with MIL-STD-883 (see 3.5 herein).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 59 | 962-89517 |

|------------------------------------------------------|-----------|----------------|----|-----------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL |    | SHEET     |

DESC FORM 193A

SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904

|                                           | TABLE I.         | Electr                                                                                                                                          | rical perf                                                              | ormanc           | e characte | ristics        | •  |            |                |                   |             |

|-------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|------------|----------------|----|------------|----------------|-------------------|-------------|

| Test                                      | Symbol           | 4                                                                                                                                               | Conditi<br>°C < T <sub>C</sub> <<br>.5 V < V <sub>CC</sub><br>ss otherw | +125°(<br>: < 5. | )<br>5 V   | Device<br>type |    |            |                | its<br> <br>  Max | Uni         |

| Output high voltage                       | V <sub>OH</sub>  | V <sub>CC</sub> =                                                                                                                               | 4.5 V, I <sub>OF</sub>                                                  | = -3             | .4 mA      | <br>  A11<br>  | 1, | 2, 3       | 2.4            | <br>              | <br>  V<br> |

| Output low voltage                        | VOL              | ACC =                                                                                                                                           | 4.5 V, I <sub>OL</sub>                                                  | = 16             | .0 mA      | A11            | 1, | 2, 3       | <br> <br>      | 0.4               | <br>  V<br> |

| Input high voltage                        | VIH              |                                                                                                                                                 |                                                                         |                  |            | A11<br>        | 1, | 2, 3       | 2.0            |                   | V           |

| Input low voltage                         | VIL              |                                                                                                                                                 |                                                                         |                  |            | A11            | 1, | 2, 3       |                | 0.8               | ٧           |

| Input leakage current                     | IIX              | VCC = 5.5 V<br>SND < VIN < VCC                                                                                                                  |                                                                         |                  |            | A11            | 1, | 2, 3       |                | ±10               | μ <b>Α</b>  |

| Output leakage current                    | I <sub>OZ</sub>  | V <sub>CC</sub> = GND <                                                                                                                         | 5.5 V<br>V <sub>OUT</sub> <u>&lt;</u> V <sub>CC</sub>                   | •                |            | A11            | 1, | 2, 3       |                | ±40               | μА          |

| Output short circuit current 1/           | Ios              | V <sub>CC</sub> = 5.5 V, V <sub>OUT</sub> = GND                                                                                                 |                                                                         |                  |            | A11            | 1, | 2, 3       | <br> <br>      | -85 I             | mA          |

| Operating supply current                  | I I CC1          | V <sub>CC</sub> = 5.5 V, f <sub>CP</sub> = 10 MHz 3/<br>  V <sub>IL</sub> = 0.8 V, V <sub>IH</sub> = 2.0 V<br>  CP = 50% duty cycle, OE = 2.0 V |                                                                         |                  |            | l 1            | 1, | 2, 3       |                | 85                | mA          |

| Quiescent supply current<br>TTL levels    | I <sub>CC2</sub> | V <sub>CC</sub> =                                                                                                                               | 5.5 ¥<br>0.8 ¥, ¥ <sub>TH</sub>                                         |                  |            |                | 1, | 2, 3       | <br> <br> <br> | 35                | mA          |

| Quiescent supply current<br>CMOS levels   | I <sub>CC3</sub> | V <sub>CC</sub> = !                                                                                                                             | ).4 V, V <sub>TH</sub>                                                  | = 3.8            | 5 V        | All            | 1, | 2, 3       |                | 30 I              | mA          |

| Input capacitance                         | CIN              |                                                                                                                                                 | 3.1c, V <sub>CC</sub>                                                   | = 5.0            | ٧          | A11            |    | 4          |                | 12                | pF          |

| Output capacitance                        | C <sub>OUT</sub> | -                                                                                                                                               |                                                                         |                  | i          | <br> <br>      |    | •          |                | 15                | рF          |

| Functional tests                          |                  | See 4.3                                                                                                                                         | 3.1d                                                                    |                  |            | A11            | 7, | 8          | ]<br>     <br> |                   |             |

| See footnotes at end of to                | able.            |                                                                                                                                                 |                                                                         |                  |            |                |    |            |                |                   |             |

| STANDARDIZED MILITARY DRAWING             |                  |                                                                                                                                                 | SIZE<br>A                                                               |                  |            |                |    | 5962-89517 |                |                   |             |

| DEFENSE ELECTRONICS SU<br>DAYTON, OHIO 49 |                  |                                                                                                                                                 | REVISION LEVEL SH                                                       |                  |            |                |    | IEET 4     |                |                   |             |

$\bigstar$  U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

TABLE I. Electrical performance characteristics - Continued. Test Symbo1 Conditions |Device| Group A | Limits Unit -55°C < T<sub>C</sub> < +125°C 4.5 V < V<sub>C</sub>C < 5.5 V unless otherwise specified type |subgroups] Min Max A setup time to positive See figure 5 2/ 19, 10, 11 ts1 01 45 ns edge of clock 4/ 02 35 A setup time to negative ts2 01 9, 10, 11 17 ns edge of clock 4/ 02 12 B (source) setup time to 01 19, 10, 11 45 ts3 ns positive edge of clock 4/ 02 35 B (source) setup time to 01 9, 10, 11 17 ts4 ns negative edge of clock 4/ 02 12 B (destination) setup time 01 | 9, 10, 11 17 ts5 ns to negative edge of clock 02 12 Data setup time to positive [9, 10, 11] 30 lts6 ns edge of clock 25 02  $C_n$  setup time to positive ts7 01 19, 10, 11 24 ns edge of clock 02 19  $I_0$ ,  $I_1$ ,  $I_2$  setup time ts8 01 19, 10, 11 37 ns to positive edge of clock 02 30 I3, I4, I5 setup time to positive edge of clock 19, 10, 11  $t_{S9}$ 01 40 ns 33 02 I<sub>6</sub>, I<sub>7</sub>, I<sub>8</sub> setup time 9, 10, 11 ts10 16 ns to negative edge of clock 02 12  ${\rm RAM_0}$  ,  ${\rm RAM_{15}}$  ,  ${\rm Q_0}$  ,  ${\rm Q_{15}}$  setup time to positive edge of  $t_{S11}$ 01 19, 10, 111 15 ns clock 02 13 A hold time from positive tH1 9, 10, 11 0 ns edge of clock 02 0 | See footnotes at end of table. **STANDARDIZED** SIZE Α **MILITARY DRAWING** 5962-89517 **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 5

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904

TABLE I. Electrical performance characteristics - Continued. Unit |Device| Group A | Limits Symbol Conditions Test | -55°C < T<sub>C</sub> < +125°C | 4.5 V < V<sub>CC</sub> < 5.5 V |unless otherwise specified type |subgroupsT Min | Max 19, 10, 11 3 See figure 5 2/ 01 A hold time from negative t<sub>H2</sub> ns edge of clock 5/ 3 02 B (source) hold time from 9, 10, 11 0 01 **t**H3 ns positive edge of clock 0 3 9, 10, 11 B (source) hold time from 01 ns tH4 negative edge of clock 5/ 3 02 B (destination) hold time 01 9, 10, 11 t<sub>H5</sub> from positive edge of clock! 9, 10, 11 Data hold time from positive | tH6 0 01 ns edge of clock 02 0  $C_n$  hold time from positive 9, 10, 11 0 01 ns **t**H7 edge of clock 0 02 I<sub>0</sub>, I<sub>1</sub>, I<sub>2</sub> hold time from positive edge of clock! 01 9, 10, 11 0 0 02 I<sub>3</sub>, I<sub>4</sub>, I<sub>5</sub> hold time from positive edge of clock 01 19, 10, 11 0 ns **≒**₩9 I<sub>6</sub>, I<sub>7</sub>, I<sub>8</sub> hold time

from positive edge of clock 01 19, 10, 11 0 ns tH10 02 0  ${\rm RAM}_0$  ,  ${\rm RAM}_{15}$  ,  ${\rm Q}_0$  ,  ${\rm Q}_{15}$  hold time from positive edge of 9, 10, 111 1 01 ns **H11** 02 1 clock 52 01 9, 10, 11 ns Delay from A to Y tp1 41 02 51 Delay from A to  $F_{15}$ tp2 01 |9, 10, 11|ns 02 40 See footnotes at end of table. SIZE STANDARDIZED Α 5962-89517 MILITARY DRAWING REVISION LEVEL **DEFENSE ELECTRONICS SUPPLY CENTER** SHEET DAYTON, OHIO 45444 6

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

TABLE I. Electrical performance characteristics - Continued. Test Symbo1 Conditions  $-55^{\circ}\text{C} < T_{\text{C}} < +125^{\circ}\text{C}$  4.5 V < V<sub>CC</sub> < 5.5 V unless otherwise specified |Device| Group A Limits Unit | type |subgroups] Min | Max Delay from A to  $C_n + 16$ See figure 5 2/ tp3 01 9, 10, 11 48 ns 02 38 Delay from A to G and P 19, 10, 11 tp4 01 45 ns 02 37 Delay from A to F = 048 9, 10, 11 tp5 01 ns 40 Delay from A to OVR tp6 01 19, 10, 11 46 ns 02 36 Delay from A to  $RAM_0$ ,  $RAM_{15}$ 9, 10, 11 tp7 01 43 ns 02 36 Delay from B to Y 19, 10, 11 52 tp8 01 ns 02 41 Delay from B to F<sub>15</sub> 01 9, 10, 11 51 tp9 02 40 Delay from B to  $C_n + 16$ 9, 10, 11 01 48 tp10 ns Delay from B to G and P 9, 10, 11 01 45 tp11 37 Delay from B to F = 09, 10, 11 tp12 48 ns 40 Delay from B to OVR 01 tp13 19, 10, 11 46 ns 36 Delay from B to  $RAM_0$ ,  $RAM_{15}$ 43 9, 10, 11 ns 36 02 See footnotes at end of table. **STANDARDIZED** SIZE Α 5962-89517 **MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 7

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

TABLE I. Electrical performance characteristics - Continued. Conditions -55°C < T<sub>C</sub> < +125°C 4.5 V < V<sub>CC</sub> < 5.5 V unless otherwise specified Symbol Devicel Group A Limits Unit Test type |subgroupsT Min Max 9, 10, 11 37 See figure 5 2/ 01 ns Delay from data to Y tp15 02 31 19, 10, 11 36 01 Delay from data to F<sub>15</sub> ns tp16 02 31 Delay from data to  $C_n + 16$ 01 19, 10, 11 36 ns tP17 29 02 Delay from data to  $\overline{\textbf{G}}$  and  $\overline{\textbf{P}}$ 01 9, 10, 11 32 ns tp18 02 28 9, 10, 11 40 01 ns Delay from data to F = 0tp19 33 02 9, 10, 11 32 Delay from data to OVR 01 ns tp20 23 02 Delay from data to  $RAM_0$ , 01 9, 10, 11 35 ns tP21 RAM<sub>15</sub> 02 30 9, 10, 11 30 Delay from C<sub>n</sub> to Y 01 ns tp22 25 9, 10, 11 29 Delay from C<sub>n</sub> to F<sub>15</sub> 01 ns tp23 24 02 9, 10, 11 27 Delay from  $C_n$  to  $C_{n+16}$ 01 ns tp 24 23 02 9, 10, 11 29 01 ns Delay from  $C_n$  to F = 0tp26 24 Delay from Cn to OVR 01 9, 10, 11 27 ns tP27 02 23 See footnotes at end of table. SIZE STANDARDIZED Α 5962-89517 **MILITARY DRAWING REVISION LEVEL DEFENSE ELECTRONICS SUPPLY CENTER** SHEET DAYTON, OHIO 45444 8

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904

TABLE I. Electrical performance characteristics - Continued. Test Symbol |Device| Group A Conditions Limits Unit | -55°C < T<sub>C</sub> < +125°C | | 4.5 V < V<sub>CC</sub> < 5.5 V | | unless otherwise specified type |subgroups] Min | Max Delay from  $C_n$  to  $RAM_0$ , See figure 5 2/ 01 19, 10, 11 31 tp28 ns RAM<sub>15</sub> 02 26 Delay from  $I_0$ ,  $I_1$ ,  $I_2$  to Y tp29 01 |9, 10, 11| 44 ns 02 36 Delay from  $I_0$ ,  $I_1$ ,  $I_2$  to  $F_{15}$ tp30 01 9, 10, 11 43 ns 02 35 Delay from  $I_0$ ,  $I_1$ ,  $I_2$  to 01 | 9, 10, 11 | 41 tp31 ns <sup>C</sup>n + 16 02 33 Delay from  $\mathbf{I}_0,~\mathbf{I}_1,~\mathbf{I}_2$  to  $\overline{\mathbf{G}}$  and  $\overline{\mathbf{P}}$ tp32 01 | 9, 10, 11 38 ns 02 31 Delay from  $I_0$ ,  $I_1$ ,  $I_2$  to 01 19, 10, 11 46 tp33 ns 02 38 Delay from  $I_0$ ,  $I_1$ ,  $I_2$  to OVR 01 | 9, 10, 11 38 tp34 ns 02 29 Delay from  ${\rm I}_0,~{\rm I}_1,~{\rm I}_2$  to  ${\rm RAM}_0,~{\rm RAM}_{15}$ 9, 10, 11 tp35 01 38 ns 02 30 Delay from  $I_3$ ,  $I_4$ ,  $I_5$  to Y01 19, 10, 111 48 tp36 ns 38 02 Delay from I3, I4, I5 to F15 | tp37 01 19, 10, 11 47 ns 02 37 Delay from I3, I4, I5 to 9, 10, 11 46 tp38 01 ns  $C_n + 16$ 02 37 Delay from I3, I4, I5 to tp39 19, 10, 11 01 38 ns G and P 31 See footnotes at end of table. **STANDARDIZED** SIZE Α 5962-89517 **MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 9

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904

TABLE I. Electrical performance characteristics - Continued. Conditions  $| -55^{\circ}C < T_{C} \le +125^{\circ}C$   $| 4.5 \text{ V} \le \text{V}_{CC} \le 5.5 \text{ V}$  | unless otherwise specified Test Symbol Device | Group A Limits Unit type |subgroups Min Max Delay from I3, I4, I5 to **tP40** See figure 5 2/ 01 9, 10, 11 45 ns 38 02 Delay from I3, I4, I5 to OVR 19, 10, 11 45 tp41 01 ns 02 36 9, 10, 11 Delay from I3, I4, I5 to 01 41 tp42 ns RAMO, RAM15 02 33 Delay from I6, I7, I8 to Y 01 9, 10, 11 24 tp43 ns 02 21 Delay from  $I_6$ ,  $I_7$ ,  $I_8$  to  $RAM_0$ ,  $RAM_{15}$ 19, 10, 11 28 01 ns tp44 02 24 Delay from I<sub>6</sub>, I<sub>7</sub>, I<sub>8</sub> to 01 19, 10, 11 28 ns tp45 Q<sub>0</sub>, Q<sub>15</sub> 02 24 Delay from A (I = 2XX) to Y 01 9, 10, 11 33 ns tp46 28 02 Delay from CP to Y 9, 10, 11 44 tp47 01 ns 35 02 Delay from CP to  $F_{15}$ [9, 10, 11] 43 tp48 01 ns 02 34 Delay from CP to  $C_{n} + 16$ 42 **tp49** 01 19, 10, 11 ns 02 34 Delay from CP to G and P 01 9, 10, 11 37 ns ₹P50 30 02 Delay from CP to F = 001 9, 10, 11 40 tp51 ns 34 02 See footnotes at end of table. **STANDARDIZED** SIZE A 5962-89517 **MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444 10

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

| Test                                              | <br> Symbol           | Conditions                                                                                                                      | Device | Group A             | Limi   | ts  | Unit       |

|---------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|--------|---------------------|--------|-----|------------|

|                                                   |                       | Conditions<br>  $-55$ °C $<$ T <sub>C</sub> $<$ +125°C<br>  4.5 Y $<$ Y <sub>CC</sub> $<$ 5.5 Y<br>  unless otherwise specified | "      | subgroups <br> <br> | Min    | Мах | [<br> <br> |

| Delay from CP to OVR                              | tp52                  | See figure 5 <u>2</u> /                                                                                                         | 01     | 9, 10, 11           |        | 38  | ns         |

|                                                   | <br>                  | <u> </u>                                                                                                                        | 02     |                     |        | 28  | <u> </u>   |

| Delay from CP to RAMO, RAM15                      | tp53                  | Ţ                                                                                                                               | 01     | 9, 10, 11           |        | 37  | ns         |

| · -                                               |                       | <br>                                                                                                                            | 02     |                     |        | 30  |            |

| Delay from CP to Q <sub>0</sub> , Q <sub>15</sub> | tp54                  | T<br>                                                                                                                           | 01     | 9, 10, 11           |        | 25  | ns         |

|                                                   | ' ' '                 |                                                                                                                                 | 02     | <br>                |        | 21  | <u> </u>   |

| Delay from OE to Y enable                         | tpzL                  | T<br>I                                                                                                                          | 01     | <br> 9, 10, 11      |        | 23  | ns         |

| 6/ 1/                                             | tPZH                  |                                                                                                                                 | 02     |                     |        | 20  |            |

| Delay from OE to Y disable                        | <br> tpLZ             | T<br>I                                                                                                                          | 01     | 9, 10, 11           |        | 20  | ns         |

| 6/ 1/                                             | tPHZ                  |                                                                                                                                 | 02     |                     |        | 17  |            |

| finimum clock low time                            | tpwL                  | T<br>I                                                                                                                          | 01     | 9, 10, 11           |        | 28  | ns         |

|                                                   |                       |                                                                                                                                 | 02     | ` <br>  <u></u>     | ļ<br>! | 23  |            |

| Minimum clock high time                           | <br> tpwH             | Ī                                                                                                                               | 01     | 9, 10, 11           |        | 17  | ns         |

| Triting of South As you as a second               | 1                     |                                                                                                                                 | 02     | 1<br>1              |        | 12  | <u> </u>   |

| wining clock period                               | i<br>It <sub>CP</sub> | Ť                                                                                                                               | 01     | 9, 10, 11           | 1      | 45  | ns         |

| Minimum clock period                              | i CP                  |                                                                                                                                 | 02     |                     | i      | 35  |            |

For test purposes, not more than one output should be shorted at one time. Duration of the short circuit should not exceed  $\bf 1$  second.

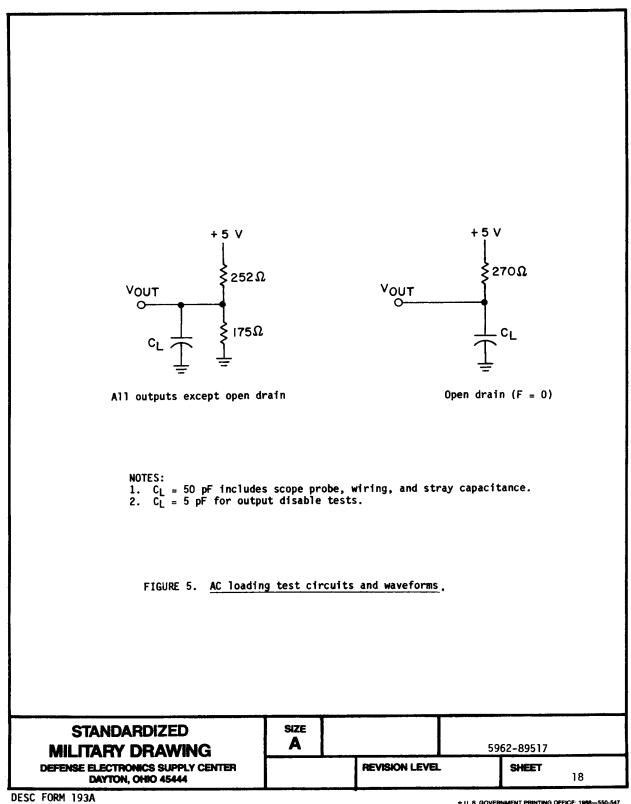

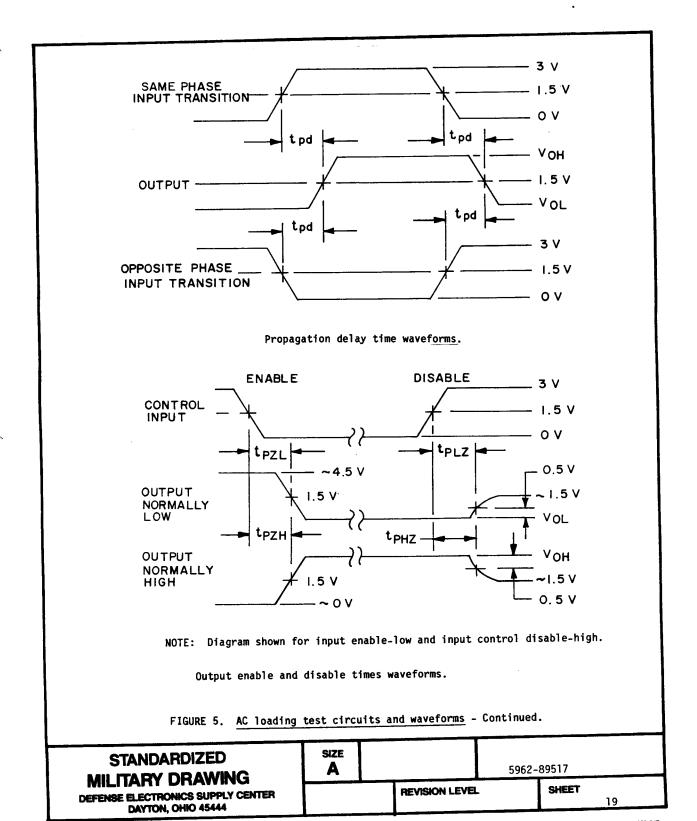

AC parameters are tested using input rise and fall times of 5 ns and input pulse levels of GND to 3.0 V. Both input and output timing reference levels are 1.5 V, and the load is shown on figure 5.

Two quiescent figures are given for different input voltage ranges. To calculate ICC at any given clock frequency, use ICC2 or ICC3 + ICC(ac), where ICC(ac) =  $(5 \text{ mA/MHz}) \times \text{clock}$

frequency. The setup time prior to the clock low to high transition is to allow time for data to be accessed, passed through the ALU, and returned to the RAM. It includes all the time from stable A and B addresses to the clock low to high transition, regardless of when the clock high to low

transition occurs. 5/ Source addresses must be stable prior to the clock high to low transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock low time.

This parameter if not tested, shall be guaranteed to the limits specified in table I. Output disable tests performed with  $C_L=5$  pF and measured to 0.5 V change of output voltage

level.

#### SIZE STANDARDIZED 5962-89517 Α **MILITARY DRAWING REVISION LEVEL** SHEET **DEFENSE ELECTRONICS SUPPLY CENTER** DAYTON, OHIO 45444

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

№ U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

| Symbol         | Inc           | hes            | <br>  Millin  | neters | <br>             |

|----------------|---------------|----------------|---------------|--------|------------------|

|                | <br>  Min<br> | <br>  Max<br>  | <br>  Min<br> | Max    | <br> Notes  <br> |

| A              |               | .225           | <br>          | 5.72   | l 1              |

| Ь              | .014          | .023           | <br>  0.36    | 0.58   | 8                |

| ь1             | .038          | .065           | 0.96          | 1.65   | 2,8              |

| С              | .008          | .015           | 0.20          | 0.38   | 8                |

| D              |               | 3.24           |               | 82.30  | 4                |

| E              | .780          | .820           | 19.81         | 20.83  | 4                |

| <br>  E1<br>   | .870          | <br>  .920<br> | 22.10         | 23.37  | 7                |

| E2             | .600          |                | 15.24         |        |                  |

| <br>  E3  <br> | .050          |                | 1.27          |        |                  |

| Symbol | I Inc      | hes  | !<br>  Milli:<br> | <u> </u><br> |                 |  |

|--------|------------|------|-------------------|--------------|-----------------|--|

|        | Min        | Max  | Min               | Max          | T<br> Notes<br> |  |

| е      | 1 .100 BSC |      | 2.54              | 2.54 BSC     |                 |  |

| L      | 1 .125     | .200 | <br>  3.18        | 5.08         | 1               |  |

| L1     | 1 .150     | <br> | 3.81              |              |                 |  |

| Q      | .080       | .110 | 2.03              | 2.79         | 3               |  |

| Q1     | .020       |      | .51               |              |                 |  |

| S      |            | .100 |                   | 2.54         | 6               |  |

| \$1    | .005       |      | 0.13              |              | 6               |  |

| a l    | 0°         | 15°  | 0°                | 15°          |                 |  |

- 1. Index area: A notch or a pin one identification mark shall be located adjacent to pin one and shall be located within the shaded area shown. The manufacturer's identification shall not be used as a pin one identification mark.

- The minimum limit for dimension b1 may be .023 (0.58 mm) for lead numbers 1, 32, 33, and 64 only.

- Dimension Q shall be measured from the seating plane to the base plane. 3.

- This dimension allows for off-center lid, meniscus, and glass overrun.

- The basic pin spacing is .100 (2.54 mm) between centerlines. Each lead centerline shall be located within +.010 (0.25 mm) of its exact longitudinal position relative to leads 1 and 64.

Applies to all four corners (lead numbers 1, 32, 33, and 64) shall apply.

Lead center when a is 0°. E1 shall be measured at the centerline of the leads.

All leads: Increase maximum limit by .003 (0.08 mm) measured at the center of the flat, when

- lead finish A or B is applied.

- Sixty-two. 10. If this configuration is used, no organic or polymeric materials shall be molded to the bottom of the package to cover the leads.

FIGURE 2. Case X (64-lead, 3.240" x 0.920" x 0.225"), dual-in-line package - Continued.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962 | 2-89517 |    |

|------------------------------------------------------|-----------|----------------|------|---------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL |      | SHEET   | 14 |

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988\_550.547

Device Device types A11 A11 types Case outlines U X Y Z U outlines X Y Z Terminal Terminal number Terminal symbol Terminal symbol number BO | I4 | I5 D<sub>1</sub> i RAMO OVR 14 35 Y13 113 2 B<sub>1</sub> 36 **ICP** ICn + 16 117 1Y12 |B2 P 3 Q<sub>15</sub> Dз G Вз 118 37 Y11 İG RAM<sub>15</sub> IB3 ICP D4 İΡ 38 IO !Y10 IČ IOVR و۲۱ ĺΑ3 39 40 5 İB<sub>1</sub> 15 |I1 |I2 16 RAMO 67 A2 D6 114 BO DO Y8 GND F<sub>15</sub> |Y<sub>15</sub> |Y<sub>14</sub> ic'n IF ≈ 100 41 8 | I 6 | I 7 A<sub>0</sub> D<sub>15</sub> NC NC 42 |015 |RAM<sub>15</sub> D<sub>1</sub> 0 NC 9 ĺΥo 43 GND , I<sub>8</sub> 10 NC VCC D3 D4 Y<sub>1</sub> Y<sub>2</sub> Y<sub>3</sub> 44 A<sub>3</sub> OE D8 D9 11 I 0 I 1 I 2 D<sub>14</sub> D<sub>13</sub> D<sub>12</sub> A2 A1 45 12 Y<sub>11</sub> D<sub>5</sub> 46 |D10 13 Y10 47 D6 D7 Y5 Y4 Y3 Y2 F = 0 A<sub>0</sub> D10 D11 D12 D13 D11 D10 D9 14 15 D<sub>15</sub> D<sub>14</sub> D<sub>13</sub> Y9 Y8 GND Y5 Y6 Y7 48 49 VCC D8 16 50 D12 D11 D10 ŌĒ 17 |Y1 |Y2 |Y3 |Y4 |Y5 |Y6 |Y7 D<sub>8</sub> D14 51 ŌĒ Do D<sub>15</sub> 18 19 IVCC D<sub>10</sub> Y<sub>0</sub> |F = 0 |C<sub>n</sub> 1Y7 52 GND Y6 Y5 Y4 Y4 Y3 A0 A1 A2 A3 RAM15 D7 D11 53 GND 20 54 55 D12 D13 D14 1Y8 21 22 23 D5 D4 D3 D8 VCC ID7 |Y10 56  $|I_1|$ 57 D15 |Y<sub>11</sub> 110 D2 D1 D0 NC ŌΕ Y<sub>1</sub> 24 Q<sub>15</sub> Y12 58 D<sub>6</sub> Ao 18 GND 25 Î3 I4 FO. 59 D5 D4 D3 A1 A2 A3 Y<sub>13</sub> 17 Ϋ́8 Ϋ́9 26 \_ = 0 Y14 NC 60 16 Cn 15 27 61 Qo İΥ<sub>10</sub> 28 P 12 B<sub>0</sub> 62 RAM<sub>15</sub> D2 Y<sub>15</sub> IRAMO |Y11 |Y12  $|_{D_1}$ G 29 I 1 I 0 B<sub>1</sub> B2 Q<sub>15</sub> F<sub>15</sub> OVR 63 CP 30 Cn + 16 13 Вз 64 Dō 31 OVR 18 Y<sub>13</sub> Вз 65 C<sub>n</sub> + 16 B<sub>2</sub> 1Y14 |F<sub>15</sub> 32 İCP 17 66 Ğ B<sub>1</sub> ---Y F 15 ram<sub>o</sub> 33 Y<sub>15</sub> I<sub>6</sub> P BO 67 34 Y<sub>14</sub> Qo 68  $Q_0$ 15 D<sub>O</sub> NC = no connection FIGURE 3. Terminal connections. **STANDARDIZED** SIZE A **MILITARY DRAWING** 5962-89517 DEFENSE ELECTRONICS SUPPLY CENTER **REVISION LEVEL** SHEET DAYTON, OHIO 45444

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

**☆** U. 8. GOVERNMENT PRINTING OFFICE: 1988—550-547

± U. S. GOVERNMENT PRINTING OFFICE: 1988--550-547

**★ U. 8. GOVERNMENT PRINTING OFFICE: 1988—550-547**

± U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- Test condition C or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method  $\frac{5005}{5005}$  of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{IN}/C_{OUT}$  measurement) shall be measured only for the initial test and after process or design changes which may affect input/output capacitance. A minimum sample size of five devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall verify the instruction set. The instruction set forms a part of the of the vendor's test tape and shall be maintained and available from the approved sources of supply.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test, method 1005 of MIL-STD-883 conditions:

- (1) Test condition C or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED MILITARY DRAWING                        | size<br><b>A</b> |                | 5962-89517 |  |

|------------------------------------------------------|------------------|----------------|------------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET 20   |  |

**★ U. S. GOVERNMENT PRINTING OFFICE: 1988-549-904**

# TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                          | <br>  Subgroups<br>  (per method<br>  5005, table I) |

|------------------------------------------------------------------------|------------------------------------------------------|

| Interim electrical parameters<br>  (method 5004)                       |                                                      |

| <br>  Final electrical test parameters<br>  (method 5004)              | 1*,2,3,7,8,9                                         |

| Group A test requirements<br>  (method 5005)                           | 1,2,3,4,7,8,<br>9,10,11                              |

| Groups C and D end-point<br>  electrical parameters<br>  (method 5005) | 1,2,3                                                |

<sup>\*</sup> PDA applies to subgroups 1 and 7.

### 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

#### 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-89517 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET 21   |

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988—549-904

| 6.4 Pin descrip                     | tions.                 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |                  |                                                   |                           |                                                                                            |  |  |

|-------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------|--|--|

| Mnemonic                            | Туре                   |                                                                                                                                                                                                                                                                                                                                | Descr                                                                                                                                                                                                                         | iption           | <u>.</u>                                          |                           |                                                                                            |  |  |

| A <sub>O</sub> - A <sub>3</sub>     | I                      | RAM address<br>in the stac                                                                                                                                                                                                                                                                                                     | A: Thes                                                                                                                                                                                                                       | e 4 ac<br>put it | dress lines se<br>s contents on                   | elect one o<br>the (inter | of the 16 registers                                                                        |  |  |

| B <sub>O</sub> - B <sub>3</sub>     | I                      | in the stac                                                                                                                                                                                                                                                                                                                    | RAM address B: These 4 address lines select one of the 16 registers in the stack and output its contents on the (internal) B port. This can also be the destination address when data is written back into the register file. |                  |                                                   |                           |                                                                                            |  |  |

| I <sub>0</sub> - I <sub>8</sub>     | İ                      | sources (In                                                                                                                                                                                                                                                                                                                    | $\{1, I_2\}$                                                                                                                                                                                                                  | , the<br>s to b  | operation to b<br>e written back                  | e performe                | lect the ALU data<br>d (I3, I4,<br>er the Q register                                       |  |  |

| D <sub>0</sub> - D <sub>15</sub>    | 1                      | Direct data by the $I_0$ ,                                                                                                                                                                                                                                                                                                     | input: 1                                                                                                                                                                                                                      | These<br>nes as  | are 16 data in<br>inputs to the                   | put lines<br>ALU.         | that may be selected                                                                       |  |  |

| Y <sub>0</sub> - Y <sub>15</sub>    | 0                      | enabled, ou                                                                                                                                                                                                                                                                                                                    | itput eithi                                                                                                                                                                                                                   | er the           | ree-state data<br>output of the<br>e code on the  | ALU or th                 | nes that, when<br>e data in the A<br>lines.                                                |  |  |

| ŌE                                  | I                      | Y <sub>15</sub> outputs                                                                                                                                                                                                                                                                                                        | . When the                                                                                                                                                                                                                    | nis si           | active low in<br>gnal is low th<br>n the high imp | e Y output                | ontrols the Y <sub>O</sub> -<br>s are enabled and<br>te.                                   |  |  |

| СР                                  | I                      | Clock input: The low level of CP is used to write data to the RAM register file. A high level of CP writes data from the dual port RAM to the A and B latches. The operation of the Q register is similar; data is entered into the master latch on the low level of CP and transferred from master to slave during CP = high. |                                                                                                                                                                                                                               |                  |                                                   |                           |                                                                                            |  |  |

| Q <sub>15</sub> , RAM <sub>15</sub> | 1/0                    | These two 1<br>I7, I8 inpu<br>the TTL com                                                                                                                                                                                                                                                                                      | ts. They                                                                                                                                                                                                                      | are t            | ctional and ar<br>nree-state out<br>outs.         | e controll<br>put driver  | ed by the I <sub>6</sub> ,<br>s connected to                                               |  |  |

| ,                                   |                        | indicates a<br>enabled and                                                                                                                                                                                                                                                                                                     | left shif<br>the MSB o                                                                                                                                                                                                        | ft (UP<br>of the | y register is                                     | he three-si<br>output on  | 6, I7, I8<br>tate outputs are<br>the Q <sub>15</sub> pin and<br>t on the RAM <sub>15</sub> |  |  |

|                                     |                        | Input mode:<br>the pins are<br>respectively                                                                                                                                                                                                                                                                                    | e the data                                                                                                                                                                                                                    | dest             | nation code in<br>s to the MSB                    | ndicates a<br>of the Q re | right shift (down),<br>egister and the RAM,                                                |  |  |

| Q <sub>O</sub> , RAM <sub>O</sub>   | I/0                    | These two li<br>and RAM <sub>15</sub> li<br>RAM.                                                                                                                                                                                                                                                                               | ines are b<br>Ines, exce                                                                                                                                                                                                      | idired<br>pt tha | tional and fu<br>t they are the                   | nction simi<br>ELSB of th | ilar to the Q <sub>15</sub><br>ne Q register and                                           |  |  |

| c <sub>n</sub>                      | I                      | Carry in: 1                                                                                                                                                                                                                                                                                                                    | The carry                                                                                                                                                                                                                     | into t           | he internal Al                                    | _U.                       |                                                                                            |  |  |

| C <sub>n</sub> + 16                 | 0                      | Carry out:                                                                                                                                                                                                                                                                                                                     | The carry                                                                                                                                                                                                                     | out o            | f the internal                                    | I ALU.                    |                                                                                            |  |  |

| ট, চ                                | 0                      | Carry genera<br>outputs of t                                                                                                                                                                                                                                                                                                   | ate, carry<br>the ALU.                                                                                                                                                                                                        | propa            | gate: The car                                     | rry generat               | e and propagate                                                                            |  |  |

| STANDA                              | RDIZEC                 |                                                                                                                                                                                                                                                                                                                                | SIZE                                                                                                                                                                                                                          |                  |                                                   |                           |                                                                                            |  |  |

| MILITARY                            | DRAW                   | NG                                                                                                                                                                                                                                                                                                                             | Α                                                                                                                                                                                                                             | L                |                                                   | 5962                      | -89517                                                                                     |  |  |

| DEFENSE ELECTRO<br>DAYTON,          | NICS SUPP<br>OHIO 4544 |                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                               |                  | REVISION LEVEL                                    | •                         | SHEET<br>22                                                                                |  |  |

★ U. S. GOVERNMENT PRINTING OFFICE: 1988--549-904

| Mnemonic        | Туре | Description                                                                                                                                                              |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVR             | 0    | Overflow: This pin indicates when the result of the ALU operation exceeds the capacity of the machines two's complement number range. It is valid only for the sign bit. |

| F = 0           | 0    | Zero detect: Open drain output that goes high if the data on the ALU outputs ( $F_0$ - $F_{15}$ ) are all low.                                                           |

| F <sub>15</sub> | 0    | Sign: The most significant bit of the ALU output.                                                                                                                        |

6.5 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5 herein) has been submitted to DESC-ECS.

| _ |                              |                              |                                             |

|---|------------------------------|------------------------------|---------------------------------------------|

|   | Military drawing part number | Vendor<br>  CAGE<br>  number | Vendor<br>similar part<br>number <u>1</u> / |

| I | 5962-8951701XX               | <br>  65786                  | CY7C9101-45DMB                              |

| L | 5962-8951701YX               | <br>  65786                  | CY7C9101-45LMB                              |

| L | 5962-8951701ZX               | 65786                        | CY7C9101-45GMB                              |

|   | 5962-8951701UX               | 65786                        | CY7C9101-45FMB                              |

| T | 5962-8951702XX               | <br>  65786                  | CY7C9101-35DMB                              |

| T | 5962-8951702YX               | 65786                        | CY7C9101-35LMB                              |

| T | 5962-8951702ZX               | 65786                        | CY7C9101-35GMB                              |

| Ī | 5962-8951702UX               | 65786                        | CY7C9101-35FMB                              |

1/ Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

Vendor CAGE number

65786

Vendor name and address

Cypress Semiconductor Corporation 3901 N. First Street San Jose, CA 95134

# STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

SIZE A 5962-89517

REVISION LEVEL SHEET 23

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1968---549-904