## Am27LV020

Advanced Micro **Devices**

## 262.144 x 8-Bit CMOS Low Voltage, One Time **Programmable Memory**

#### DISTINCTIVE CHARACTERISTICS

- 3.3 V  $\pm$  0.3 V V<sub>CC</sub> read operation

- High performance at 3.3 V<sub>CC</sub>

- 200 ns maximum access time

- Low power consumption

- 90 µW maximum standby power

- 25 uA maximum standby current

- 54 mW maximum power at 5 MHz

- 15 mA maximum current at 5 MHz

- No data retention power

- Industry standard packaging

- 32-pin PLCC

- 32-pin Thin Small Outline Package

- 32-pin Plastic DIP

- Program voltage 12.75 ± .25 V

- Latch-up protected to 100 mA from -1 V to Vcc +1 V

- Flashrite<sup>™</sup> programming

- 10 us typical byte-program

- Less than 3 seconds typical chip program

- Advanced CMOS memory technology

- Low cost single transistor memory cell

#### **GENERAL DESCRIPTION**

The Am27LV020 device is a low voltage, low power. CMOS 256K x 8 One Time Programmable (OTP) nonvolatile memory.

Maximum power consumption in standby mode is 90 µW. If the device is constantly accessed at 5 MHz, then maximum power consumption increases to 54 mW. These power ratings are significantly lower than typical EPROM devices. Since power consumption is proportional to voltage squared, 3.3 V devices typically consume at least 57% less power than 5.0 V devices.

The Am27LV020 typically draws 10 mA of current enabling 200 ns read operations. Typical power consumption under these conditions equals 33 mW. This "high performance", low voltage device is ideal for BIOS storage in portable computing applications and control code storage in portable digital cellular phone applications. Low voltage CMOS designs require less operating power and hence dramatically increases the usable operating life of battery powered systems.

The Am27LV020 is packaged in a 32-pin PLCC, Plastic DIP and Thin Small Outline Package (TSOP) versions. It is designed to be programmed in standard EPROM programmers.

The highest degree of latch-up protection is achieved with AMD's proprietary non-epi process. Latch-up protection is provided for stresses up to 100 milliamps on address and data pins from -1 V to Vcc+1 V.

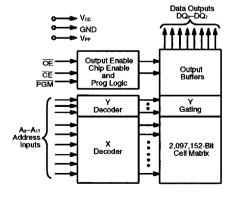

#### **BLOCK DIAGRAM**

11507-001B

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

Rev. A Amendment /0 Publication #: 16357 Issue Date: July 1992

## PRODUCT SELECTOR GUIDE

| Family Part No.      |      | Am27LV020 |      |

|----------------------|------|-----------|------|

| Ordering Part No:    |      |           |      |

| ±0.3 V Vcc Tolerance | -200 | -250      | -300 |

| Max Access Time (ns) | 200  | 250       | 300  |

| CE (E) Access (ns)   | 200  | 250       | 300  |

| OE (G) Access (ns)   | 75   | 100       | 100  |

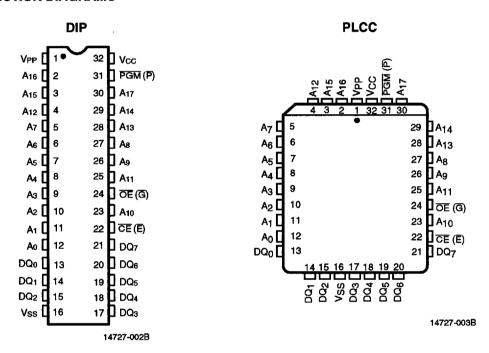

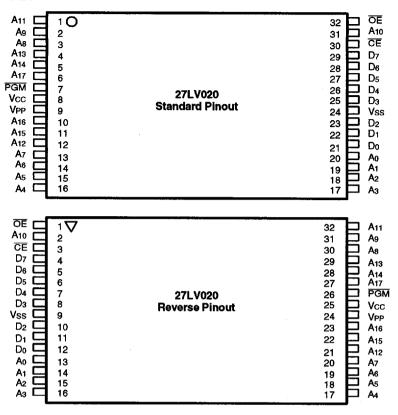

## **CONNECTION DIAGRAMS**

Note: Pin 1 is marked for orientation.

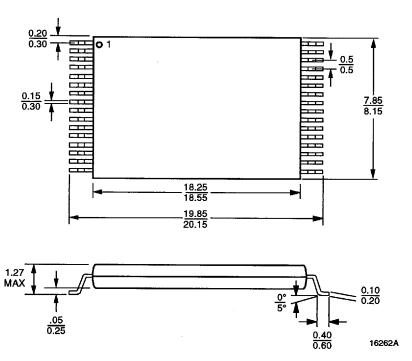

## **TSOP PACKAGES**

## 27LV020 256K x 8 OTP in 32 Lead TSOP

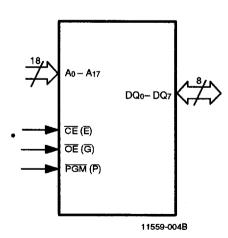

## **LOGIC SYMBOL**

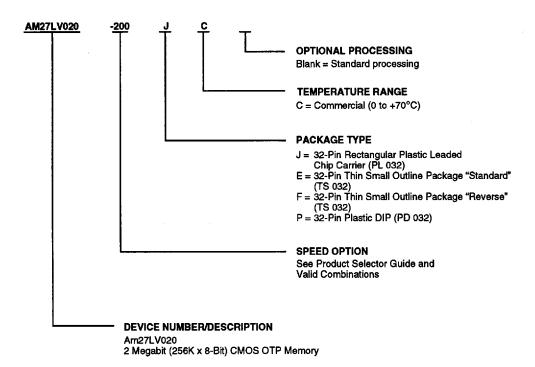

## ORDERING INFORMATION

### Standard Products

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of these elements:

| Valid Combinations |                |  |  |  |  |  |

|--------------------|----------------|--|--|--|--|--|

| Am27LV020-200      |                |  |  |  |  |  |

| Am27LV020-250      | JC, EC, FC, PC |  |  |  |  |  |

| Am27LV020-300      |                |  |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

AMD

## PIN DESCRIPTION

$V_{PP}$

Power supply for programming.

Vcc

Power supply for device operation. (Read:  $V_{CC} = 3.3 V \pm 0.3 V$ , Program:  $V_{CC} = 5.0 V \pm 10\%$ )

Vss

Ground

NC

No Connect-corresponding pin is not connected internally to the die.

$A_0 - A_{17}$

Address Inputs for memory locations.

DQ<sub>0</sub>-DQ<sub>7</sub>

Data Inputs during memory program cycles. Internal latches hold data during program cycles. Data Outputs during memory read cycles.

CE (E)

The Chip Enable active low input activates the chip's control logic and input buffers. Chip Enable high will deselect the device and operates the chip in stand-by mode.

OE (G)

The Output Enable active low input gates the outputs of the device through the data buffers during memory read cycles.

PGM (P)

The Program Enable active low input controls the program function of the memory array.

### **BASIC PRINCIPLES**

The Am27LV020 supports programming operations using a fixed 12.75  $\pm$  0.25 V power supply.

## **Read Only Memory**

Without high V<sub>PP</sub> voltage, the Am27LV020 functions as a read only memory and operates like a standard EPROM. The control inputs still manage traditional read, standby, output disable, and Auto select modes.

## **Programming**

These devices are programmable on standard PROM programmer equipment.

Please contact Advanced Micro Devices for PROM programmer information.

## **FUNCTIONAL DESCRIPTION**

## **Description Of User Modes**

Table 1. Am27LV020 User Bus Operations

| Operation  Read |                                  | CE<br>(E) |     |                 | V <sub>PP</sub><br>(Note 1) | Ao  | As                          | VO            |

|-----------------|----------------------------------|-----------|-----|-----------------|-----------------------------|-----|-----------------------------|---------------|

|                 |                                  | VIL       | VIL | Х               | VPPL                        | Αo  | A <sub>9</sub>              | Dour          |

|                 | Standby                          | ViH       | Х   | Х               | VPPL                        | Х   | Х                           | HIGH Z        |

|                 | Output Disable                   | ViL       | ViH | ViH             | VPPL                        | Х   | X                           | HIGH Z        |

| Read-Only       | Auto-select Manufacturer<br>Code | VIL       | VıL | V <sub>IH</sub> | VPPL                        | VIL | V <sub>ID</sub><br>(Note 2) | CODE<br>(01H) |

|                 | Auto-select Device Code          | VIL       | VIL | ViH             | VPPL                        | ViH | V <sub>ID</sub><br>(Note 2) | CODE<br>(2CH) |

#### Legend:

X = Don't care, where Don't Care is either  $V_{IL}$  or  $V_{IH}$  levels,  $V_{PPL} = V_{PP} < V_{CC} + 2V$ , See DC Characteristics for voltage levels of  $V_{PPH}$ ,  $0V < An < V_{CC} + 2V$ , (normal CMOS input levels, where n = 0 or 9).

#### Notes:

- VPPL may be grounded, connected with a resistor to ground, or ≤ VCC +2.0 V. VPPH is the programming voltage specified

for the device. Refer to the DC characteristics. When VPP = VPPL, memory contents can be read but not written.

- 2.  $11.5 \le \text{ViD} \le 13.0 \text{ V}, \text{VCC} = 5.0 \text{ V} \pm 10\%$

### **READ ONLY MODE**

$V_{cc} = 3.3 \text{ V} \pm 0.3 \text{ V}$

#### Read

The Am27LV020 functions as a read only memory. The Am27LV020 has two control functions. Both must be satisfied in order to output data. CEcontrols power to the device. This pin should be used for specific device selection. OE controls the device outputs and should be used to gate data to the output pins if a device is selected.

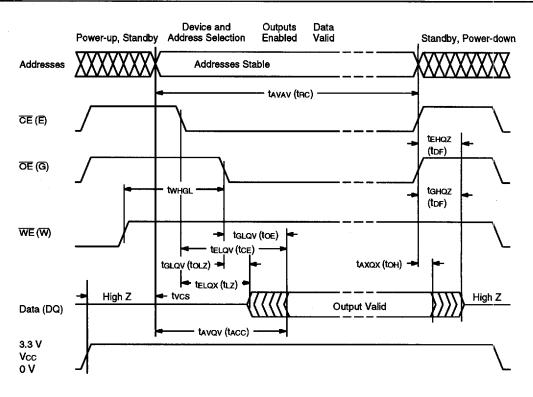

Address access time  $t_{ACC}$  is equal to the delay from stable addresses to valid output data. The chip enable access time  $t_{CE}$  is the delay from stable addresses and stable  $\overline{CE}$  to valid data at the output pins. The output enable access time is the delay from the falling edge of  $\overline{OE}$  to valid data at the output pins (assuming the addresses have been stable at least  $t_{ACC} - t_{OE}$ ).

#### Standby Mode

The Am27LV020 has one standby mode. The CMOS standby mode ( $\overline{\text{CE}}$  input held at  $V_{\text{CC}} \pm 0.5V$ ), consumes less than 25  $\mu$ A of current. When in the standby mode the outputs are in a high impedance state, independent of the  $\overline{\text{OE}}$  input.

If the device is deselected during programming, or program verification, the device will draw active current until the operation is terminated.

#### **Output Disable**

Output from the device is disabled when  $\overline{OE}$  is at a logic high level. When disabled, output pins are in a high impedance state.

#### **Auto Select**

The Am27LV020 can be programmed in a standard PROM programmer.

The Auto select mode allows the reading out of a binary code from the device that will identify its manufacturer and type. This mode is intended for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm.

## Programming In A PROM Programmer

To activate this mode, the programming equipment must force  $V_{\rm ID}$  (11.5V to 13.0V) on address  $A_{\rm 9}$ . Two identifier bytes may then be sequenced from the device outputs by toggling address  $A_{\rm 0}$  from  $V_{\rm IL}$  to  $V_{\rm IH}$ . All other address lines must be held at  $V_{\rm IL}$ , and  $V_{\rm PP}$  must be less than or equal to  $V_{\rm CC} + 2.0V$  while using this Auto select mode. Byte 0 ( $A_{\rm 0} = V_{\rm IL}$ ) represents the manufacturer code and byte 1 ( $A_{\rm 0} = V_{\rm IH}$ ) the device identifier code. For the Am27LV020 these two bytes are given in the table below. All identifiers for manufacturer and device codes will exhibit odd parity with the MSB (DQ7) defined as the parity bit.

Table 2. Am27LV020 Auto Select Code

| Туре              | Ao  | Code<br>(HEX) | DQ <sub>7</sub> | DQ <sub>6</sub> | DQ <sub>5</sub> | DQ4 | DQ <sub>3</sub> | DQ <sub>2</sub> | DQ <sub>1</sub> | DQ₀ |

|-------------------|-----|---------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----|

| Manufacturer Code | VIL | 01            | 0               | 0               | 0               | 0   | 0               | 0               | 0               | 1   |

| Device Code       | ViH | 2C            | 0               | 0               | 1               | 0   | 1               | 1               | 0               | 0   |

#### **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature Plastic Packages65°C to +125°C                |

|-------------------------------------------------------------------|

| Ambient Temperature with Power Applied55°C to + 125°C             |

| Voltage with Respect To Ground. All pins                          |

| except A <sub>9</sub> and V <sub>PP</sub> (Note 1)2.0 V to +7.0 V |

| Vcc (Note 1)                                                      |

| A <sub>9</sub> (Note 2)                                           |

| V <sub>PP</sub> (Note 2)                                          |

| Output Short Circuit Current (Note 3) 200 mA                      |

| Notes:                                                            |

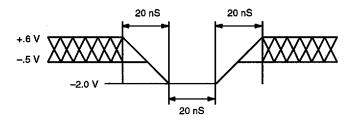

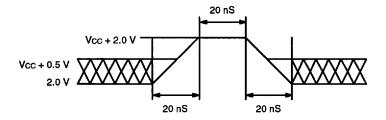

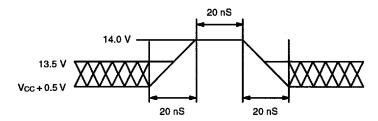

- Minimum DC voltage on input or I/O pins is -0.5 V. During voltage transitions, inputs may overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC voltage on output and I/O pins is V<sub>CC</sub> + 0.5 V. During voltage transitions, outputs may overshoot to V<sub>CC</sub> + 2.0 V for periods up to 20 ns.

- During programming operations only. Minimum DC input voltage on Ae and VPP pins is -0.5V. During voltage transitions, Ae and VPP may overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC input voltage on Ae and VPP is +13.5 V which may overshoot to 14.0 V for periods up to 20 ns.

- No more than one output shorted at a time. Duration of the short circuit should not be greater than one second.

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent darnage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure of the device to absolute maximum rating conditions for extended periods may affect device reliability.

### **OPERATING RANGES**

| Commercial (C) Devices          |                |

|---------------------------------|----------------|

| Case Temperature (Tc)           | 0°C to +70°C   |

| V <sub>CC</sub> Supply Voltages |                |

| Voc for Am27I V020              | 130 V to 136 V |

Vcc for Am27LV020 ..... +3.0 V to +3.6 V

V<sub>PP</sub> Supply Voltages

Program and Verify . . . . . . . +12.5 V to +13 V

Operating ranges define those limits between which the functionality of the device is guaranteed.

## **MAXIMUM OVERSHOOT Maximum Negative Input Overshoot**

11561-009B

## **Maximum Positive Input Overshoot**

11561-010A

## Maximum V<sub>PP</sub> Overshoot

11561-011A

59E D

#### DC CHARACTERISTICS-CMOS COMPATIBLE

| Parameter<br>Symbol | Parameter Description                           | Test Conditions                                                                                      | Min.        | Max.                     | Unit |

|---------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------|--------------------------|------|

| lu                  | Input Leakage Current                           | Vcc = Vcc Max.,<br>Vin = Vcc or Vss                                                                  |             | + 1.0                    | μА   |

| lro                 | Output Leakage Current                          | Vcc = Vcc Max.,<br>Vout = Vcc or Vss                                                                 |             | + 1.0                    | μΑ   |

| lccs                | Vcc Standby Current                             | Vcc = Vcc Max.<br>CE = Vcc ± 0.3 V                                                                   |             | 25                       | μΑ   |

| lcc1                | Vcc Active Read Current                         | $V_{CC} = V_{CC} Max., \overline{CE} = V_{IL}, \overline{OE} = V_{IH}$<br>$I_{OUT} = 0 mA, at 5 MHz$ |             | 15                       | mA   |

| lcc2                | Vcc Programming Current                         | CE = V <sub>IL</sub><br>Programming in Progress                                                      |             | 30                       | mA   |

| IPPS                | VPP Standby Current                             | VPP = VPPL                                                                                           |             | + 1.0                    | μА   |

| VıL                 | Input Low Voltage                               |                                                                                                      | -0.5        | 0.6                      | ٧    |

| Vıн                 | Input High Voltage                              |                                                                                                      | 2.0         | Vcc<br>+ 0.5             | ٧    |

| Vol                 | Output Low Voltage                              | IoL = 1 mA<br>Vcc = Vcc Min.                                                                         |             | 0.3                      | V    |

| Vон                 | Output High Voltage                             | I <sub>OH</sub> = −100 μA, Vcc = Vcc Min.                                                            | Vcc<br>-0.3 |                          | ٧    |

| VID                 | A <sub>9</sub> Auto Select Voltage              | A9 = V <sub>ID</sub>                                                                                 | 11.5        | 13.0                     | ٧    |

| lıD                 | A <sub>9</sub> Auto Select Current              | A <sub>9</sub> = V <sub>ID</sub> Max.<br>Vcc = Vcc Max.                                              |             | 35                       | μА   |

| VPPL                | V <sub>PP</sub> during Read-Only<br>Operations  |                                                                                                      | 0.0         | V <sub>CC</sub><br>+ 2.0 | ٧    |

| VPPH                | V <sub>PP</sub> during Read/Write<br>Operations |                                                                                                      | 12.5        | 13.0                     | ٧    |

#### Notes:

- 1. Caution: the Am27LV020 must not be removed from (or inserted into) a socket when Vcc or Vpp is applied.

- 2. ICC1 is tested with  $\overline{OE} = V_{IH}$  to simulate open outputs.

- 3. Maximum active power usage is the sum of Icc and IPP.

## PIN CAPACITANCE

| Parameter<br>Symbol | Parameter Description | Test Conditions     | Тур. | Max. | Unit |

|---------------------|-----------------------|---------------------|------|------|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 0 | 8    | 10   | рF   |

| Соит                | Output Capacitance    | Vout = 0            | 8    | 12   | pF   |

| C <sub>IN2</sub>    | VPP Input Capacitance | V <sub>PP</sub> = 0 | 8    | 12   | pF   |

#### Notes:

- 1. Sampled, not 100% tested.

- 2. Test conditions TA = 25°C, f = 1.0 MHz.

## SWITCHING CHARACTERISTICS over operating range unless otherwise specified AC CHARACTERISTICS—Read Only Operation (Note 1)

| Parameter<br>Symbols |                                       |                                                     | Am27LV020             |     |      |      |      |  |

|----------------------|---------------------------------------|-----------------------------------------------------|-----------------------|-----|------|------|------|--|

| JEDEC                | Standard                              | Parameter Description                               | Parameter Description |     | -250 | -300 | Unit |  |

| tavav                | tavav t <sub>RC</sub> Read Cycle Time |                                                     | Min.<br>Max.          | 200 | 250  | 300  | ns   |  |

| <b>t</b> ELQV        | tce                                   | Chip Enable<br>Access Time                          | Min.<br>Max.          | 200 | 250  | 300  | ns   |  |

| tavqv                | tacc                                  | Address<br>Access Time                              | Min.<br>Max.          | 200 | 250  | 300  | ns   |  |

| tglav                | toE                                   | Output Enable<br>Access Time                        | Min.<br>Max.          | 75  | 100  | 100  | ns   |  |

| telox                | tız                                   | Chip Enable to<br>Output in Low Z                   | Min.<br>Max.          | 0   | 0    | 0    | ns   |  |

| teHQZ                | tor                                   | Chip Disable to<br>Output in High Z                 | Min.<br>Max.          | 35  | 35   | 35   | ns   |  |

| tGLQX                | toLz                                  | Output Enable to<br>Output in Low Z                 | Min.<br>Max.          | 0   | 0    | 0    | ns   |  |

| tgноz                | <b>t</b> DF                           | Output Disable to<br>Output in High Z               | Min.<br>Max.          | 35  | 35   | 35   | ns   |  |

| taxqx                | tон                                   | Output Hold from first of Address, CE, or OE Change | Min.<br>Max.          | 0   | 0    | 0    | ns   |  |

| tvcs                 |                                       | Vcc Set-up Time to<br>Valid Read                    | Min.<br>Max.          | 50  | 50   | 50   | μs   |  |

#### Notes:

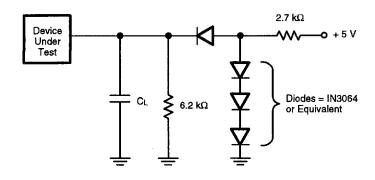

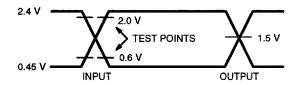

- 1. Output Load: 1 TTL gate and C<sub>L</sub> = 100 pF, Input Rise and Fall Times: ≤ 10 ns, Input Pulse levels: 0.45 to 2.4 V, Timing Measurement Reference Level - Inputs: 0.6 V and 2 V Outputs: 1.5 V

- 2. tycs is guaranteed by design not tested.

11561-013C

**AC Waveforms for Read Operations**

## SWITCHING TEST CIRCUIT

11561-012A

C<sub>L</sub> = 100 pF including jig capacitance

## **SWITCHING TEST WAVEFORMS**

All Devices

AC Testing: Inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Input pulse rise and fall times are  $\leq$  10 ns.

16357A-002B

AMD

## PRELIMINARY

## **ERASE AND PROGRAMMING PERFORMANCE**

|                       | Limits |               | Limits |      |                                |  |  |

|-----------------------|--------|---------------|--------|------|--------------------------------|--|--|

| Parameter             | Min.   | Тур.          | Max.   | Unit | Comments                       |  |  |

| Chip Programming Time |        | 4<br>(Note 1) | 48     | s    | Excludes system-level overhead |  |  |

## Note:

## LATCHUP CHARACTERISTICS

|                                                                                                           | Min.    | Max.        |

|-----------------------------------------------------------------------------------------------------------|---------|-------------|

| Input Voltage with respect to $V_{SS}$ on all pins except I/O pins (Including $A_{\theta}$ and $V_{PP}$ ) | -1.0 V  | 13.5 V      |

| Input Voltage with respect to Vss on all pins I/O pins                                                    | -1.0 V  | Vcc + 1.0 V |

| Current                                                                                                   | -100 mA | +100 mA     |

| Includes all pins except $V_{\rm CC}$ . Test conditions: $V_{\rm CC}$ = 5.0 V, one pin at a               | time.   |             |

<sup>1. 25°</sup>C, 12.75 V VPP.

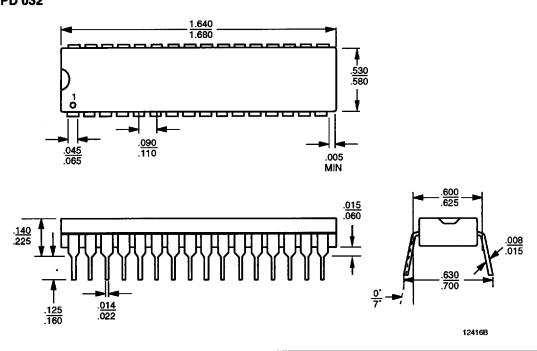

## PHYSICAL DIMENSIONS\* PD 032

PL 032

\*For reference only. All dimensions are measured in inches, unless otherwise noted. BSC is an ANSI standard for Basic Space Centering.

AMD 🗔

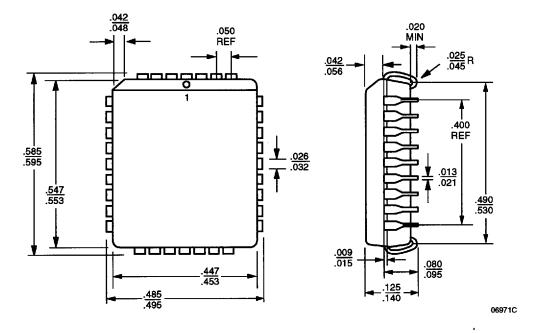

# PHYSICAL DIMENSIONS TS 032