# 64K x 32 3.3V Static RAM Module

#### **Features**

- · High-density 3.3V 2-megabit SRAM module

- High-speed SRAMs

- Access time of 12 ns

- · Low active power

- 1.512W (max.) at 12 ns

- 64 pins

- · Available in ZIP format

#### **Functional Description**

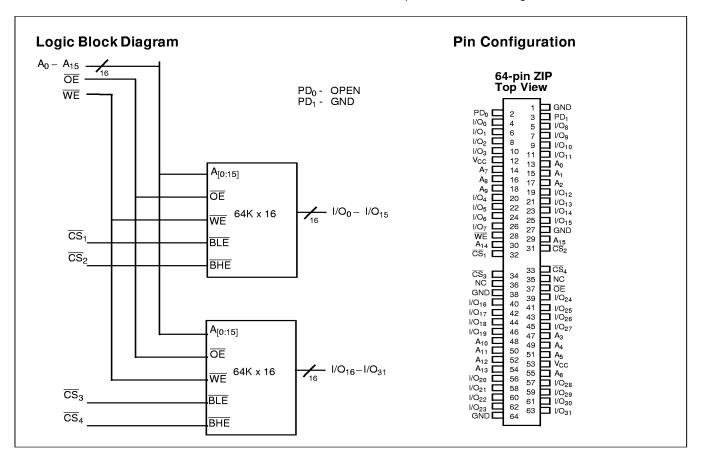

The CYM1831V33 is a high-performance 3.3V 2-megabit static RAM module organized as 64K words by 32 bits. This module is constructed from two 64K x 16 SRAMs in SOJ packages mounted on an epoxy laminate substrate. Four chip selects are used to independently enable the four bytes. Reading or writing can be executed on individual bytes or any combination of multiple bytes through proper use of selects.

The CYM1831V33 is designed for use with standard 64-pin ZIP sockets. The pinout is compatible with the 64-pin JEDEC ZIP module family (CYM1821, CYM1831, CYM1836, and CYM1841). Thus, a single motherboard design can be used to accommodate memory depth ranging from 16K words (CYM1821) to 256K words (CYM1841). The CYM1831V33 is offered in a vertical ZIP configuration.

Presence detect pins (PD<sub>0</sub>-PD<sub>1</sub>) are used to identify module memory density in applications where modules with alternate word depths can be interchanged.

#### Selection Guide

|                                | 1831V33-12 | 1831V33-15 | 1831V33-20 | 1831V33-25 | 1831V33-35 |

|--------------------------------|------------|------------|------------|------------|------------|

| Maximum Access Time (ns)       | 12         | 15         | 20         | 25         | 35         |

| Maximum Operating Current (mA) | 420        | 400        | 380        | 380        | 380        |

| Maximum Standby Current (mA)   | 250        | 250        | 250        | 250        | 250        |

### **Maximum Ratings**

Storage Temperature ......-55°C to +125°C Ambient Temperature with Power Applied......-10°C to +85°C Supply Voltage to Ground Potential ..... -0.5V to +4.6V

| DC Voltage Applied to Outputs |                          |

|-------------------------------|--------------------------|

| in High Z State               | 0.5V to +V <sub>CC</sub> |

| DC Input Voltage              | 0.5V to +4.6V            |

### **Operating Range**

| Range      | Ambient<br>Temperature | V <sub>cc</sub>    |

|------------|------------------------|--------------------|

| Commercial | 0°C to +70°C           | 3.3V<br>(+10%/–5%) |

### **Electrical Characteristics** Over the Operating Range

| Parameter        | Description                                       | Test Condi                                                                                                                                                                                       | tions                      | Min.                  | Max. | Unit |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|------|------|

| V <sub>OH</sub>  | Output HIGH Voltage                               | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4.0 mA                                                                                                                                                | 2.4                        |                       | ٧    |      |

| V <sub>OL</sub>  | Output LOW Voltage                                | $V_{CC} = Min., I_{OL} = 4.0 \text{ mA}$                                                                                                                                                         |                            |                       | 0.4  | ٧    |

| V <sub>IH</sub>  | Input HIGH Voltage                                |                                                                                                                                                                                                  | 2.0                        | V <sub>CC</sub> + 0.3 | ٧    |      |

| V <sub>IL</sub>  | Input LOW Voltage                                 |                                                                                                                                                                                                  |                            | -0.3                  | 0.8  | ٧    |

| I <sub>IX</sub>  | Input Load Current                                | $GND \leq V_1 \leq V_{CC}$                                                                                                                                                                       |                            | -10                   | +10  | μΑ   |

| l <sub>oz</sub>  | Output Leakage Current                            | GND $\leq$ V <sub>O</sub> $\leq$ V <sub>CC</sub> , Output [                                                                                                                                      | -10                        | +10                   | μΑ   |      |

| lcc              | V <sub>CC</sub> Operating Supply                  | $\frac{V_{CC}}{CS_N} \le V_{IL}$ = 0 mA, $\frac{-12}{-15}$                                                                                                                                       |                            |                       | 420  | mA   |

|                  | Current                                           |                                                                                                                                                                                                  |                            |                       | 400  |      |

|                  |                                                   |                                                                                                                                                                                                  | -20, -25, -35              |                       | 380  |      |

| I <sub>SB1</sub> | Automatic CS Power-Down Current <sup>[1]</sup>    |                                                                                                                                                                                                  |                            |                       | 250  | mA   |

| I <sub>SB2</sub> | Automatic CS Power-Down<br>Current <sup>[1]</sup> | $\label{eq:local_local_local} \begin{split} & \frac{Max}{CS} \cdot V_{CC}, \\ & \frac{CS}{CS} \geq V_{CC} - 0.2V, \\ & V_{IN} \geq V_{CC} - 0.2V, \text{ or } \\ & V_{IN} \leq 0.2V \end{split}$ | -12, -15, -20,<br>-25, -35 |                       | 250  | mA   |

### Capacitance<sup>[2]</sup>

| Parameter        | Description                                    | Test Conditions                   | Max. | Unit |

|------------------|------------------------------------------------|-----------------------------------|------|------|

| C <sub>INA</sub> | Input Capacitance (WE, OE, A <sub>0-19</sub> ) | T <sub>A</sub> = 25°C, f = 1 MHz, | 12   | pF   |

| C <sub>INB</sub> | Input Capacitance (CS)                         | $V_{CC} = 5.0V$                   | 6    | pF   |

| C <sub>OUT</sub> | Output Capacitance                             |                                   | 8    | pF   |

#### Notes:

A pull-up resistor to V<sub>CC</sub> on the CS input is required to keep the device deselected during V<sub>CC</sub> power-up, otherwise I<sub>SB</sub> will exceed values given.

Tested on a sample basis.

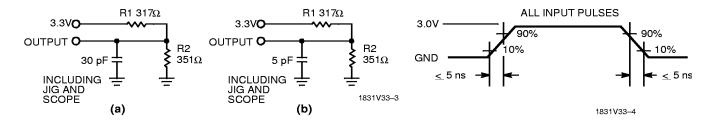

#### **AC Test Loads and Waveforms**

Equivalent to: THÉVENIN EQUIVALENT 0UTPUT 0 167 $\Omega$  1.73V

#### Switching Characteristics Over the Operating Range<sup>[3]</sup>

|                   |                                     | 1831     | /33-12 | 1831\ | /33-15 |      |

|-------------------|-------------------------------------|----------|--------|-------|--------|------|

| Parameter         | Description                         |          | Max.   | Min.  | Max.   | Unit |

| READ CYCLE        |                                     |          | 1      | •     | •      | •    |

| t <sub>RC</sub>   | Read Cycle Time                     | 12       |        | 15    |        | ns   |

| t <sub>AA</sub>   | Address to Data Valid               |          | 12     |       | 15     | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change       | 3        |        | 3     |        | ns   |

| t <sub>ACS</sub>  | CS LOW to Data Valid                |          | 12     |       | 15     | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid                |          | 7      |       | 8      | ns   |

| <sup>t</sup> LZOE | OE LOW to Low Z                     | 0        |        | 0     |        | ns   |

| <sup>t</sup> HZOE | OE HIGH to High Z                   |          | 7      |       | 8      | ns   |

| t <sub>LZCS</sub> | CS LOW to Low Z <sup>[4]</sup>      | 3        |        | 3     |        | ns   |

| t <sub>HZCS</sub> | CS HIGH to High Z <sup>[4, 5]</sup> |          | 7      |       | 8      | ns   |

| t <sub>PD</sub>   | CS HIGH to Power-Down               |          | 12     |       | 15     | ns   |

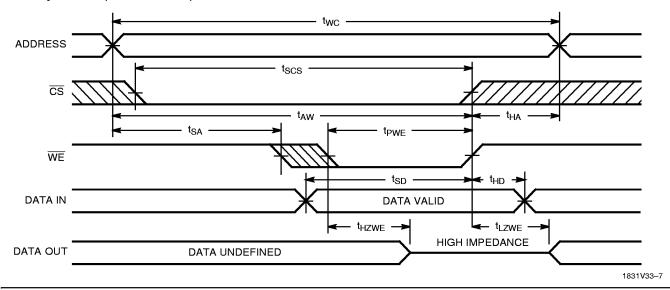

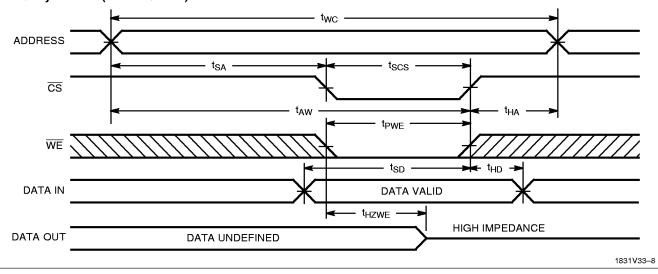

| WRITE CYCLE       | 6]                                  | <u> </u> | •      |       | •      |      |

| t <sub>WC</sub>   | Write Cycle Time                    | 12       |        | 15    |        | ns   |

| t <sub>SCS</sub>  | CS LOW to Write End                 | 9        |        | 10    |        | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End         | 9        |        | 10    |        | ns   |

| t <sub>HA</sub>   | Address Hold from Write End         | 0        |        | 0     |        | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start       | 1        |        | 1     |        | ns   |

| t <sub>PWE</sub>  | WE Pulse Width                      | 10       |        | 12    |        | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End            | 7        |        | 8     |        | ns   |

| t <sub>HD</sub>   | Data Hold from Write End            | 1        |        | 1     |        | ns   |

| t <sub>LZWE</sub> | WE HIGH to Low Z                    | 3        |        | 3     |        | ns   |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[5]</sup>     | 0        | 7      | 0     | 8      | ns   |

#### Notes:

- 3. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 30-pF load capacitance.

- 4. At any given temperature and voltage condition, t<sub>HZCS</sub> is less than t<sub>LZCS</sub> for any given device. These parameters are guaranteed and not 100% tested.

- t<sub>HZCS</sub> and t<sub>HZWE</sub> are specified with C<sub>L</sub> = 5 pF as in part (b) of AC Test Loads and Waveforms. Transition is measured ±500 mV from steady-state voltage.

The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

## $\textbf{Switching Characteristics} \ \, \text{Over the Operating Range}^{[3]} \text{(continued)}$

|                   |                                     | 1831\    | /33-20 | 1831V33-25 |      | 1831V33-35 |      |      |

|-------------------|-------------------------------------|----------|--------|------------|------|------------|------|------|

| Parameter         | Description                         | Min.     | Max.   | Min.       | Max. | Min.       | Max. | Unit |

| READ CYCLE        | Į.                                  |          |        |            |      | 1          |      |      |

| t <sub>RC</sub>   | Read Cycle Time                     | 20       |        | 25         |      | 35         |      | ns   |

| t <sub>AA</sub>   | Address to Data Valid               |          | 20     |            | 25   |            | 35   | ns   |

| t <sub>OHA</sub>  | Data Hold from Address Change       | 3        |        | 3          |      | 3          |      | ns   |

| t <sub>ACS</sub>  | CS LOW to Data Valid                |          | 20     |            | 25   |            | 35   | ns   |

| t <sub>DOE</sub>  | OE LOW to Data Valid                |          | 12     |            | 15   |            | 18   | ns   |

| t <sub>LZOE</sub> | OE LOW to Low Z                     | 0        |        | 0          |      | 0          |      | ns   |

| t <sub>HZOE</sub> | OE HIGH to High Z                   |          | 10     |            | 12   |            | 15   | ns   |

| t <sub>LZCS</sub> | CS LOW to Low Z <sup>[4]</sup>      | 3        |        | 3          |      | 3          |      | ns   |

| t <sub>HZCS</sub> | CS HIGH to High Z <sup>[4, 5]</sup> |          | 10     |            | 12   |            | 15   | ns   |

| t <sub>PD</sub>   | CS HIGH to Power-Down               |          | 20     |            | 25   |            | 35   | ns   |

| WRITE CYCLE       | <u>:[6]</u>                         | <u>'</u> |        |            |      |            |      |      |

| t <sub>WC</sub>   | Write Cycle Time                    | 20       |        | 25         |      | 35         |      | ns   |

| t <sub>SCS</sub>  | CS LOW to Write End                 | 17       |        | 20         |      | 30         |      | ns   |

| t <sub>AW</sub>   | Address Set-Up to Write End         | 17       |        | 20         |      | 30         |      | ns   |

| t <sub>HA</sub>   | Address Hold from Write End         | 3        |        | 3          |      | 3          |      | ns   |

| t <sub>SA</sub>   | Address Set-Up to Write Start       | 2        |        | 2          |      | 2          |      | ns   |

| t <sub>PWE</sub>  | WE Pulse Width                      | 15       |        | 20         |      | 30         |      | ns   |

| t <sub>SD</sub>   | Data Set-Up to Write End            | 12       |        | 15         |      | 20         |      | ns   |

| t <sub>HD</sub>   | Data Hold from Write End            | 2        |        | 2          |      | 2          |      | ns   |

| t <sub>LZWE</sub> | WE HIGH to Low Z                    | 3        |        | 3          |      | 3          |      | ns   |

| t <sub>HZWE</sub> | WE LOW to High Z <sup>[5]</sup>     | 0        | 12     | 0          | 12   | 0          | 15   | ns   |

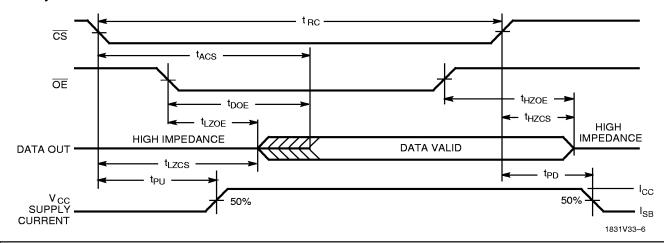

### **Switching Waveforms**

### Read Cycle No. 1 [7, 8]

1831V33-5

Notes:

7. WE is HIGH for read cycle.

8. Device is continuously selected, CS = V<sub>|L</sub>, and OE = V<sub>|L</sub>.

### Switching Waveforms (continued)

### Read Cycle No. 2 [7, 9]

### Write Cycle No. 1 (WE Controlled) [6]

#### Note

9. Address valid prior to or coincident with  $\overline{\text{CS}}$  transition LOW.

### Switching Waveforms (continued)

# Write Cycle No. 2 (CS Controlled) [6,10]

#### Note:

10. If  $\overline{\text{CS}}$  goes HIGH simultaneously with  $\overline{\text{WE}}$  HIGH, the output remains in a high-impedance state.

#### **Truth Table**

| cs | WE | OE | Inputs/Output | Mode                |

|----|----|----|---------------|---------------------|

| Н  | Х  | Х  | High Z        | Deselect/Power-Down |

| L  | Н  | L  | Data Out      | Read                |

| L  | L  | Х  | Data In       | Write               |

| L  | Н  | Н  | High Z        | Deselect            |

### **Ordering Information**

| Speed<br>(ns) | Ordering Code    | Package<br>Type | Package Type              | Operating<br>Range |

|---------------|------------------|-----------------|---------------------------|--------------------|

| 12            | CYM1831V33PZ-12C | PZ12            | 64-Pin Plastic ZIP Module | Commercial         |

| 15            | CYM1831V33PZ-15C |                 |                           |                    |

| 20            | CYM1831V33PZ-20C |                 |                           |                    |

| 25            | CYM1831V33PZ-25C |                 |                           |                    |

| 35            | CYM1831V33PZ-35C |                 |                           |                    |

Document #: 38-M-00087-A

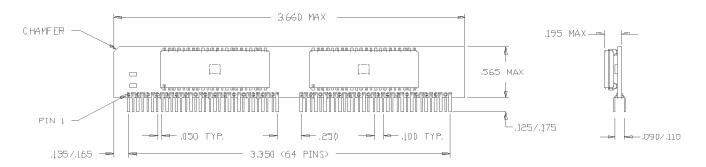

### Package Diagram

#### 64-Pin Plastic ZIP Module PZ12