# *CL-GD6410*

Data Book

### FEATURES

- Single-chip VGA controller

- IBM<sup>®</sup> VGA hardware-compatible

- Simultaneous CRT and LCD (SimulSCAN™) operation

- Two 256K x 4 DRAM video memory for small form factor

- Integrates RAMDAC

- Integrates LCD panel interface

- Control and data buffering

- Power-sequencing logic

- Direct connection to ISA (PC AT) Bus

- Frame-Accelerator for low-active power

- Standby and Suspend Modes to save power

- Expanded operational range: 5V ± 10%

Low-voltage (4.5V) operation saves power

- 64-shade grayscale on monochrome STN LCD

- NTSC sum-to-gray color mapping

- Multiple sum-to-gray weighting options

- Direct connection to 512-color TFT LCD

- Single-controller design for STN monochrome and TFT color LCDs

- Graphics and text expansion and compression maps CRT modes to fixed-resolution LCD

- 800 x 600 x 16 color on analog CRT

- 8- or 16-bit CPU interface

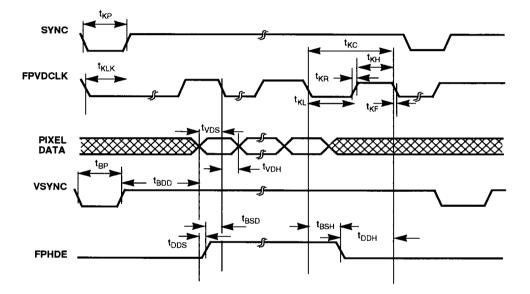

- 160-pin (EIAJ-standard) QFP package

- Pinout optimized for efficient board layout

### High-Integration LCD VGA Controller for Notebook Computers

### OVERVIEW

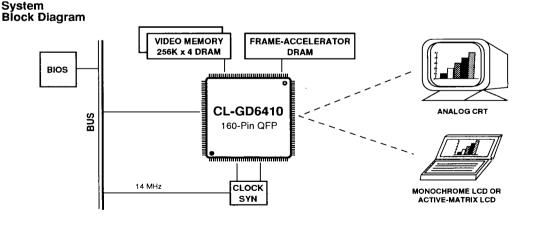

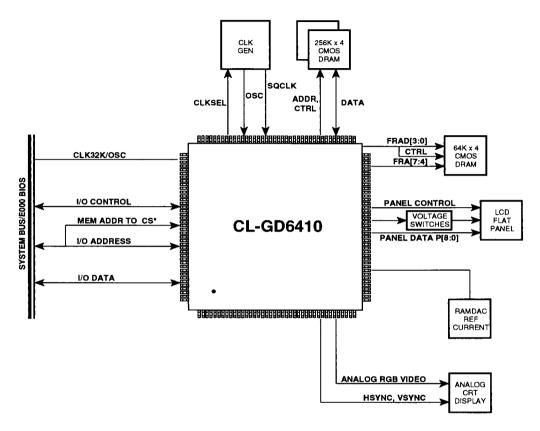

The CL-GD6410 is a single-chip VGA controller optimized for use in notebook computers, where reduced form factor and low power consumption are critical design objectives. With the CL-GD6410, a complete motherboard VGA controller requires only four or five ICs and can fit within four square inches (excluding power sources and connectors). A true two-DRAM video memory (256K x 4), on-chip RAMDAC, direct-connect ISA (PC AT) Bus interface, and direct-connect LCD interface all help to minimize the form factor.

By using Cirrus Logic's Frame-Accelerator technique, the CL-GD6410 is able to provide a high vertical refresh rate for dual-scan LCD panels while operating at approximately one-half the clock speed of other LCD controller solutions; this provides a significant reduction in full-active power consumption and extends battery life. In addition, Standby and Suspend Modes are supported in the hardware of the CL-GD6410 to enable multiple levels of system power management.

(cont. next page)

### OVERVIEW (cont.)

Cirrus Logic LCD VGA controllers have earned a reputation for providing the industry's best LCD image quality. The CL-GD6410 continues this lineage, providing 64 shades of gray on monochrome LCD panels. Duty-cycle modulation, combined with dynamic pattern-management algorithms, provide 640 x 480-resolution grayscales with no apparent flicker. Pixel-doubling and stippling techniques provide increased grayscale in the VGA high-color Mode 13. In all cases, the Cirrus Logic grayscale provides consistent linear-step functions, making smooth transitions from black, through the grayscale, to white.

With a direct connection to 512-color TFT (Thin Film Transistor) LCD panels, the CL-GD6410 provides a single-controller solution for 64-grayscale-monochrome and 256-simultaneous-color portable computers. The

CL-GD6410 also provides a direct interface to the CL-GD6340, Cirrus Logic's color LCD interface controller. With this combination, color LCDs can produce stunning, CRT-quality images.

The CL-GD6410 panel interface includes programmable panel parameters that allow a controller design to be optimized for excellent display quality on a variety of panels.

SimulSCAN<sup>™</sup> operation, a Cirrus Logic technique for achieving simultaneous CRT and LCD operation, is one of the features of the CL-GD6410. SimulSCAN allows the portable computer to become a key part of presentation environments for sales force automation, field service, and educational organizations.

### SimulSCAN™ Operation

SimulSCAN operation is:

- Simultaneous display on internal LCD and external CRT

- Compatible with VGA modes not limited to special modes

- Compatible with VGA applications software not limited to special applications

- Transparent to the viewer of the external display

SimulSCAN provides:

- □ An external display for audience presentations fixed frequency or multi-frequency analog CRT

- An internal display for computer operation singlescan or dual-scan LCD (6.3-MHz panel speed required for dual-scan LCD)

- Reverse intensity (optional) on the internal display; simultaneous with normal operation of the external display

SimulSCAN operation allows the portable computer to be used in large audience presentation/demonstration environments. With SimulSCAN, the computer provides an analog RGB video signal for overhead projection systems, standard CRTs, or large-screen CRTs for the audience to view, while maintaining operation of the computer's internal LCD display for the computer operator to view.

To achieve SimulSCAN operation, the CL-GD6410 provides separate CRT and LCD display data output paths. Resolution mapping logic converts the various CRT resolutions to the fixed resolution of the LCD. Clock management logic converts the CRT timing to LCD timing. The CL-GD6410 is able to provide clock signals at different rates to two displays simultaneously.

Today's most popular monochrome STN (Super Twist Nematic) LCD panels are of dual-panel construction. It is a considerable design challenge to reconcile the singlescan format of the CRT with the dual-scan format required by the LCD. The Frame-Accelerator technology of the CL-GD6410 buffers one-half of a frame, alternating between the lower-panel half-frame and upper-panel half-frame of the LCD. In this manner, the controller's direct-output operates as though it is driving a singlescan display, with the frame accelerator driving the halfframe that lags (or leads) the direct-output frame.

2

DATA BOOK

## CL-GD6410

Notebook VGA Controller

### **Table of Contents**

| Sec | tion                                                                                                                                                                                                                      | Page     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.  | PIN INFORMATION                                                                                                                                                                                                           |          |

| 2.  | PIN ASSIGNMENTS                                                                                                                                                                                                           | *        |

| 3.  | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                    |          |

| 4.  | VIDEO MODES         4.1       CRT Video Modes         4.2       LCD Video Modes                                                                                                                                           | 17       |

| 5.  | ELECTRICAL SPECIFICATIONS         5.1       Absolute Maximum Ratings         5.2       CL-GD6410 DC Specifications (Digital)         5.3       CL-GD6410 DC Specifications (RAMDAC)         5.4       DAC Characteristics |          |

| 6.  | AC TIMING CHARACTERISTICS<br>6.1 Index of Timing Information                                                                                                                                                              |          |

| 7.  | CL-GD6410 REGISTERS         7.1       VGA Register Port Map         7.2       Register Delta List Between the CL-GD6410-A and the CL-GD6410-B         7.3       CL-GD6410 Extended Register Details                       | 54<br>54 |

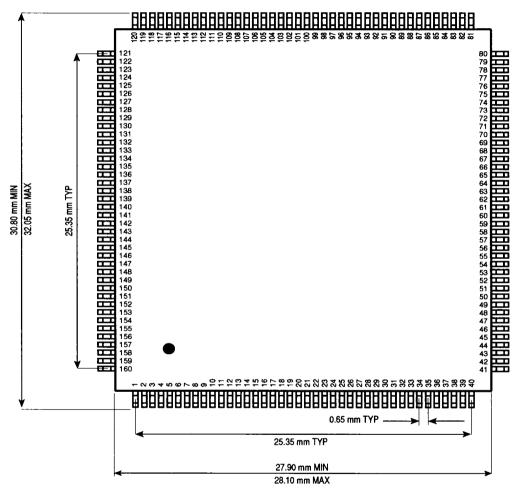

| 8.  | SAMPLE PACKAGE         8.1       160-Pin Quad Flat Pack (QFP, EIAJ)         8.2       160-Pin Quad Flat Pack Expanded View (QFP, EIAJ)                                                                                    | 129      |

| 9.  | TYPICAL APPLICATION                                                                                                                                                                                                       | 131      |

| 10. | ORDERING INFORMATION                                                                                                                                                                                                      |          |

April 1993

#### 1. PIN INFORMATION

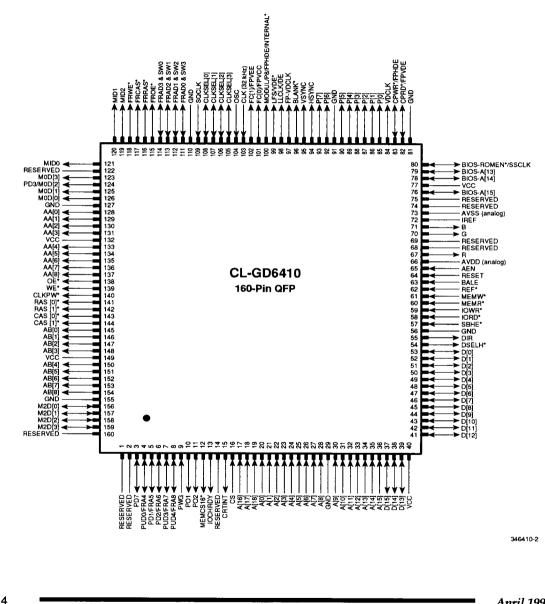

The CL-GD6410 is available in a 160-pin guad flat pack device configuration, shown below.

#### 1.1 **Pin Diagram**

April 1993

### 2. PIN ASSIGNMENTS

The following conventions are used in the pin assignment table: (I) indicates input; (O) indicates output; (TO) indicates tristate output; (AO) indicates analog output; (AI) indicates analog input; (PW) indicates power; (\*) denotes a negative-true (active-low) signal.

### 2.1 Pin Assignment Table

| Name                            | Pin No.                  | Туре                                                                                               | Description                                                                                                                         |  |  |  |  |  |

|---------------------------------|--------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CS                              | 16                       | <b>CHIP SELECT</b> : When high, this indicates that the CL-GD6410 is selected for memory accesses. |                                                                                                                                     |  |  |  |  |  |

| A[18:16],<br>A[15:9],<br>A[8:0] | 19:17<br>36:30,<br>28:20 | 1                                                                                                  | CPU ADDRESS INPUTS.                                                                                                                 |  |  |  |  |  |

| D[15:0]                         | 37:39<br>41:53           | I/O                                                                                                | CPU DATA I/O.                                                                                                                       |  |  |  |  |  |

| DSELH*                          | 54                       | 0                                                                                                  | <b>DATA SELECT HIGH BYTE</b> : This enables the CPU data bus upper-byte buffer when needed.                                         |  |  |  |  |  |

| DIR                             | 55                       | 0                                                                                                  | CPU DATA BUS BUFFER DIRECTION: When low, this indicates a CPU read. (DIR is used only when CPU data has to be buffered).            |  |  |  |  |  |

| SBHE*                           | 57                       | Ι                                                                                                  | <b>BYTE HIGH ENABLE</b> : This signal is sampled only if 16-Bit<br>Mode is enabled; otherwise, 8-bit bus operations are<br>assumed. |  |  |  |  |  |

| IORD*                           | 58                       | I                                                                                                  | I/O READ: This indicates that an I/O read cycle is occurring.                                                                       |  |  |  |  |  |

| IOWR*                           | 59                       | I                                                                                                  | I/O WRITE: This indicates that an I/O write cycle is occurring.                                                                     |  |  |  |  |  |

| MEMR*                           | 60                       | I                                                                                                  | <b>MEMORY READ</b> : This indicates that a memory read cycle is occurring.                                                          |  |  |  |  |  |

| MEMW*                           | 61                       | I                                                                                                  | <b>MEMORY WRITE</b> : This indicates that a memory write cycle is taking place.                                                     |  |  |  |  |  |

| REF*                            | 62                       | I                                                                                                  | <b>REFRESH:</b> This indicates a memory-refresh cycle and will cause the CL-GD6410 to ignore memory accesses on the bus.            |  |  |  |  |  |

| BALE                            | 63                       | I                                                                                                  | ADDRESS LATCH ENABLE: A high indicates a valid memory address.                                                                      |  |  |  |  |  |

April 1993

DATA BOOK

2.1 Pin Assignment Table (cont.)

| Name               | Pin No.            | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|--------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET              | 64                 | 1    | SYSTEM RESET: This input is normally connected to the System Reset Bus Signal and is used as a hardware reset signal for the CL-GD6410.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AEN                | 65                 | I    | <b>ADDRESS ENABLE</b> : This is a host CPU Bus Signal that distinguishes between DMA and non-DMA Bus Cycles. The signal is high for a DMA Cycle, and it will cause the CL-GD6410 to ignore IORD* and IOWR*.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MEMCS16*           | 12                 | то   | This output is an acknowledge for 16-bit-wide accesses and<br>is generated by the CL-GD6410 only if the 16-Bit Peripheral<br>Mode is enabled and a valid memory-address range has<br>been decoded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

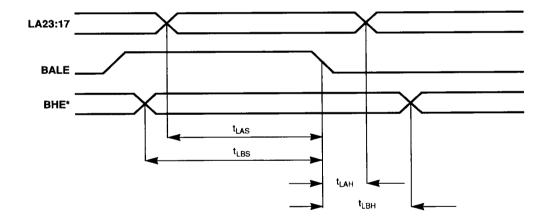

| IOCHRDY            | 13                 | то   | This signal is driven low to lengthen memory cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CRTINT             | 15                 | то   | Indicates the start of a vertical retrace, normally connected<br>to one of the interrupt inputs on the PC Bus. It is enabled by<br>clearing Bit 5 of the Vertical Retrace End Register and dis-<br>abled by clearing Bit 4 of the Vertical Retrace End Register.<br>When enabled, the CRTINT Pin will go high at the start of<br>the vertical retrace interval, and remain high until cleared by<br>a write of '0' to Bit 4 of the Vertical Retrace End Register<br>(CR11). CRTINT is enabled by:<br><i>Clearing Bit 5 of CR11</i><br><i>Setting Bit 4 of CR11</i><br>If Bit 4 is not reset to a '1' after clearing the initial CRTINT,<br>interrupts will cease. This feature greatly simplifies the task<br>of OR'ing in the proper value for the remaining bits of the<br>CR11 Register (this is not the case for an IBM <sup>®</sup> EGA or VGA<br>controller). CRTINT may be programmed for the AT Bus, or<br>a direct-interrupt controller interface. |

| AA[8:4]<br>AA[3:0] | 137:133<br>131:128 | 0    | VIDEO MEMORY 'A' ADDRESS BUS: This bus contains<br>the row/column address information required by the DRAMs<br>in Video Memory Planes 0 and 1. This bus carries different<br>addresses than the 'AB' Bus in text modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AB[8:4]<br>AB[3:0] | 154:150<br>148:145 | 0    | VIDEO MEMORY 'B' ADDRESS BUS: This bus contains<br>the row/column address information required by the DRAMs<br>in Video Memory Planes 2 and 3. This bus carries different<br>addresses than the 'AA' Bus in text modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

6

DATA BOOK

### **CL-GD6410** Notebook VGA Controller

------

### 2.1 Pin Assignment Table (cont.)

| Name                            | Pin No. | Туре | Description                                                                                                                                                                               |  |  |  |  |

|---------------------------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OE*                             | 138     | 0    | VIDEO MEMORY OUTPUT ENABLE, active low.                                                                                                                                                   |  |  |  |  |

| WE*                             | 139     | 0    | VIDEO MEMORY WRITE ENABLE.                                                                                                                                                                |  |  |  |  |

| CLKPW*                          | 140     | 0    | <b>CLOCK CHIP POWER CONTROL</b> , active low, can be used<br>to control external transistor logic connected to clock<br>synthesizer power pins. This signal is active in Suspend<br>Mode. |  |  |  |  |

| RAS*[1:0]                       | 142:141 | 0    | VIDEO MEMORY RAS: RAS*[0] to AA Bus, RAS*[1] to AB Bus.                                                                                                                                   |  |  |  |  |

| CAS*[1:0]                       | 144:143 | 0    | VIDEO MEMORY CAS: CAS*[0] to AA Bus, CAS[*1] to AB Bus.                                                                                                                                   |  |  |  |  |

| M0D[3], M0D[1:0],<br>M0D[2]/PD3 | 123:126 | I/O  | VIDEO MEMORY DATA PINS, Planes 0 and 1, Bits 3:0.<br>MOD[2] is multiplexed with PD3.                                                                                                      |  |  |  |  |

| MID[2:0]                        | 119:121 | I    | <b>MONITOR ID</b> , Bits 2:0. This pin is sampled on reset or under software control.                                                                                                     |  |  |  |  |

| M2D[3:0]                        | 159:156 | I/O  | VIDEO MEMORY DATA PINS, Planes 1 and 2, Bits 3:0.                                                                                                                                         |  |  |  |  |

| PD7                             | 3       | l    | CONFIGURATION PULL-DOWN 7.                                                                                                                                                                |  |  |  |  |

| FRWE*                           | 118     | 0    | FRAME-ACCELERATOR WRITE ENABLE.                                                                                                                                                           |  |  |  |  |

| FRCAS *                         | 117     | 0    | FRAME-ACCELERATOR CAS.                                                                                                                                                                    |  |  |  |  |

| FRRAS*                          | 116     | 0    | FRAME-ACCELERATOR RAS.                                                                                                                                                                    |  |  |  |  |

| FROE*                           | 115     | 0    | FRAME-ACCELERATOR OE.                                                                                                                                                                     |  |  |  |  |

| FRAD3 & SW0                     | 114     | I/O  | FRAME-ACCELERATOR MULTIPLEXED ADDRESS/<br>DATA[3] multiplexed with Switch 0.                                                                                                              |  |  |  |  |

| FRAD2 & SW1                     | 113     | 1/0  | FRAME-ACCELERATOR MULTIPLEXED ADDRESS/<br>DATA[2] multiplexed with Switch 1.                                                                                                              |  |  |  |  |

| FRAD1 & SW2                     | 112     | I/O  | FRAME-ACCELERATOR MULTIPLEXED ADDRESS/<br>DATA[1] multiplexed with Switch 2.                                                                                                              |  |  |  |  |

| FRAD0 & SW3                     | 111     | I/O  | FRAME-ACCELERATOR MULTIPLEXED ADDRESS/<br>DATA[0] multiplexed with Switch 3.                                                                                                              |  |  |  |  |

April 1993

DATA BOOK

------

### 2.1 Pin Assignment Table (cont.)

| NAME        | PIN NO.        | TYPE | DESCRIPTION                                                                                                                         |

|-------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| FRA4 & PUD0 | 4              | I/O  | FRAME-ACCELERATOR ADDRESS [4] multiplexed with Pull-Up or Pull-Down 0.                                                              |

| FRA5 & PD1  | 5              | I/O  | FRAME-ACCELERATOR ADDRESS [5] multiplexed with Pull-Down 1.                                                                         |

| FRA6 & PD2  | 6              | I/O  | FRAME-ACCELERATOR ADDRESS [6] multiplexed with Pull-Down 2.                                                                         |

| FRA7 & PUD3 | 7              | I/O  | FRAME-ACCELERATOR ADDRESS [7] multiplexed with Pull-Up or Pull-Down 3.                                                              |

| FRA8 & PUD4 | 8              | I/O  | FRAME-ACCELERATOR ADDRESS [8] multiplexed with Pull-Up or Pull-Down 4.                                                              |

| PWG         | 9              | I    | <b>POWER GOOD INPUT</b> : This signal initiates flat panel power sequencing when power is applied or is removed from the CL-GD6410. |

| PO1         | 10             | 0    | PROGRAMMABLE OUTPUT 1.                                                                                                              |

| PO2         | 11             | 0    | PROGRAMMABLE OUTPUT 2.                                                                                                              |

| CPRD*/FPVDE | 82             | I/O  | COLOR PALETTE (RAMDAC) READ if external RAMDAC<br>configuration, or FLAT-PANEL VERTICAL DISPLAY<br>ENABLE for special panels.       |

| CPWR*/FPHDE | 83             | I/O  | COLOR PALETTE (RAMDAC) WRITE if external<br>RAMDAC configuration, or FLAT-PANEL HORIZONTAL<br>DISPLAY ENABLE for special panels.    |

| VDCLK       | 84             | 0    | VIDEO CLOCK: This is the output for the external RAMDAC or color panel.                                                             |

| P[0:7]      | 85:90<br>92:93 | 0    | VIDEO DATA OUT if external RAMDAC configuration and pixel-data output for flat panels.                                              |

| HSYNC       | 94             | 0    | HORIZONTAL SYNC to CRT Monitor.                                                                                                     |

| VSYNC       | 95             | 0    | VERTICAL SYNC to CRT Monitor.                                                                                                       |

| BLANK*      | 96             | 0    | <b>BLANK OUTPUT</b> if external RAMDAC configuration; I/O if on-chip RAMDAC configuration.                                          |

8

DATA BOOK

### CL-GD6410 Notebook VGA Controller

\_\_\_\_\_

### 2.1 Pin Assignment Table (cont.)

| Name                        | Pin No.   | Туре | Description                                                                                                                                                                                                                                                       |

|-----------------------------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPVDCLK                     | 97        | 0    | FLAT-PANEL VIDEO CLOCK.                                                                                                                                                                                                                                           |

| LLCLK/DE                    | 98        | 0    | <b>FLAT-PANEL LINE CLOCK:</b> This is used to increment<br>Row Shift Registers within LCD panels or display enable if<br>the CL-GD6410 is used with the CL-GD6340.                                                                                                |

| LFS                         | 99        | 0    | LCD FRAME START PULSE: This indicates the start of a new frame on flat panels.                                                                                                                                                                                    |

| MODUL/P8/FPHDE<br>INTERNAL* | 100       | 0    | LCD PANEL MODULATION SIGNAL: This is required for<br>LCD panels that do not drive the function themselves.<br>INTERNAL* is a programmable output. P8 is needed for<br>512-color LCD panels. FPHDE is needed as an alternate<br>for Pin 83.                        |

| FC[0]/FPVCC                 | 101       | 0    | FEATURE CONNECTOR PROGRAMMABLE I/O BIT [0]<br>or LCD panel 5V control.                                                                                                                                                                                            |

| FC[1]/FPVEE                 | 102       | 0    | FEATURE CONNECTOR PROGRAMMABLE I/O BIT [1]<br>or LCD panel back-light power control.                                                                                                                                                                              |

| CLK32K                      | 103       | ł    | <b>32-kHz CLOCK</b> : The input is used both for slow timers and in Suspend Mode. This input is required.                                                                                                                                                         |

| OSC                         | 104       | 1    | <b>CLOCK-IN</b> : This is an input from a multifrequency clock source or 14.318-MHz crystal.                                                                                                                                                                      |

| CLKSEL[3:0]                 | 105:108   | i/O  | <b>CLOCK SELECT</b> : These are inputs from external oscillators or outputs to a multifrequency synthesizer.                                                                                                                                                      |

| SQCLK                       | 109       | 1    | VIDEO MEMORY SEQUENCER CLOCK.                                                                                                                                                                                                                                     |

| R                           | 67        | AO   | ANALOG RED.                                                                                                                                                                                                                                                       |

| G                           | 70        | AO   | ANALOG GREEN.                                                                                                                                                                                                                                                     |

| В                           | 71        | AO   | ANALOG BLUE.                                                                                                                                                                                                                                                      |

| BIOS-A[13:15]               | 79, 78, 1 | 76 O | BIOS ADDRESS 13-15.                                                                                                                                                                                                                                               |

| BIOS-ROMEN*/SSCLK           | 80        | I/O  | <b>BIOS-ROM ENABLE</b> : This is used to enable C000 BIOS<br>ROM if the CL-GD6410 is used in an adapter card applica-<br>tion. <b>SCREEN-SAVE CLOCK</b> : This input is used to detect<br>keyboard activity for Standby Mode in E000 motherboard<br>applications. |

| April 1993                  |           |      | ДАТА ВООК 9                                                                                                                                                                                                                                                       |

### 2.1 Pin Assignment Table (cont.)

| Name            | Pin No.                          | Туре | Description                     |  |

|-----------------|----------------------------------|------|---------------------------------|--|

| IREF            | 72                               | Al   | RAMDAC CURRENT REFERENCE.       |  |

| AVSS            | 73                               | PW   | RAMDAC ANALOG V <sub>SS</sub> . |  |

| AVDD            | 66                               | PW   |                                 |  |

| V <sub>CC</sub> | 40, 77<br>132, 149               | PW   | V <sub>CC</sub> PINS.           |  |

| GND             | 127, 155<br>56, 29,<br>81, 91, 1 |      | GND PINS.                       |  |

### 3. FUNCTIONAL DESCRIPTION

### 3.1 Functional Operation

The CL-GD6410 interfaces with the host processor, video memory, display device, and other external I/O. The host memory interface may be either 8- or 16-bit. Video memory interface is optimized for 256K bytes. The CL-GD6410 is AT bus-compatible to 10 MHz. Because the CL-GD6410 has a demultiplexed address and data bus, most systems will be able to interface it directly — without the addition of bus-interface buffers.

Flat-panel display devices supported will typically be 640 x 480-resolution monochrome STN or color TFT LCD panels. These panels are supported by a direct interface, precluding the need for buffers. Different-resolution displays can be used if the VGA BIOS is modified to support non-standard panel resolutions. Direct-power sequencing is supported for panels that require it.

CRT displays supported are PS/2<sup>™</sup> VGAcompatible analog monitors, including the IBM 85XX families, and multifrequency analog monitors, including the NEC<sup>®</sup> Multisync<sup>™</sup> families. The CL-GD6410 also interfaces with the Cirrus Logic CL-GD6340 Color LCD Interface Controller for the best possible color support on a wide variety of color panels.

A PS/2-compatible RAMDAC, necessary to accomplish a VGA design, is built into the CL-GD6410. This allows savings in both power consumption and space requirements. The RAMDAC is fully compatible, and is fully supported by the CL-GD6410 enhanced power-management features.

The four major operations supported by the CL-GD6410 are:

- Host Access to CL-GD6410 Registers

- Host Access to Video Memory

- Memory Refresh

- Display Refresh

### Host Access to Registers

The host processor is typically a minimum 8088- or 80X86-type microprocessor in a PC/XT/AT buscompatible environment and can access the CL-GD6410 Registers by setting up a 24-bit address and generating IORD\*, IOWR, MEMR\* and MEMW\* Signals. Memory reads and writes can be 8- or 16-bit; I/O reads and writes are 8-bit.

DRAM and screen-refresh activities occur concurrently and independently. The registers that may be accessed by the host are listed in Section 4. They include all of the standard VGA registers.

All registers have been made host-readable and writable to allow BIOS and driver software to determine the state of the video controller, allowing it to be readily switched and restored in multi-tasking and windowing environments.

### Host Access to Video Memory

Host access to video memory is channeled via the CL-GD6410. The host must establish the proper address/data/timing parameters in the CL-GD6410 Registers to transfer to and from video memory.

The CL-GD6410 also contains an intelligent sequencer that allocates Video Memory Cycles not only to the host, but also to the DRAM Refresh and the Display CRT Controllers.

#### Memory Refresh

Memory bandwidth is allocated to each process according to the actual real-time needs of the process, ensuring efficient use of the available bandwidth. In the case of a CRT display device, the display is blanked during horizontal and vertical-retrace intervals, opening memory bandwidth for host access and/or memory refresh.

Unlike early VGA implementations that gave the host only 14% of memory cycles, the CL-GD6410 can give the host from 25-50% access to video memory, or one out of two memory cycles. This is largely due to the sequencing strategy.

April 1993

DATA BOOK

#### Display Refresh

In bit-mapped graphics modes, and text modes, pixel data is latched into the CL-GD6410, transferred to Shift Registers, and shifted-out upon translation through the CL-GD6410 self-contained color-palette registers and RAMDAC.

The CL-GD6410 tracks the active and unused areas of the screen and cursor positions and consequently supplies screen control signals: VSYNC, HSYNC, and BLANK\*.

When the CL-GD6410 is connected to a dual-scan LCD display, an additional 64K x 4 DRAM is needed. The Frame-Accelerator is used for splitpanel data formatting. The reconstituted data from the Frame-Accelerator and video memory is then supplied in parallel to the LCD 4-bit upper and lower panel data buses. This technique not only maintains display contrast, but also reduces the power consumption of the video circuitry. The panel-frame rate is twice the rate that the data is fetched from video memory.

#### 3.2 CRT Display Modes

The CL-GD6410 includes all registers and data paths required for VGA compatibility. VGA enhancements include 16 simultaneously loadable text fonts (twice the capability of IBM VGA), and readable registers.

Extended graphics resolutions beyond the 640 x 480 IBM VGA standard are available. Using multiple-frequency monitors, such as the NEC Multi-Sync or Sony<sup>®</sup> MultiScan<sup>TM</sup>, 800 x 600 Mode with a 4:3 aspect ratio can be displayed.

High-resolution text modes offer from 100 columns by 30 rows up to 132 columns by 60 rows. 100 columns by 30 rows can be displayed on 640 x 480 flat panels.

#### 3.3 Flat Panel Display Modes

The CL-GD6410 will directly drive all of the popular monochrome dual-panel/dual-scan LCD panels. Proprietary techniques minimize flicker, noise, and pattern motion while enhancing contrast within the grayscales being used. Grayscaling is accomplished by modulating the ON-to-OFF time of individual pixels in the panel, and allowing the eye to integrate the superposed pixels to 16-perceptible grayscales. Flicker is eliminated by proprietary techniques involving distribution of time between ON and OFF pixels during frame modulation.

The CL-GD6410 allows the full spectrum of PC applications written for analog monitors and various video modes to run on standard 640 x 480 flat panels. This is accomplished through color emulation, attribute remapping, and resolution mapping.

In addition, summing circuitry allows rapid generation of IBM-compatible grayscale equivalents of color images. Up to 64 grayscale levels are available by using proprietary two-dimensional stippling logic. This technique permits all applications that generate monochrome, 4-, 16-, or 256-color images to be run on a monochrome flat-panel display.

Cirrus Logic AutoMap™ Logic can map 256 colors into a monochrome image; the colors then appear in 64 shades. The hardware-based algorithm tracks the particular palette map being used by the internal RAMDAC. RAMDAC data may be stored, as desired by the application, in orderly or random sequences. Realistic renditions of color images are not affected.

In color-text modes, foreground and background attributes can be automatically remapped to black and white for maximum contrast. Positive or negative raster may be selected under program control to match the visual qualities of the display and/or needs of the application.

The video resolutions that an application has selected are remapped to a flat panel according to whether Compatibility Mode, Compression Mode, or Expanded Mode was selected.

April 1993

DATA BOOK

\_\_\_\_\_

### 3.4 Intelligent Power Management and Sequencing

Notebook and laptop PCs have stringent power limitations due to battery operation and heat dissipation. To meet these needs, the CL-GD6410 is manufactured using low-power CMOS technology. In addition, the CL-GD6410 has programmable output pins as well as other intelligent power management features that permit the controller to enter four possible power-conserving modes, which are discussed below:

#### Normal Mode

- · Power to LCD panel and full screen refresh

- CPU access to Video Memory

- · Refresh to Video Memory

- CPU access to RAMDAC

- · CPU access to I/O Registers

Since power consumption is directly proportional to the frequency at which the controller is run, the CL-GD6410 uses a proprietary Frame-Accelerator to maintain the maximum screen refresh rate, while the clock to the CL-GD6410 functions at 25 MHz or less. The Frame-Accelerator is used only with dual-scan LCD panels.

### Standby Mode

- No power to LCD panel and no screen refresh

- Panel power sequencing is observed

- CPU access to Video Memory

- Refresh to Video Memory

- CPU access to RAMDAC

- · CPU access to I/O Registers

- Frequency Synthesizer is not powered-down

The primary power savings in this mode comes from reducing power to the LCD panel only. Since there is no screen refresh, normal clock rates are not required and may be replaced by slower clock rates to further reduce power consumption. The input pin SSCLK (Screen-Save-Clock) detects any keyboard activity. Any RAMDAC I/O can be executed. The system will recover from Standby Mode after receiving stimuli in the form of video memory read or write accesses, or the presence of the SSCLK Signal. If power sequencing is in progress, then the CL-GD6410 will allow the se-

quencing to complete before exiting from Standby Mode.

The CL-GD6410 contains a power-save timer that allows it to be programmable, in increments of 1 minute, up to 63 minutes. If the feature is enabled, this is the time-out time from the last stimuli to automatically switch to Standby Mode. The timer can be activated by either the SSCLK Signal or by CPU memory access (read or write).

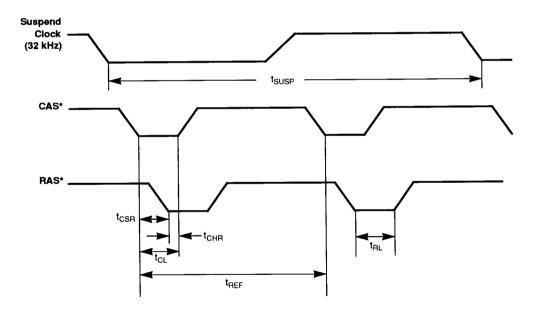

#### Suspend Mode

- · No power to LCD panel and no screen refresh

- Panel power sequencing is observed

- No CPU access to Video Memory

- Refresh to Video Memory continues but using a 32-kHz clock

- No CPU access to RAMDAC

- No CPU access to I/O Registers

- Frequency Synthesizer is powered-down

The power savings in this mode occurs because host access to video memory is now denied and a slower clock is used. This slow clock refreshes video memory by performing CAS\*-before-RAS\* refresh. With slow-refresh DRAM, a clock running as slow as 32 kHz can be used. Other than this refresh logic, the rest of the CL-GD6410 does not have clocks, reducing power consumption even further.

Suspend Mode can be activated or deactivated, under program control, by a sequence of three consecutive I/O writes to the 'active' IBM VGAcompatible 'Sleep' Port (46E8H or 3C3H).

### Shutdown

No power to LCD panel

Prior to initiating a system-wide shutdown, the video-subsystem state can be saved by the system itself for later restoration. The CL-GD6410 allows the system to save or restore the status of all Controller Registers.

The CL-GD6410 can operate at  $5V \pm 10\%$ . With this range, a substantial power savings can be realized by designing for 4.5V operation.

April 1993

Several dedicated pins have been assigned to facilitate power management. The PWG Signal (Power Good) can be used to signify the beginning of a power-on or power-off sequence. The FPVCC and FPVEE Signals can be used to control panel logic power and panel backlight/contrast, when a panel requires that these functions be sequenced or controlled.

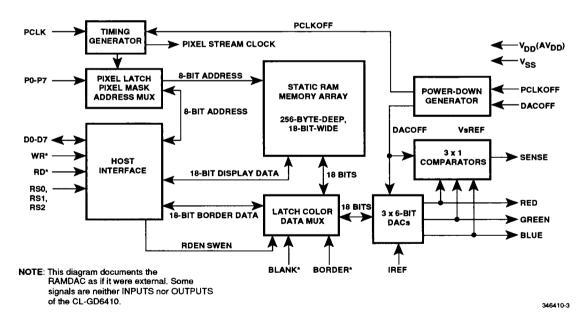

### 3.5 Internal RAMDAC

The CL-GD6410 includes an on-chip, high-speed, memory digital-to-analog converter known as a RAMDAC. The RAMDAC circuitry helps the CL-GD6410 process color-video signals and timing information to the display.

The RAMDAC includes a 256-entry by 18-bit word color lookup table, three 6-bit digital-to-analog converters (DACs), a Pixel Mask Register, and a Border Color Register.

An 8-bit address value applied on the Pixel Address Inputs defines the memory location for reading an 18-bit color data word from the color lookup table. This data is partitioned as three fields of six bits each — one for R, one for G, and one for B and then applied to the individual DAC Inputs.

A pixel word mask is incorporated to allow the incoming pixel address to be altered, permitting changes to the color lookup table contents to be made immediately. This feature allows special display operations such as flashing objects and overlays to be created.

The color lookup table contents are accessed via its 8-bit-wide host interface. An internal synchronizing circuit allows the color value accesses to be completely asynchronous to the pixel video operation.

Figure 3–1. RAMDAC Block Diagram

14

DATA BOOK

#### RAMDAC Video Operation

In video operation, pixel addresses P0 through P7, BLANK\* and BORDER\* are sampled on the rising edge of the Pixel Clock (PCLK). Their effect appears at the DAC Outputs after three further rising edges of PCLK.

Both BLANK\* and BORDER\* are active-low signals. When the BLANK\* Input is low, a binary 0 is applied to the DAC Inputs, producing a zero-volt DAC Output. When the BORDER\* Input is low, the color data from the Border Color Register is applied to the DAC Inputs.

The DACOFF\* Input is both a display disable control and a DAC power-down control. When DACOFF\* is low, the DACs in the RAMDAC are totally inoperative, which results in the power dissipation being reduced to standby minimum. During this time, the three DAC Outputs are at a zero-volt level. When DACOFF\* goes high, several PCLK Cycles are required before the DACs in the RAMDAC will function properly.

#### Analog Outputs

The DAC outputs are designed to produce 0.7-volt peak white amplitude with a reference current ( $I_{REF}$ ) of 6.7 mA when driving a doubly-terminated 75-ohm load, which corresponds to an effective DAC Output load of 37.5 ohms ( $R_{effective}$ ).

For all values of IREF and output loading:

V<sub>blacklevel</sub> = 0 volts

#### Writing to the Color Lookup Table

To write a color definition to the lookup table, a value specifying an address location in the lookup table is first written to the Write Mode Address Register. The color values for the red, green, and blue intensities are then written in succession to the Color Value Register. After the blue data is latched, this new color data is then written into the lookup table at the defined address, and the Address Register is incremented automatically.

Since Address Register increments after each transfer of data to the lookup table, it is best to write a set of consecutive locations at once. The

April 1993

start address of the set of locations is first written to the Write Address Mode Register. The color data for each address location is then sequentially written to the Color Value Register. The RAMDAC automatically writes data to the lookup table, and increments the Address Register after each host transfer of three bytes of color data.

#### Reading from the Color Lookup Table

To read color data from the lookup table, a value specifying the address location of the data is written to the Read Mode Address Register. After the address is latched, the data from this location is automatically read out to the Color Value Register, and the Address Register automatically increments.

The color intensity values are then read from the Color Value Register by the sequence of three read (RD\*) commands. After the blue value is transferred out, new data is read from the lookup table at the current address to the Color Value Register, and the Address Register to automatically increment again.

If the Address Register is loaded with a new starting address while an unfinished sequence is in progress, the system resets and starts a new sequence. This occurs for both read and write operations.

3.6 CL-GD6410 Configuration

The CL-GD6410 provides several configuration options. These options are set by installing 'pull-up' or 'pull-down' resistors on certain CL-GD6410 pins that are sampled at system reset.

NOTE: The CL-GD6410-A needs configuration resistors to establish either 'high' or 'low' conditions. The CL-GD6410-B has internal pull-down resistors; it requires pull-up resistors to establish other than default (low) values.

The configurations need to be made only once. All listed connections are required.

| Pin Name (and No.)                        | Function                                                                             | Notes                                                                                                                                                               |       |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| M0D[2]/PD3 (124)                          | Reserved                                                                             | Low to maintain compatibility with future<br>CL-GD64XX VGA controllers. (Only needs to be<br>set on the CL-GD6410-A.)                                               |       |  |  |  |

| FRA5/PD1 (5)                              | Reserved                                                                             | Low to maintain compatibility with future<br>CL-GD64XX VGA controllers. (Only needs<br>set on the CL-GD6410-A.)                                                     | to be |  |  |  |

| FRA4/PUD0 (4)                             | BIOS Support<br>High = BIOS @ C000; Low = E000                                       | Low for motherboard implementations when<br>the desired BIOS is at E000. Pull high for<br>adapter implementations or when the BIOS<br>is at C000.                   |       |  |  |  |

| FRA6/PD2 (6)                              | VGA Address Space<br>High = Yxx (I/O)/Yxxx (memory)<br>Low = 3xx (I/O)/Axxx (memory) | Low in most cases. Pulling high allows for a non-DOS environment.                                                                                                   |       |  |  |  |

| FRA7/PUD3 (7)                             | Sleep Mode I/O Address<br>High = 46E8h; Low = 3C3h                                   | Normally high for adapter controller<br>implementations; low for motherboard<br>implementations.                                                                    |       |  |  |  |

| FRA8/PUD4 (8)                             | BIOS Width Select<br>High = 16-bit BIOS; Low = 8-bit                                 | Defines BIOS-to-controller interface.                                                                                                                               |       |  |  |  |

| PD7 (3)                                   | DIR Configuration<br>High = Reserved; Low = DIR                                      | When buffers are required by the design, the this signal should be pulled low to allow Pi to control buffer devices.                                                |       |  |  |  |

| FRAD0/SW3 (111)<br>and FRAD1/SW2<br>(112) | Reserved                                                                             | No connection required.                                                                                                                                             |       |  |  |  |

| FRAD2/SW1 (113)<br>and FRAD3/SW0<br>(114) | Panel Class                                                                          | SW1         SW0         Panel Class           0         0         0           0         1         1           1         0         2           1         1         3 |       |  |  |  |

DATA BOOK

<sup>16</sup>

**CL-GD6410** Notebook VGA Controller

### 4. VIDEO MODES

### 4.1 CRT Video Modes

### Table 4–1. IBM<sup>®</sup> Standard VGA Video Modes

| Mode<br>No. | Number<br>of<br>Colors | Char.<br>x Row | Char.<br>Cell | Screen<br>Format | Display<br>Mode | Dot<br>Clock<br>(MHz) | Horiz.<br>Freq.<br>(kHz) | Vert.<br>Freq.<br>(Hz) | Monitor<br>Supported |

|-------------|------------------------|----------------|---------------|------------------|-----------------|-----------------------|--------------------------|------------------------|----------------------|

| 0, 1        | 16/256K                | 40 x 25        | 9 x 16        | 360 x 400        | Text            | 28                    | 31.5                     | 70                     | All                  |

| 2, 3        | 16/256K                | 80 x 25        | 9 x 16        | 720 x 400        | Text            | 28                    | 31.5                     | 70                     | All                  |

| 4, 5        | 4/256K                 | 40 x 25        | 8 x 8         | 320 x 200        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

| 6           | 2/256K                 | 80 x 25        | 8 x 8         | 640 x 200        | Graphics        | 25                    | 31.5                     | 70                     | Ali                  |

| 7           | Mono.                  | 80 x 25        | 9 x 16        | 720 x 400        | Text            | 28                    | 31.5                     | 70                     | Ali                  |

| d           | 16/256K                | 40 x 25        | 8 x 8         | 320 x 200        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

| e           | 16/256K                | 80 x 25        | 8 x 14        | 640 x 200        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

| f           | Mono.                  | 80 x 25        | 8 x 14        | 640 x 350        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

| 10          | 16/256K                | 80 x 25        | 8 x 14        | 640 x 350        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

| 11          | 2/256K                 | 80 x 30        | 8 x 16        | 640 x 480        | Graphics        | 25                    | 31.5                     | 60                     | All                  |

| 12          | 16/256K                | 80 x 30        | 8 x 16        | 640 x 480        | Graphics        | 25                    | 31.5                     | 60                     | All                  |

| 13          | 256/256K               | 40 x 25        | 8 x 8         | 320 x 200        | Graphics        | 25                    | 31.5                     | 70                     | All                  |

Table 4-2. Cirrus Logic Extended CRT Video Modes

| Mode<br>No. | Number<br>of<br>Colors | Char.<br>x Row | Char.<br>Cell | Screen<br>Format | Display<br>Mode | Dot<br>Clock<br>(MHz) | Horiz.<br>Freq.<br>(kHz) | Vert.<br>Freq.<br>(Hz) | Monitor<br>Supported |

|-------------|------------------------|----------------|---------------|------------------|-----------------|-----------------------|--------------------------|------------------------|----------------------|

| 41          | 16/256K                | 100 x 50       | 8 x 8         | 800 x 400        | Text            | 32                    | 31.5                     | 60                     | Ali                  |

| 42          | 16/256K                | 100 x 60       | 8 x 8         | 800 x 480        | Text            | 32                    | 31.5                     | 70                     | All                  |

| 43          | 16/256K                | 100 x 25       | 8 x 16        | 800 x 400        | Text            | 32                    | 31.5                     | 60                     | All                  |

| 51          | 16/256K                | 132 x 50       | 8 x 8         | 1056 x 400       | Text            | 32                    | 25                       | 60                     | Multifrequency       |

| 52          | 16/256K                | 132 x 60       | 8 x 8         | 1056 x 480       | Text            | 32                    | 25                       | 50                     | Multifrequency       |

| 53          | 16/256K                | 80 x 60        | 8 x 8         | 640 x 480        | Text            | 25                    | 31.5                     | 60                     | All                  |

| 54          | 16/256K                | 132 x 25       | 8 x 16        | 1056 x 400       | Text            | 32                    | 25                       | 60                     | Multifrequency       |

| 64, 6a      | 16/256K                | 100 x 37       | 8 x 16        | 800 x 600        | Graphics        | 32                    | 31.5                     | 53                     | Multifrequency       |

\_\_\_\_\_

### 4.2 LCD Video Modes

### Table 4–3. IBM Standard VGA Video Modes

| Mode<br>No. | Mono.<br>STN<br>Number<br>of<br>Shades | Color<br>TFT<br>Number<br>of<br>Colors | CRT<br>Number<br>of<br>Colors | Char. x<br>Row | Char.<br>Ceil | Screen<br>Format | Expanded<br>Char. Cell | Expanded<br>Size | Display<br>Mode |

|-------------|----------------------------------------|----------------------------------------|-------------------------------|----------------|---------------|------------------|------------------------|------------------|-----------------|

| 0, 1        | 16/16                                  | 16/185K                                | 16/256K                       | 40 x 25        | 9 x 16        | 360 x 400        | 16 x 19                | 640 x 475        | Text            |

| 2, 3        | 16/16                                  | 16/185K                                | 16/256K                       | 80 x 25        | 9 x 16        | 720 x 400        | 8 x 16                 | 640 x 475        | Text            |

| 4, 5        | 4/64                                   | 4/185K                                 | 4/256K                        | 40 x 25        | 8 x 8         | 320 x 200        | NA                     | 640 x 475        | Graphics        |

| 6           | 2/16                                   | 2/185K                                 | 2/256K                        | 80 x 25        | 8 x 8         | 640 x 200        | NA                     | 640 x 475        | Graphics        |

| 7           | 2/16                                   | 2/185K                                 | Mono.                         | 80 x 25        | 9 x 16        | 720 x 400        | 8 x 19                 | 640 x 475        | Text            |

| d           | 16/64                                  | 16/185K                                | 16/256K                       | 40 x 25        | 8 x 8         | 320 x 200        | NA                     | 640 x 475        | Graphics        |

| e           | 16/16                                  | 16/185K                                | 16/256K                       | 80 x 25        | 8 x 14        | 640 x 200        | NA                     | 640 x 475        | Graphics        |

| f           | 2/16                                   | 2/185K                                 | Mono.                         | 80 x 25        | 8 x 14        | 640 x 350        | NA                     | 640 x 475        | Graphics        |

| 10          | 16/16                                  | 16/185K                                | 16/256K                       | 80 x 25        | 8 x 14        | 640 x 350        | NA                     | 640 x 475        | Graphics        |

| 11          | 2/16                                   | 2/185K                                 | 2/256K                        | 80 x 25        | 8 x 16        | 640 x 480        | NA                     | 640 x 480        | Graphics        |

| 12          | 16/16                                  | 16/185K                                | 16/256K                       | 80 x 25        | 8 x 16        | 640 x 480        | NA                     | 640 x 480        | Graphics        |

| 13          | 64/64                                  | 256/185K                               | 256/256K                      | 40 x 25        | 8 x 8         | 320 x 200        | NA                     | 640 x 475        | Graphics        |

Table 4-4. Cirrus Logic Extended LCD Video Mode

| Mode<br>No. | Mono.<br>STN<br>Number<br>of<br>Shades | Color<br>TFT<br>Number<br>of<br>Colors | CRT<br>Number<br>of<br>Colors | Char. x<br>Row | Char.<br>Cell | Screen<br>Format | Expanded<br>Char. Cell | Expanded<br>Size | Display<br>Mode |

|-------------|----------------------------------------|----------------------------------------|-------------------------------|----------------|---------------|------------------|------------------------|------------------|-----------------|

| 63          | 16/16                                  | 16/185K                                | 16/256K                       | 80 x 60        | 8 x 8         | 640 x 480        | 8 x 8                  | 640 x 480        | Text            |

### 5. ELECTRICAL SPECIFICATIONS

### 5.1 Absolute Maximum Ratings

| Ambient temperature under bias            | 0° C to 70° C                      |

|-------------------------------------------|------------------------------------|

| Storage temperature                       |                                    |

| Voltage on any pin with respect to ground | 0.5 to V <sub>CC</sub> + 0.5 Volts |

| Operating power dissipation               |                                    |

| Standby power dissipation                 |                                    |

| Suspend power dissipation                 |                                    |

| Power supply voltage                      |                                    |

| Injection current (latch-up)              |                                    |

NOTE: Stresses above those listed may cause permanent damage to system components. These are stress ratings only. Functional operation at these or any conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect system reliability.

April 1993

### 5.2 CL-GD6410 DC Specifications (Digital)

(V<sub>CC</sub> = 5V  $\pm$  10%; T<sub>A</sub> = 0° to 70° C, unless otherwise specified)

| Symbol           | Parameter                | MIN  | MAX                   | Units | Conditions                            |

|------------------|--------------------------|------|-----------------------|-------|---------------------------------------|

| V <sub>CC</sub>  | Power Supply Voltage     | 4.50 | 5.50                  | V     | Normal Operation                      |

| V <sub>IL</sub>  | Input Low Voltage        | 0    | 0.8                   | v     |                                       |

| V <sub>IH</sub>  | Input High Voltage       | 2.0  | V <sub>CC</sub> + 0.5 | V     |                                       |

| VIHC             | Input High Voltage CMOS  | 3.0  | V <sub>CC</sub> - 0.7 | v     |                                       |

| VILC             | Input Low Voltage CMOS   |      | 0.6                   | v     |                                       |

| V <sub>OHC</sub> | Output High Voltage CMOS | 3.5  |                       | v     | l <sub>OHC</sub> = -200 μA            |

| Volc             | Output Low Voltage CMOS  |      | 0.4                   | v     | i <sub>OLC</sub> = 3.2 mA             |

| V <sub>OH</sub>  | Output High Voltage      | 2.4  |                       | v     | l <sub>OHC</sub> = -200 μA            |

| V <sub>OL</sub>  | Output Low Voltage       |      | 0.5                   | v     | I <sub>OLC</sub> = 3.2 mA             |

| I <sub>cc</sub>  | Operating Supply Current |      | 180                   | mA    | 5V nominal<br>SimulSCAN               |

| ۱ <sub>L</sub>   | Input Leakage            | -10  | 10                    | μA    | $0 < V_{IN} < V_{CC}$                 |

| loz              | Input Leakage            | -10  | 10                    | μA    | 0 < V <sub>IN</sub> < V <sub>CC</sub> |

| C <sub>IN</sub>  | Input Capacitance        |      | 10                    | pF    |                                       |

| C <sub>OUT</sub> | Output Capacitance       |      | 10                    | pF    |                                       |

NOTES:

$I_{OL}$  MAX for CRTINT = 12 mA.

$I_{OL}$  MAX for CPU DATA, DIR, WE\*, CAS\* = 8 mA.

I<sub>OL</sub> MAX for LCD Control Signals = 4 mA (LCD Control Signals = FPVDCLK, LLCLK, MOD, and LFS).

I<sub>CCpd</sub> — The actual current in Power Down Modes will vary depending on the implementation of the system environment. For information on system implementation of Power Down Modes, refer to application notes.

20

<sup>1)</sup> I<sub>OI</sub> MAX for IOCHRDY, MEMCS16\* = 24 mA.

### 5.3 CL-GD6410 DC Specifications (RAMDAC)

(V<sub>CC</sub> = 5V  $\pm$  10%; TA = 0° to 70° C, unless otherwise specified)

| Symbol                            | Parameter                | MIN  | MAX  | Units | Conditions        |

|-----------------------------------|--------------------------|------|------|-------|-------------------|

| V <sub>CC</sub> /AV <sub>DD</sub> | Power Supply Voltage     | 4.50 | 5.50 | V     | Normal Operations |

| I <sub>REF</sub>                  | DAC Reference Current    | -6.7 | -10  | mA    | Notes 1 and 2     |

| I <sub>DD</sub>                   | Operating Supply Current |      | 100  | mA    | Note 3            |

#### NOTES:

1) Reference currents below the minimum specified may cause the analog output to become invalid.

2) The pixel clock frequency must be stable for a period of 20 µs after power-up before proper device operation.

I<sub>DD</sub> is dependent upon the digital output loading and pixel clock rate. The value specified is with the outputs unloaded and the pixel clock frequency equal to 32 MHz.

### 5.4 DAC Characteristics

| Parameter                | MIN                                                         | MAX                                                                    | Units                                                                                             | Conditions                                                        |

|--------------------------|-------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Resolution               | 6                                                           |                                                                        | Bits                                                                                              |                                                                   |

| Output Voltage           |                                                             | 0.75                                                                   | V                                                                                                 | IO < 10 mA                                                        |

| Output Current           |                                                             | -21                                                                    | mA                                                                                                | Vo < 1V                                                           |

| Rise Time                |                                                             | 8                                                                      | ns                                                                                                | Note 1                                                            |

| Full-scale settling time |                                                             | 30                                                                     | ns                                                                                                | Notes 1 and 2                                                     |

|                          | Resolution<br>Output Voltage<br>Output Current<br>Rise Time | Resolution     6       Output Voltage     0       Output Current     6 | Resolution     6       Output Voltage     0.75       Output Current     -21       Rise Time     8 | Resolution6BitsOutput Voltage0.75VOutput Current-21mARise Time8ns |

### NOTES:

1) Load = 37.5 ohms and 30 pF, and  $I_{REF}$  = -6.7 mA.

2) From a 2% change in output voltage until settling within 2% of the final value.

### 6. AC TIMING CHARACTERISTICS

This section includes system timing requirements for the CL-GD6410. Timings are provided in nanoseconds (ns), at TTL input levels, with the ambient temperature varying from 0° to 70° C, and  $V_{CC}$  varying from 4.50 to 5.50V DC. The AT-bus speed is10 MHz unless otherwise noted. Note that (\*) denotes an active-low signal. Also note the following.

- 1. All timings assume a load of 50 pF.

- 2. TTL signals are measured at TTL threshold; CMOS signals are measured at CMOS threshold.

- 3. On power-up, all DRAM interface signals are inactive. Memory data bus is in Input Mode to sense values on configuration option pins set by pull-up or pull-down resistors.

- 4. The CL-GD6410 executes eight RAS\*-only cycles to initialize DRAMs before executing normal cycles.

\_\_\_\_\_

### 6.5 Index of Timing Information

| Table | Title                                                 | Page |

|-------|-------------------------------------------------------|------|

| 6–1   | I/O Write Timing (ISA Bus)                            | 24   |

| 6–2   | I/O Read Timing (ISA Bus)                             | 25   |

| 6–3   | Memory Write Timing (ISA Bus)                         | 26   |

| 64    | Memory Read Timing (ISA Bus)                          | 27   |

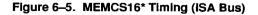

| 6–5   | MEMCS16* Timing (ISA Bus)                             | 28   |

| 6–6   | BALE Timing (ISA Bus)                                 | 29   |

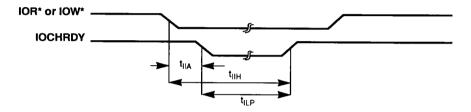

| 6–7   | IOCHRDY Timing for Memory Access (ISA Bus)            | 30   |

| 68    | IOCHRDY Timing for I/O Access (ISA Bus)               | 31   |

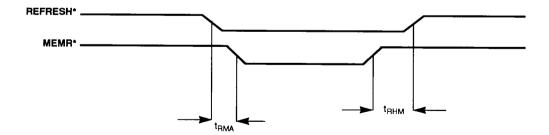

| 69    | REFRESH* Timing (ISA Bus)                             | 31   |

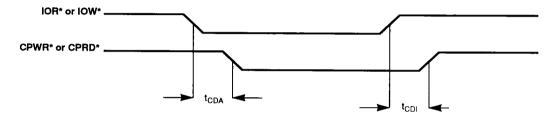

| 6–10  | CPWR*/CPRD* Timing (ISA Bus)                          | 32   |

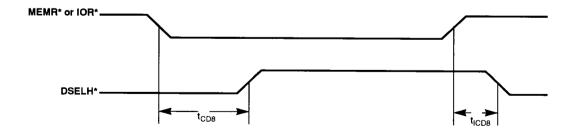

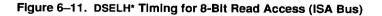

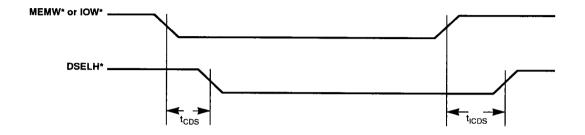

| 6–11  | DSELH* Timing for 8-Bit Read Access (ISA Bus)         | . 32 |

| 6–12  | DSELH* Timing for 16-Bit Memory Read Access (ISA Bus) | . 33 |

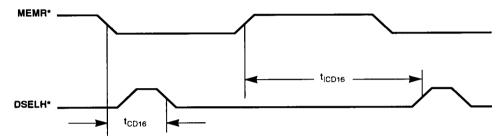

| 6-13  | DIR Timing for Read Access (ISA Bus)                  | 33   |

| 6–14  | DSELH* Timing for Write Access (ISA Bus)              | . 34 |

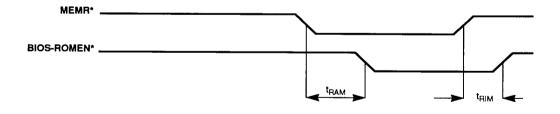

| 615   | BIOS-ROMEN* Timing (ISA Bus)                          | . 34 |

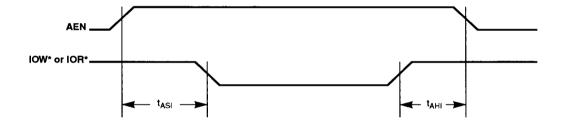

| 616   | AEN Timing (ISA Bus)                                  | . 35 |

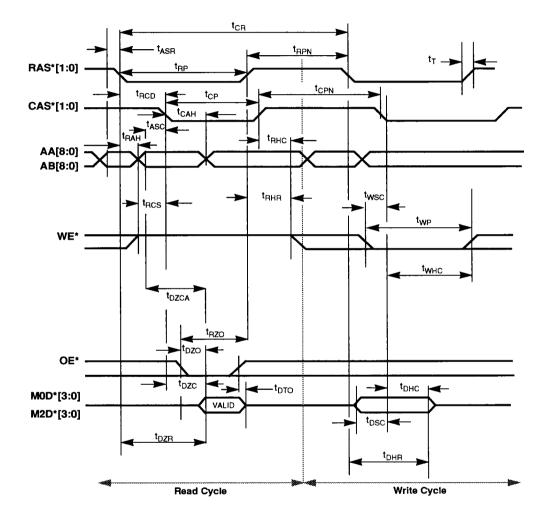

| 6–17  | Random Read/Write Cycle Timing                        | . 36 |

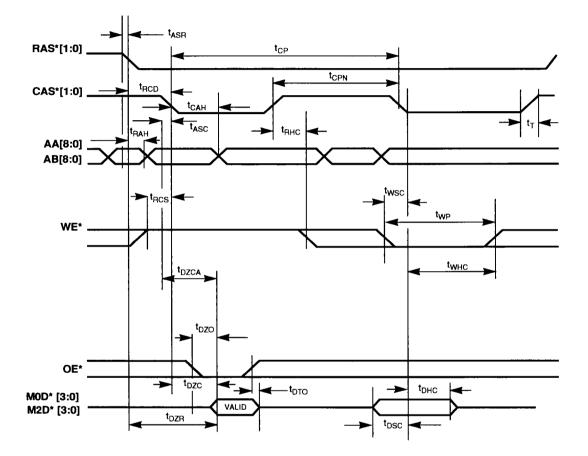

| 6–18  | Fast Page Mode Read/Write Cycle Timing                | . 38 |

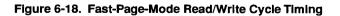

| 6–19  | CAS*-Before-RAS* Refresh Cycle Timing                 | . 40 |

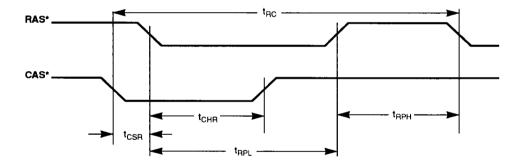

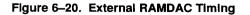

| 6–20  | External RAMDAC Timing                                | . 41 |

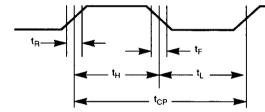

| 6–21  | Clocks                                                | . 42 |

| 6–22  | Sync, BLANK*, and RGB as Outputs (Internal VDCLK)     | . 44 |

| 6–23  | Suspend Mode Timing                                   | . 45 |

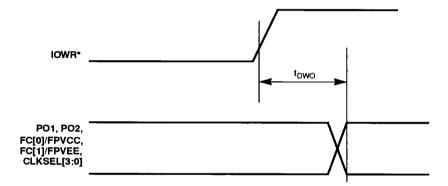

| 624   | Programmable Pins Output Timing                       | . 46 |

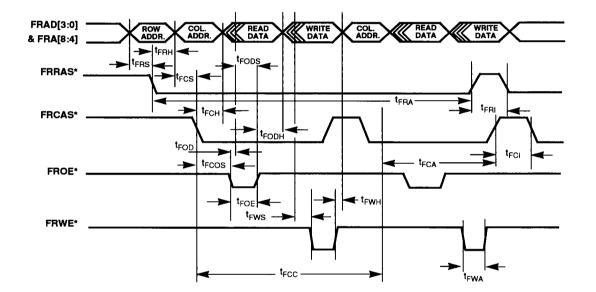

| 625   | Frame-Accelerator Interface Timing                    | . 47 |

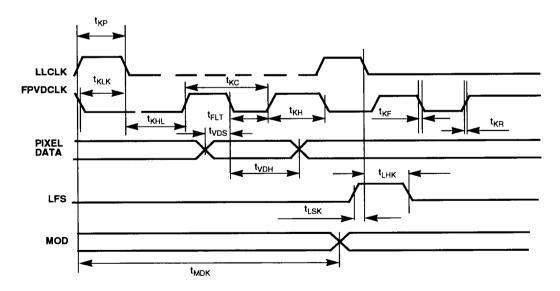

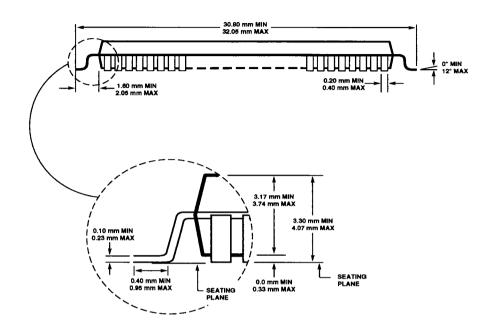

| 6–26  | Monochrome Dual-Scan Passive LCD Interface Timing     | . 49 |

| 627   | 512-Color LCD Interface Timing                        | . 50 |

April 1993

DATA BOOK

\_\_\_\_

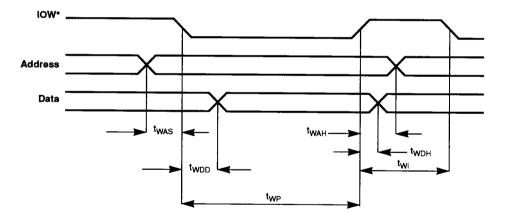

### Table 6-1. I/O Write Timing (ISA Bus)

| Symbol           | Parameter                            | MIN | MAX | Unit |

|------------------|--------------------------------------|-----|-----|------|

| twas             | Address to IOW* active setup         | 40  |     | ns   |

| twDH             | Data hold time from IOW* inactive    | 0   |     | ns   |

| t <sub>WAH</sub> | Address hold time from IOW* inactive | 0   |     | ns   |

| twod             | Data delay from IOW* active          |     | 0   | ns   |

| t <sub>WP</sub>  | IOW⁺ pulse width                     | 320 |     | ns   |

| t <sub>WI</sub>  | IOW* inactive to any command         | 100 |     | ns   |

#### NOTES:

- 1) AEN must be inactive (See Figure 6-16 for AEN timing).

- 2) See Figure 6-11 for DSELH\* timing.

- 3) See Figure 6-8 for IOCHRDY\* timing.

Figure 6–1. I/O Write Timing (ISA Bus)

DATA BOOK

## **CL-GD6410** Notebook VGA Controller

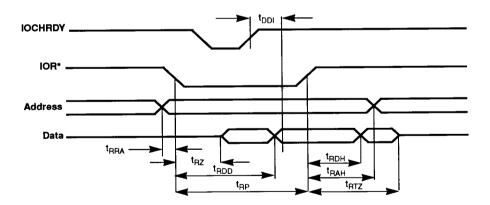

### Table 6-2. I/O Read Timing (ISA Bus)

| Symbol           | Parameter                         | MIN | MAX | Unit |

|------------------|-----------------------------------|-----|-----|------|

| t <sub>RRA</sub> | Address setup to IOR* active      | 10  |     | ns   |

| t <sub>RDH</sub> | Data hold time from IOR* inactive | 0   | 30  | ns   |

| t <sub>RAH</sub> | Address hold from IOR* inactive   | 0   |     | ns   |

| t <sub>RDD</sub> | Data delay from IOR* active       |     | 220 | ns   |