# Am81C451/458

**CMOS Color Palette**

### **PRELIMINARY**

### **DISTINCTIVE CHARACTERISTICS**

- Plug-in Replacement for Bt451 (Bt458)

- Available in 80-, 110-, 125-, 165-MHz versions Typical Power Dissipation: 1.0 W

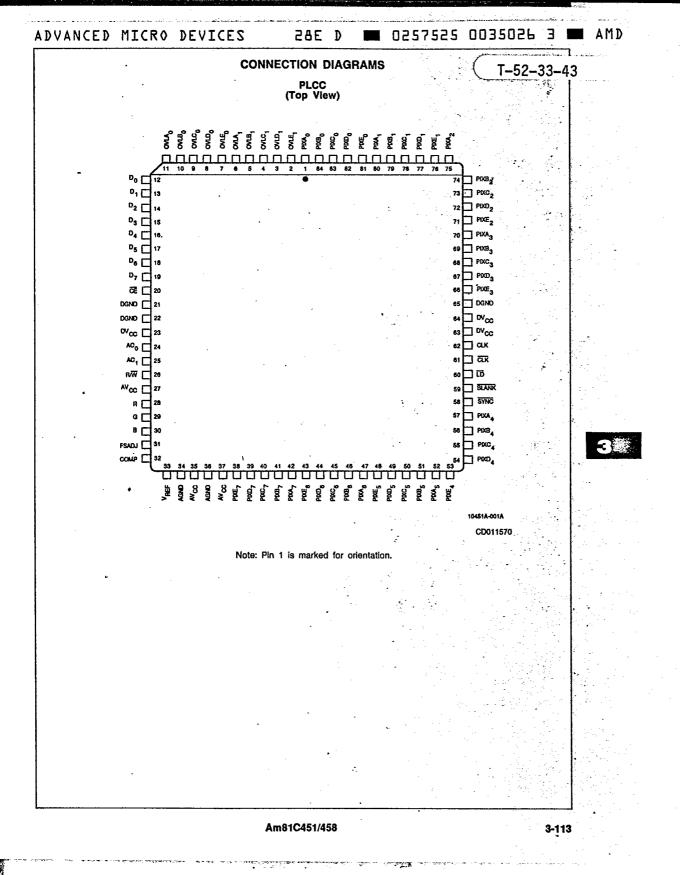

- Available in PGA and PLCC packages

- Multiplexed TTL Pixel Ports

- Triple 4-Bit (8-Bit) Digital-to-Analog Converters (DACs)

- 256 x 12(24) Dual-Port Color Palette RAM

- 4 x 12(24) Dual-Port Overlay RAM

- RS-343A-Compatible RGB Outputs

- Read and Blink Masks for each bit-plane

- Standard MPU Interface

- Single +5-V Power Supply

- Full military range specifications

### **GENERAL DESCRIPTION**

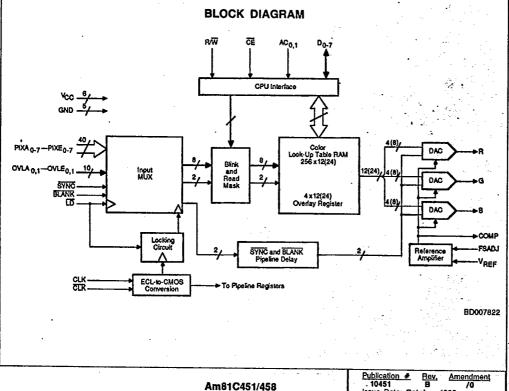

The Am81C451/458 CMOS Color Palette drives all three guns of a standard RS-343A color monitor. It is designed specifically for the high-resolution color graphics market for applications such as image processing, CAE/CAD/CAM, solid modeling, and animation. The Am81C451/458 operates at speeds sufficient to support monitor resolutions up to 1600 x 1280 pixels, and can simultaneously display 259 colors out of an available set of 4K colors for the Am81C451 and 16.8 million colors for the Am81C458.

The Am81C451/458 includes an input buffer, an input multiplexer, a 256 x 12(24) Look-Up Table, a 4 x 12(24) Overlay Table, and three 4-bit (8-bit) RS-343A-compatible DACs. It is available in versions with pixel rates as high as 165 MHz. It also contains programmable bit-plane Read and Blink Masks. Proprietary DAC decoding techniques minimize glitch energy and skew.

The Am81C451/458 minimizes the need for high-speed ECL signals on the PC board since there are only two inputs (CLK, CLK) that need to operate at pixel rate. Multiple pixel ports and internal multiplexing enables TTLcompatible interfacing to the Display Memory while maintaining the high pixel data rates on-chip.

The Am81C451/458 is fabricated using AMD's state-ofthe-art 1.2-micron CMOS process. The device is available in an 84-lead PGA package as well as a lower cost 84-pin PLCC package.

3-112

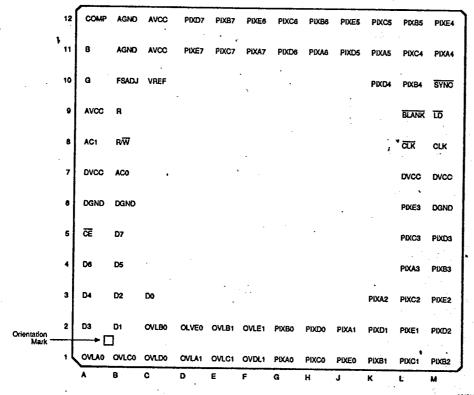

PGA\* Top View (Pins Facing Down)

CD011580

Please see PGA Pin Designations for pinout sorted by both Pin Names and Pin Numbers.

3-114

Am81C451/458

T-52-33-43

# PGA PIN DESIGNATIONS

(Sorted by Pin Name)

| Pin No. | Name            | Pin No. | Name              | Pin No. | Name              | Pin No. | Name              |

|---------|-----------------|---------|-------------------|---------|-------------------|---------|-------------------|

| B-7     | AC <sub>0</sub> | B-6     | DGND              | K-3     | PIXA <sub>2</sub> | E-11    | PIXC7             |

| A-8     | AC <sub>1</sub> | M-6     | DGND              | L-4     | PIXA <sub>3</sub> | H-2     | PIXD <sub>0</sub> |

| B-12    | AGND            | A-6     | DGND              | M-11    | PIXA <sub>4</sub> | K-2     | PIXD <sub>1</sub> |

| B-11    | AGND            | L-7     | DVCC              | K-11    | PIXA5             | M-2     | PIXD <sub>2</sub> |

| C-12    | AVCC            | A-7     | DVCC              | H-11    | PIXA6             | M-5     | PIXD3             |

| C-11    | AVCC            | M-7     | DVCC              | F-11    | PIXA <sub>7</sub> | K-10    | PIXD4             |

| A-9     | AVCC            | B-10    | FSADJ             | G-2     | PIXB0             | J-11    | PIXD5             |

| A-11    | В               | . A-10  | G                 | K-1     | PIXB <sub>1</sub> | G-11    | PIXD <sub>6</sub> |

| L-9     | BLANK           | M-9     | LD                | M-1     | PIXB <sub>2</sub> | D-12    | PIXO7             |

| A-5     | CE              | A-1     | OVLA <sub>0</sub> | M-4     | PIXB3             | J-1     | PIXE <sub>0</sub> |

| L-8     | CLK             | D-1     | OVLA <sub>1</sub> | L-10    | PIXB4             | L-2 ·   | PIXE <sub>1</sub> |

| M-8     | CLK             | C-2     | OVLB0             | L-12    | PIXB5             | M-3     | PIXE <sub>2</sub> |

| A-12    | COMP            | E-2     | OVLB <sub>1</sub> | H-12    | PIXB6             | L-6     | PIXE <sub>3</sub> |

| C-3     | D <sub>0</sub>  | B-1     | OVLC0             | E-1     | PIXB7             | M-12    | PIXE4             |

| B-2     | D <sub>1</sub>  | E-1     | OVLC <sub>1</sub> | H-1     | PIXC <sub>0</sub> | J-12    | PIXE <sub>5</sub> |

| 8-3     | D <sub>2</sub>  | C-1     | OVLD <sub>0</sub> | L-1     | PIXC <sub>1</sub> | F-12    | PIXE <sub>6</sub> |

| A-2     | D <sub>3</sub>  | F-1     | OVLD1             | L-3     | PIXC <sub>2</sub> | D-11    | PIXE <sub>7</sub> |

| A-3     | D <sub>4</sub>  | D-2     | OVLE <sub>0</sub> | L-5     | PIXC <sub>3</sub> | B-9     | R                 |

| B-4     | D <sub>5</sub>  | F-2     | OVLE <sub>1</sub> | L-11    | PIXC4             | B-8     | R/₩               |

| A-4     | D <sub>6</sub>  | G-1     | PIXA <sub>0</sub> | K-12    | PIXC5             | M-10    | SYNC              |

| B-5     | D <sub>7</sub>  | J-2     | PIXA <sub>1</sub> | G-12    | PIXC <sub>6</sub> | C-10    | VREF              |

T-52-33-43

# PGA PIN DESIGNATIONS (Cont'd.)

## (Sorted by Pin Number)

| Pin No.    | Name              | Pin No. | Name              | Pin No. | Name                | Pin No. | Name              |

|------------|-------------------|---------|-------------------|---------|---------------------|---------|-------------------|

| <b>A-1</b> | OVLA <sub>0</sub> | B-10    | FSADJ             | G-1     | PIXA <sub>0</sub>   | L-4     | PIXA <sub>3</sub> |

| A-2        | D <sub>3</sub>    | B-11    | AGND              | G-2     | PIXB <sub>0</sub>   | L-5     | PIXC <sub>3</sub> |

| A-3        | D <sub>4</sub>    | B-12    | AGND              | G-11    | PIXD <sub>6</sub>   | L-6     | PIXE <sub>3</sub> |

| A-4        | D <sub>6</sub>    | C-1     | OVLD <sub>0</sub> | G-12    | PIXC <sub>6</sub>   | L-7     | DVCC              |

| A-5        | CE                | C-2     | OVLB <sub>0</sub> | H-1     | , PIXC <sub>0</sub> | L-8     | CLK               |

| A-6        | DGND              | C-3     | D <sub>0</sub>    | H-2     | PIXD <sub>0</sub>   | L-9     | BLANK             |

| A-7        | DVCC              | C-10    | VREF              | H-11    | PIXA <sub>6</sub>   | L-10    | PIXB <sub>4</sub> |

| A-8        | AC <sub>1</sub>   | C-11    | AVCC              | H-12    | PIXB <sub>6</sub>   | L-11    | PIXC <sub>4</sub> |

| A-9        | AVCC              | C-12    | AVCC              | J-1     | PIXE <sub>0</sub>   | L-12    | PIXB <sub>5</sub> |

| A-10       | G                 | D-1     | OVLA <sub>1</sub> | J-2     | PIXA <sub>1</sub>   | M-1     | PIXB <sub>2</sub> |

| A-11       | 8                 | D-2     | OVLE <sub>0</sub> | J-11    | PIXD5               | M-2     | PIXO <sub>2</sub> |

| A-12       | COMP              | D-11    | PIXE <sub>7</sub> | J-12    | PIXE <sub>5</sub>   | M-3     | PIXE <sub>2</sub> |

| B-1        | OVLC <sub>0</sub> | D-12    | PIXD <sub>7</sub> | K-1     | PIXB <sub>1</sub>   | M-4     | PIXB <sub>3</sub> |

| B-2        | D <sub>1</sub>    | E-1     | OVLC <sub>1</sub> | K-2     | PIXD <sub>1</sub>   | M-5     | PIXD <sub>3</sub> |

| B-3        | D <sub>2</sub>    | E-2     | OVLB <sub>1</sub> | K-3     | PIXA <sub>2</sub>   | M-6     | DGND              |

| B-4        | D <sub>5</sub>    | E-11    | PIXC <sub>7</sub> | K-10    | PIXD <sub>4</sub>   | M-7     | DVCC              |

| B-5        | D <sub>7</sub>    | E-12    | PIXB <sub>7</sub> | K-11    | PIXA <sub>5</sub>   | M-8     | CLK               |

| B-6        | DGND              | F-1     | OVLD1             | K-12    | PIXC <sub>5</sub>   | M-9     | LD                |

| B-7        | AC <sub>0</sub>   | F-2     | OVLE <sub>1</sub> | L-1     | PIXC <sub>1</sub>   | M-10    | SYNC              |

| B-8        | R/W               | F-11    | PIXA <sub>7</sub> | L-2     | PIXE <sub>1</sub>   | M-11    | PIXA <sub>4</sub> |

| B-9        | R                 | F-12    | PIXE6             | L-3     | PIXC <sub>2</sub>   | M-12    | PIXE <sub>4</sub> |

3

Am81C451/458

3-117

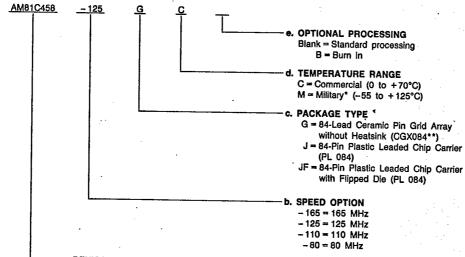

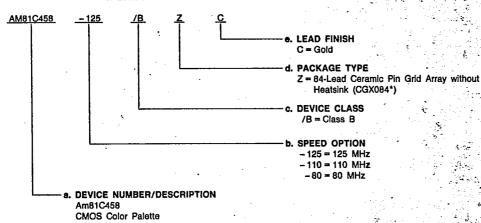

### ORDERING INFORMATION

T-52-33-43

### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type 9

d. Temperature Range

e. Optional Processing

DEVICE NUMBER/DESCRIPTION Am81C451/458 **CMOS Color Palette**

| Valid Co     | Valid Combinations |  |  |  |

|--------------|--------------------|--|--|--|

| AM81C451-165 |                    |  |  |  |

| AM81C451-125 | 7                  |  |  |  |

| AM81C451-110 |                    |  |  |  |

| AM81C451-80  | <u> </u>           |  |  |  |

| AM81C458-165 | GC, JC, GM, GMB    |  |  |  |

| AM81C458-125 |                    |  |  |  |

| AM81C458-110 | 7                  |  |  |  |

| AM81C458-80  |                    |  |  |  |

<sup>&</sup>quot;Military or Limited Military temperature range products are "NPL" (Non-Compliant Products List) or Non-MIL-STD-883C Compliant products only.

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade

<sup>\*\*</sup>Preliminary; Package in development.

### MILITARY ORDERING INFORMATION

T-52-33-43

### **APL Products**

AMD products for Aerospace and Defence applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-883C requirements. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

# CMOS Color Palette

| Valid Co     | mbinations |  |

|--------------|------------|--|

| AM81C458-125 |            |  |

| AM81C458-110 | /BZC       |  |

| AM81C458-80  | <b>1</b>   |  |

\*Preliminary; Package in development.

### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations or to check for newly released valid combinations.

### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

### PIN DESCRIPTION

T-52-33-43

### **Timing Section**

### BLANK Blank (TTL-Compatible Input)

When active, the BLANK input overrides the color pixel and overlay data to force the Red, Green, and Blue video outputs to their blank levels. This blank level is required during the monitor's vertical and horizontal retrace times. It is latched on the rising edge of LD.

### CLK, CLK Clock Source Pins (Pseudo-ECL-Compatible Inputs)

These differential clock inputs operate at the pixel clock rate of the system. They are driven by ECL logic configured for single (+5 V) supply operation.

## Load Clock (TTL-Compatible Input)

Data present on the PIXA0-7 through PIXE0-7 and OVLA0, 1 through OVLE0, 1, SYNC, and BLANK inputs are clocked into the part on the rising edge of LD. The input rate for this pin may be either one-fourth or one-fifth of the clock frequency, depending on how the part is programmed. See Display Memory Interface section under Functional Description.

### SYNC Sync (TTL-Compatible Input)

When active, the SYNC input switches off a current source on the Green video output. It is latched on the rising edge of LD. Because SYNC does not override any other inputs or control pins, it should be asserted only during blanking intervals

### **Data Path Section**

### OVLA<sub>0, 1</sub> through OVLE<sub>0, 1</sub> Color Overlay Data Address (TTL-Compatible Inputs)

These ten inputs are organized as five 2-bit addresses. Each 2-bit address selects which of the four Overlay Registers is used to provide color information. These ten inputs are latched into the input buffer on the rising edge of LD. Either four or all five ports may be used for selecting Overlay Registers. Unused inputs should be grounded. These inputs are used with bit CMD6 of the Command Register as follows (assuming no Read and no Blink Masking):

| OVLX1            | OVLX0 | CMD6 = 1        | CMD6 = 0                                                                 |

|------------------|-------|-----------------|--------------------------------------------------------------------------|

| 0<br>0<br>1<br>1 | .0    | Overlay Color 2 | Overlay Color 0<br>Overlay Color 1<br>Overlay Color 2<br>Overlay Color 3 |

### PIXA0-7 through PIXE0-7 Color Pixel Data Addresses (TTL-Compatible inputs)

These 40 inputs are organized as five 8-bit addresses. Each 8-bit address selects which of the 256 entries in the Color Look-Up Table is to be used to provide pixel color information. These 40 inputs are latched into the input buffer on the rising edge of LD. Either four or all five ports may be used for selecting color information. Unused inputs should be grounded.

### Analog Section

### Compensation Capacitor Connection (Analog COMP

A 0.1-µF ceramic capacitor is connected between this pin and AVCC.

## FSADJ Full-Scale Adjust (Analog Input)

The magnitude of the full-scale video signal is controlled by a resistor connected between FSADJ and AGND. The typical value for this resistor for RS-343A into 37.5 ohms is 523 ohms.

### Red Video Output (Analog Output)

This is the analog output of the Red DAC. This output is capable of driving an RS-343A-compatible doubly terminated 75-ohm cable.

## Green Video Output (Analog Output)

This is the analog output of the Green DAC. This output is capable of driving an RS-343A-compatible doubly terminated 75-ohm cable. The SYNC current source is connected to this output.

### Blue Video Output (Analog Output)

This is the analog output of the Blue DAC. This output is capable of driving an RS-343A-compatible doubly terminated 75-ohm cable.

### Voltage Reference (Analog Input)

An external voltage reference circuit must be used to supply this input with a 1.235-V (typical) reference.

### **MPU** Interface

AC<sub>0, 1</sub> Address Control (TTL-Compatible Inputs)

AC<sub>0</sub> and AC<sub>1</sub> allow the MPU to address any location in the Color Look-Up Table or any of the internal control registers. They are latched on the falling edge of CE. See Table 1.

### Chip Select (TTL-Compatible Input)

This signal enables the MPU interface. Data on  $D_{0-7}$  is internally latched on the rising edge of CE during Write operations.

### Data and Address Bus (TTL-Compatible Input/ Do - 7 Output)

These eight pins are used to load and read back the internal control registers and the Color Look-Up Table. Do is the least-significant bit.

# Read/Write (TTL-Compatible Input)

$R/\overline{W}$  is latched on the falling edge of  $\overline{CE}$ . A "logical one" indicates a Look-Up Table or Register Read-Back operation. A "logical zero" indicates a Write operation.

### **Power Supply**

### AGND, DGND Analog, Digital Ground

AVCC, DVCC Analog, Digital +5-Volt Supply

### **FUNCTIONAL DESCRIPTION**

The Am81C451/458 CMOS Color Palette integrates all the major functions required in the back-end of a video system, and supports pixel rates sufficient for most medium- to highresolution monitors.

Four or five pixels are input in parallel from Display Memory and are serialized internally. A programmable Look-Up Table maps the serial pixel stream (address) into a physical color (data), and finally, three DACs convert the digital outputs of the look-up table into RS-343A-compatible RGB analog for-

### Microprocessor Interface

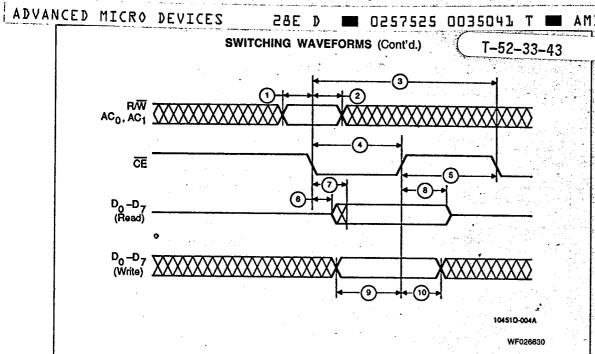

A standard 8-bit MPU Interface allows easy communication between the Am81C451/458 and most common MPUs. The CE and R/W inputs control MPU access timing, as shown in Figure 1. The AC<sub>1</sub> and AC<sub>0</sub> inputs select the access type as detailed in Table 1.

TABLE 1. AC1, AC0 DECODING

| Γ | AC <sub>1</sub> | AC <sub>0</sub> | Access Type       |

|---|-----------------|-----------------|-------------------|

| Г | -               | 0               | Address Register  |

| 1 | 0               | 1 1 1           | Look-Up Table     |

| ı | 1               | 0               | Control Registers |

| 1 | 1               | 1               | Overlay Registers |

Fast access to the Look-Up Table and to the Overlay Registers is achieved by means of two internal counters: an 8-bit Address Register (ARO – AR7), which generates addresses for the Color Memory locations and the Control Registers, and a Modulo 3 Counter (ARa,ARb) that controls which byte of the 24-bit Color Memory word is accessed. Tables 2 and 3 Illustrate the operation of these two counters.

## TABLE 2. ADDRESS REGISTER OPERATION 7-52-33-43

| AR7-AR0   | AC <sub>1</sub> | AC <sub>0</sub> | Location/Register Addressed<br>by MPU |

|-----------|-----------------|-----------------|---------------------------------------|

| \$00-\$FF | 0               | 1               | Color Look-up Table Location          |

| \$00      | 1               | 1               | Overlay Register 0                    |

| \$01      | 1 1             | 1               | Overlay Register 1                    |

| \$02      | 1               | 1               | Overlay Register 2                    |

| \$03      | 1 1             | 1 1             | Overlay Register 3                    |

| \$04      | 1               | ló              | Read Mask Register                    |

| \$05      | 1               | 0               | Blink Mask Register                   |

| \$06      | 1               | 0               | Command Register .                    |

| \$07      | 1               | 0               | Test Register                         |

TABLE 3. MODULO 3 COUNTER OPERATION

| ARb | ARa | Color Byte<br>Being Accessed |

|-----|-----|------------------------------|

| 0   | 0   | Red                          |

| 1 0 | 1   | Green                        |

| 1   | 0   | Blue                         |

The Address Register, directly accessible by the MPU, autoincrements at the end of each third (Blue) access having ACo = 1. This feature avoids the rewriting of the Address Register with consecutive values, saving MPU time and Bus bandwidth for transfers to or from consecutive Color Memory locations.

The Modulo 3 Counter, not accessible by the MPU, increments at the end of each MPU access with ACo = 1 (color operations), and is reset to 0 at the end of each MPU access with  $AC_0 = 0$  (Control Register operations).

Table 4 illustrates the Read/Write access to the Am81C451/ 458 palette.

TABLE 4, READ/WRITE ACCESS TO THE Am81C458

| R/₩         | AC <sub>1</sub>  | AC <sub>0</sub>  | ARb              | ARa              | Function                                                                                                                                                                                                                                                                                                                                    | <del></del> |

|-------------|------------------|------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0 0         | 0 0 0            | 0<br>1<br>1<br>1 | x<br>0<br>0<br>1 | X<br>0<br>1<br>0 | Write Address Register; AR7-AR0 ← D <sub>7-0</sub> ; ARb, ARa ← 0. Write Red Color; RREG ← D <sub>7-0</sub> ; Incr. ARb, ARa. Write Green Color; GREG ← D <sub>7-0</sub> ; Incr. ARb, ARa. Write Blue Color; BREG ← D <sub>7-0</sub> ; ARb, ARa ← 0 Write Color Look-Up Table; R7-R0 ← RREG; G7-G0 ← GREG; B7-B0 ← BREG; Incr. AR7-AR0.     |             |

| 000         | 1<br>1<br>1<br>1 | 0<br>1<br>1<br>1 | X<br>0<br>0<br>1 | X<br>0<br>1<br>0 | Write Control Register; Reg (AR7-AR0) ← D <sub>7-0</sub> ; ARb, ARa ← 0. Write Red Color; RREG ← D <sub>7-0</sub> ; Incr. ARb, ARa. Write Green Color; GREG ← D <sub>7-0</sub> ; Incr. ARb, ARa. Write Blue Color; BREG ← D <sub>7-0</sub> ; ARb, ARa ← 0; Write Overlay Register; R7-R0 ← RREG; G7-G0 ← GREG; B7-B0 ← BREG; Incr. AR7-AR0. |             |

| 1<br>1<br>1 | 0<br>0.<br>0     | 0<br>1<br>1      | 0<br>0<br>1      | X<br>0<br>1<br>0 | Read Address Register; D <sub>7-0</sub> ← AR7-AR0; ARb, ARa ← 0.<br>Read Color LUT Red; D <sub>7-0</sub> ← R7-R0; Incr. ARb, ARa.<br>Read Color LUT Green; D <sub>7-0</sub> ← G7-G0; Incr. ARb, ARa.<br>Read Color LUT Blue; D <sub>7-0</sub> ← B7-B0; ARb, ARa ← 0; Incr. AR7-AR0.                                                         |             |

| 1<br>1<br>1 | 1<br>1<br>1      | 0 1 1 1          | 0<br>0<br>1      | 0<br>1<br>0      | Read Control Register; D <sub>7-0</sub> ← Reg (AR7-AR0); ARb, Ara ← 0.<br>Read Overlay Red; D <sub>7-0</sub> ← R7-R0; Incr. ARb, ARa.<br>Read Overlay Green; D <sub>7-0</sub> ← G7-G0; Incr. ARb, ARa.<br>Read Overlay Blue; D <sub>7-0</sub> ← B7-B0; ARb, ARa ← 0; Incr. AR7-AR0.                                                         |             |

Key:

— "'gets the value of"

D<sub>7-0</sub> = MPU Data Bus

R7-R0 = Color Memory Red Byte

G7-G0 = Color Memory Green Byte

B7-B0 = Color Memory Blue Byte

RREG = Red Byte Register

GREG = Green Byte Register

BREG = Blue Byte Register

Reg (AR7-AR0) = Register pointed to by Address Register

Note that for the Am81C451 only the most significant data lines (D<sub>7</sub>-D<sub>4</sub>) are used while accessing the color lookup table or overlay registers. During a write cycle bits D<sub>3</sub>-D<sub>0</sub> are ignored and during a read cycle bits D<sub>3</sub>-D<sub>0</sub> are forced to logical zero.

If the pixel or overlay inputs address same entry in the color lookup table that is being written to by the MPU during blue write, the possibility exists that one or more pixels may be corrupted. Only one pixel may be corrupted if the MPU data is valid during the entire CE active time.

THE ST WARREN

### Display Memory Interface

The Am81C451/458 allows pixel data to be transferred from Display Memory at TTL-type data rates while presenting RGB information to the CRT at much higher rates through the use of internal latches and multiplexers.

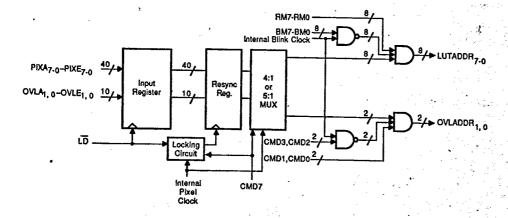

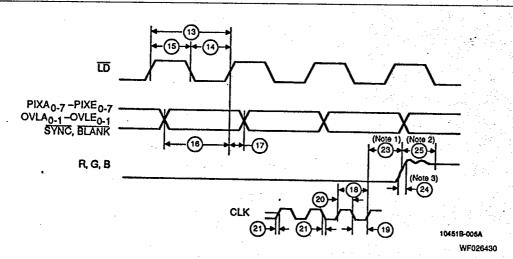

Forty pixel data inputs (PIXA $_{0-7}$  through PIXE $_{0-7}$ ), ten overlay data inputs (OVLA $_{0-1}$  through OVLE $_{0-1}$ ), and two video inputs (SYNC and BLANK), are loaded on the rising edge of LD. An input MUX performs a 4:1 or a 5:1 serialization based on the FORMAT bit (CMD7) of the Command Register. During each clock cycle the Ama1C451/458 outputs video information based first on the PIXA $_{0-7}$  inputs, then the PIXB $_{0-7}$  inputs, and so on until the PIXD $_{0-7}$  inputs (CMD7 = 0) or PIXE $_{0-7}$  inputs (CMD7 = 1), at which time the cycle repeats.

No phase relationship is imposed on the  $\overline{\text{LD}}$  and CLK inputs; the only requirement is that the  $\overline{\text{LD}}$  frequency be one-fourth or one-fifth of pixel clock (CLK,  $\overline{\text{CLK}}$  depending on the CMD7 bit of the Command Register). This is obtained by virtue of an onchip Locking Circuit that guarantees stable inputs to the Resync Register during positive transitions of the internal load signal (see Figure 1).

Note that the pixel data, overlay data, and SYNC and BLANK are loaded with the same LD clock to maintain synchronization with video data inside the Am81C451/458.

### **Color Selection**

During each clock cycle, 10 bits of data are transferred from the input MUX and processed by the Read Mask, Blink Mask, and Command Register (see Figure 2). The processed data then selects an entry in the color palette RAM or an Overlay

Register to provide color information.

| T-52-33-43

The Read Mask is used to selectively enable or disable bit-planes from being presented to the color palette RAM; the Blink Mask is used to selectively enable or disable blinking on a bit-plane. CMD4 and CMD5 in the Command Register determine the blink-rate duty cycle. The counter that generates the internal blink clock is incremented during vertical retrace intervals. Such intervals are detected when the BLANK input is LOW for a period of at least 256 LD cycles.

### **Overlay Color Selection**

Four different overlay colors are available through four Overlay Registers. CMD1 and CMD0 in the Command Register act as Read Masks, and CMD2 and CMD3 in the Command Register act as Blink Masks on the overlay inputs (see Figure 1).

When OVLADDR<sub>1</sub> = 0 and OVLADDR<sub>0</sub> = 0 (see Figure 1), CMD6 of the Command Register selects between Overlay Register 0 and Look-Up Table output (determined by LUTADDR<sub>7-0</sub>). See Table 5.

TABLE 5. OVERLAY COLOR SELECTION

| OVLADDR1    | R1 OVLADDR0 CMD6 = 0 |                                                                                      | CMD6 = 1           |

|-------------|----------------------|--------------------------------------------------------------------------------------|--------------------|

| 0<br>0<br>1 | 0                    | Overlay Register 0<br>Overlay Register 1<br>Overlay Register 2<br>Overlay Register 3 | Overlay Register 2 |

Key: LUT = Look-Up Table content addressed by LUTADDR7-0 CMD6 = Bit 6 of Command Register (RAM Enable)

Note: CMDx bits are programmed in the Command Register BMx bits are programmed in the Blink Mask Register RMx bits are programmed in the Read Mask Register

10451B-006A BD008070

Figure 1. Input MUX and Masking Stage

T-52-33-43

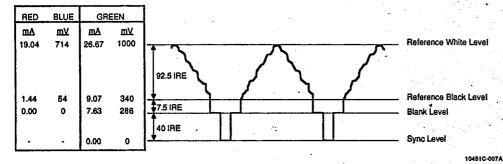

### Video Generation

During each clock cycle, 12(24) bits of information from either the Look-Up Table or an Overlay Register are presented to the three 4-bit (8-bit) DACs. These DACs convert the Color Memory digital output into RGB RS-343A analog format.

The SYNC and BLANK inputs are routed to the DACs after a delay equal to the pipeline delay incurred by the video stream to produce the relative Blank and Sync levels. BLANK is routed to all three DACs while SYNC is routed only to the Green DAC. See Figure 2 for DAC current and voltage levels.

DF00668

Note:  $75-\Omega$  doubly terminated load. Sync on Green DAC only. When Sync is used, the Green DAC current output is 7.63 mA higher than the corresponding Red or Blue current outputs. When Sync is not used, Green, Red, and Blue outputs are identical.

Figure 2. DAC Current and Voltage Levels

3

### **User-Accessible Registers**

Command Register (CMD7 - CMD0)

T-52-33-43

In addition to the address register, there are four useraccessible registers: Command, Read Mask, Blink Mask, and Test. These registers should be initialized after power-up.

This is an 8-bit register located at address #6, and is described below.

### TABLE 6. COMMAND REGISTER DEFINITION

| Position      | Name                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD7          | FORMAT  0 = 4:1 Multiplexing 1 = 5:1 Multiplexing                                                 | CMD7 specifies whether 4:1 or 5:1 multiplexing should take place on the pixel and overlay data. If CMD7 is set to logical '0' (4:1 multiplexing), LD should be one-fourth the frequency of CLK; the PIXE <sub>0-7</sub> and OVLE <sub>0, 1</sub> Inputs are ignored and should be connected to GND. If CMD7 is set to logical '1' (5:1 multiplexing), LD should be one-fifth the frequency of CLK. |

| CMD6          | RAM Enable  0 = Use Overlay Register 0  1 = Use LUT                                               | When the processed overlay inputs OVLADDR1 and OVLADDR0 equal (0, 0) this bit selects between the Color Look-Up Table output and Overlay Register 0.                                                                                                                                                                                                                                               |

| CMD5,<br>CMD4 | Blink Rate Select  00 = 25/75 (16/48)  01 = 50/50 (16/16)  10 = 50/50 (32/32)  11 = 50/50 (64/64) | These bits specify the blink rate and duty cycle of the internal blink clock. Numbers in parentheses specify the rate and duty cycle of the internal blink clock (logic I/logic 0) expressed in vertical retrace intervals. See Figure 1.                                                                                                                                                          |

| CMD3          | OVL <sub>1</sub> Blink Mask 0 = Disable Blinking 1 = Enable Blinking                              | When this bit is set to a logical 1, the OVLA1 Through OVLE1 inputs are allowed to toggle at the selected blinking blink rate between the input value and logical 0 before being applied to the LUT/Overlay decode logic. When this bit is set to logical 0 it does not affect the OVLA1 through OVLE1 inputs.                                                                                     |

| CMD2          | OVL <sub>0</sub> Blink Mask 0 = Disable Blinking 1 = Enable Blinking                              | When this bit is set to a logical 1, the OVLA <sub>0</sub> through OVLE <sub>0</sub> inputs are allowed to toggle at the selected blink rate between the input value and logical 0 before being applied to the LUT/ Overlay decode logic. When this bit is set to logical 0 it does not affect the OVLA <sub>0</sub> through OVLE <sub>0</sub> inputs.                                             |

| CMD1          | OVL <sub>1</sub> Read Mask 0 = Disable Mask 1 = Enable Mask                                       | When this bit is set to logical 0, the OVLA1 through OVLE1 inputs are forced to logical 0 before being applied to the LUT/Overlay decode logic. When this bit is set to logical 1 it does not affect the OVLA1 through OVLE1 inputs.                                                                                                                                                               |

| CMD0          | OVL <sub>0</sub> Read Mask 0 = Disable Mask 1 = Enable Mask                                       | When this bit is set to logical 0, the OVLA <sub>0</sub> through OVLE <sub>0</sub> inputs are forced to logical 0 before being applied to the LUT/Overlay decode logic. When this bit is set to logical 1 it does not affect the OVLA <sub>0</sub> through OVLE <sub>0</sub> inputs.                                                                                                               |

### Read Mask Register (RM7-RM0)

This is an 8-bit register located at address #4. It selectively enables (logical 1) or disables (logical 0) pixel bit-planes from addressing the Color Look-Up Table. Bit RM0 will mask inputs PIXA<sub>0</sub> through PIXE<sub>0</sub>; bit RM1 will mask inputs PIXA<sub>1</sub> through PIXE1; and so on.

Overlay plane masking is controlled by bits CMD1 and CMD0 of the Command Register. See Figure 1.

### Blink Mask Register (BM7 - BM0)

This is an 8-bit register located at address #5. It selectively enables (logical 1) or disables (logical 0) pixel bit-planes from blinking, Bit BM0 will mask inputs PIXA0 through PIXE0; bit BM1 will mask inputs PIXA1 through PIXE1; and so on. When enabled, that particular bit-plane will toggle between its original value and logical 0 at the selected rate and duty cycle.

Overlay plane blinking is controlled by bits CMD3 and CMD2 of the Command Register. See Figure 1.

### Test Register (T7 - T0)

This is an 8-bit register located at address #7, it is used to read back data presented to the DACs from the Color Memory (either pixel or overlay data). The four most-significant bits, 17-T4, contain color information while the four least-significant bits, T3-T0, contain control information, as shown in Table 7. T7-T4 are defined only when exactly one of the

T2-T0 bits is a "logical one". Note that for the Am81C451. bit T3 is forced to logical zero.

When unused, this register should be initialized to Hex 00.

TABLE 7. TEST REGISTER DEFINITION

| Test Register Bits | Function                                        |

|--------------------|-------------------------------------------------|

| T7-T4              | Color Nibble                                    |

| ТЗ                 | 1 = Select LOW Nibble<br>0 = Select HIGH Nibble |

| Т2                 | 1 = Enable Blue Data<br>0 = Disable Blue Data   |

| T1                 | 1 = Enable Green Data<br>0 = Disable Green Data |

| то                 | 1 = Enable Red Data<br>0 = Disable Red Data     |

As an example, in order to read the least-significant 4 bits of data presented to the Green DAC, the user must first write Hex 0A to the Test Register to enable the LOW nibble and green data. Subsequently, the user reads the Test Register, keeping the pixel inputs constant; bits D7-D4 of the MPU interface Bus will contain the desired color data while bits D3-D0 will contain Hex A.

When reading the Test Register, the data presented to the DAC inputs must be held stable during this period either by slowing the pixel clock or by holding the pixel and overlay inputs constant.

### **ABSOLUTE MAXIMUM RATINGS**

## **OPERATING RANGES** (

T-52-33-43

| Storage Temperature65 to +150°C        |

|----------------------------------------|

| Ambient Temperature                    |

| Under Bias55 to +125°C                 |

| Junction Temperature+ 175°C            |

| Supply Voltage to Ground Potential     |

| Continuous                             |

| DC Voltage Applied to Outputs for      |

| HIGH Output State0.5 V to VCC Max.     |

| DC input Voltage GND0.3 to VCC + 0.3 V |

| DC Input Current =10 to ±10 mA         |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Commercial (C) Devices Amblent Temperature (T <sub>A</sub> )                                |

|---------------------------------------------------------------------------------------------|

| Military (M) Devices Case Temperature (Tc)55 to +125°C Supply Voltage (Vcc)+4.50 to +5.50 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL products, Group A Subgroups 1, 2, 3, 7, & 8 are tested unless otherwise noted)

| Parameter<br>Symbol                    | Parameter<br>Description                                                                                                                                                          | Test<br>Conditions                                     | Min.                                | Тур.                                     | Max.                                       | Unit                       |  |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|------------------------------------------|--------------------------------------------|----------------------------|--|

| DIGITAL CL                             | OCK INPUTS (CLK, CLK)                                                                                                                                                             |                                                        |                                     | •                                        |                                            |                            |  |

| VCKIH                                  | Input HIGH Voltage                                                                                                                                                                | •                                                      | VCC -1.0                            |                                          | V <sub>CC</sub> +0.5                       | ٧                          |  |

| VCKIL                                  | Input LOW Voltage                                                                                                                                                                 |                                                        | GND -0.5                            |                                          | V <sub>CC</sub> -1.6                       | ٧                          |  |

| Скін                                   | Input HIGH Current                                                                                                                                                                |                                                        |                                     |                                          | 1                                          | μА                         |  |

| CKIL                                   | Input LOW Current                                                                                                                                                                 |                                                        |                                     |                                          | -1                                         | μA                         |  |

| CCKIN                                  | Input Capacitance                                                                                                                                                                 | f = 1 MHz, V <sub>IN</sub> = 4.0 V                     |                                     |                                          | 10                                         | ρF                         |  |

|                                        | PUTS (Except CLK, CLK)                                                                                                                                                            |                                                        |                                     | · .                                      |                                            |                            |  |

| ViH                                    | Input HIGH Voltage                                                                                                                                                                |                                                        | 2.0                                 |                                          | V <sub>CC</sub> +0.5                       | V                          |  |

| VIL                                    | Input LOW Voltage                                                                                                                                                                 |                                                        | GND -4.5                            | t                                        | 0.8                                        | V .                        |  |

| I <sub>tH</sub>                        | Input HIGH Current                                                                                                                                                                | V <sub>IN</sub> = 2.4 V                                | 4                                   |                                          | 1                                          | μА                         |  |

| ht.                                    | Input LOW Current                                                                                                                                                                 | V <sub>IN</sub> = 0.4 V                                |                                     |                                          | -1                                         | μΑ                         |  |

| Cin                                    | Input Capacitance                                                                                                                                                                 | f = 1 MHz, V <sub>IN</sub> = 2.4 V 4                   |                                     | •                                        | 10                                         | pF                         |  |

|                                        | JTPUTS (D <sub>0-7</sub> )                                                                                                                                                        | <b>A</b>                                               |                                     | •                                        |                                            |                            |  |

| VoH                                    | Output HIGH Voltage                                                                                                                                                               | IOH = 800 #A                                           | 2.4                                 |                                          |                                            | ٧                          |  |

| VOL                                    | Output LOW Voltage *                                                                                                                                                              | IOL = 64 mA                                            | -                                   |                                          | 0.4                                        | ٧                          |  |

| loz                                    | Three-State Current                                                                                                                                                               | A GOOD                                                 |                                     |                                          | 10                                         | μΑ                         |  |

| COUT                                   | Output Capacitance                                                                                                                                                                | ABB                                                    |                                     | 10                                       |                                            | pF                         |  |

|                                        | UTPUTS (R <sub>FS</sub> = 523 Ω, V <sub>REF</sub> = 1.235                                                                                                                         | NA III                                                 |                                     |                                          |                                            |                            |  |

| ······································ | Resolution (Each DAC)                                                                                                                                                             | a a a                                                  | 4 (8)                               |                                          | 4 (8)                                      | Bits                       |  |

| LIN <sub>i</sub><br>LIN <sub>d</sub>   | Accuracy (Each DAC): Integral Linearity Differential Linearity                                                                                                                    | COM'L                                                  | •                                   | 69.1                                     | ± 1/8 (± 1)<br>± 1/16 (± 1)<br>+ 1/8 (± 2) | LSB                        |  |

|                                        | LSB Output Current                                                                                                                                                                | MIL                                                    |                                     |                                          | + 1/16 (± 1)                               |                            |  |

|                                        | LSB Output Current                                                                                                                                                                | 2                                                      |                                     | 1175 (69.1)                              |                                            | μA                         |  |

|                                        | Gray Scale Error                                                                                                                                                                  | % Gray Scale                                           |                                     |                                          | ±5                                         | %                          |  |

|                                        | Monotonicity                                                                                                                                                                      |                                                        |                                     | L                                        | Guaranteed                                 |                            |  |

|                                        | Coding                                                                                                                                                                            | Binary                                                 |                                     |                                          |                                            |                            |  |

|                                        | Output Current:  White Level Relative to Blank Level White Level Relative to Black Level Black Level Relative to Blank Level Blank Level on R, B Blank Level on G Sync Level on G | R <sub>FS</sub> = 523 Ω,<br>V <sub>REF</sub> = 1.235 V | 17.69<br>16.74<br>0.95<br>0<br>6.29 | 19.05<br>17.62<br>1.44<br>5<br>7.62<br>5 | 20.40<br>18.50<br>1.90<br>50<br>8.96<br>50 | mA<br>mA<br>mA<br>μA<br>mA |  |

|                                        | DAC-to-DAC Matching                                                                                                                                                               |                                                        |                                     | . 2                                      | 5                                          | %                          |  |

| Voc                                    | Output Compliance                                                                                                                                                                 |                                                        | -1.0                                |                                          | +1.2                                       | V                          |  |

| Rout                                   | Output Impedance                                                                                                                                                                  |                                                        |                                     | 50                                       |                                            | kΩ                         |  |

| Cour                                   | Output Capacitance                                                                                                                                                                | f = 1 MHz, lour = 0 mA                                 |                                     | 13                                       | 20                                         | pF                         |  |

| IREF                                   | Volt Reference Input Current                                                                                                                                                      |                                                        |                                     | 10                                       |                                            | μΑ                         |  |

| PSRR                                   | Power Supply Rejection Ratio                                                                                                                                                      | CCOMP = 0.1 μF f = 1 KHz                               | [                                   | 0.5                                      |                                            | %/%A V                     |  |

SWITCHING CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 unless otherwise noted)

T-52-33-43

|     | Parameter   | Parameter                                                      | 165 MHz |      |       | 125 MHz  |      |       | 110 MHz |          |      | 80 MHz |              |      |      |

|-----|-------------|----------------------------------------------------------------|---------|------|-------|----------|------|-------|---------|----------|------|--------|--------------|------|------|

| No. | Symbol      | Description                                                    | Min.    | Тур. | Max.  | Min.     | Тур. | Max.  | Min.    | Тур.     | Max. | Min.   | Тур.         | Max. | Unit |

| D   | IGITAL CPU  | INTERFACE TIMING                                               |         |      |       |          |      |       |         |          | •    |        |              |      |      |

| 1   | ts          | R/W, AC <sub>0</sub> , AC <sub>1</sub> Setup<br>Time           | 0       |      |       | 0        |      |       | 0       |          |      | 0      |              |      | ns   |

| 2   | ч           | $R/\overline{W}$ , $AC_0$ , $AC_1$ Hold Time                   | 15      |      |       | 15       |      |       | 15      |          |      | 15     |              |      | ns   |

| 3   | tcyc        | CPU Cycle Time                                                 | 100     |      |       | 100      |      | T     | 110     | <b>-</b> | _    | 125    | <b></b>      |      | ns   |

| 4   | ₩           | CE LOW Active Time                                             | 70      |      |       | 75       |      |       | 85      |          |      | 100    |              |      | ns   |

| 5   | tw          | CE HIGH Time                                                   | 25      |      |       | 25       |      |       | 25      |          |      | 25     |              |      | ns   |

| 6   | tPD         | CE Edge to Data Bus<br>Driven (C <sub>L</sub> = 40 pF)         | 10      |      |       | 10       |      |       | 10      |          |      | 10     |              |      | ns   |

| 7   | tPD         | CE Edge to Data Valid (CL = 40 pF)                             |         |      | 70    |          |      | 1     | *       |          | 85 - |        |              | 100  | ns   |

| 8   | tPD CI9T    | CE Edge to Data<br>Three-Stated<br>(CL = 40 pF)                |         |      | 15    |          | P    | 15    |         |          | 15   | -      |              | 15   | ns   |

| 9   | ts          | Write Data Setup Time                                          | 35      |      | PA    | <b>W</b> | •    |       | 40      |          |      | 50     |              |      | ns   |

| 10  | ħ           | Write Data Hold Time                                           | 0       |      | 13    | ₹00      |      |       | 0       |          |      | 0      |              |      | ns   |

| DI  | GITAL VIDEO | PATH TIMING                                                    |         |      | 1 16  | <b>*</b> | •    |       | l       |          |      |        | لببيا        |      |      |

| 11  | fcĸ         | Video Clock Frequency                                          |         | A A  | 165   |          |      | 125   |         |          | 110  |        |              | 80   | MHz  |

| 12  | fLD         | LD Rate                                                        | · 6     | -    | 41.25 |          |      | 31.25 |         | ·        | 27.5 |        |              | 20   | MHz  |

| 13  | tcyc        | LD Cycle Time                                                  | 24      |      |       | 32       |      |       | 36.36   |          |      | 50     |              |      | ns   |

| 14  | W           | LD Pulse Width                                                 | EQ.     |      |       | 13       |      |       | 15      |          |      | 20     |              |      | ns   |

| 15  | ₩.          | LD Pulse Width Pight                                           | _9      |      |       | 13       |      |       | 15      |          |      | 20     |              |      | ns   |

| 18  | ts          | PIXx, OVE SYNC and BLANK Setup Time                            | 2       |      |       | 3        |      |       | 3       | -        |      | 4      | -            |      | ns   |

| 17  | ч           | PIX <sub>x</sub> , OVL <sub>x</sub> , SVIC and BLANK Hold Time | 2       |      |       | 2        |      |       | 2       |          |      | 2      |              | •    | ns   |

| 18  | tcyc        | Clock Cycle Time                                               | 6       |      |       | 8        |      |       | 9.09    |          |      | 12.5   |              |      | ns   |

| 18  | w           | Clock Pulse Width<br>LOW                                       | 2.4     |      |       | 3.2      |      |       | 4.0     | -        |      | 5.0    |              |      | ns   |

| 20  | tw          | Clock Pulse Width<br>HIGH                                      | 2.4     |      |       | 3.2      |      |       | 4.0     |          |      | 5.0    |              |      | ns   |

| 21  | ta, tr      | Clock Rise/Fall Time<br>(20%-80%)                              |         |      | 1.6   |          |      | 1.6   |         |          | 1.6  |        |              | 1.6  | ns   |

| 22  |             | Pipeline Delay                                                 | 6       |      | 10    | 6        |      | 10    | 6       |          | 10   | -6     | <del> </del> | 10   | Ciks |

Notes: See notes following end of table continued on next page.

### SWITCHING CHARACTERISTICS over operating ranges (Cont'd.)

T-52-33-43

|     | ·                   |                                                 |                           |      |          |           |      |      |         |      |      |        |      |      |      |            |

|-----|---------------------|-------------------------------------------------|---------------------------|------|----------|-----------|------|------|---------|------|------|--------|------|------|------|------------|

|     | Parameter<br>Symbol | Parameter<br>Description                        | 165 MHz                   |      |          | · 125 MHz |      |      | 110 MHz |      |      | 80 MHz |      |      |      |            |

| No. |                     |                                                 | Min.                      | Тур. | Max.     | Min.      | Тур. | Max. | Min.    | Тур. | Max. | Min.   | Тур. | Max. | Unit |            |

| A   | NALOG VIDE          | O DAC TIMI                                      | NG                        |      |          |           |      |      |         |      |      | •      |      |      |      |            |

| 23  |                     | Analog Out                                      | tput Delay                |      | 20       |           |      | 20   |         |      | 20   |        |      | 20   |      | ns         |

| 24  | ta, tr              | Analog Output Rise<br>and Fall Time<br>(Note 1) |                           |      | 2        |           |      | 2    |         |      | 2    |        |      | 2    |      | ns.        |

| 25  | ts                  | Analog Out<br>Time (Note                        | tput Settling<br>es 1, 2) |      |          | 6         | ~    | M    |         | 1    |      | 8      |      | s.   | 12   | ns         |

| 26  |                     | Analog Out                                      | tput Skew                 |      | 0,       | GA V      | HAST | 0.3  | A 13    |      | 0    | 2      |      | 0    | 2    | ns         |

| 27  |                     | Glitch Impulse Energy<br>(Note 2)               |                           | 4    | 150      |           | 11   | 50   |         |      | 50   |        |      | 50   |      | PV-<br>sec |

| 28  |                     | Clock and<br>Feedthroug<br>(Note 3)             |                           | A.   | TBD      | 4.        |      | TBD  |         |      | TBD  |        | 4    | TBD  |      | dB         |

| D   | YNAMIC POY          | ER DISSIPA                                      | HIONS                     |      |          |           |      |      |         |      |      |        |      |      |      | ·          |

|     |                     | Icc 🕽                                           | COM'L                     |      | 270      | 370       |      | 250  | 340     |      | 240  | 330    | ,    | 230  | 295  | T          |

|     |                     | (Supply<br>Current)                             | MIL                       | -    | <b>-</b> | -         |      | 250  | 425     |      | 240  | 410    |      | 230  | 370  | mA         |

Notes: 1. Clock and data feedthrough is not included.

2. Includes clock and data feedthrough, -3-dB bandwidth = 2 x clock frequency.

3. Measurement performed on TTL digital inputs with 74HC logic level and with 1-kohm resistor to GND.

Test Conditions: TTL Input Level: 0 to 3 V with  $t_{\rm R}$ ,  $t_{\rm F}(10.90\%) \leqslant 3$  ns; ECL Input Level: ( $V_{\rm CC}$  - 0.8 V) to ( $V_{\rm CC}$  - 1.8 V) with  $t_{\rm F}$ ,  $t_{\rm R}$  (20-80%)  $\leqslant$  2 ns; RseT = 523 ohms,  $V_{\rm REF}$  = 1.235 V; Analog Output Load  $\leqslant$  10 pF; D<sub>0.7</sub> Output Load  $\leqslant$  40 pF.

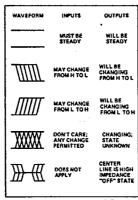

## **SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS**

KS000010

CPU Read/Write Timing

Notes: 1. Output delay time measured from 50% point of the rising clock edge to 50% point of full-scale

- Output settling time measured from 50% point of full-scale level to output settling within ±1 LSB.

Output rise/fall time measured between 10% and 90% points of full-scale level.

**Video Input/Output Timing**

### SWITCHING TEST CIRCUIT

T-52-33-43

AF004810

Notes: 1. Ct = 50 pF (includes scope probe, wiring, and stray capacitance without device in test fixture).

2.  $V_T = 1.5 \text{ V}$ .

### **Notes on Testing**

Incoming test procedures on this device should be carefully planned, taking into account the complexity and power levels of the part. The following notes may be useful.

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current as the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- Do not attempt to perform threshold tests at high speed.Following an input transition, ground current may change by

as much as 400mA in 5-8ns. Inductance in the ground cable may allow the ground pin at the device to rise by 100's of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0$  V and  $V_{IH} \geqslant 3$  V for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

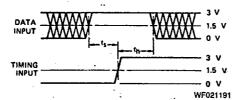

### SWITCHING TEST WAVEFORM

Notes: 1. Diagram show for HIGH data only. Output transition may be opposite sense.

2. Cross-hatched are is don't care condition.

Setup and Hold Times

### APPENDIX A - APPLICATION NOTE FOR THE Am81C458

T-52-33-43

The design of a system using the Am81C458 should be guided by considerations similar to those used for designing precision highspeed mixed analog and digital systems. The following rules and examples are given for orientation purposes. Users may choose to design circuits, differently from the examples given here.

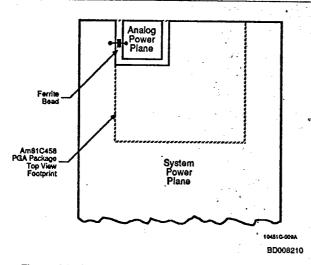

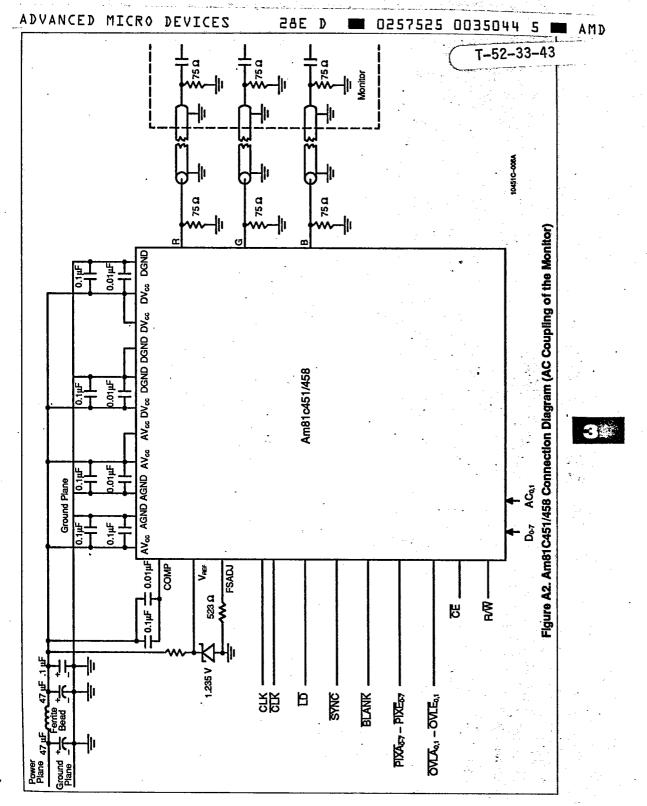

38E

Power pins should be decoupled from power lines of the rest of the system. The circuit board layout should have a dedicated analog power plane. The power plane should be connected to the main power plane by wires running through ferrite beads. The analog plane should be small enough so that no digital signal passes under it (see Figures A1 and A2).

Figure A1. Example of Power Planes Layout

There should be only one ground plane for all digital and analog ground pins, which is the same ground plane of the rest of the board. Tantalum capacitors, in parallel with a 0.1-µF ceramic capacitor, would be placed between each side of the ferrite beads and the ground plane. If too much ripple exists on the supply lines, the use of a dedicated linear regulator only for the Am81C451/458 is recommended.

The two groups of digital V<sub>CC</sub> (DV<sub>CC</sub>) pins should be decoupled from each other by connecting a 0.1-μF capacitor and a 0.01- μF capacitor in parallel between them and the closest group of digital ground pins (DGND).

A 0.1-μF ceramic capacitor, in parallel with a 0.001-μF chip capacitor, should be connected between each group of analog power pins (AVCC) and the group of analog ground pins (AGND),

The COMP pin should also be decoupled from the power pins and the rest of the system. A 0.1-µF and a 0.01-µF chip capacitor should be connected, in parallel, between the COMP pin and the analog power plane.

Digital lines concerning the CPU interface should be kept far from pixel data lines. Pixel clock lines should be kept far from all other digital inputs. Analog outputs should be kept far from any other input. No digital line should run under the analog plane. The CE line should be as short as possible to minimize any noise picked up from other sources.

Connection with the monitor should be done through a doubly terminated 75-ohm coaxial cable. To minimize reflections, terminating resistors on the color palette side should be placed as close as possible to the R, G, B outputs.

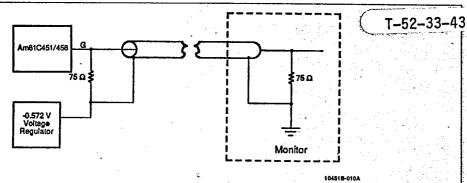

The signals produced by the Am81C451/458, including Sync, are all positive (outgoing) currents, which when passing through the terminating resistors produce positive voltages. Since most monitors are AC-coupled, DC restoration with the proper DC levels is done inside the monitor. If a negative-going Sync (of -0.286 V) is required, DC-level shifting can be done outside the palette, prior to entering the transmission cable. Two possible circuits that produce the level shifting are shown here.

The first circuit (Figure A3) shows the 75-ohm terminating resistor relative to the green DAC, connected between the G output and a voltage source of -0.572 V. This resistor, in series with the other 75-ohm terminator inside the monitor, constitutes a voltage divider which forces the voltage on the line to be offset by half of 0.572 V (i.e., 0.286 V).

Am81C451/458

3-131

BD008041

Figure A3. DC-Level Shifting Using a Voltage Regulator

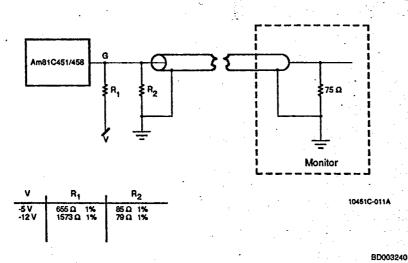

The second circuit (Figure A4), useful if an exact 0.572-V voltage source is not available, shows two resistors (R<sub>1</sub> and R<sub>2</sub>) instead of one, constituting the terminator at the transmitting side. R<sub>1</sub> is connected between the green DAC output and ground, while R<sub>2</sub> is connected between the green DAC output and a voltage source more negative than 0.572 V. R<sub>1</sub> and R<sub>2</sub> are such that in parallel they constitute 75 ohms, while their ratio is such that the voltage drop caused by the negative voltage source across R<sub>1</sub> is 0.572 V. This relationship is described by the following formulas:

$$R_2 = \frac{V \times 75}{-0.572}$$

$$R_1 = \frac{V \times 75}{V - 0.572}$$

or  $R_1 = \frac{1}{V}$

The variable voltage drop across the parallel of R<sub>1</sub> and R<sub>2</sub> caused by the DAC currents adds to that caused by the external voltage source.

Figure A4. DC-Level Shifting Using Two Resistors in Parallel

Am81C451/458

3-133