### Features

- High-performance, Low-power AVR<sup>®</sup> 8-bit Microcontroller

- 130 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 8 MIPS Throughput at 8 MHz

- On-chip 2-cycle Multiplier

- Nonvolatile Program and Data Memories

- Self-programming In-System Programmable Flash Memory

- 16K Bytes with Optional Boot Block (256 2K Bytes) Endurance: 1,000 Write/Erase Cycles

- Boot Section Allows Reprogramming of Program Code without External Programmer

- Optional Boot Code Section with Independent Lock Bits

- 512 Bytes EEPROM

- Endurance: 100,000 Write/Erase Cycles

- 1024 Bytes Internal SRAM

- Programming Lock for Software Security

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Clock with Separate Oscillator and Counter Mode

- Three PWM Channels

- 8-channel, 10-bit ADC

- Byte-oriented Two-wire Serial Interface

- Programmable Serial UART

- Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- Analog Comparator

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Four Sleep Modes: Idle, ADC Noise Reduction, Power-save, and Power-down

- Power Consumption at 4 MHz, 3.0V, 25°C

- Active 5.0 mA

- Idle Mode 1.9 mA

- Power-down Mode < 1 μA</li>

- I/O and Packages

- 32 Programmable I/O Lines

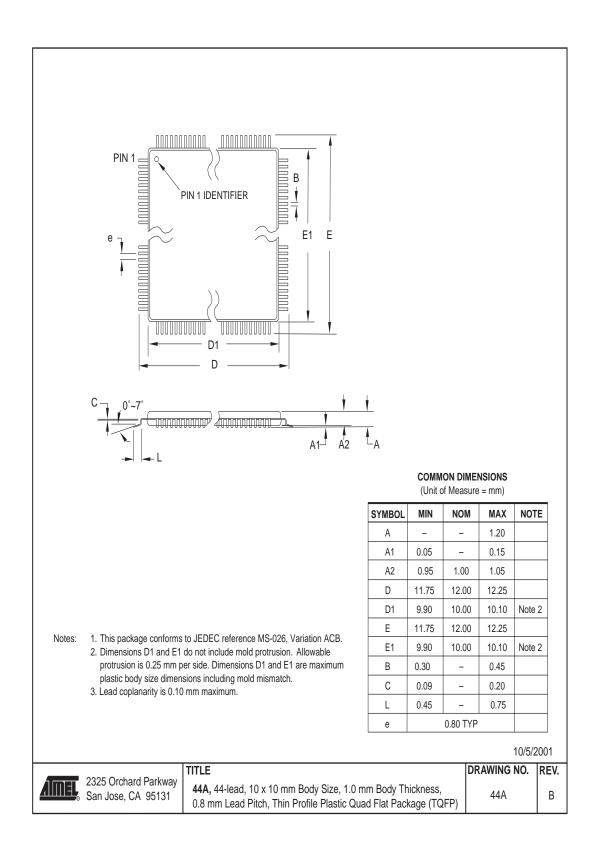

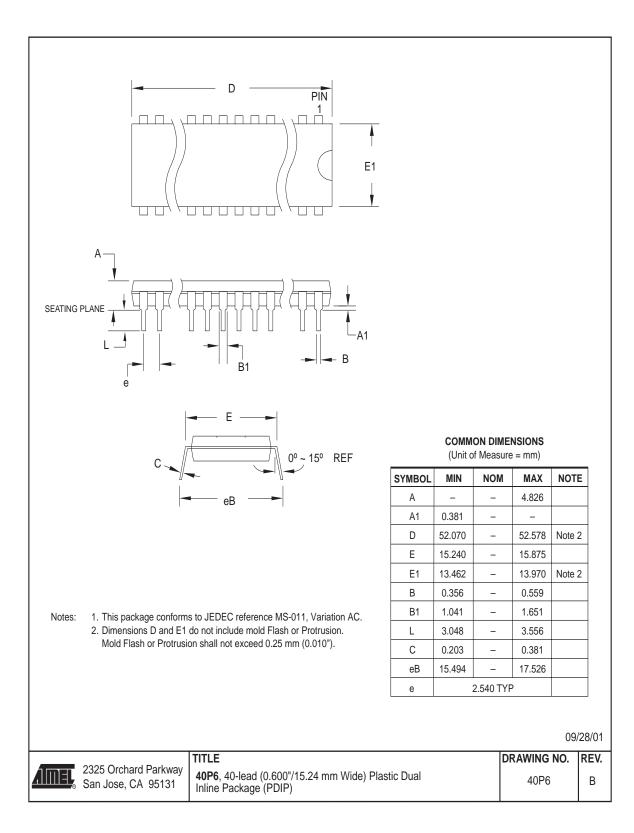

- 40-pin PDIP and 44-pin TQFP

- Operating Voltages

- 2.7 5.5V for ATmega163L

- 4.0 5.5V for ATmega163

- Speed Grades

- 0 4 MHz for ATmega163L

- 0 8 MHz for ATmega163

8-bit **AVR**<sup>®</sup> Microcontroller with 16K Bytes In-System Programmable Flash

ATmega163 ATmega163L

## Summary

Not Recommend for New Designs. Use ATmega16.

Rev.1142ES-AVR-02/03

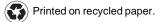

### **Pin Configurations**

### Description

The ATmega163 is a low-power CMOS 8-bit microcontroller based on the AVR architecture. By executing powerful instructions in a single clock cycle, the ATmega163 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

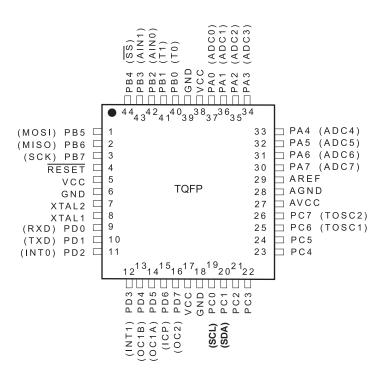

Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock

cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega163 provides the following features: 16K bytes of In-System Self-Programmable Flash, 512 bytes EEPROM, 1024 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC, a programmable Watchdog Timer with internal Oscillator, a programmable serial UART, an SPI serial port, and four software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous Timer Oscillator continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions.

The On-chip ISP Flash can be programmed through an SPI serial interface or a conventional programmer. By installing a Self-Programming Boot Loader, the microcontroller can be updated within the application without any external components. The Boot Program can use any interface to download the application program in the Application Flash memory. By combining an 8-bit CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega163 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega163 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

#### **Pin Descriptions**

| VCC             | Digital supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND             | Digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port A (PA7PA0) | Port A serves as the analog inputs to the A/D Converter.<br>Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.<br>Port pins can provide internal pull-up resistors (selected for each bit). The Port A output<br>buffers can sink 20mA and can drive LED displays directly. When pins PA0 to PA7 are<br>used as inputs and are externally pulled low, they will source current if the internal pull-<br>up resistors are activated. The Port A pins are tristated when a reset condition becomes<br>active, even if the clock is not running. |

| Port B (PB7PB0) | Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers can sink 20 mA. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. Port B also serves the functions of various special features of the ATmega83/163 as listed on page 117. The Port B pins are tristated when a reset condition becomes active, even if the clock is not running.                                                                                                       |

| Port C (PC7PC0) | Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers can sink 20 mA. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tristated when a reset condition becomes active, even if the clock is not running.                                                                                                                                                                                                               |

## 4 ATmega163(L)

Port C also serves the functions of various special features of the ATmega163 as listed on page 124.

- Port D (PD7..PD0) Port D is an 8-bit bidirectional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers can sink 20 mA. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. Port D also serves the functions of various special features of the ATmega163 as listed on page 128. The Port D pins are tristated when a reset condition becomes active, even if the clock is not running.

- **RESET**Reset input. A low level on this pin for more than 500 ns will generate a Reset, even if<br/>the clock is not running. Shorter pulses are not guaranteed to generate a Reset.

- **XTAL1** Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

- XTAL2 Output from the inverting Oscillator amplifier.

- **AVCC** This is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. See page 105 for details on operation of the ADC.

- AREF

AREF is the analog reference input pin for the A/D Converter. For ADC operations, a voltage in the range 2.5V to AVCC can be applied to this pin.

- AGND Analog ground. If the board has a separate analog ground plane, this pin should be connected to this ground plane. Otherwise, connect to GND.

# **AIMEL**®

## **Register Summary**

| Address         Name         Bit 7         Bit 6         Bit 7         H         S         V         N         Z         C         C         20           55E (55C)         SPH             SP10         SP5         SP1         SP2         C         C         20           55E (55C)         SPH         SP7         SP6         SP4         SP3         SP10         SP5         SP2         211           55C (55C)         Reserved             SP10         SP2         SP1         SP2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | News   | D:/ 7       | Dit o             | D% 5             | D'' 4         | D'' 0 | Dit 0 | D'' 4   | Dit o | Dama |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|-------------|-------------------|------------------|---------------|-------|-------|---------|-------|------|

| Size (Sec)         SPH         SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        | Bit /       |                   |                  |               |       |       |         |       | -    |

| SDB SED         SPL         SPS         SPA         SP3         SP2         SP1         SP0         21           SDB SGD         SER         MIT         INTO         -         -         -         -         -         -         -         -         -         -         -         30           SSB SSD         SER         SER         SER         CCIE2         TOE2         TOE1         -         -         -         -         -         30           SSB SSD         SER         CCIE2         TOE2         TOE2         TOE1         CCIE18         TOE11         -         -         -         30           SSB SSD         MCCR         WINT         TWER         AVEX         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        | 1           | T                 | н                | S             | V     |       |         |       |      |

| S2C (SC)         Reserved         Intro         Intro <thintro< th="">         Intro         Intro</thintro<>                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |        | -           | -                 | -                | -             |       |       |         |       |      |

| S88       GMBK       INTI       INTO       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       0       0       0       2       1       0       0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       - <t< td=""><td></td><td></td><td>SP7</td><td>SP6</td><td>SP5</td><td>SP4</td><td>SP3</td><td>SP2</td><td>SP1</td><td>SP0</td><td>21</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        | SP7         | SP6               | SP5              | SP4           | SP3   | SP2   | SP1     | SP0   | 21   |

| 38A (SA)       OFR       INTFI       INTF0       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |        | INIT4       | INITO             | 1                | 1             | 1     | 1     | 1       | 1     | 20   |

| 389         (58)         TMBK         OCIE2         TOLE2         TOLE1         OCIE18         OCIE18         TOLE1         TOLE1         TOLE1         TOLE3         T                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |        |             |                   |                  | -             |       | _     |         |       |      |

| 338       1FR       OCF2       TOV2       ICF1       OCF18       OCF18       TOV1       TOV1       TOV1       TOV3       32         357       6570       SPUCR       TWIRT       TWER       TWER       TWER       TWER       TWER       TWER       TWER       TWER       TWER       State       State<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        |             |                   |                  |               |       |       | _       |       |      |

| Str     SPMCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |        |             |                   |                  |               |       |       | -       |       |      |

| Sige Sige       TWCR       TWCR       TWSTA       TSTA       TSTA       TSTA       TSTA       TSTA       TS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |        |             |                   |                  |               |       |       |         |       |      |

| 328 (359)         MCUGR         -         SE         SM1         SM0         ISC11         ISC10         ISC01         ISC00         34           S34 (354)         MCUSR         -         -         -         -         -         CS02         CS01         CS00         41           S33 (553)         TCCR0         Tmer/Counter0 (Bts)         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |        |             |                   |                  |               |       |       |         |       |      |

| 334 (53)       MCUSR       -       -       -       WDF       BORF       EXTFF       PORF       28         333 (53)       TORTO       Tmer/Counter() (B Bis)       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |        |             |                   |                  |               |       |       |         |       |      |

| S33         DCR0         -         -         -         -         CS02         CS01         CS00         41           S32         DS2         DS2         CS01         CS01         CS00         41           S31         DS10         -         -         -         -         CS02         CS01         CS01         42           S31         DS10         -         -         -         -         ACME         PUD         PSR2         44           S32         DS41         CON141         COM141         COM141         COM141         PMM10         44           S20         DS40         TCNT11         Timer/Counter1 - Counter Register Migh Byte         -         CS11         CS1         CS1         46           S20         G440         TCNT11         Timer/Counter1 - Output Compare Register High Byte         -         47         -         47           S28         G464         COR14L         Timer/Counter1 - Noput Capture Register High Byte         -         47         -         47           S28         G464         TCR24         FOC2         PVM2         COM20         CT2         CS21         CS20         S2         -         48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |        |             |                   |                  | 31010         |       |       |         |       |      |

| 322 (32)       TONTO       Timer/Countrator (0 Bits)       37         331 (551)       OSCAL       Osellator Calibration Register       37         320 (550)       SFIOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |        |             |                   | _                | _             |       |       |         |       |      |

| 3511       0.95CCAL       Oscillator Calibration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |        |             | ter0 (8 Bits)     |                  |               |       | 0002  | 0001    | 0000  |      |

| Sa0 (So)         SFIOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |        |             |                   | ter              |               |       |       |         |       |      |

| S2F         GAH1         COM140         COM180         FOC1A         FOC1A <thf< td=""><td></td><td></td><td></td><td>· · · · ·</td><td></td><td>-</td><td>ACME</td><td>PUD</td><td>PSR2</td><td>PSR10</td><td></td></thf<>                                                                                                                                                                                                                                                                                                      |             |        |             | · · · · ·         |                  | -             | ACME  | PUD   | PSR2    | PSR10 |      |

| SZE (S4E)         TCCR1B         CKC1         CES1         -         CTC1         CS12         CS11         CS10         45           SZD (S4D)         TCNT1H         Timer/Countert - Counter Register High Byte         -         46           SZB (S4B)         OCR1AH         Timer/Counter 1 - Output Compare Register A Low Byte         47           SZB (S4B)         OCR1BL         Timer/Counter 1 - Output Compare Register A Low Byte         47           SZB (S4B)         OCR1BL         Timer/Counter 1 - Output Compare Register B Low Byte         47           SZB (S4B)         OCR1BL         Timer/Counter 1 - Output Compare Register I Sub Byte         47           SZB (S4B)         OCR1BL         Timer/Counter 1 - Input Capture Register I Sub Byte         48           SZB (S4B)         OCR1BL         Timer/Counter 2 (Btr)         53           SZB (S4B)         OCR2         FOC2         PWM2         COM2         CTC2         CS21         CS20         52           SZB (S4B)         OCR2         Timer/Counter 2 (Btr)         53         54         53         53         54         53         54         53         54         54         52         54         54         52         54         52         54         52         54                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |        | COM1A1      | COM1A0            | COM1B1           | COM1B0        |       |       |         |       |      |

| \$20.640)         TCNT1H         Timer/Counterl - Counter Register High Pyre         46           \$26.640)         CRN1L         Timer/Counterl - Counter Register A High Pyre         47           \$26.6461)         OCR1AH         Timer/Counterl - Output Compare Register A High Pyre         47           \$26.6461)         OCR1BH         Timer/Counterl - Output Compare Register B High Pyre         47           \$26.6461)         OCR1BH         Timer/Counterl - Output Compare Register B High Pyre         48           \$26.6461)         ICR1L         Timer/Counterl - Output Compare Register Low Pyre         48           \$26.6461         TCOR2         FOC2         PVM2         COM20         CTC2         CS21         CS20         52           \$24.6451         TOR2         FOC2         PVM42         COM20         CTC2         CS21         CS20         52           \$24.6451         TOR2         Timer/Counter2 (Output Compare Register Low Pyre         53         54         54         52           \$24.6451         WDTCR         -         -         MOTE         VDP1         WDP0         60           \$25.04401         UBRR/113         -         -         -         -         EEAR8         62           \$26.6350         EEAR1 <t< td=""><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                    |             |        |             |                   | -                |               |       |       |         |       |      |

| SZC (S4C)         TCNT1L         Tmer/Counter1 - Output Compare Register A Low Brie         447           SZA (S4B)         OCR1AL         Tmer/Counter1 - Output Compare Register A Low Brie         477           SZB (S4B)         OCR1BL         Tmer/Counter1 - Output Compare Register B Low Brie         477           SZB (S4B)         OCR1BL         Tmer/Counter1 - Output Compare Register B Low Brie         47           SZB (S4B)         OCR1BL         Timer/Counter1 - Input Capture Register Low Brie         48           SZB (S4B)         ICR1L         Timer/Counter2 - Output Compare Register         53           SZB (S4B)         ICR1L         Timer/Counter2 Output Compare Register         53           SZB (S4B)         ICR1Z         Timer/Counter2 Output Compare Register         53           SZB (S4B)         ICR1Z         Timer/Counter2 Output Compare Register         53           SZB (S4B)         UBRR1HI         -         -         ASZ         TCN2UB         TCR2UB         57           SZB (S4B)         UBRR1HI         -         -         -         UBRR1HI         78         54           SZB (S4B)         UBRR1HI         -         -         -         -         -         -         -         -         -         -         -         <                                                                                                                                                                                                                                                                                                                                                                                                                       |             |        |             |                   | Register High E  |               |       |       |         |       |      |

| S2B (S4A)         OCR1AH         Timer/Counter1 - Output Compare Register A High Byte         47           S2B (S4A)         OCR1BH         Timer/Counter1 - Output Compare Register B High Byte         47           S2B (S4B)         OCR1BH         Timer/Counter1 - Output Compare Register B High Byte         47           S2B (S4B)         OCR1BH         Timer/Counter1 - Input Capture Register B High Byte         48           S2B (S4B)         ICR1H         Timer/Counter1 - Input Capture Register High Byte         48           S2B (S4B)         OCR1Z         Timer/Counter2 (B lits)         52           S24 (S4A)         TCR2Z         PVM2         COM20         CTC2         CS21         CS20         52           S24 (S4A)         TCR2Z         Timer/Counter2 (B lits)         53         53         53         53         54         52           S24 (S4A)         MDTCR         -         -         -         AS2         TCN2UB         OCR2UB         TCR2UB         57           S22 (S4A)         MDTCR         -         -         -         -         EEARB         62         51         53           S20 (S4D)         UBRRHI         -         -         -         -         EEARB         62         51         53                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        |             |                   | <u> </u>         |               |       |       |         |       |      |

| \$28(4A)       OCR1AL       Timer/Counter1 - Output Compare Register A Low Byte       47         \$29(549)       OCR1BL       Timer/Counter1 - Output Compare Register B Low Byte       47         \$27(547)       Inter/Counter1 - Output Compare Register B Low Byte       48         \$26(546)       ICR1L       Timer/Counter1 - Input Copure Register Low Byte       48         \$26(546)       ICR1L       Timer/Counter1 - Input Copure Register Low Byte       53         \$24(544)       TCR1Z       Timer/Counter2 (8 Bits)       53         \$23(543)       OCR2A       Timer/Counter2 (0 Bits)       53         \$24(544)       TCN1Z       Timer/Counter2 (0 Bits)       57         \$21(541)       VDTCR       -       -       AS2       TCN2UB       OCR2UB       TCN2UB       57         \$21(543)       UBRRHI       -       -       -       UBRRHI       -       -       100000       000000       0000000       0000000000       000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |        |             |                   |                  |               |       |       |         |       |      |

| \$29.(54)       OCR1BH       Timer/Counter1 - Output Compare Register 1 Map Byte       47         \$28.(548)       OCR1BL       Timer/Counter1 - Input Capture Register Low Byte       47         \$26.(546)       ICR1L       Timer/Counter1 - Input Capture Register Low Byte       48         \$26.(546)       ICCR2       FOC2       PVM2       COM20       CTC2       CS21       CS20       52         \$24.(541)       Timer/Counter2 (6 Bits)       -       -       -       AS2       TCN2UB       OCR2UB       TCR2UB       57         \$21.(541)       WDTCR       -       -       -       WDTCE       WDP1       WDP0       60         \$20.(540)       UBRR1H       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        |             |                   |                  |               |       |       |         |       |      |

| \$27(\$47)       ICR1H       Timer/Counter1 - Input Capture Register High Byte       48         \$26(\$46)       ICR1L       Timer/Counter2 (B Bits)       648         \$24(\$44)       TCNT2       Timer/Counter2 (B Bits)       53         \$24(\$44)       TONT2       Timer/Counter2 (D Bits)       53         \$24(\$44)       TONT2       Timer/Counter2 (D Bits)       53         \$23(\$43)       OCR2       Timer/Counter2 (D Bits)       54         \$24(\$42)       ASSR       -       -       -       AS2       TCN2UB       OCR2UB       TCR2UB       57         \$21(\$41)       WDTCR       WDTCE       WDP2       WDP2       WDP1       WDP0       60         \$20(\$40)       UBRRH1       -       -       -       WDTCE       WDE       WDP2       WDP1       WDP0       60         \$21(\$41)       WDTCR       WD       WDTCE       WDE       WDP2       WDP1       62       21       51       53       51       53       51       53       51       53       51       53       53       53       53       53       53       53       53       53       53       53       53       53       53       53       53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$29 (\$49) | OCR1BH |             |                   |                  |               |       |       |         |       |      |

| S26 (546)         ICR1L         Timer/Counter1 - Input Capture Register Low Byte                          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53          53 <td>\$28 (\$48)</td> <td>OCR1BL</td> <td>Timer/Count</td> <td>ter1 – Output C</td> <td>ompare Regist</td> <td>er B Low Byte</td> <td></td> <td></td> <td></td> <td></td> <td>47</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$28 (\$48) | OCR1BL | Timer/Count | ter1 – Output C   | ompare Regist    | er B Low Byte |       |       |         |       | 47   |

| S25 (S45)         TCCR2         FOC2         PWM2         COM21         COM20         CTC2         CS22         CS21         CS20         52           S24 (S44)         TCNT2         Timer/Counter2 (B Bits)         53         53         53           S23 (S43)         OCR2         Timer/Counter2 (Duput Compare Register         54         53           S21 (S41)         MOTCE         -         -         -         -         54           S22 (S42)         ASSR         -         -         -         -         AS2         TCN2UB         CCR2UB         TCR2UB         57           S21 (S41)         WDTCR         -         -         -         -         -         -         EEARH         -         78           S20 (S40)         UBRRHI         -         -         -         -         -         EEARB         EEAR1         EEAR1         EEAR1         EEAR1         -         -         EEAR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | \$27 (\$47) | ICR1H  | Timer/Count | ter1 – Input Ca   | pture Register I | High Byte     |       |       |         |       | 48   |

| \$24 (\$44)         TCNT2         Timer/Counter2 (8 lits)         53           \$23 (\$43)         OCR2         Timer/Counter2 Output Compare Register         54           \$22 (\$42)         ASSR         -         -         -         AS2           \$21 (\$41)         WDTCR         -         -         -         WDTE         WDP0         60           \$21 (\$41)         WDTCR         -         -         -         WDTE         WDP1         WDP0         60           \$21 (\$41)         WDTCR         -         -         -         -         UBRRHI         -         78           \$20 (\$40)         UBRRHI         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | \$26 (\$46) |        | Timer/Count | ter1 – Input Ca   | pture Register I | _ow Byte      |       |       |         |       |      |

| \$23         OCR2         Timer/Counter/2 Output Compare Register         54           \$22 (\$42)         ASSR         -         -         -         AS2         TCN2UB         OCR2UB         TCR2UB         57           \$21 (\$41)         WDTCR         -         -         -         WDTC         WDP2         WDP1         WDP0         60           \$20 (\$40)         UBRRHI         -         -         -         -         UBR(118)         78           \$21 (\$41)         WDTCR         -         -         -         -         EEARB         62           \$15 (\$35)         EEAR         EEARA         EEAR6         EEAR5         EEAR4         EEAR3         PORTA1         PORTA1         PORTA2         PORTA4         PORTA3         PORTA2         PORTA1         PORTA0         115           \$16 (\$30)         DDRA         DDA7         DDA4         DDA1         DDA0         115           \$16 (\$30)         PORTB         PORTB6         PORTB5         PORTB3         PORTB3         PORTB2         PORTB1         PORTB0         117           \$16 (\$38)         PINB         PINB7         PINB6         PINB5         PINB4         PINB3         PINB1         PINB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | \$25 (\$45) |        |             |                   | COM21            | COM20         | CTC2  | CS22  | CS21    | CS20  | 52   |

| S22 (S42)         ASSR         -         -         -         AS2         TCN2UB         OCR2UB         TCR2UB         57           S21 (S41)         WDTCR         -         -         -         WDT0E         WDP2         WDP1         WDP0         60           S20 (S40)         UBRRI11         -         -         -         -         UBRRI113         78           S1F (S35)         EEARH         -         -         -         -         -         -         EEAR8         62           S1G (S30)         EEDR         EERRM E         EEAR1         EEAR0         62           S1G (S3C)         EECR         EECR         FEAR4         PORTA7         PORTA6         PORTA7         PORTA6         PORTA7         PORTA6         PORTA5         PORTA1         PORTA2         PORTA1         DDA0         115           S16 (S30)         PINA         PINA5         PINA4         PINA3         PINA2         PINA1         PINA0         1115           S16 (S30)         PORTB         PORTB7         PORTB6         PORTB5         PORTB4         PORTB2         PORTB1         PORTB0         1117           S16 (S30)         PINB         PINB6         PINB5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        | Timer/Count | ter2 (8 Bits)     |                  |               |       |       |         |       |      |

| \$21 (\$41)         WDTCR         -         -         -         WDTOE         WDE         WDP2         WDP0         60           \$20 (\$40)         UBRRHI         -         -         -         UBRR[11:3]         78           \$1F (\$3F)         EEARH         -         -         -         -         -         EEAR8         62           \$1F (\$3F)         EEARL         EEAR1         EEAR6         EEAR8         EEAR3         EEAR3         EEAR3         EEAR4         EEAR3         EEAR3         EEAR4         PORTA3         PORTA1         PORTA0         115           \$18 (\$38)         PORTA         PORTA7         PORTA6         PORTA5         PORTA4         PORTB3         PORTB1         PORTB0         1115           \$18 (\$39)         PINA         PINA7         PINA6         PINA5         PINA14         PINA3         PINA3         PINA3         PINA14         PINA3         PINA3         PINA3         PINA3         PINA3         PINA3         PINA3         PINA3         PINA14         PINA3         PINA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        | Timer/Count | ter2 Output Co    | mpare Register   |               | 1     | 1     | r       |       |      |

| \$20 (940)       UBRRHI       -       -       -       -       UBR(11:8)       78         \$1F (\$3F)       EEARH       -       -       -       -       EARB       62         \$1F (\$3F)       EEARL       EEAR       EEAR7       EEAR6       EEAR5       EEAR3       EEAR2       EEAR1       EEAR0       62         \$10 (\$3D)       EEDR       EEPROM Data Register       -       -       -       62         \$11 (\$3A)       PORTA       PORTB       PORTB       PORTB       PORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        | -           | -                 | -                | -             |       |       |         |       |      |

| \$1F (\$3F)         EEARL         -         -         -         -         -         EEAR3                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |        | -           | -                 | -                | WDTOE         | WDE   |       |         | WDP0  |      |

| STE (\$3E)         EEARL         EEAR1         EEAR2         EEAR3         EEAR3         EEAR2         EEAR1         EEAR1         62           \$1D (\$3D)         EEDR         EEPROM Data Register         62         62           \$1D (\$3C)         EECR         -         -         -         EERIE         EEMWE         EEWE         EERE         63           \$1B (\$3B)         DORA         DORA         DORA         PORTA6         PORTA5         PORTA4         PORTA2         PORTA1         PORTA0         115           \$14 (\$3A)         DDRA         DDA7         DDA6         DDA5         PORTB4         PORTB2         PORTB0         117           \$19 (\$39)         PINA         PINA7         PINA6         PINA5         PINA4         PINA3         PINA2         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB7         PORT66         PORT55         PORTB3         PORT2         PORTB1         PORTB0         117           \$16 (\$36)         PINC         PINC7         PINC6         PINC5         PORTC4         PORTC3         PORTC2         PORTC1         PORT00         123           \$16 (\$33)         PINC         PINC7         PINC6 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>R[11:8]</td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                      |             |        |             |                   |                  |               |       |       | R[11:8] |       |      |

| \$10 (\$3D)         EEDR         EEPRON Data Register         62           \$11 (\$3C)         EECR         -         -         -         ERIE         EEMRE         EEWRE         EERE         63           \$18 (\$3B)         PORTA         PORTA6         PORTA5         PORTA1         PORTA1         PORTA0         115           \$14 (\$3A)         DDRA         DDA7         PDRA6         PDRA5         PORTA1         PDRTA2         PORTA0         115           \$19 (\$39)         PINA         PINA7         PINA6         PINA5         PINA4         PINA3         PINA2         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB6         PORTB5         PORTB4         PORTB3         PORTB1         PORTB0         117           \$17 (\$37)         DDRB         DDB7         PINB6         PINB5         PINB4         PINB3         PINB2         PINB1         PINB0         117           \$16 (\$36)         PINB         PINB7         PORTB6         DDR5         PORT4         PORT3         PORT2         PINB1         PINB0         117           \$16 (\$36)         PINC         PINC6         PINC5         PINC4         PORT03         PINC2         PINC1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        |             |                   |                  |               |       |       |         |       |      |

| \$1C (\$3C)         EECR         -         -         -         EERIE         EERWE         EEWE         EERE         63           \$1B (\$3A)         DDRA         DDA7         DDA6         DDA5         DDA4         DDA3         DDA1         DDA0         115           \$19 (\$39)         PINA         PINA7         PINA6         PINA5         PINA3         PINA2         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB         PORTB         PORTB         PORTB         PORTB         PINA6         PINA5         PINA3         PINA2         PINA1         PINA0         115           \$17 (\$37)         DDRB         DDB7         DDB6         DDB5         DDB4         DDB3         DDB1         DDB0         117           \$16 (\$36)         PINB         PINB7         PINB6         PINB5         PINB3         PINB2         PINB1         PINB0         117           \$16 (\$34)         DDRC         DDC7         POC6         POC5         POC4         POC3         DDC2         DDC1         DDC0         123           \$14 (\$34)         DDRD         DDT7         PORT06         PORT05         PORT04         PORT03         PORT02         POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |        |             |                   | EEAR5            | EEAR4         | EEAR3 | EEAR2 | EEAR1   | EEAR0 |      |

| \$1B (\$3B)         PORTA         PORTA         PORTA6         PORTA5         PORTA4         PORTA3         PORTA2         PORTA1         PORTA0         115           \$14 (\$3A)         DDRA         DDA7         DDA6         DDA6         DDA3         DDA3         DDA2         DDA0         115           \$19 (\$38)         PINA         PINA4         PINA6         PINA5         PINA4         PINA3         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB7         PORTB6         PORTB5         PORTB4         PORTB3         PORTB2         PORTB1         PORTB0         117           \$17 (\$37)         DDR8         DDB7         DD86         DD85         DD84         PDR3         PINB2         PINB1         PINB0         117           \$16 (\$36)         PINB         PINB7         PINB6         PINB5         PINB4         PINB3         PINB3         PINB12         PINB1         PINB0         117           \$15 (\$35)         PORTC         PORTC7         PORT6         PORTC4         PORT3         PORT2         PORT01         PORT00         123           \$14 (\$34)         DDR0         DD7         PORT6         PORT04         PORT3         PORT02<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |        | EEPROMI     | Data Register     |                  |               | FEDIE |       |         |       |      |

| \$1A (\$3A)         DDRA         DDA7         DDA6         DDA5         DDA4         DDA3         DDA2         DDA1         DDA0         115           \$19 (\$39)         PINA         PINA7         PINA6         PINA5         PINA4         PINA3         PINA2         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB7         PORTB6         PORTB5         PORTB3         PORTB3         PORTB1         PORTB0         117           \$17 (\$37)         DDR8         DDB7         DDB6         DDB6         DDB5         DDB4         DDB3         DDB2         DDB1         DDB0         117           \$16 (\$36)         PINB         PINB7         PINB6         PINB5         PINB4         PINB3         PINB2         PINB1         PINB0         117           \$15 (\$35)         PORTC         PORTC7         PORT66         PORTC5         PORTC3         PORTC2         PORTC1         123           \$14 (\$34)         DDRC         DDC7         DDC6         DDC5         DDC4         DDC2         DDC1         DDC0         123           \$13 (\$33)         PINC         PINC7         PINC6         PINC5         PINC4         PINC3         PINC2         PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        |             |                   |                  |               |       |       |         |       |      |

| \$19 (\$39)         PINA         PINA7         PINA6         PINA5         PINA4         PINA3         PINA2         PINA1         PINA0         115           \$18 (\$38)         PORTB         PORTB         PORTB6         PORTB6         PORTB6         PORTB4         PORTB3         PORTB2         PORTB1         PORTB0         117           \$17 (\$37)         DDRB         DDR5         DDB6         DDB5         DDB4         DDB3         DDB2         DDB1         DDB0         117           \$16 (\$36)         PINB         PINB7         PINB6         PINB5         PINB4         PINB3         PINB2         PINB1         PINB0         117           \$15 (\$35)         PORTC         PORTC7         PORTC6         PORTC5         PORT4         PORT2         PORT2         PORT0         123           \$14 (\$34)         DDRC         DDR7         PORT06         PORT05         PORT04         PORT03         PORT02         PORT01         PORT00         123           \$13 (\$33)         PIND         PIND7         PINC6         PINC5         PINT4         PINC3         PINC2         PINT0         128           \$11 (\$30)         DDR0         DDD7         DDD6         DDD5         DD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |        |             |                   |                  |               |       |       |         |       |      |

| \$18 (\$38)         PORTB         PORTB7         PORTB6         PORTB5         PORTB4         PORTB3         PORTB2         PORTB1         PORTB0         117           \$17 (\$37)         DDR8         DDB7         DDB6         DDB5         DDB4         DDB3         DDB2         DDB1         DDB0         117           \$16 (\$36)         PINB         PINB7         PINB6         PINB6         PINB5         PINB3         PINB2         PINB1         PINB0         117           \$15 (\$35)         PORTC         PORTC7         PORTC6         PORTC6         PORTC4         PORTC3         PORTC2         PORTC1         PORT00         123           \$14 (\$34)         DDRC         DDC7         DDC6         DDC5         DDC4         PORT3         PORTD         PORT0         123           \$14 (\$34)         DDRC         PINC7         PINC6         PINC5         PINC4         PINC3         PINC2         PINC1         PORT0         128           \$11 (\$31)         DDR         DDD7         DDD6         DDD5         DD14         DD13         DD12         DD11         PORT0         128           \$11 (\$30)         PIND         PIND6         PIND6         PIND6         PIND3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |        |             |                   |                  |               |       |       |         |       |      |

| \$17 (\$37)         DDRB         DDB7         DDB6         DDB5         DDB4         DDB3         DDB2         DDB1         DDB0         117           \$16 (\$36)         PINB         PINB         PINB6         PINB5         PINB4         PINB2         PINB1         PINB0         1117           \$15 (\$35)         PORTC         PORTC7         PORTC6         PORTC5         PORTC4         PORTC3         PORTC2         PORTC1         PORT0         123           \$14 (\$34)         DDRC         DDC7         DDC6         DDC5         DDC4         DDC2         DDC1         DDC0         123           \$13 (\$33)         PINC         PINC7         PINC6         PINC5         PINC4         PINC3         PINC2         PINC1         PINC0         123           \$11 (\$31)         DDRD         PORTD7         PORTD6         PORTD5         PORTD4         PORTD3         PORTD2         PORTD1         PORTD0         128           \$10 (\$30)         PIND         PIND7         PIND6         PIND5         PIND4         PIND3         PIND2         PIND1         PIND0         128           \$00 (\$22)         SPCR         SPIP         MCOL         -         -         -         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |        |             |                   |                  |               |       |       |         |       |      |

| \$16 (\$36)PINBPINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0117\$15 (\$35)PORTCPORTC7PORTC6PORTC6PORTC5PORTC3PORTC2PORTC1PORTC0123\$14 (\$34)DDRCDDC7DDC6DDC5DDC4DDC3DDC2DDC1DDC0123\$13 (\$33)PINCPINC7PINC6PINC5PINC4PINC3PINC2PINC1PINC0123\$12 (\$32)PORTDPORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0128\$11 (\$31)DDR0DDD7DD66DD5DD4DD33DD22DD1DD00128\$11 (\$31)DDR0PIND7PIN66PIND5PIND4PIND3PIND2PIND1PIND0128\$06 (\$2F)SPDRSPIFWC0L69\$05 (\$2F)SPDRSPIFWC0L74\$06 (\$2C)UDRUART I/O Z#WC0L74\$06 (\$2C)UDRUART KegisterVICEVICEVICEVICE7474\$06 (\$2A)UCSRARXCETXCEUDREFEOR-U2XMPCM74\$09 (\$29)UBRUART Baud Rate RegisterVICEACICACIS1ACIS0102102\$09                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |        |             |                   |                  |               |       |       |         |       |      |

| \$15 (\$35)         PORTC         PORTC7         PORTC6         PORTC5         PORTC4         PORTC3         PORTC2         PORTC1         PORTC0         123           \$14 (\$34)         DDRC         DDC7         DDC6         DDC5         DDC4         DDC3         DDC2         DDC1         DDC0         123           \$13 (\$33)         PINC         PINC7         PINC6         PINC5         PINC4         PINC3         PINC2         PINC1         PINC0         123           \$12 (\$32)         PORTD         PORTD7         PORTD6         PORTD5         PORTD4         PINC3         PINC2         PINC1         PINC0         123           \$11 (\$31)         DDRD         PORTD7         PORTD6         PORTD5         PORTD4         PORTD3         PORTD2         PORTD1         PORTD0         128           \$11 (\$31)         DDRD         DDD7         DDD6         DD5         DD4         DD3         DD22         DD11         DD00         128           \$10 (\$30)         PIND         PIND7         PIND6         PIN5         PIN4         PIN3         PIN2         PIN1         PIN00         128           \$00 (\$20)         SPR         SPIE         DSR         DORD         M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |        |             |                   |                  |               |       |       |         |       |      |

| \$14 (\$34)         DDRC         DDC7         DDC6         DDC5         DDC4         DDC3         DDC2         DDC1         DDC0         123           \$13 (\$33)         PINC         PINC7         PINC6         PINC5         PINC4         PINC3         PINC2         PINC1         PINC0         123           \$12 (\$32)         PORTD         PORTD7         PORTD6         PORTD5         PORTD4         PORTD3         PORTD2         PORTD1         PORTD0         128           \$11 (\$31)         DDRD         DDD7         DD6         DD5         DD44         DD3         DD2         DD11         DD00         128           \$10 (\$30)         PIND         PIND7         PIND6         PIND5         PIND4         PIND3         DD2         PIN1         PIND0         128           \$0F (\$52F)         SPDR         SPI Data Register         -         -         -         -         SP12X         68           \$0D (\$2D)         SPCR         SPIE         SPE         DORD         MSTR         CPOL         CPHA         SPR1         SPR0         67           \$00 (\$2D)         SPCR         SPIE         SPE         DORD         MSTR         CPOL         CPHA         SPR1 </td <td></td>                                                                                                                                                                                                                                                                                                                                                                                       |             |        |             |                   |                  |               |       |       |         |       |      |