PML2852

### **FEATURES**

- · Wide gates for efficient product term use

- Multiple I/O pins for 16–32 bit buses or up to 32-bit data flow

- Multiple I/O pins for multiple-port data handling

- Multiple clocks for independent state machines and storage banks

- 100% connectible, no place and route restrictions

- Erasable and one time programmable versions available

- Scan test

- Low CMOS power dissipation = 525mW max.

- Power down mode (52mW max.)

- Power on reset

- Security fuse for copy protection

- Supported by advanced SNAP and SLICE development systems

#### PERFORMANCE

- 35ns max. pin-to-pin for 32-bit decoders

- 40ns max. internal, 55ns max. pin-to-pin for 16-bit multiplexers

- 33MHz max. throughput for 16-bit latches

- 18-50MHz max, for 10-bit counters

- 31MHz max. for 10-bit shift registers

- 15ns (typ.) delay for internal NANDs

- 50MHz max. flip-flop toggle rate

### **APPLICATIONS**

- Bus interface and control (microchannel, VME, NuBus, etc.)

- Microcomputer peripheral interface and control (printers, SCSI, hard disk drives, etc.)

- Multiport memory control and arbitration (cache, DRAM, VRAM, etc.)

- Intelligent instrumentation (data acquisition, testers, medical equipment, etc.)

- Industrial control (process control, motor control, engine control, etc.)

- Communication network control (LAN, Ethernet, T1, TDMA, etc.)

- General purpose logic integration

- Laptops, pocket computers, and handheld instruments

- Low-end gate array replacement for quick prototyping

### **SNAP DEVELOPMENT SYSTEM**

- Supports third-party schematic entry formats

- Versatile EDIF-compatible netlist format for design portability

- TTL macro library for automatic mapping

- · Logic, timing, and fault simulation

- Automatic test vector generator

- Espresso logic minimizer

- Boolean equation extractor from JEDEC fusemap

### DESCRIPTION

The Philips Semiconductors family of Programmable Macro Logic is optimized for handling wide buses, wide datapaths, and multiple-port applications with the highest throughputs among high density PLDs and FPGAs. The PML2852 now expands Philips Semiconductors CMOS PML product offering into the 32-bit arena. Fabricated with a high-performance EPROM process, the PML2852 is ideal in today's bus interface control, microprocessor peripheral control, memory interface, communications, instrumentation, and industrial control. It is capable of replacing large amounts of TTL

SSI and MSI logic, and literally integrates a complete custom microcontroller.

The PML2852 incorporates the folded NAND array architecture, which provides 100% connectivity to eliminate the routing restrictions associated with other high density PLD/FPGA architectures. The array of wide-input NAND gates enables the designer to implement any wide-gate logic function, from decoders to multiplexers, with no more than two gate-level delays. It also allows implementation of multiple levels of logic within the chip, without wasting I/O pins. Its flexible and potent flip-flop building blocks provide for high throughput data storage, high speed state machines, and fast counters.

The PML2852 also incorporates two unique features: scan test and power down. With user-controlled scan test, the PML2852 significantly reduces system functional test time by providing access to all of its internal registers. In the user-controlled power down mode, the PML2852 power dissipation is reduced to a mere 52mW, making it ideal for laptop or pocket computers and handheld instruments.

Thanks to its high density and its flexible architecture, the PML2852 provides Instant gate array capabilities for all general purpose logic integration. As such, the PML2852 eliminates the NRE costs, risks, inventory problems, and hard to use design tools associated with semicustom and full custom approaches. It allows the designer to quickly bring concepts to silicon for faster learning cycles and a much shorter time to market. Functional prototypes are available within minutes.

The SNAP development software is designed to fully exploit the flexibility and density of the PML2852. It accepts a variety of design entry formats, including schematic, logic equations, and state equations in any combination for maximum flexibility. Its powerful features, but ease of use, allows literally push-button operation.

Together, the PML2852 and SNAP constitute the designer's personal **desktop silicon foundry**.

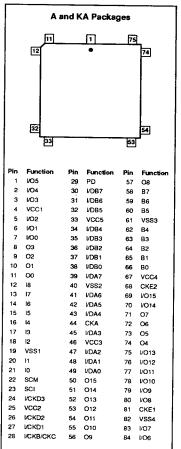

### **ORDERING INFORMATION**

| DESCRIPTION                               | t <sub>PD</sub> (MAX) | ORDER CODE   | DRAWING NUMBER |

|-------------------------------------------|-----------------------|--------------|----------------|

| 84-pin Plastic Leaded Chip Carrier        | 35ns                  | PML2852-35A  | 0399F          |

| 84-pin "J" Leaded Ceramic Cerquad Package | 35ns                  | PML2852-35KA | 1551           |

| 84-pin Plastic Leaded Chip Carrier        | 50ns                  | PML2852-50A  | 0399F          |

| 84-pin "J" Leaded Ceramic Cerquad Package | 50ns                  | PML2852-50KA | 1551           |

NuBus is a trademark of Texas Instruments, Inc.

October 22, 1993 486 853–1586 11164

PML2852

### PIN CONFIGURATION

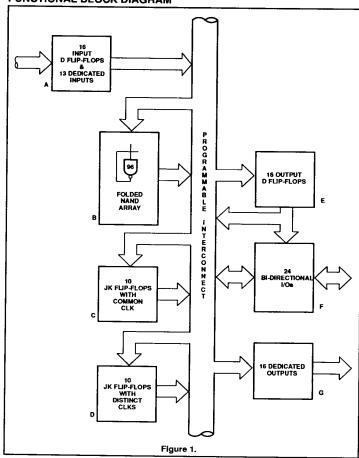

### **FUNCTIONAL BLOCK DIAGRAM**

PML2852

October 22, 1993

488

PML2852

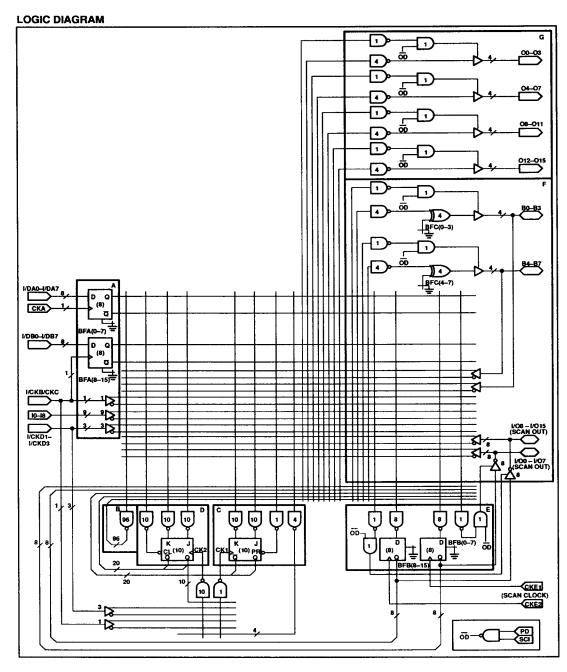

### STRUCTURE

- 112 possible foldback NAND gates:

- 96 internal NAND

- 16 from the I/O macros

- 114 additional logic terms

- 53 possible inputs (with programmable polarity)

- 29 dedicated inputs

- 24 bidirectional I/Os

- 24 bidirectional pins

- 16 dedicated output pins

- 52 flip-flops

- 40 possible outputs with Output Enable control (8 with programmable polarity)

- Multiple independent clocks

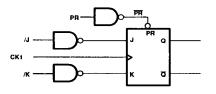

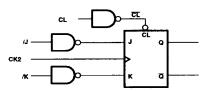

- 20 Buried JK-type flip-flops with foldback (JKFFs):

- 10 JKFFs with one shared preset signal and one shared clocked signal originating from the clock array.

- 10 JKFFs with 10 independent clock signals originating from the clock array and 10 independent clear signals

- 258 inputs per NAND gate

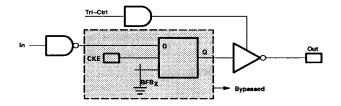

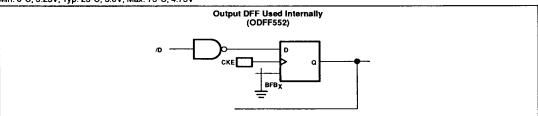

- Bypassable Input D-type flip-flop (DFFs)/Combinatorial Inputs:

- 16 DFFs/combinatorial inputs

- DFFs clocked in two groups of eight

- DFFs not bypassed in unprogrammed state

- Independent bypass fuse on each DFF

- Inputs/bypassable D-type flip-flop outputs/foldback NAND gates:

- 16 output DFFs/combinatorial inputs/outputs with individual Output Enable control

- DFFs clocked in two groups of eight

- DFFs not bypassed in unprogrammed state

- Independent bypass fuse on each DFF

- The DFF can be used as an internal DFF or an internal foldback NAND gate.

- Combinatorial inputs:

- 9 dedicated inputs to the NAND array

- 3 inputs optional to NAND array and/or clock array

- 1 input optional to NAND array and/or clock array, and/or clock of Input D Flip-Flops (Group B)

- Separate clock array:

- Separate clock array for JKFFs clock inputs

- 4 inputs to clock array originated from NAND array

- 4 inputs (with programmable polarity) directly from input pins

- 10 inputs from Q outputs of JKFFs with clear

- Dedicated clocks:

- One dedicated clock for input DFFs (Group A)

- Two dedicated clocks for output DFFs (Group E)

- Scan test feature:

- Scan chain is implemented through the 20 buried JKFFs and 16 output DFFs

- Pins SCI, SCM, and CKE1 are used to operate the scan test

- Power down mode

- Dedicated pin (PD) freezes the circuit when brought to logic "1". The circuit remains in the same state prior to the logic "0" to logic "1" transition of the "PD" pin.

- When in the power down mode, the SCI pin acts as the 3-State pin for the 40 outputs.

- Power on reset:

- All flip-flops (16 input DFFs, 20 buried JKFFs, and 16 output DFFs) are reset to logic "0" after V<sub>CC</sub> power on.

### **ARCHITECTURE**

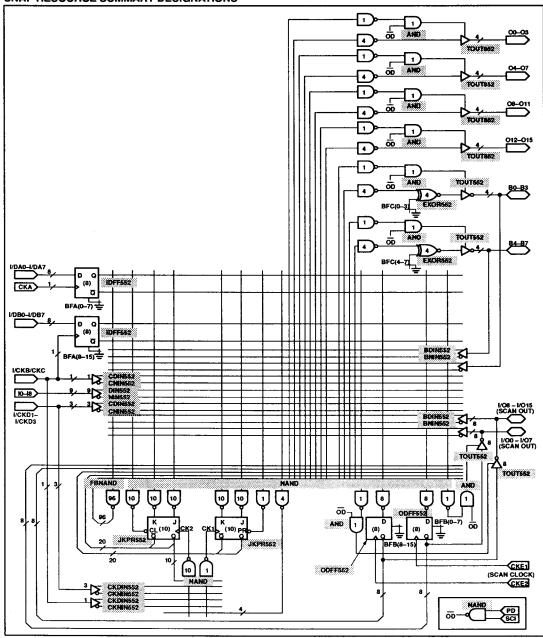

The core of the PML2852 is a programmable NAND array of 96 NAND gates and 20 buried JKFFs. The output of each NAND gate folds back upon itself and all other NAND gates and flip-flops. The 'O' and 'O' output of each flip-flop also folds back in the same manner. Thus, total connectivity of all logic functions is achieved in the PML2852. Any logic function can be created within the core without wasting valuable I/O pins. Furthermore, a speed advantage is acquired by implementing multi-level logic within a fast internal core without incurring any delays from the I/O buffers. Figure 1 shows the functional block diagram of the PML2852.

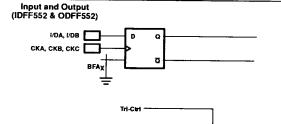

### Macro Celis

There are 16 bypassable DFFs on the input to the NAND array. These flip-flops are split in two banks of 8 (Bank A and Bank B). Each

bank of flip-flops has a common clock. In the unprogrammed state of the device the flip-flops are active. In order to bypass any DFF, its respective bypass fuse (BFA<sub>X</sub>) must be programmed.

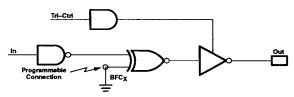

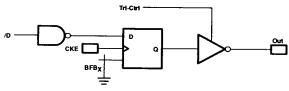

The 16 I/O pins ( $\rm IO_0$  -  $\rm IO_{15}$ ) and their respective D flip-flop macros can be used in any one of the following configurations:

- As combinatorial input(s):

Each of the 16 3-State outputs can be individually disabled by the associated NAND term and the pin is used as an inverting or non-inverting input.

- As registered DFF outputs: These DFFs are split into two banks of 8, and each bank is clocked separately. The bypass fuse BFB<sub>X</sub> (see PML2552 Logic Diagram) is used to bypass any one of these DFFs. The flip-flops are all active in an unprogrammed device.

- As combinatorial outputs: By programming the bypass (BFB<sub>X</sub>) fuse of any one of the DFFs, the flip-flop(s) is bypassed. The I/O pin can then be used as a combinatorial output.

- 4. As Internal foldback DFFs or foldback NAND gates: When the I/O pin is used as an input, the output macro can be used as a buried DFF or a foldback NAND term. If the bypass fuse is programmed, the macro will act as a foldback NAND term. Otherwise it will act as a buried DFF.

The 8 bidirectional pins (B0-B7) can be used as either combinatorial inputs or outputs with programmable polarity. The Exclusive-OR polarity gates are non-inverting in the unprogrammed state.

The NAND signal labeled 'OD' (Output Disable) shown on the PML2852 logic diagram is used for the Power Down mode operation. This signal disables the outputs when the device enters the Power Down mode and SCI is high.

### Clock Array

The 20 buried JKFFs are clocked through the 'Clock Array'. The Clock Array consists of 11 NAND terms. Ten of these terms are connected to the clock inputs of the Bank A flip-flops that can be clocked individually. One NAND gate is connected to Bank B flip-flops that have a common clock. There are 18 inputs to the clock array. Four come directly from the input pins (with programmable polarity), 4 inputs are from 4 NAND gates connected directly to the folded NAND array. 10 inputs are from the Q outputs of the JKFFs with clear.

PML2852

### **SCAN TEST FEATURE**

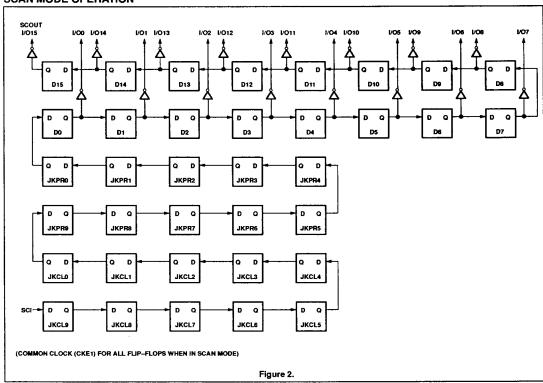

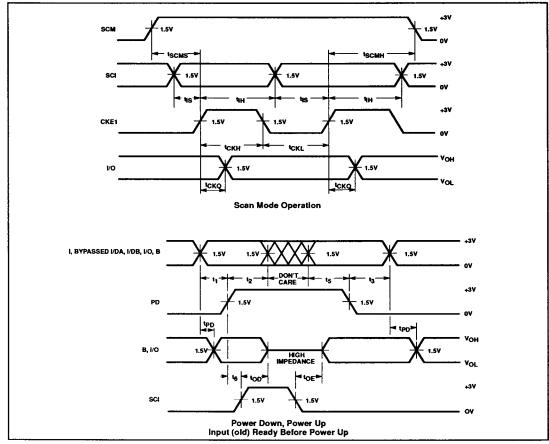

With the rise in the ratio of devices on a chip to the number of I/O pins, Design For Testability is becoming an essential factor in logic design methodology. The PML2852 incorporates a variable length scan test feature which permits access to the internal flip-flop nodes without requiring a separate external I/O pin for each node accessed. Figure 2 (Scan Mode Operation) shows how a scan chain is implemented through the 20 buried JKFFs and 16 output DFFs. Two dedicated pins, SCI (Scan In) and SCM (Scan Mode), are used to operate the scan test. The SCM pin is used to put the circuit in scan mode. When this pin is brought to a logic "1", the circuit enters the scan mode.

In this mode it is possible to shift an arbitrary test pattern into the flip-flops. The SCI pin is used to input the pattern. The inverted outputs of flip-flops D0 - D15 are observable on pins I/O0 - I/O15.

The following are features and characteristics of the device when in Scan Mode:

- CKE1 is the common scan-clock for all the flip-flops when in scan mode. CKE1 overrides all clock resources of normal operational mode.

- The Preset (PR) and Clear (CL) functions of the flip-flops are disabled.

- Scan overrides the bypass fuse of the flip-flops. This means that all the

bypassable DFFs remain intact during scan operation even though they may have been bypassed during normal operation.

- To observe the SCAN data, the output buffers must be enabled by the Output Enable (tri-ctrl) terms.

- The outputs of the flip-flops are complemented on pins I/O0 - I/O15.

- All external inputs to flip-flops in the scan chain are disabled when the device enters the scan mode.

- Blowing the security fuse does not disable the Scan Test feature.

### SCAN MODE OPERATION

PML2852

### **SCAN TEST STRATEGY**

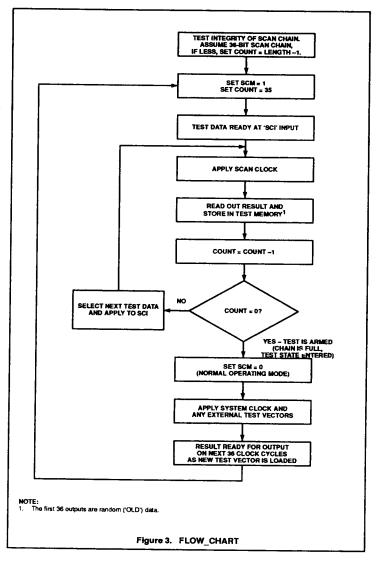

The scan test pattern is design dependent and the user must make considerations for Design For Testability (DFT) during the initial stages of the design. A typical test sequence is to pre-load (i.e., enter a state); revert to normal operation (i.e., activate the next state transition); go back to scan mode to check the result. Note that the scan test feature available in the PML2852 is a variable length scan chain. The DATA entered at SCI (JKCL9) can be accessed anywhere between 21 clock cycles (at I/O0) to 36 clock cycles (at I/O15). For the strategy discussed here, DATA is read out after 36 clocks at I/O15 (i.e., D15). The following operation sequence suggests a possible scan test method.

A conservative test policy demands proof that the test facility is working. Thus, to prove Scan Chain holds and maintains correct data:

- Fill chain with several patterns (for example, all ones and all zeros).

- b. Retrieve same patterns.

The user is responsible for managing an external test memory buffer for applied vectors and results, as part of the test equipment.

- Parallel readout of I/O0 I/O15 is possible, but assume only I/O15 is used for this strategy.

- The first DATA entered at SCI (or JKCL9) will be the content of D15 after 36 clocks.

This DATA will be inverted at the output pin I/O15 (i.e., SCOUT). The last DATA entering the scan chain will be the content of JKCL9. Thus, the scan chain resembles a first-in-first-out shift register with inverted outputs (I/O0 I/O15).

- 'Test Data' is read in at the SCI input and read out of the SCOUT output pin (I/O15). To enter 'Test Data':

- Put device in Scan Mode by applying the scan control signals (SCM=1).

- b. Clock device with scan clock (CKE1).

- c. Apply consecutive serial test vectors.

- d. Read back results as new 'Test Data' (States) are applied. The first 36 outputs read at SCOUT (I/O15) are random ('old') data (e.g., remnant of Step 1).

- e. Apply 36 'Test Data' until the chain is full.

- To apply 'Test Data' (States), exit Scan Mode and apply on system clock together with any other possible test vectors.

- 5. To read result of the state transition, re-enter scan and apply the scan clock (CKE1). The result of the state transition in JKCL9 will be available at SCOUT (I/O15) after 36 clocks. The results can be stored in a user defined test memory buffer in inverted logic representation.

- As the results are being read and stored, new 'Test Data' can be entered via SCI.

- Repeat for all test patterns of interest.

- Figure 3 (FLOW\_CHART) depicts a flow chart version of the test sequence.

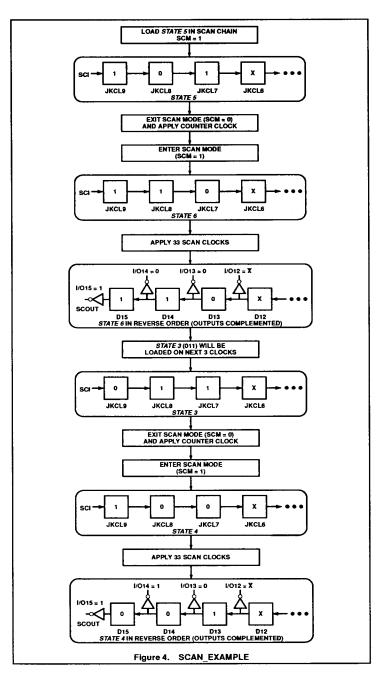

### A Simple Example

Assume the last three cells of the scan chain (JKCL9, JKCL8, JKCL7 in Figure 4 contain a 3-bit up counter. Our test vector will be a single clock applied to the counter. Suppose we wish to first check the State 5 (i.e., 101) to State 6 (i.e., 110) transition, then the State 3 (i.e., 011) to State 4 (i.e., 100) transition. Assume the scan chain has been pre-verified and we may begin.

Enter scan mode (set SCM=1)I apply 36 bits in sequence so that the value 101 (i.e., State 5) resides in the last three cells. Exit scan mode (set SCM=0) and apply a single clock to the counter. Now the value 110 (i.e., State 6) resides in the last three cells. Re-enter scan mode (set SCM=1) and read back 36 bits from position I/O15. Note that the outputs are complemented and are also read back in the reverse order. Therefore the value for STATE 6 read at I/O15 will be 100 which is the complement of STATE 6 (110) read in the reverse order.

As this is being read back, apply a new state, serially equal to the value 011 (i.e., State 3). This state should be loaded on the last three clock cycles during which STATE 6 is being read back at I/O15. After STATE 3 has been loaded (and STATE 6 read back), exit scan mode and apply a single clock which will invoke the STATE 3 (i.e., 011) to STATE 4 (i.e., 100) transition. Re-enter scan mode and read back 36 bits at I/O15. The last three bits should contain 110 which is the complement of State 4 read in the reverse order. 4 (SCAN\_EXAMPLE) shows a flow diagram of this example. Note that the States will always be complemented and read back in the reverse at I/O15. Other sequences may be applied in the same manner.

A possible alternative to this example is to read back the output states at I/O0 (D0) instead of I/O15 (JKCL9). This will allow the outputs to be read back after 21 clock cycles rather than the 36 used in the above example.

PML2852

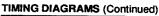

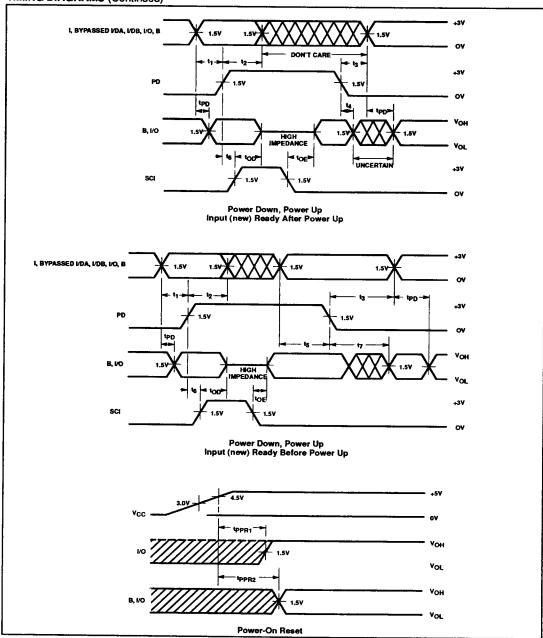

### POWER DOWN

The PML2852 offers the user controlled capability of putting the device to "sleep" where power dissipation is reduced to very low levels. When brought to a logic "1", the PD pin freezes the circuit while reducing the power. All data is retained. This not only includes that of the registers, but also the state of each foldback gate. For those cases where it is desirable to 3-State the outputs, that can be accomplished by raising the SCI pin to a logic "1".

There is one point that should be noted while the circuit is in its power-down mode. The switching of any external clock pin will cause a disruption of the data. All clocks must be frozen before the circuit goes into power-down and stay that way until it powered back up. Clocks that are internally generated and feed the clock array are automatically stopped by the power-down circuitry. Any other input can toggle without any loss of data

#### NOTE:

- During power down, external clocks (CKA, CKB/CKC, CKE1, CKE2) should not change.

- SCM must be "0" as in normal operation mode

- External clock recovery time (low-to-high) is 60ns (high-speed) and 70ns (standard) after the device is powered up.

- Power Down Timing Diagrams on pages 502 and 503 are for combinatorial operation only.

#### **DEVELOPMENT TOOLS**

The PM2852 is supported by the Philips Semiconductors SNAP software development package and a multitude of hardware and software development tools. These include industry standard PLD programmers and CAD software.

### SNAP

### Features

- Schematic entry using DASH<sup>TM</sup> 4.0 or above or OrCAD<sup>TM</sup> SDT III

- State Equation Entry

- Boolean Equation Entry

- Allows design entry in any combination of above formats

- Simulator

- Logic and fault simulation

- Timing model generation for device timing simulation

- Synthetic logic analyzer format

- Macro library for standard TTL and user defined functions

- Device independent netlist generation

- JEDEC fuse map generated from netlist

SNAP (Synthesis, Netlist, Analysis and Program) is a versatile development tool that speeds the design and testing of PML. SNAP combines a user-friendly environment and powerful modules that make designing with PML simple. The SNAP environment gives the user the freedom to design independent of the device architecture.

The flexibility in the variations of design entry methodologies allows design entry in the most appropriate terms. SNAP merges the inputs, regardless of the type, into a high-level netlist for simulation or compilation into a JEDEC fuse map. The JEDEC fuse map can then be transferred from the host computer to the device programer.

SNAP's simulator uses a synthetic logic analyzer format to display and set the nodes of the design. The SNAP simulator provides complete timing information, setup and hold-time checking, plus toggle and fault grading analysis.

SNAP operates on an IBM® PC/XT, PC/AT, PS/2, or any compatible system with DOS 2.1 or higher. A minimum of 640K bytes of RAM is required together with a hard disk.

#### **DESIGN SECURITY**

The PML2852 has a programmable security fuse that controls the access to the data programmed in the device. By using this programmable feature, proprietary design implemented in the device cannot be copied or retrieved.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | PARAMETER                   | RATINGS     | UNIT            |

|------------------|-----------------------------|-------------|-----------------|

| Vcc              | Supply voltage              | +7          | V <sub>DC</sub> |

| VIN              | input voltage               | +5.5        | V <sub>DC</sub> |

| V <sub>OUT</sub> | Output voltage              | +5.5        | V <sub>DC</sub> |

| I <sub>IN</sub>  | Input currents              | -30 to +30  | mA              |

| l <sub>OUT</sub> | Output currents             | +100        | mA              |

| T <sub>amb</sub> | Operating temperature range | 0 to +75    | °C              |

| T <sub>stg</sub> | Storage temperature range   | -65 to +150 | °C              |

### NOTE:

Stresses above those listed may cause malfunction or permanent damage to the device. This

is a stress rating only. Functional operation at these or any other condition above those

indicated in the operational and programming specification of the device is not implied.

### THERMAL RATINGS

| TEMPERATUR                                 | E     |

|--------------------------------------------|-------|

| Maximum junction                           | 150°C |

| Maximum ambient                            | 75°C  |

| Allowable thermal rise ambient to junction | 75°C  |

DASH is a trademark of Data I/O Corporation.

OrCAD is a trademark of OrCAD, Inc.

IBM is a registered trademark of International Business Machines Corporation.

PML2852

## DC ELECTRICAL CHARACTERISTICS 0°C ≤ T<sub>amb</sub> ≤ +75°C, 4.75V ≤ V<sub>CC</sub> ≤ 5.25V

|                     |                                        |                                              |                            |      | LIMITS |                       |      |

|---------------------|----------------------------------------|----------------------------------------------|----------------------------|------|--------|-----------------------|------|

| SYMBOL              | PARAMETER                              | TEST CONDIT                                  | rions                      | MIN  | TYP1   | MAX                   | UNIT |

| Input volt          | age                                    |                                              |                            |      |        |                       |      |

| V <sub>IL</sub>     | Low                                    | V <sub>CC</sub> = MI                         | N                          | -0.3 |        | 0.8                   | V    |

| V <sub>IH</sub>     | High                                   | V <sub>CC</sub> = MA                         | ×                          | 2.0  |        | V <sub>CC</sub> + 0.3 | V    |

| Output vo           | Itage                                  |                                              |                            |      |        |                       |      |

| V <sub>OL</sub>     | Low                                    | V <sub>CC</sub> = MIN, I <sub>OL</sub>       | ± 5m <b>A</b>              |      | I      | 0.45                  | ٧    |

| V <sub>OH</sub>     | High                                   | V <sub>CC</sub> = MIN, I <sub>OH</sub>       | = <b>–</b> 2m <b>A</b>     | 2.4  |        |                       | ٧    |

| Input curr          | ent                                    |                                              |                            |      |        |                       |      |

| I <sub>IL</sub>     | Low                                    | V <sub>IN</sub> = GN                         | D                          |      |        | -10                   | μА   |

| l <sub>IH</sub>     | High                                   | V <sub>IN</sub> = V <sub>CC</sub>            |                            |      |        | 10                    | μΑ   |

| Output cu           | rrent                                  |                                              |                            |      |        |                       |      |

| I <sub>O(OFF)</sub> | Hi-Z state                             | $V_{OUT} = V_0$                              | cc                         |      |        | 10                    | μА   |

| -,,                 | ]                                      | V <sub>OUT</sub> = Gi                        | ND                         |      |        | -10                   | μА   |

| Іон                 | Output High                            | V <sub>CC</sub> = MIN, V <sub>OU</sub>       | <sub>T</sub> = 2.4V        |      |        | -2                    | mA   |

| loL                 | Output Low                             | V <sub>CC</sub> = MIN, V <sub>OU1</sub>      | r = 0.45V                  |      |        | 5                     | mA   |

| los                 | Short-circuit <sup>5</sup>             | V <sub>OUT</sub> = GI                        | ND                         |      | · ·    | -100                  | mA   |

| Icc                 | V <sub>CC</sub> supply current         | V <sub>CC</sub> = MAX, No load               | CMOS input <sup>2</sup>    |      | 60     | 100 <sup>6</sup>      | mA   |

|                     |                                        | f = 1MHz                                     | TTL input <sup>3</sup>     |      | 65     | 120 <sup>6</sup>      | mΑ   |

| I <sub>SB</sub>     | Standby V <sub>CC</sub> supply current | V <sub>CC</sub> = MAX, No load               | CMOS input                 |      | 1.0    | 10                    | mA   |

|                     |                                        | PD = V <sub>IH</sub>                         | TTL input                  |      | 1.5    | 10                    | mA   |

| Capacitar           | nce                                    |                                              |                            |      |        |                       |      |

| C <sub>IN</sub>     | Input                                  | V <sub>CC</sub> = 5V, T <sub>amb</sub> = +25 |                            |      | 8      |                       | рF   |

| C <sub>B</sub>      | 1/0                                    | $V_{CC} = 5V, T_{amb} = +25$                 | °C, V <sub>IO</sub> = 2.0V |      | 16     |                       | рF   |

### NOTES:

- All typical values are at V<sub>CC</sub> = 5V, T<sub>amb</sub> = +25°C.

CMOS inputs: V<sub>IL</sub> = GND, V<sub>IH</sub> = V<sub>CC</sub>.

TTL inputs: V<sub>IL</sub> = 0.45V, V<sub>IH</sub> = 2.4V.

All voltage values are with respect to network ground terminal.

- 5. Duration of short-circuit should not exceed one second. Test one at a time.

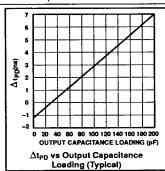

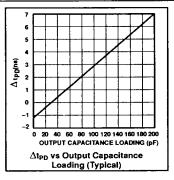

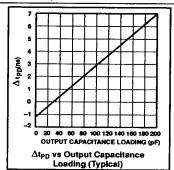

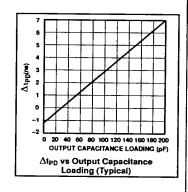

- ΔI<sub>CC</sub> vs. Frequency = 4mA/MHz max.

### **TEST LOAD CIRCUITS**

### **VOLTAGE WAVEFORMS**

PML2852

### MACRO CELL AC SPECIFICATIONS

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V (SNAP Resource Summary Designations in Parentheses)

# Input Buffer (DIN552, NIN552, BDIN552, BNIN552 CDIN552, CNIN552, CKDIN552, CKNIN552, IDFF552\*)

|                  | PARAMETER |         |            | LIMITS |     |        |      |     |    |  |

|------------------|-----------|---------|------------|--------|-----|--------|------|-----|----|--|

| SYMBOL To        | From      | PI      | PML2852-35 |        |     | AL2852 | UNIT |     |    |  |

|                  | (Output)  | (input) | MIN        | TYP    | MAX | MIN    | TYP  | MAX |    |  |

| t <sub>PHL</sub> | х         | ı       | 5          | 7      | 10  | 7      | 10   | 15  | ns |  |

| <b>t</b> eth     | x         | 1       | 5          | 7      | 10  | 7      | 10   | 15  | ns |  |

| t <sub>PHL</sub> | Υ         | 1       | 5          | 7      | 10  | 7      | 10   | 15  | ns |  |

| ФLH              | Y         | I       | 5          | 7      | 10  | 7      | 10   | 15  | ns |  |

\* When input D flip-flop is bypassed. Input Pins: 12–18, 20, 21, 24, 26–28. I/O and Bidirectional Pins: 1–3, 5–7, 58–60, 62–66, 69, 70, 75–80, 83, 84. Bypassed DFF at Pins: 30–32, 34–39, 41–43, 45, 47–49.

## Internal NAND of Main Array (FBNAND, NAND)

|                  | PARAM    | ETER            | ETER LIMITS |        |     |     | LIMITS | 3   |      |  |

|------------------|----------|-----------------|-------------|--------|-----|-----|--------|-----|------|--|

| SYMBOL           | То       | To From         |             | AL2852 | -35 | PI  | AL2852 | -50 | UNIT |  |

|                  | (Output) | Output) (Input) | MIN         | TYP    | MAX | MIN | TYP    | MAX |      |  |

| <b>t</b> PHL     | Υ        | X               | 10          | 15     | 20  | 12  | 18     | 25  | ns   |  |

| t <sub>PLH</sub> | Y        | X               | 10          | 15     | 20  | 12  | 18     | 25  | ns   |  |

### internal NAND of Clock Array (NAND)

|                    | PARAM    |         | LIMITS |        |     |     |      |     |    |

|--------------------|----------|---------|--------|--------|-----|-----|------|-----|----|

| SYMBOL To (Output) | То       | To From |        | AL2852 | -35 | PA  | UNIT |     |    |

|                    | (Output) | (Input) | MIN    | TYP    | MAX | MIN | TYP  | MAX |    |

| <b>t</b> PHL       | Υ        | ×       | 5      | 7      | 10  | 7   | 10   | 15  | ns |

| <b>t</b> PLH       | Y        | x       | 5      | 7      | 10  | 7   | 10   | 15  | ns |

### MACRO CELL AC SPECIFICATIONS (Continued)

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V (SNAP Resource Summary Designations in Parentheses)

|                                                              | PARAI    | METER    |     |        |     |     |       |     |      |

|--------------------------------------------------------------|----------|----------|-----|--------|-----|-----|-------|-----|------|

| SYMBOL                                                       | То       | From     | PI  | AL2852 | -35 | P1  | L2852 | -50 | UNIT |

|                                                              | (Output) | (Input)  | MIN | TYP    | MAX | MIN | TYP   | MAX |      |

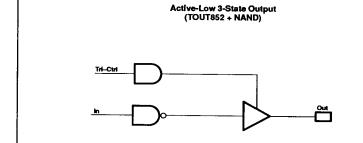

| t <sub>PHL</sub>                                             | Out      | ln       | 12  | 18     | 25  | 17  | 25    | 35  | ns   |

| <b>t</b> PLH                                                 | Out      | ln In    | 12  | 18     | 25  | 17  | 25    | 35  | ns   |

| t <sub>OE</sub> <sup>4</sup><br>t <sub>OD</sub> <sup>4</sup> | Out      | Tri-Ctrl | 5   | 7      | 10  | 7   | 10    | 15  | ns   |

| top⁴                                                         | Out      | Tri-Ctrl | 5   | 7      | 10  | 7   | 10    | 15  | ns   |

Bidirectional Pins: 58-60, 62-66.

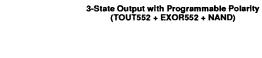

## I/O Output Buffer with 3-State Control, DFF Bypassed (TOUT552 + NAND)

|                                      | PARAM   | PARAMETER |                |     | LIMITS |     |     |     |      |  |  |

|--------------------------------------|---------|-----------|----------------|-----|--------|-----|-----|-----|------|--|--|

| SYMBOL To (Output)                   | То      | From      | PML2852-35 PML |     |        |     |     | -50 | UNIT |  |  |

|                                      | (input) | MIN       | TYP            | MAX | MIN    | TYP | MAX |     |      |  |  |

| t <sub>PHL</sub>                     | Out     | ln        | 12             | 18  | 25     | 17  | 25  | 35  | ns   |  |  |

| t <sub>PLH</sub>                     | Out     | In        | 12             | 18  | 25     | 17  | 25  | 35  | ns   |  |  |

| toE4                                 | Out     | Tri-Ctrl  | 5              | 7   | 10     | 7   | 10  | 15  | ns   |  |  |

| to∈ <sup>4</sup><br>top <sup>4</sup> | Out     | Tri-Ctrl  | 5              | 7   | 10     | 7   | 10  | 15  | ns   |  |  |

Notes on page 501.

October 22, 1993

496

PML2852

### MACRO CELL AC SPECIFICATIONS (Continued)

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V (SNAP Resource Summary Designations in Parentheses)

| SYMBOL To (Output) | PARAM      | IETER   |     | LIMITS |     |     |        |     |      |  |

|--------------------|------------|---------|-----|--------|-----|-----|--------|-----|------|--|

|                    | DL To From |         | PI  | IL2852 | -35 | Pi  | AL2852 | -50 | UNIT |  |

|                    | (Output)   | (Input) | MIN | TYP    | MAX | MIN | TYP    | MAX |      |  |

| t <sub>PHL</sub>   | Out        | In      | 12  | 18     | 25  | 17  | 25     | 35  | ns   |  |

| <b>‡</b> Р∟Н       | Out        | In      | 12  | 18     | 25  | 17  | 25     | 35  | ns   |  |

Output Pins: 8-11, 50-57, 71-74.

PML2852

## MACRO CELL AC SPECIFICATIONS (Continued) (SNAP Resource Summary Designations in Parentheses) D FLIP-FLOP

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V

|                       |                       |     | LIMITS     |     |     |        |     |      |  |

|-----------------------|-----------------------|-----|------------|-----|-----|--------|-----|------|--|

| SYMBOL PARAMETER      | PARAMETER             | PI  | PML2852-35 |     |     | AL2852 | -50 | UNIT |  |

|                       |                       | MIN | TYP        | MAX | MIN | TYP    | MAX |      |  |

| fCKE                  | Flip-flop toggle rate |     |            | 50  |     |        | 35  | MHz  |  |

| tw cke High           | Clock HIGH            | 10  |            |     | 14  |        |     | ns   |  |

| tw cke Low            | Clock LOW             | 10  |            |     | 14  |        |     | ns   |  |

| t <sub>SETUP</sub> /D | /D setup time to CKE  | 15  |            |     | 20  |        |     | ns   |  |

| t <sub>HOLD</sub> /D  | /D hold time to CKE   | 4   |            |     | 6   |        |     | ns   |  |

|                  | PARAMETER   |          |            |     |            |     |     |      |    |

|------------------|-------------|----------|------------|-----|------------|-----|-----|------|----|

| SYMBOL           | SYMBOL From |          | PML2852-35 |     | PML2852-50 |     |     | UNIT |    |

|                  | (Input)     | (Output) | MIN        | TYP | MAX        | MIN | TYP | MAX  |    |

| t <sub>PLH</sub> | CKE ↑       | Q        | 10         | 15  | 20         | 14  | 20  | 25   | ns |

| t <sub>PHL</sub> | CKE ↑       | Q        | 10         | 15  | 20         | 14  | 20  | 25   | ns |

PML2852

## MACRO CELL AC SPECIFICATIONS (Continued) (SNAP Resource Summary Designations in Parentheses) D FLIP-FLOP (Continued)

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V

NOTE: Q<sub>0</sub>, Q̄<sub>0</sub> represent previous stable condition of Q, Q̄.

|                               |            | LIMITS |     |     |     |      |     |  |

|-------------------------------|------------|--------|-----|-----|-----|------|-----|--|

| SYMBOL                        | PML2852-35 |        |     | PN  | -50 | UNIT |     |  |

|                               | MIN        | TYP    | MAX | MIN | TYP | MAX  |     |  |

| fcка, скв, скс                |            |        | 50  |     |     | 35   | MHz |  |

| tw cka, ckb, ckc High         | 10         |        |     | 14  |     |      | ns  |  |

| tw cka, ckb, ckc Low          | 10         |        |     | 14  |     |      | ns  |  |

| t <sub>SETUP</sub> I/DA, I/DB | 5          |        |     | 7   |     |      | ns  |  |

| t <sub>HOLD</sub> I/DA, I/DB  | 5          |        |     | 7   |     |      | ns  |  |

| fcke                          |            |        | 50  |     |     | 35   | MHz |  |

| tw cke High                   | 10         |        |     | 14  |     |      | ns  |  |

| tw cke Low                    | 10         |        |     | 14  |     |      | ns  |  |

| t <sub>SETUP</sub> /D         | 15         |        |     | 20  |     |      | ns  |  |

| t <sub>HOLD</sub> /D          | 4          |        |     | 6   |     |      | ns  |  |

| PARAME                               |                                | TER                                |            |          | LIM      | ITS        |          |          |          |

|--------------------------------------|--------------------------------|------------------------------------|------------|----------|----------|------------|----------|----------|----------|

| SYMBOL                               | From                           | То                                 | PML2852-35 |          |          | PML2852-50 |          |          | UNIT     |

|                                      | (Input)                        | (Output)                           | MIN        | TYP      | MAX      | MIN        | TYP      | MAX      |          |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | CKA, CKB/CKC↑<br>CKA, CKB/CKC↑ | a, <del>a</del><br>a, <del>a</del> | 5<br>5     | 7        | 10<br>10 | 7<br>7     | 10<br>10 | 15<br>15 | ns<br>ns |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | CKE↑<br>CKE↑                   | Out<br>Out                         | 12<br>12   | 18<br>18 | 25<br>25 | 17<br>17   | 25<br>25 | 35<br>35 | ns<br>ns |

## MACRO CELL AC SPECIFICATIONS (Continued) (SNAP Resource Summary Designations in Parentheses) JK FLIP-FLOPS

Min: 0°C, 5.25V; Typ: 25°C, 5.0V; Max: 75°C, 4.75V

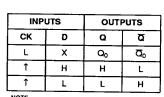

|    | (JKPR552) |     |   |                |      |  |  |  |

|----|-----------|-----|---|----------------|------|--|--|--|

|    | INP       | JTS |   | OUT            | PUTS |  |  |  |

| PR | СК        | J   | K | a              | ā    |  |  |  |

| L  | Х         | Х   | Х | Н              | L    |  |  |  |

| н  | 1         | L   | L | Qo             | ಧ₀   |  |  |  |

| н  | 1         | н   | L | н              | L    |  |  |  |

| н  | 1         | L   | н | L              | н    |  |  |  |

| н  | î         | н   | н | TOG            | GLE  |  |  |  |

| н  | L         | ×   | × | Q <sub>0</sub> | ಠ₀   |  |  |  |

|    | (JKCL552) |      |      |                |    |  |  |

|----|-----------|------|------|----------------|----|--|--|

|    | INP       | OUTI | PUTS |                |    |  |  |

| CL | СК        | J    | К    | Q              | a  |  |  |

| L  | х         | х    | Х    | L              | н  |  |  |

| н  | 1         | L    | L    | Q <sub>0</sub> | ಧ₀ |  |  |

| н  | 1         | н    | L    | н              | L  |  |  |

| н  | 1         | L    | н    | L              | н  |  |  |

| н  | 1         | н    | н    | TOGGLE         |    |  |  |

| Н  | L         | ×    | ×    | Q <sub>0</sub> | ರ₀ |  |  |

|                           |                               | LIMITS     |     |     |            |     |     |      |

|---------------------------|-------------------------------|------------|-----|-----|------------|-----|-----|------|

| SYMBOL                    | PARAMETER                     | PML2852-35 |     |     | PML2852-50 |     |     | UNIT |

|                           |                               | MIN        | TYP | MAX | MIN        | TYP | MAX |      |

| f <sub>CK1</sub>          | CK1 toggle frequency          |            |     | 50  |            |     | 35  | MHz  |

| fcк2                      | CK2 toggle frequency          |            |     | 50  |            |     | 35  | MHz  |

| tw ck1 High               | CK1 clock HIGH                | 10         |     |     | 14         |     |     | ns   |

| tw ck1 Low                | CK1 clock LOW                 | 10         |     |     | 14         |     |     | ns   |

| tw CK2 High               | CK2 clock HIGH                | 10         |     |     | 14         |     |     | ns   |

| tw CK2 Low                | CK2 clock LOW                 | 10         |     |     | 14         |     |     | ns   |

| t <sub>SETUP</sub> /J, /K | /J, /K setup time to CK1, CK2 | 27         |     |     | 35         |     |     | ns   |

| t <sub>HOLD</sub> /J, /K  | /J, /K hold time to CK1, CK2  | 0          |     |     | 0          |     |     | ns   |

| tw PR Low                 | Preset Low period             | 10         |     |     | 14         |     |     | ns   |

| tw CL Low                 | Clear Low period              | 10         |     |     | 14         |     |     | ns   |

|                  | PARA    | PARAMETER       |            | LIMITS |     |            |     |     |      |  |

|------------------|---------|-----------------|------------|--------|-----|------------|-----|-----|------|--|

| SYMBOL           | From    | То              | PML2852-35 |        |     | PML2852-50 |     |     | UNIT |  |

|                  | (Input) | (Output)        | MIN        | TYP    | MAX | MIN        | TYP | MAX |      |  |

| t <sub>PLH</sub> | CK1,2   | Q, <b>ā</b>     | 2          | 3.5    | 5   | 3          | 5   | 7   | ns   |  |

| t <sub>PHL</sub> | CK1,2   | Q, 🖸            | 2          | 3.5    | 5   | 3          | 5   | 7   | ns   |  |

| t <sub>PLH</sub> | PR      | Q, <b>Q</b>     | 12         | 18     | 25  | 17         | 24  | 30  | ns   |  |

| t <sub>PHL</sub> | PR      | ۵٫۵             | 12         | 18     | 25  | 17         | 24  | 30  | ns   |  |

| t <sub>PLH</sub> | CL      | Q, <del>Q</del> | 12         | 18     | 25  | 17         | 24  | 30  | ns   |  |

| t <sub>PHL</sub> | CL      | a, <del>a</del> | 12         | 18     | 25  | 17         | 24  | 30  | ns   |  |

PML2852

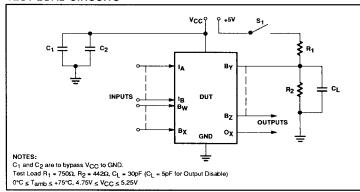

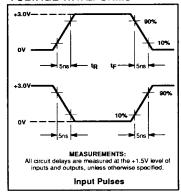

AC ELECTRICAL CHARACTERISTICS 0°C  $\leq$  T<sub>amb</sub>  $\leq$  +75°C, 4.75V  $\leq$  V<sub>CC</sub>  $\leq$  5.25V, V<sub>PP</sub> = V<sub>CC</sub>, R<sub>1</sub> = 750 $\Omega$ , R<sub>2</sub> = 442 $\Omega$ , C<sub>L</sub> = 5pF for Output Disable) (See Test Load Circuit Diagram)

|                   |                                                                                                         |            | LIM | IITS       |          |      |  |

|-------------------|---------------------------------------------------------------------------------------------------------|------------|-----|------------|----------|------|--|

| SYMBOL            | PARAMETER                                                                                               | PML2852-35 |     | PML2852-50 |          | UNIT |  |

|                   |                                                                                                         | MIN        | MAX | MIN        | MAX      |      |  |

| Scan mod          | e operation <sup>1</sup>                                                                                |            |     |            |          |      |  |

| tscms             | Scan Mode (SCM) Setup time                                                                              | 15         |     | 15         |          | ns   |  |

| <sup>t</sup> scmH | Scan Mode (SCM) Hold time                                                                               | 25         |     | 30         |          | ns   |  |

| t <sub>IS</sub>   | Data Input (SCI) Setup time                                                                             | 5          |     | 5          |          | ns   |  |

| t <sub>IH</sub>   | Data Input (SCI) Hold time                                                                              | 5          |     | 5          |          | ns   |  |

| ‡ско              | Clock to Output (I/O) delay                                                                             |            | 30  |            | 40       | ns   |  |

| t <sub>СКН</sub>  | Clock High                                                                                              | 10         |     | 15         |          | ns   |  |

| tckl              | Clock Low                                                                                               | 10         |     | 15         |          | ns   |  |

| Power do          | wn, power up <sup>2</sup>                                                                               |            | ·   |            | II       |      |  |

| t <sub>1</sub>    | Input (I, bypassed I/DA, I/DB, I/O, B) setup time before power down                                     | 40         | -   | 50         |          | ns   |  |

| t <sub>2</sub>    | Input hold time                                                                                         | 30         |     | 35         |          | ns   |  |

| t <sub>3</sub>    | Power Up recovery time                                                                                  |            | 60  |            | 70       | ns   |  |

| 4                 | Output hold time                                                                                        | 0          |     | 0          |          | ns   |  |

| t <sub>5</sub>    | Input setup time before Power Up                                                                        | 20         |     | 25         |          | ns   |  |

| t <sub>OE</sub>   | SCI to Output Enable time <sup>3</sup>                                                                  |            | 40  |            | 50       | ns   |  |

| top               | SCI to Output Disable time <sup>3</sup>                                                                 |            | 40  |            | 50       | ns   |  |

| t <sub>6</sub>    | Power Down setup time                                                                                   | 10         |     | 15         |          | ns   |  |

| t <sub>7</sub>    | Power Up to Output valid                                                                                |            | 70  |            | 80       | ns   |  |

| Power-on          | reset                                                                                                   |            |     |            | <u> </u> |      |  |

| t <sub>PPR1</sub> | Power-on reset output register (Q = 0) to output (I/O) delay                                            |            | 10  |            | 15       | ns   |  |

| t₽PR2             | Power-on reset input register (Q = 0), buried JK Flip-Flop (Q = 0) to output (B, bypassed $I/O$ ) delay |            | 40  |            | 50       | ns   |  |

<sup>1.</sup> SCM recovery time is 50ns after SCM operation. 50ns after SCM operation, normal operations can be resumed.

<sup>2.</sup> Timings are measured without foldbacks.

Transition is measured at steady state High level (-500mV) or steady state Low level (+500mV) on the output from 1.5V level on the input with specified test load (R<sub>1</sub> = 750Ω, R<sub>2</sub> = 442Ω, C<sub>L</sub> = 5pF). This parameter is sampled and not 100% tested.

For 3-State output; output enable times are tested with C<sub>L</sub> = 30pF to the 1.5V level, and S<sub>1</sub> is open for high-impedance to High tests and

closed for high-impedance to Low tests. Output disable times are tested with  $C_L = 5pF$ . High-to-High impedance tests are made to an output voltage of  $V_T = (V_{OH} - 0.5V)$  with  $S_1$  open, and Low-to-High impedance tests are made to the  $V_T = (V_{OL} + 0.5V)$  level with  $S_1$  closed.

PML2852

### **TIMING DIAGRAMS**

PML2852

### **SNAP RESOURCE SUMMARY DESIGNATIONS**

PML2852

# ERASURE CHARACTERISTICS (For Quartz Window Packages Only)

The erasure characteristics of the PML2852 device is such that erasure begins to occur upon exposure to light with wavelengths shorter than approximately 4000 Angstroms (Å). It should be noted that sunlight and certain types of fluorescent lamps have wavelengths in the 3000 – 4000Å range. Data shows that constant exposure to room level fluorescent lighting could erase a typical PML2852 in approximately three years, while it would take approximately one week to

cause erasure when exposed to direct sunlight. If the PML2852 is to be exposed to these types of lighting conditions for extended periods of time, opaque labels should be placed over the window to prevent unintentional erasure.

The recommended erasure procedure for the PML2852 is exposure to shortwave ultraviolet light which has a wavelength of 2537 Angstroms (Å). The integrated dose (i.e., UV intensity × exposure time) for erasure should be a minimum of 15Wsec/cm². The erasure time with this dosage is approximately 30 to

35 minutes using an ultraviolet lamp with a 12,000μW/cm² power rating. The device should be placed within one inch of the lamp ubes during erasure. The maximum integrated dose a CMOS EPLD can be exposed to without damage is 7258Wsec/cm² (1 week @ 12,000μW/cm²). Exposure of these CMOS EPLDs to high intensity UV light for longer periods may cause permanent damage.

The maximum number of guaranteed erase/write cycles is 50. Data retention exceeds 20 years.

### PROGRAMMING

Refer to the following charts for qualified manufacturers of programmers and software tools:

| PROGRAMMER MANUFACTURER                                                         | PROGRAMMER MODEL                     | FAMILY/PINOUT CODES    |

|---------------------------------------------------------------------------------|--------------------------------------|------------------------|

| DATA I/O CORPORATION<br>10525 WILLOWS ROAD, N.E.                                | UNISITE 40/48 Ver. 3.5               | 15918C* (with adaptor) |

| P.O. BOX 97046<br>REDMOND, WASHINGTON 98073~9746                                | PINSITE Ver. 3.5                     | 15918D                 |

| (800)247–5700                                                                   |                                      |                        |

| STREBOR DATA COMMUNICATIONS<br>1008 N. NOB HILL<br>AMERICAN FORK, UT 84003      | PLP-S1A Programmer<br>MP68CC adapter |                        |

| BASIC COMPUTER SYSTEMS AG<br>WOLFGANG-PAULI-GASSE<br>A-1140 WIEN-AUHOF, AUSTRIA | UP2000<br>Rev. 2.28                  |                        |

| SMS – W. STEUDEL<br>IM MORGENTAL 13<br>D-8994 HERGATZ, GERMANY                  | SPRINT PLUS/EXPERT<br>Rev. TBD       |                        |

| SYSTEM GENERAL<br>244 SOUTH PARK VICTORIA DRIVE<br>MILPITAS, CALIFORNIA 95035   | TURPRO-1<br>Rev. 1.42                |                        |

Needs a 40-pin DIP to 84-pin PLCC adaptor that is available from Emulation Technology. Part Number: AS-84-40-01P-6YAM

> EMULATION TECHNOLOGY, INC. 2368B Walsh Avenue, Building D Santa Clara, California 95051 Telephone No. (408) 982–0660 Fax. No. (408) 982–0664

| SOFTWARE MANUFACTURER                                                                                 | DEVELOPMENT SYSTEM |  |  |  |

|-------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| PHILIPS SEMICONDUCTORS<br>811 EAST ARQUES AVENUE<br>P.O. BOX 3409<br>SUNNYVALE, CALIFORNIA 94088–3409 | SNAP SOFTWARE      |  |  |  |

| (408)991–2000                                                                                         |                    |  |  |  |