4

# 4K × 4 Bit Static Random Access Memory

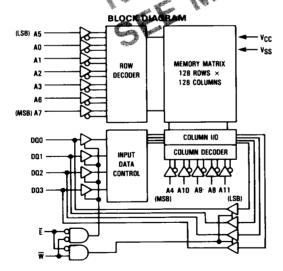

The MCM6168 is a 16,384-bit static random access memory organized as 4096 words of 4 bits, fabricated using Motorola's second-generation high-performance silicon-gate CMOS (HCMOS III) technology. Static design eliminates the need for external clocks or timing strobes, while CMOS circuitry reduces power consumption and provides greater reliability. Fast access time makes this device suitable for cache and other high speed applications.

The chip enable (Ē) pin is not a clock. In less than a cycle time after Ē goes high, the part enters a low-power standby mode, remaining in that state until Ē goes low again. This feature provides reduced system power requirements without degrading access time performance.

The MCM6168 is available in a 300 mil, 20 lead plastic dual-in-line package with the standard JEDEC pinout.

- Single 5 V Supply, ± 10%

- 4K × 4 Bit Organization

- Fully Static—No Clock or Timing Strobes Necessary

- Three State Output

- Fast Access Time (Maximum):

MCM6168-45 45 ns 45 ns MCM6168-70 60 s 70 s

Low Power Operation: 10 ma Max (Active)

Max (Standard TL Levels)

2 mA Max (Sandby CMOS Lave

● Fully TTL Compatible

# MCM6168

| A4 [ 1 ◆             | 20 🛚 V <sub>CC</sub> |

|----------------------|----------------------|

| A5 🛭 2               | 19 DA3               |

| A6 🛭 3               | 18 🕽 A2              |

| A7 🛭 4               | 17 🕽 A1              |

| A8 🗗 5               | 16 🕽 AO              |

| A9 🖸 6               | 15 000               |

| A10 <b>₫</b> 7       | 14 🕽 001             |

| A11 🛭 8              | 13 002               |

| ĒQ 9                 | 12 003               |

| V <sub>SS</sub> [ 10 | 11 🕽 👿               |

| PIN NAMES   |                   |  |  |  |  |  |  |  |  |

|-------------|-------------------|--|--|--|--|--|--|--|--|

| A0-A11      | Address Input     |  |  |  |  |  |  |  |  |

|             | Write Enable      |  |  |  |  |  |  |  |  |

| Ē           | Chip Enable       |  |  |  |  |  |  |  |  |

|             | Data Input/Output |  |  |  |  |  |  |  |  |

| Vcc · · · · | +5 V Power Supply |  |  |  |  |  |  |  |  |

| VSS         | Ground            |  |  |  |  |  |  |  |  |

#### TRUTH TABLE

| Ē | w | Mode         | V <sub>CC</sub> Current | I/O Pin |

|---|---|--------------|-------------------------|---------|

| Н | × | Not Selected | ISB1, ISB2              | High-Z  |

| L | н | Read         | lcc lcc                 | Dout    |

| L | L | Write        | ¹cc                     | Din     |

ABSOLUTE MAXIMUM RATINGS (See Note)

| Rating                                            | Symbol                             | Value                        | Unit |

|---------------------------------------------------|------------------------------------|------------------------------|------|

| Power Supply Voltage                              | Vcc                                | -0.5 to +7.0                 | V    |

| Voltage Relative to VSS for Any<br>Pin Except VCC | V <sub>in</sub> , V <sub>out</sub> | -0.5 to V <sub>CC</sub> +0.5 | ٧    |

| Output Current (per I/O)                          | lout                               | ±20                          | mA   |

| Power Dissipation (T <sub>A</sub> = 25°C)         | PD                                 | 1.0                          | w    |

| Temperature Under Bias                            | T <sub>bias</sub>                  | - 10 to +85                  | °C   |

| Operating Temperature                             | TA                                 | 0 to +70                     | °C   |

| Storage Temperature                               | T <sub>stg</sub>                   | - 55 to + 125                | °¢   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

# DC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>CC</sub> =  $5.0 \text{ V} \pm 10\%$ , T<sub>A</sub> = 0 to 70°C, Unless Otherwise Noted)

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                                | Symbol          | Min  | Тур | Max                  | Unit | Notes |

|------------------------------------------|-----------------|------|-----|----------------------|------|-------|

| Supply Voltage (Operating Voltage Range) | Vcc             | 4.5  | 5.0 | 5.5                  | V    |       |

| Input High Voltage                       | V <sub>IH</sub> | 2.0  | -   | V <sub>CC</sub> +0.3 | ٧    | 1     |

| Input Low Voltage                        | V <sub>IL</sub> | -0.3 | _   | 0.8                  | ٧    | 1, 2  |

# DC CHARACTERISTICS

| Parameter                                                                                                 | Symbol           | Min | Max  | Unit | Notes |

|-----------------------------------------------------------------------------------------------------------|------------------|-----|------|------|-------|

| Input Leakage Current (All Inputs, V <sub>in</sub> = 0 to V <sub>CC</sub> )                               | likg(i)          | _   | ±1.0 | μΑ   |       |

| Output Leakage Current ( $\overline{E} = V_{IH}$ or $\overline{W} = V_{IL}$ , $V_{out} = 0$ to $V_{CC}$ ) | likg(O)          | 1   | ±2.0 | μΑ   | 3     |

| Power Supply Current (E=V <sub>IL</sub> , I <sub>out</sub> =0 mA)                                         | -cc              | -   | 80   | mA   | 3     |

| TTL Standby Current (E=V <sub>jH</sub> )                                                                  | I <sub>SB1</sub> | -   | 20   | mA   |       |

| CMOS Standby Current (E≥V <sub>CC</sub> - 0.2 V, V <sub>in</sub> ≤0.2 V or ≥V <sub>CC</sub> - 0.2 V)      | ISB2             | _   | 2    | mA   |       |

| Output Low Voltage (IOL = 8.0 mA)                                                                         | VOL              | -   | 0.4  | V    |       |

| Output High Voltage (IOH = -4.0 mA)                                                                       | ∨он              | 2.4 | _    | V    |       |

#### CAPACITANCE (f = 1.0 MHz, TA = 25°C, Periodically Sampled Rather Than 100% Tested)

| Characteristic                                              | Symbol           | Тур    | Max    | Unit |

|-------------------------------------------------------------|------------------|--------|--------|------|

| Input Capacitance All Inputs Except $\overline{\mathbb{E}}$ | C <sub>in</sub>  | 3<br>5 | 5<br>7 | рF   |

| I/O Capacitance                                             | C <sub>I/O</sub> | 5      | 7      | pF   |

#### NOTES:

- 1. Address rise and fall times while the chip is selected are 50 ns maximum.

- 2.  $V_{IL}(min) = -0.3 \text{ V dc}$ ;  $V_{IL}(min) = -3.0 \text{ V ac (pulse width } \leq 20 \text{ ns)}$ .

- 3. Input levels less than -0.3 V or greater than  $V_{CC} + 0.3$  V will cause I/O and power supply currents to exceed maximum rating.

# AC OPERATING CONDITIONS AND CHARACTERISTICS

(V<sub>CC</sub> = 5 V  $\pm$  10%, T<sub>A</sub> = 0 to +70°C, Unless Otherwise Noted)

Output Timing Measurement Reference Level . . . . . 0.8 and 2.0 V Output Load . . . . . . . . . Figure 1A Unless Otherwise Noted

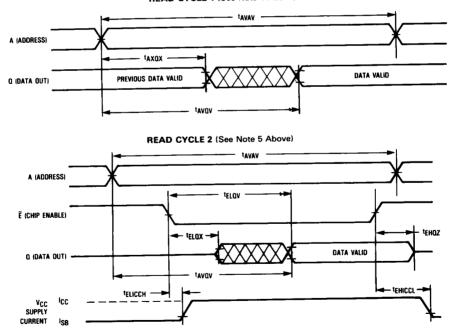

#### DEAD CVCI E (See Note 1)

|                                 | Syn      | Symbol    |     | MCM6168-45 |     | MCM6168-55 |     | MCM6168-70 |      | Notes  |

|---------------------------------|----------|-----------|-----|------------|-----|------------|-----|------------|------|--------|

| Parameter                       | Standard | Alternate | Min | Max        | Min | Max        | Min | Max        | Unit | 140100 |

| Read Cycle Time                 | tavav    | tRC       | 45  |            | 55  |            | 70  | _          | ns   |        |

| Address Access Time             | tAVQV    | tAA       | _   | 45         | _   | 50         |     | 60         | ns   |        |

| Ē Access Time                   | tELQV    | tACS      | _   | 45         |     | 55         |     | 70         | ns   |        |

| E Low to Output Active          | †ELQX    | tLZ       | 10  | _          | 10  | _          | 10  |            | ns   | 2, 3   |

| E High to Output High-Z         | tEHOZ    | tHZ       | 0   | 15         | 0   | 20         | 0   | 25         | ns   | 2, 3   |

| Output Hold from Address Change | tAXQX    | tон       | 5   |            | 5   | _          | 5   |            | ns   |        |

| Power Up Time                   | tELICCH  | tPU       | 0   | T -        | 0   | I -        | 0   |            | ns   |        |

| Power Down Time                 | TEHICCL  | tPD       | _   | 45         | _   | 55         |     | 70         | ns   |        |

#### NOTES:

- 1. W is high for read cycle.

- 2. Transition is measured ±500 mV from steady-state voltage with load of Figure 1B.

- 3. This parameter is sampled and not 100% tested.

- 4. Device is continuously selected ( $\overline{E} = V_{|L}$ ).

- 5. Addresses valid prior to or coincident with  $\overline{\mathbf{E}}$  going low.

# READ CYCLE 1 (See Note 4 Above)

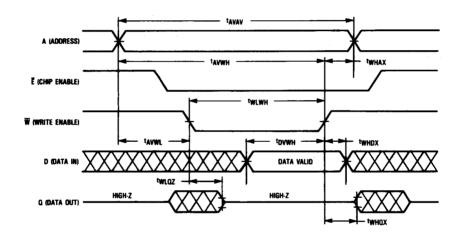

WRITE CYCLE 1 (W Controlled; See Note 1)

| Parameter                     | Syn      | Symbol    |     | MCM6168-45 |     | MCM6168-55 |     | MCM6168-70 |      |       |

|-------------------------------|----------|-----------|-----|------------|-----|------------|-----|------------|------|-------|

|                               | Standard | Alternate | Min | Max        | Min | Max        | Min | Max        | Unit | Notes |

| Write Cycle Time              | †AVAV    | twc       | 40  | I –        | 50  |            | 60  | _          | ns   |       |

| Address Setup Time            | †AVWL    | †AS       | 0   | _          | 0   | <u> </u>   | 0   | _          | ns   |       |

| Address Valid to End of Write | †AVWH    | tAW       | 35  | -          | 45  | -          | 55  | _          | ns   |       |

| Write Pulse Width             | twwh     | twp       | 35  | _          | 45  | _          | 55  | _          | ns   |       |

| Data Valid to End of Write    | tDVWH    | tDW       | 15  | 1-         | 20  | _          | 25  |            | ns   |       |

| Data Hold Time                | ¹WHDX    | tDH       | 3   | _          | 3   | _          | 3   | _          | ns   |       |

| Write Low to Output High-Z    | twLoz    | twz       | _   | 20         | _   | 25         | _   | 30         | ns   | 2, 3  |

| Write High to Output Active   | tw+ox    | tow       | 5   | _          | 5   | _          | 5   | <b>—</b>   | ns   | 2, 3  |

| Write Recovery Time           | twhax    | †WR       | 5   | _          | 5   | _          | 5   |            | ns   |       |

#### NOTES:

- 1. A write occurs during the overlap of E low and W low.

- 2. Transition is measured ± 500 mV from steady-state voltage with load in Figure 18.

- 3. Parameter is sampled and not 100% tested.

# AC TEST LOADS 480 480 480 480 5 pF (INCLUDING SCOPE AND JIG) Figure 1A Figure 1B

#### TIMING LIMITS

The table of timing values shows either a minimum or a maximum limit for each parameter. Input requirements are specified from the external system point of view. Thus, address setup time is shown as a minimum since the system must supply at least that much time (even though most devices do not require it). On the other hand, responses from the memory are specified from the device point of view. Thus, the access time is shown as a maximum since the device never provides data later than that time.

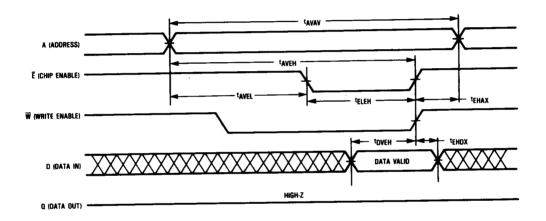

# WRITE CYCLE 2 (E Controlled; See Note 1)

| MHILE CICLE & (E CONTIONED, 200 14 | Ote 17            |           |     |            |     |            |     |            |      |            |

|------------------------------------|-------------------|-----------|-----|------------|-----|------------|-----|------------|------|------------|

| Parameter                          | Syn               | Symbol    |     | MCM6168-45 |     | MCM6168-55 |     | MCM6168-70 |      | Notes      |

|                                    | Standard          | Alternate | Min | Max        | Min | Max        | Min | Max        | Unit | .,,,,,,    |

| Write Cycle Time                   | tavav             | twc       | 40  |            | 50  |            | 60  |            | ns   | L_         |

| Address Setup Time                 | tAVEL             | †AS       | 0   |            | 0   |            | 0   | <u> </u>   | ns   |            |

| Address Valid to End of Write      | †AVEH             | tAW       | 35  |            | 45  |            | 55  |            | ns   |            |

| Write Pulse Width                  | <sup>†</sup> ELEH | tcw       | 35  |            | 45  |            | 55  |            | ns   | 2, 3       |

| Data Valid to End of Write         | tDVEH             | tDW       | 15  |            | 20  |            | 25  |            | ns   |            |

| Data Hold Time                     | tEHDX             | tDH.      | 3   |            | 3   |            | 3   | <u> </u>   | ns   | <b>└</b>   |

| Write Recovery Time                | tEHAX             | twn       | 5   | _          | 5   | l          | 5   | <u> </u>   | ns   | <u> 1 </u> |

#### NOTES:

- NOTES:

1. A write occurs during the overlap of Ē low and ₩ low.

2. If Ē goes low coincident with or after ₩ goes low, the output will remain in a high impedance condition.

3. If Ē goes high coincident with or before ₩ goes high, the output will remain in a high impedance condition.

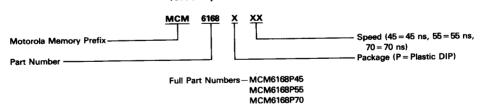

#### ORDERING INFORMATION (Order by Full Part Number)