# ·WYUNDAI

# HY57V16801 Series 2M x 8 bit Synchronous DRAM

**PRELIMINARY**

#### DESCRIPTION

The HY57V16801 is a very high speed 3.3 Volt synchronous dynamic RAM organized 2,097,152x8bits, and fabricated with the Hyundai CMOS process. This dual bank circuit consists of two memories, each 1,048,576 words by 8 bits which share the same chip inputs and outputs but otherwise can be independently operated. The HY57V16801 is compatible with the JEDEC functional description and pinout, offering fully synchronous operation. All address, data and control inputs are latched on the rising edge of the master clock input. The data paths are internally pipelined to achieve very high bandwidth. The maximum operating frequency depends on system considerations including capacitance on outputs; the internal circuits, including data pipeline, can operate at frequencies above 150MHz.

The part is user programmable to allow optimization to system requirements. Programmable options include the length of pipeline(Read latency of 1, 2, or 3), the number of consecutive read or write cycles initiated by a single control command (burst length of 1, 2, 4, 8 or full page), and the burst count sequence(sequential or interleave). A burst of read or write cycles in progress can be terminated by a burst terminate command or can be interrupted and replaced by a new burst read or write command on any cycle. (This pipelined design is not restricted by a "2N" rule.)

The synchronous DRAM also allows both Auto refresh and self refresh. All input and output voltage levels are LVTTL compatible.

#### **FEATURES**

- Fully synchronous; all inputs referenced to positive edge of system clock

- Dual internal banks with single pulsed RAS

- Auto Precharge / Precharge All banks by A10 flag

- Single 3.3V±0.3V power supply

- All device pins are LVTTL compatible

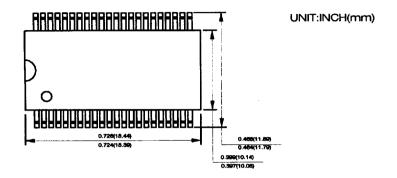

- 400mil 44pin TSOP(II) with 0.8mm of lead pitch (Lead-on-Chip)

- · 4096 refresh cycles every 64ms

- Possible to assert random column address every clock cycle

- Programmable Burst Lengths and Sequences

- 1, 2, 4, 8, full page for Sequential type

- 1, 2, 4, 8 for Interleave type

- Programmable CAS latency; 1, 2, 3 clocks

- Support Clock Suspend / Power Down Mode by CKE

- Data mask function by DQM

- WCBR Mode Register programming

- Burst termination command

- Meets all the other JEDEC specifications

- Self Refresh provides minimum power, full internal refresh control

#### PIN CONNECTION

(Top View)

44 pin TSOP (II)

Normal-TC

VCC 1 0 44 VSS

DQ0 2 3 42 VSSQ

DQ1 4 41 DQ6

VSSQ 3 42 VSSQ

DQ1 4 41 DQ6

VSSQ 6 39 DQ6

VSSQ 7 38 DQ6

VSSQ 9 36 NCC

NCC 10 35 NCC

NCC 10 35 NCC

NCC 11 34 NCC

WE 12 33 DQM

NCC 11 34 NCC

WE 12 33 DQM

CAS 15 30 NC

CAS 15 30 NC

CAS 16 39 CAS

A1 1 16 29 A8

A1 17 28 A8

A1 19 28 A8

A1 19 28 A8

A2 19 26 A6

A3 19 22 25 A5

A3 A4

## PIN DESCRIPTION

| PIN NUMBERS                   | PIN NAME     | PIN TYPE          | DESCRIPTION                                                                                                                                               |

|-------------------------------|--------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32                            | CLK          | INPUT             | System Clock Input ; All other inputs except CKE are registered to the SDRAM on the rising edge of CLK.                                                   |

| 31                            | CKE          | INPUT             | Clock Enable; controls internal clock signal and when deactivated, the SDRAM will be either one of the states among power down, suspend, or self refresh. |

| 16                            | A11          | INPUT             | Bank Select(BS) Address Input; selects either one of dual banks during both RAS and CAS activity.                                                         |

| 17-21<br>24-29                | A0-A10       | INPUT             | Address Inputs; A0-A8; X & Y address, Opcode for mode register set. A9; X address only. A10; X address, Precharge Flag.                                   |

| 15                            | CS           | INPUT             | Chip Select ; functions command mask(NOP)                                                                                                                 |

| 14                            | RAS          | INPUT             | Row Address Strobe ; see Functional Truth Table for details.                                                                                              |

| 13                            | CAS          | INPUT             | Column Address Strobe ; see Functional Truth Table for details.                                                                                           |

| 12                            | WE           | INPUT             | Write Enable; see Functional Truth Table for details.                                                                                                     |

| 33                            | DQM          | INPUT             | Data Input / Output Mask                                                                                                                                  |

| 2, 4, 6, 8,<br>37, 39, 41, 43 | DQ0-DQ7      | INPUT /<br>OUTPUT | Data Input / Output ; includes inputs, outputs, or Hi-Z state.                                                                                            |

| 5, 9, 36, 40,<br>3, 7, 38, 42 | VccQ<br>VssQ | SUPPLY<br>for DQ  | DQ Power Supplies                                                                                                                                         |

| 1, 22                         | Vcc          | SUPPLY            | Power Supplies ; 3.3V ± 0.3V                                                                                                                              |

| 23, 44                        | Vss          | SUPPLY            | Ground                                                                                                                                                    |

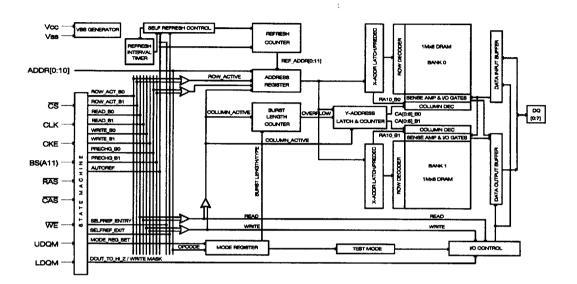

## **FUNCTIONAL BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL               | PARAMETER                          | RATING      | UNIT     |  |  |

|----------------------|------------------------------------|-------------|----------|--|--|

| TA                   | Ambient Temperature                | 0 to 70     | •€       |  |  |

| TSTG                 | Storage Temperature                | -55 to 125  | °C       |  |  |

| VIN, VOUT            | Voltage on Any Pin relative to Vss | -0.5 to 4.6 | ٧        |  |  |

| Vcc                  | Voltage on Vcc relative to Vss     | -1.0 to 4.6 | V        |  |  |

| los                  | Short Circuit Output Current       | 50          | mA       |  |  |

| PD Power Dissipation |                                    | 1           | w        |  |  |

| TSOLDER              | Soldering Temperature • Time       | 260 • 10    | °C • sec |  |  |

Note: Operation at or above Absolute Maximum Ratings can adversely affect device reliability.

## RECOMMENDED DC OPERATING CONDITIONS

(TA=0°C to 70°C)

| SYMBOL    | PARAMETER            | MIN. | TYP. | MAX.     | UNIT        |  |

|-----------|----------------------|------|------|----------|-------------|--|

| Vcc, Vccq | Power Supply Voltage | 3.0  | 3.3  | 3.6      | <b>&gt;</b> |  |

| VIH       | Input High Voltage   | 2.0  | -    | Vcc+ 0.3 | ٧           |  |

| VIL       | Input Low Voltage    | -0.5 | -    | 0.8      | <b>v</b>    |  |

Note:All voltages are referenced to Vss.

## DC CHARACTERISTICS(I)

(Ta=0°C to 70°C, Vcc=3.3V±10%, Vss=0V, unless otherwise noted)

| SYMBOL | PARAMETER                                     | TEST CONDITION                                                                                                                       | MIN. | MAX. | UNIT | NOTE |

|--------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| iu     | Input Leakage Current<br>(Any Input Pins)     | Vss <vin<vcc+1.0 all="" not="" other="" pins="" test="Vss&lt;/td" under=""><td>-10</td><td>10</td><td>μА</td><td></td></vin<vcc+1.0> | -10  | 10   | μА   |      |

| lro    | Output Leakage Current (High Impedance State) | Vss <vout<vcc<br>Both Banks in idle state</vout<vcc<br>                                                                              | -10  | 10   | μА   |      |

| Vol    | Output Low Voltage                            | IOL=2.0mA                                                                                                                            | -    | 0.4  | V    |      |

| Vон    | Output High Voltage                           | IOH= -2.0mA                                                                                                                          | 2.4  | -    | V    |      |

## **CAPACITANCE**

(Ta=25°C, f=1MHz)

| SYMBOL | PARAMETER          | PIN                                | TYP. | MAX. | UNIT |

|--------|--------------------|------------------------------------|------|------|------|

| C11    | Input Capacitance  | A0-A11                             | -    | 4    | pF   |

| C12    | Input Capacitance  | CLK, CKE, CS, RAS, CAS,<br>WE, DQM | -    | 4    | pF   |

| Соит   | Output Capacitance | DQ0-DQ15                           | -    | 5    | pF   |

**4675088 0004894 305**

## DC CHARACTERISTICS(II)

(TA=0°C to 70°C, Vcc=3.3V±10%, Vss=0V, unless otherwise noted.)

| SYMBOL | PARAMETER / CONDITION                                                                                                                                                | 40       | SPEE    | D/POWER | -MAX    | UNIT |         |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|---------|---------|------|---------|

| SIMBOL | PARAMETER / CONDITION                                                                                                                                                | tclk     | -8      | -10 -13 |         | UNII | NOTE    |

| Icc1   | RAS Operating Current per bank<br>No CAS activity,<br>tRC=tRC(min)                                                                                                   | min      | 130     | 120     | 110     | mA   | 1, 2    |

| ICC2PD | Precharge Stand-By Current<br>in Power-Down Mode,<br>CKE <vil(max)< td=""><td>min<br/>∞</td><td>4 2</td><td>3<br/>2</td><td>3 2</td><td>mA</td><td></td></vil(max)<> | min<br>∞ | 4 2     | 3<br>2  | 3 2     | mA   |         |

| Icc2NP | Prechanrge Stand-By Current<br>in Non Power-Down Mode,<br>CKE>ViH(min)                                                                                               | min<br>∞ | 20<br>5 | 15<br>5 | 12<br>5 | mA   | 3       |

| Icc3PD | Active Stand-By Current<br>in Power-Down Mode,<br>CKE <vil(min)< td=""><td>min<br/>∞</td><td>4<br/>3</td><td>4 3</td><td>4 3</td><td>mA</td><td>4</td></vil(min)<>   | min<br>∞ | 4<br>3  | 4 3     | 4 3     | mA   | 4       |

| Icc3NP | Active Stand-By Current<br>in Non Power-Down Mode,<br>CKE>VIH(min)                                                                                                   | min<br>∞ | 22<br>7 | 17<br>7 | 15<br>7 | mA   | 3, 4    |

| Icc4   | Burst Mode Operating Current                                                                                                                                         | min      | 150     | 120     | 100     | mA   | 2, 5, 6 |

| Icc5   | Auto Refresh Operating Current, tRC=tRC(min)                                                                                                                         | min      | 130     | 120     | 110     | mA   | 2       |

| Iccs   | Self Refresh Operating Current, CKE<0.2V                                                                                                                             | -        | 2       | 2       | 2       | mA   |         |

#### Notes:

- 'No CAS activity' means that the operating cycle activates row circuits only while it does not command any read or write cycle, what could be called, CAS activity

- 2. All Icc currents except Iccs depend on cycle rate.

- 3. All input signals are toggled every other clock cycle.

- 4. Assuming that one bank is active.

- These Icc Parameters are dependent on output loading. Specified values are obtained with the outputs open.

- Specified values are obtained with the timing that a burst cycle is completed upto its registered burst length without any interrupt cycle. Interrupted burst cycle may consume more power.

## RECOMMENDED AC OPERATING CONDITIONS

(TA=0°C to 70°C, Vcc=3.3V ±10%, Vss=0V, unless otherwise noted)

| PARAMETER                                           | SYMBOL    | VALUE       |

|-----------------------------------------------------|-----------|-------------|

| AC Input High/Low Level Voltage                     | ViH / ViL | 2.4V / 0.4V |

| Input Timing Measurement Reference Level Voltage    | Vtrip     | 1.4V        |

| Input Rise / Fall Time                              | tr/tf .   | 2ns / 2ns   |

| Output Reference Voltage                            | Voutref   | 1.4V        |

| Output Load Capacitance for Access Time Measurement | CL        | Note1       |

Note1: Output load to measure access times(tovc, toH, etc) varies to clock frequency. A load is equivalent to two TTL gates and one capacitance.

For the specification, the values used are as follows;

CL=10pF, for 100MHz~125MHz of fCLK CL=30pF, for 80MHz~100MHz of fCLK CL=50pF, for below 80MHz of fCLK

## **AC CHARACTERISTICS**

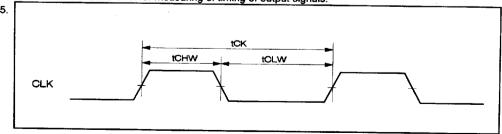

[PART1] Synchronous Parameters referred to Clock 1,2,3,4

|    |        |                                |                    |     | -8   | _    | 10   |      | 13   |      |       |

|----|--------|--------------------------------|--------------------|-----|------|------|------|------|------|------|-------|

| #  | SYMBOL | PARA                           | PARAMETER          |     | MAX. | MIN. | MAX. | MIN. | MAX. | UNIT | NOTE  |

| 1  | tcĸ    | System Cloc                    | k Cycle Time       | 8   | -    | 10   | -    | 13   | -    | ns   | 5     |

| 2  | tchw   | CLK High Le                    | evel Width         | 2   |      | 3    | -    | 4    | _    | ns   | 5     |

| 3  | tclw   | CLK Low Le                     | vel Width          | 3   | -    | 3    | -    | 4    | _    | ns   | 5     |

| ļ  |        | Access                         | CAS Lat.=3         | -   | 6    | _    | 7    | -    | 9    | ns   | 30pF  |

| 4  | tovc   | Time from<br>Clock             | CAS Lat.=2         |     | 9    | -    | 10   | -    | 12   | ns   | 50pF  |

|    |        | Clock                          | CAS Lat.=1         |     | 23   | -    | 25   |      | 30   | ns   | 100pF |

| 5  | taa    | Read command to DQ<br>Access   |                    | -   | 17   | -    | 18   | •    | 25   | ns   | 30pF  |

| 6  | tas    | Address Set-up Time            |                    | 1.5 | -    | 2    |      | 3    | -    | ns   |       |

| 7  | tan    | Address Hold Time              |                    | 1.5 | -    | 1.5  | -    | 1.5  | _    | ns   |       |

| 8  | tcks   | CKE Set-up                     | Time               | 1.5 | -    | 2    | -    | 3    | -    | ns   |       |

| 9  | tckh   | CKE Hold Ti                    | me                 | 1.5 | -    | 1.5  | -    | 1.5  | -    | ns   |       |

| 10 | tcs    | Command S                      | et-up Time         | 1.5 | -    | 2    | _    | 3    | -    | ns   |       |

| 11 | tсн    | Command H                      | old Time           | 1.5 | -    | 1.5  | -    | 1.5  | -    | ns   |       |

| 12 | tos    | Data-in Set-u                  | ıp Time            | 1.5 | -    | 2    | -    | 3    | -    | ns   |       |

| 13 | tDH    | Data-in Hold                   | Time               | 1.5 | -    | 1.5  | -    | 1.5  | - 1  | ns   |       |

| 14 | toн    | Data-out Hole                  | Data-out Hold Time |     | -    | 3    | -    | 4    | -    | ns   |       |

| 15 | toLZ   | Data-out Low-impedance<br>Time |                    | 4   | -    | 5    | -    | 6    | -    | ns   |       |

| 16 | tonz   | Data-out Higl<br>Time          | n-impedance        | 4   | -    | 5    | -    | 6    | -    | ns   | ·     |

#### Notes:

- An initial pause of 200

μs is required after power-up by 'Power On Sequence' (JEDEC Standard.) and Auto Refresh before proper device operation is achieved.

- 2. AC measurements assume tT=1ns.

- 3. (VIH+VIL)/2 is a reference level for measuring of timing of input signals. Also transition time is measured between VIH and VIL.

- 4. Voutref is a reference level for measuring of timing of output signals.

4675088 0004897 014

[PART2] Asynchronous Parameters like conventional DRAMs. 1,2,3,4

|    |        |                                 | -8              |      | -10            | ) _  | -13            | 3    | UNIT  | NOTE  |

|----|--------|---------------------------------|-----------------|------|----------------|------|----------------|------|-------|-------|

| #  | SYMBOL | PARAMETER                       | MIN.            | MAX. | MIN.           | MAX. | MIN.           | MAX. | 01111 | 11012 |

| 1  | tRC    | Nomal/Refresh cycle<br>Time     | 80              | -    | 80             | -    | 100            | -    | ns    |       |

| 2  | tRCD   | RAS-to-CAS delay<br>Time        | 20              | -    | 25             | -    | 30             | -    | ns    |       |

| 3  | tRAS   | Bank Active Time                | 50              | 10K  | 50             | 10K  | 60             | 10K  | ns    |       |

| 4  | trasp  | Bank Active Time<br>(full page) | 40              | 400K | 50             | 400K | 60             | 400K | ns    |       |

| 5  | tRP    | Bank Precharge Time             | 30              | -    | 30             | -    | 40             | -    | ns    |       |

| 6  | trrd   | Bank Active-to-Active<br>Time   | 20              | -    | 20             | -    | 25             | -    | ns    |       |

| 7  | twr    | Write Recovery Time             | 10              | -    | 15             | -    | 20             | -    | ns    |       |

| 8  | tsre   | Self-Refresh Exit               | tRC min<br>+0.5 | -    | tRC min<br>+15 | -    | tRC min<br>+20 |      | ns    |       |

| 9  | tτ     | Transition Time                 | 0.5             | 1.5  | 0.5            | 2    | 0.5            | 2.5  | ns    |       |

| 10 | tref   | Refresh Period                  | -               | 64   | _              | 64   | -              | 64   | ms    |       |

#### Notes:

2. AC measurements assume tr=1ns.

4. Voutref is a reference level for measuring of timing of output signals.

<sup>1.</sup> An initial pause of 200μs is required after power-up by 'Power On Sequence' (JEDEC Standard.) and Auto Refresh before proper device operation achieved.

<sup>3. (</sup>VIH+VIL)/2 is a reference level for measuring of timing of input signals. Also transition time is measured between VIH and VIL.

[PART 3] Latency - Fixed Parameters 1

| # | SYMBOL               | PARAME                                         | -8             | -10  | -13  | UNIT   |        |      |

|---|----------------------|------------------------------------------------|----------------|------|------|--------|--------|------|

|   | J                    | r Alvania                                      | TER            | Lat. | Lat. | Lat.   | UNII   | NOTE |

| 1 | tCKED                | CKE to CLK Suspend or<br>Power Down Mode Entry |                | 1    | 1    | 1      | CLK(s) |      |

| 2 | toomoz               | DQM to Data Output in Hi-Z                     |                | 2    | 2    | 2      | CLK(s) |      |

| 3 | tDQMIM               | DQM to Data Input Mask                         |                | 0    | 0    | 0      | CLK(s) |      |

| 4 | twTL                 | Write command to Da                            | ta Input Valid | 0    | 0    | 0      | CLK(s) | 2    |

| 5 | tPROZ                | Precharge to Data                              | CAS Lat.=1     | 1    | 1    | 1      | CLK(s) |      |

|   | Output in Hi-Z delay | CAS Lat.>1                                     | 2              | 2    | 2    | CLK(s) |        |      |

| 6 | tMRD                 | Mode Register Set to Bank Active               |                | 3    | 2    | 2      | CLK(s) |      |

| 7 | tccp                 | CAS to CAS command delay                       |                | 1    | 1    | 1      | CLK(s) | 3    |

## Notes:

- 1. The latency values in the above table are fixed regardless of clock cycle time.

- 2. "Write Latency" as JEDEC standard says.

- 3. Superset of "2N-rule".

## STATE AND FUNCTIONAL TRUTH TABLE, SELECTED BANK <sup>1</sup>

| Current                      |    |     | -   | CLI | <b>K</b> ↑ |        |       |                                                     |

|------------------------------|----|-----|-----|-----|------------|--------|-------|-----------------------------------------------------|

| State of<br>Selected<br>Bank | ĊS | RAS | CAS | WE  | A11(BS)    | A10    | A9-A0 | Action to Selected Bank<br>(Unless otherwise noted) |

|                              | L  | L   | L   | L   | (          | Opcode |       | Mode Register Access                                |

|                              | L  | Н   | Н   | Н   | x          | х      | x     |                                                     |

| ldle                         | Н  | х   | х   | х   | х          | х      | x     | NOP                                                 |

|                              | L  | L   | Н   | L   | BA         | x      | x     |                                                     |

|                              | L  | L   | Н   | Н   | BA         | RA     | RA    | Activate Row                                        |

|                              | L  | L   | L   | L   | х          | х      | x     | ILLEGAL                                             |

|                              | L  | Н   | Н   | Н   | x          | х      | x     | NOD                                                 |

|                              | Н  | ×   | х   | х   | ×          | х      | х     | NOP                                                 |

| Row                          | L  | L   | Н   | L   | BA         | L      | ×     | Precharge Selected Bank                             |

| Active                       | L  | L   | Н   | L   | ×          | Н      | x     | Precharge Both Banks                                |

|                              | L  | Н   | L   | L   | ВА         | L      | CA    | Begin Write                                         |

|                              | L  | Н   | L   | L   | BA         | Н      | CA    | Begin Write / Auto Precharge                        |

|                              |    | Н   |     | Н   | BA         | L      | CA    | Begin Read                                          |

|                              | L  | Н   | L   | Н   | BA         | Н      | CA    | Begin Read / Auto Precharge                         |

|                              | T  | Н   | Н   | Н   | ×          | х      | ×     | NOP(continue burst to end                           |

|                              | H  | ×   | ×   | ×   | ×          | ×      | ×     | →Row Active)                                        |

|                              | L  | L   | Н   | L   | BA         | L      | х     | Precharge Selected Bank                             |

|                              |    | T_  | Н   | L   | ×          | Н      | x     | Precharge Both Banks                                |

| Read                         | L  | Н   | L   | L   | BA         | L      | CA    | Begin Write 2                                       |

|                              |    | Н   | L   | L   | BA         | Н      | CA    | Begin Write / Auto Precharge 2                      |

|                              | L  | Н   | L   | Н   | BA         | L      | CA    | Begin New Read                                      |

|                              | L  | Н   | L   | Н   | ВА         | Н      | CA    | New Read / Auto Precharge                           |

|                              | L  | Н   | Н   | L   | BA         | х      | х     | Term Burst→Row Active                               |

|                              | L  | Н   | Н   | Н   | ×          | х      | ×     | NOP, continue burst to end                          |

|                              | Н  | ×   | х   | ×   | ×          | ×      | ×     | →Row Active                                         |

|                              | L  | L   | Н   | L   | BA         | L      | ×     | Precharge Selected Bank                             |

|                              | L  | L   | Н   | L   | x          | Н      | ×     | Precharge Both Banks                                |

| Write                        | L  | Н   | L   | L   | BA         | L      | CA    | Begin New Write                                     |

|                              | L  | Н   | L   | L   | ВА         | Н      | CA    | Begin New Write / Auto Precharge                    |

|                              | L  | Н   | L   | Н   | BA         | L      | CA    | Begin New Read                                      |

|                              | L  | н   | L   | Н   | BA         | Н      | CA    | Begin New Read / Auto Precharge                     |

|                              | L  | Н   | Н   | L   | BA         | ×      | ×     | Term Burst→Row Active                               |

|     | 4675088 | 0004900 | 439 | 1SD02-00-MAY95  |

|-----|---------|---------|-----|-----------------|

| 888 |         |         |     | 13002-00-40-130 |

| Current State<br>of Selected<br>Bank |    |     |     | Action to Selected Bank |         |     |       |                                                       |  |

|--------------------------------------|----|-----|-----|-------------------------|---------|-----|-------|-------------------------------------------------------|--|

|                                      | CS | RAS | CAS | WE                      | ALL(BS) | A10 | A9-A0 | (Unless otherwise noted)                              |  |

| Read, Auto<br>Precharging            | L  | Н   | Н   | Н                       | x       | х   | x     | NOP, continue burst to end<br>→Precharge <sup>3</sup> |  |

|                                      | Н  | ×   | x   | х                       | x       | х   | х     |                                                       |  |

| Write, Auto<br>Precharging           | L  | Н   | Н   | Н                       | x       | х   | x     | NOP, continue burst to end<br>→Precharge <sup>3</sup> |  |

|                                      | Н  | ×   | х   | X                       | ×       | х   | х     |                                                       |  |

| Precharging                          | L  | Н   | Н   | Н                       | х       | х   | x     | NOP→Idle after tRP                                    |  |

|                                      | Н  | ×   | х   | x                       | x       | x   | x     |                                                       |  |

| Row Activating                       | L  | н   | Н   | Н                       | х       | х   | ×     | NOP→Row active after tRCD                             |  |

|                                      | Н  | х   | х   | x                       | ×       | x   | ×     |                                                       |  |

| Mode Register<br>Accessing           | L  | Н   | Н   | Н                       | x       | х   | ×     |                                                       |  |

|                                      | Н  | х   | х   | х                       | x       | х   | x     | NOP                                                   |  |

#### Notes:

- 1. Assumes CKE high on the previous and current clock cycles.

- 2. Read burst must terminate one cycle before the start of a write sequence. This can be accomplished in one of two ways. First, if the last bit of the burst is output two cycles before the start of the write sequence, the burst will terminate, the output will tristate, and the internal read pipeline will be flushed during the cycle before the write command is issued. Second, the burst can be terminated by bringing DQMi high and issuing a terminate burst command two cycles before the write command. This will also guarantee that the output will tristate and the read pipeline will be flushed during the cycle before the write command is issued.

- While either bank is executing a Read or Write burst sequence with Auto Precharge selected, no Read or Write commands are allowed to the opposite bank.

## STATE AND FUNCTIONAL TRUTH TABLE, OPERATIONS INVOLVING BOTH BANKS

| Current State              | CKE   |       | CS | RAS  | CAS | WE         | A11    | A10 | A9- | Action                                  |  |

|----------------------------|-------|-------|----|------|-----|------------|--------|-----|-----|-----------------------------------------|--|

|                            | prev. | curr. |    | ICAS | CAS | ***        | (BS)   | A10 | A0  |                                         |  |

|                            | L     | L     | ×  | x    | x   | х          | x      | x   | x   | Maintain Power Down                     |  |

| Power Down                 | L     | Н     | L  | н    | Н   | Н          | x      | x   | х   | Exit Power Down→BBI                     |  |

|                            | L     | H     | Ι  | х    | х   | x          | х      | x   | х   | Exit Power Down→BBI                     |  |

|                            | L     | L     | x  | х    | х   | x          | х      | x   | ×   | Maintain Self Refresh                   |  |

| Self Refresh 1             | L     | Н     | L  | Н    | Н   | Н          | х      | x   | х   | Exit Self Refresh→BBI                   |  |

|                            | L     | Н     | н  | ×    | х   | х          | х      | x   | x   |                                         |  |

|                            | Н     | L     | L  | Н    | Н   | н          | x      | x   | x   | Enter Power Down                        |  |

|                            | Н     | L     | Н  | х    | x   | х          | х      | x   | x   | Enter Power Down                        |  |

| Both Banks                 | Н     | L     | L  | L    | L   | Н          | х      | х   | x   | Enter Self Refresh                      |  |

| Idie(BBI)                  | Н     | Н     | L  | Н    | Н   | Н          | х      | х   | х   | NOP                                     |  |

|                            | Н     | Н     | ×  | х    | х   | x          | х      | x   | ×   | NOP                                     |  |

|                            | Н     | Н     | L  | L    | L   | L          | Opcode |     | •   | Mode Register Access                    |  |

|                            | Н     | Н     | L  | L    | L   | Н          | х      | х   | x   | Auto Refresh                            |  |

| 01160                      | L     | L     | x  | х    | x   | x          | х      | х   | x   | Maintain CLK Suspend                    |  |

| CLK Suspend                | L     | Н     | x  | x    | x   | х          | x      | x   | x   | Exit CLK Suspend                        |  |

| Auto<br>Refreshing         | Н     | Н     | L  | Н    | Н   | Н          | x      | x   | x   | NOP→Both Banks                          |  |

|                            | Н     | Н     | Н  | х    | х   | х          | х      | x   | х   | Idie after tRC                          |  |

| Any state other than above | н     | L     | ×  | ×    | x   | <b>x</b> · | x      | x   | ×   | Suspend Clock, next cycle→Clock Suspend |  |

Notes 1: Exiting Self Refresh occurs by asynchronously bringing CKE from low to high.

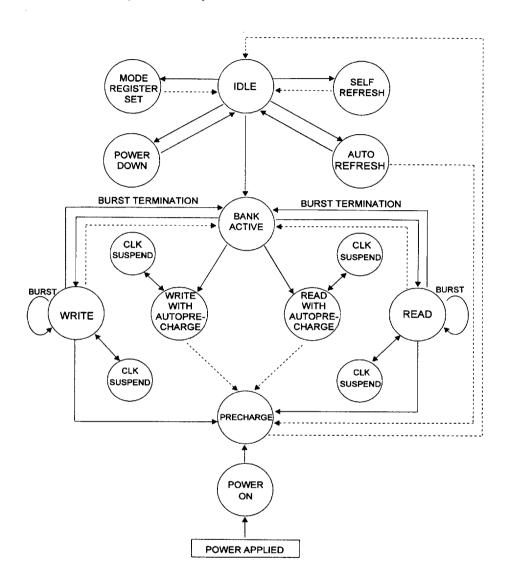

## STATE DIAGRAM(SIMPLIFIED)

| Note: |                                                    |

|-------|----------------------------------------------------|

|       | <br>by command input                               |

|       | <br>automatic sequence after finishing the command |

**4675088 0004903 148**

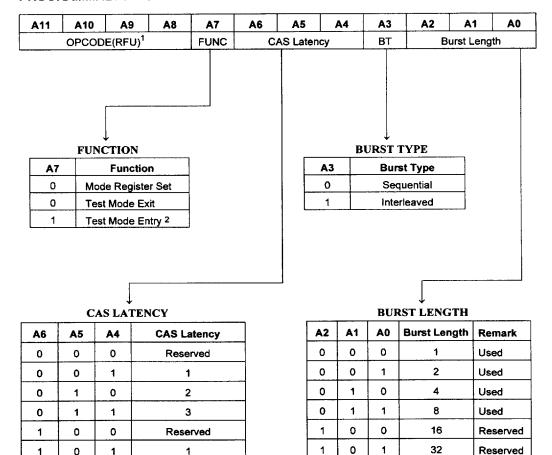

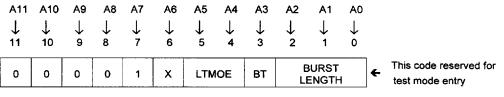

#### PROGRAMMABLE MODE REGISTER

1

1

1

1

0

64

Full Page

#### Note:

1

1

1

1

- 1. RFU-Reserved for Future Use.

- 2. TEST Mode JEDEC Standard Test

0

1

- Used to test the counter of auto refresh.

2

3

3. Full page burst supports only sequential type.

Reserved

Used3

## **OPERATION(Cycle Description, Timing Overview)**

#### 1. Mode Register Access

## 1.1. Description of Register Functions

The SDRAM has an on-chip mode register which is programmed by the user to select the read latency, burst length, and burst type to be used during read/write operations to the DRAM.

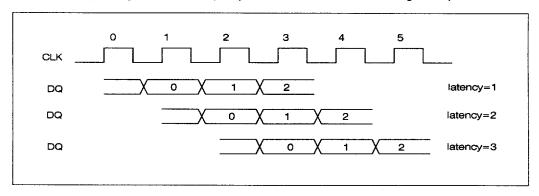

To achieve very high data rates, the SDRAM is equipped with a read pipeline which can be programmed by the user to operate with one, two, or three cycles of clock latency. Read latency is defined as the number of the first positive clock edge following the initial read invokation cycle (which we arbitrarily define as cycle 0) at which the first piece of data is guaranteed to be valid. Figure 1 illustrates read latencies of one, two, and three. The higher the latency, the higher the clock frequency the SDRAM can run at, and the higher the peak data rate.

Figure 1. Definition of Read Latency with Examples

Whenever a read(or write) command is invoked, the SDRAM initiates a read(or write) to the appropriate column address selected by A8-A0. This is defined as the beginning of the read(or write) burst. Subsequent clock cycles can be used to perform high speed read bursts (or write bursts) to column addresses adjacent to the column address supplied on A8-A0 when the read or write was invoked. The number of column addresses which can be read or written, including the original address supplied on A8-A0 is defined as the burst length. The SDRAM supports burst lengths of one, two, four, eight, or a full page of column addresses.

The SDRAM supports both sequential and interleaved mode address bursting. In burst mode, read or write is done to the address selected by A8-A0 at the beginning of the burst. On successive burst cycles, the column address is internally incremented and a read(or write) is performed to the incremented address. Table 1 shows the sequence of burst addressing for burst lengths of two, four, eight, and full page.

4675088 0004905 T10 **--**

Burst Length=2

| Starting column        | Burst Sequence |            |  |  |  |

|------------------------|----------------|------------|--|--|--|

| address<br>A0(decimal) | Sequential     | Interleave |  |  |  |

| 0                      | 0, 1           | 0, 1       |  |  |  |

| 1                      | 1.0            | 1 0        |  |  |  |

Burst Length=8

| Starting column           | Burst Sequence  |                 |  |  |  |  |

|---------------------------|-----------------|-----------------|--|--|--|--|

| address<br>A2-A0(decimal) | Sequential      | Interleave      |  |  |  |  |

| 0                         | 0,1,2,3,4,5,6,7 | 0,1,2,3,4,5,6,7 |  |  |  |  |

| 1                         | 1,2,3,4,5,6,7,0 | 1,0,3,2,5,4,7,6 |  |  |  |  |

| 2                         | 2,3,4,5,6,7,0,1 | 2,3,0,1,6,7,4,5 |  |  |  |  |

| 3                         | 3,4,5,6,7,0,1,2 | 3,2,1,0,7,6,5,4 |  |  |  |  |

| 4                         | 4,5,6,7,0,1,2,3 | 4,5,6,7,0,1,2,3 |  |  |  |  |

| 5                         | 5,6,7,0,1,2,3,4 | 5,4,7,6,1,0,3,2 |  |  |  |  |

| 6                         | 6,7,0,1,2,3,4,5 | 6,7,4,5,2,3,0,1 |  |  |  |  |

| 7                         | 7,0,1,2,3,4,5,6 | 7,6,5,4,3,2,1,0 |  |  |  |  |

Burst Length=4

Burst Length=full page

| Starting column | Burst Sc   | equence    | Starting column address | Burst Sequence    |  |

|-----------------|------------|------------|-------------------------|-------------------|--|

| address         | Commential | Interleave | A8-A0(decimal)          | (Sequential only) |  |

| A1-A0(decimal)  | Sequential |            | <b>o</b>                | 0,1,2,511         |  |

| 0               | 0, 1, 2, 3 | 0, 1, 2, 3 | 1                       | 1,2,3,511,0       |  |

| 1               | 1, 2, 3, 0 | 1, 0, 3, 2 | 2                       | 2,3,4,511,0,1     |  |

| 2               | 2, 3, 0, 1 | 2, 3, 0, 1 | 3                       | 3,4,5,511,0,1,2   |  |

| 3               | 3, 0, 1, 2 | 3, 2, 1, 0 |                         | ;                 |  |

|                 |            |            | 511                     | 511,0,1,510       |  |

Table 1. Address sequence for different burst lengths

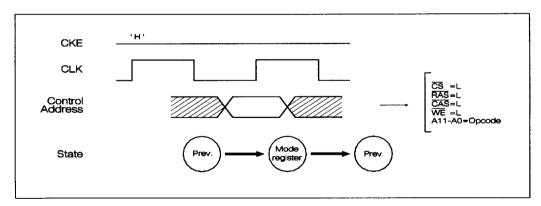

Figure 2. Timing of mode register access(program latency and burst).

**4675088 0004906 957** 894

## 1.2. Loading the Mode Register

Figure 2 shows the general timing and control for loading the mode register. Figure 3 shows the assignment of the opcode bits to the mode register and how the mode register bits control latency and burst operation. The figure also shows the assignments for entering Hyundai vendor specific test functions(to be determined).

Figure 3. Loading of the mode register and mode register bit decoding

#### Note:

1. Sequential Burst Type Only

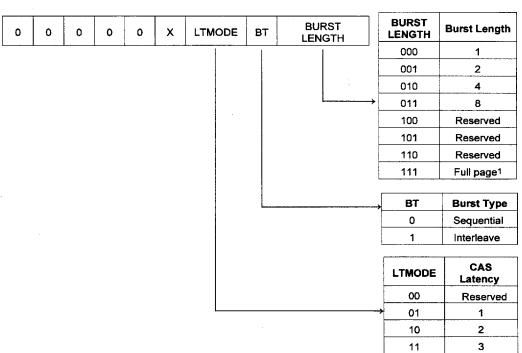

#### 2. Row Activate

A single row in either bank of DRAM can be activated using a row active command. A bank can be activated even when the opposite bank is active. A row active command cannot be given to a bank if that bank is already active. Also, a row active command cannot be given to either bank if the SDRAM is currently in the power down, self refresh, auto refresh (for the period specified by tRC), or clock suspend states. Once a row active command has been issued to the bank selected by the bank address (supplied by A11(BS)), the selected bank leaves its idle state and goes into its row activating state. Accordingly, the row address is latched and the appropriate row in the bank selected. Data from that row of memory is sensed and latched by the bank's sense amplifiers, to be used for later read(or write) operations. During the row activating period, defined by timing parameter tRCD, only NOP cycles can be executed on the selected bank. After the period tRCD, selected bank is in the row active state. Figure 4 shows a row activation cycle. Once in the row active state, the user can initiate a read or write burst, or can precharge the bank back to its idle state.

Figure 4. Row Active command to idle bank.

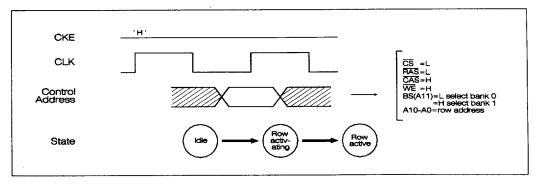

## 3. Read Operation with Programmable Pipeline

#### 3.1. Normal Read Bursts(Auto Precharge Deselected)

Figure 5 shows the basic timing and control for initiating a burst read operation without Auto Precharge selected. Output of data depends on the read latency, burst length, and burst type selected (See Section 1., *Mode Register Access*, for details). The higher the latency, the higher the operating frequency the SDRAM can run at, and the higher the peak data rate. See Table 2 and Figures 17 through 19 for details. Figures 17 through 19 illustrate burst writes following burst read on the same page. The examples assume a burst length of four but burst lengths of 1, 2, 4, 8, or full page can also be used. By issuing NOPs after the initial read command, the SDRAM will continue reading data starting from the starting column address to the end of the read burst. Data will be read to the DQ outputs (assuming DQM remains disabled low) until the last address in the burst, defined by the burst length and type has been read out. On the next clock cycle, the DQ outputs will go to Hi-Z and the bank will re-enter the row active state.

Figure 5. Burst read sequence, Auto Precharge Deselected.

While in a read burst with Auto Precharge deselected, the user can issue the following command sequences:

- 1. Issue NOPs, continue reading data starting from the starting column address to the end of the read burst. Data will be read to the DQ outputs(assuming DQM remains disabled low) until the last address in the burst, defined by the burst length and type, has been read out. On the next clock cycle, the DQ outputs will go to Hi-Z and the bank will re-enter the row active state.

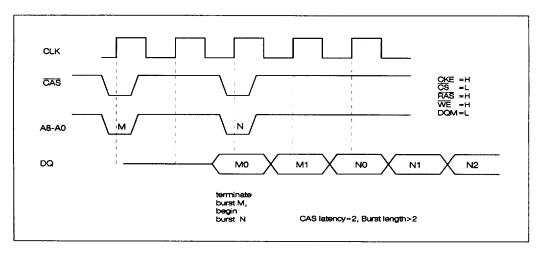

- 2. Initiate another read command (with or without Auto Precharge selected) before the end of the burst and begin a new read burst starting from another column address. The burst in progress is terminated and the first address of the new burst is read to the output after a number of clock cycles defined by the CAS latency. See Figure 6 for details.

Figure 6. Timing of read initiation with read burst in progress.

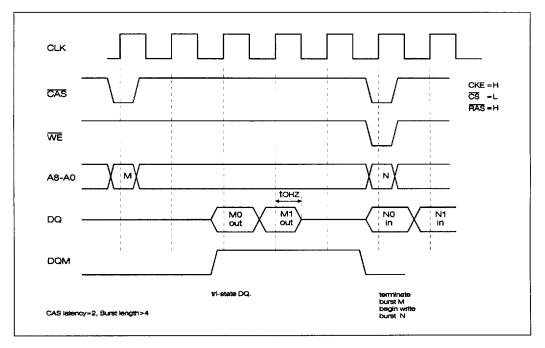

- 3. Initiate a write command with or without Auto Precharge selected before the end of the burst and begin a write burst starting from another column address. The burst in progress is terminated and the first address of the new burst is initiated. Figure 7 illustrates the timing and control for this sequence. The appropriate DQMi read/write byte enable signals must be asserted two clock cycles before the write command is issued (JEDEC specifies DQM latency is always two regardless of the CAS latency. This needs further clarification from users.)

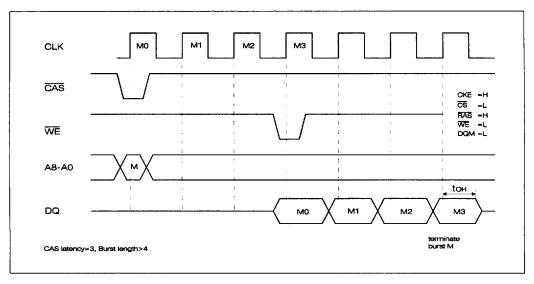

- 4. Issue a terminate burst command and return to the row active state. The timing and control for this sequence is shown in Figure 8 for the case where CAS latency is three and burst length is greater than four. Note that in this example the terminate burst command occurs on the third clock cycle after the initial read command. Currently, the SDRAM is defined such that the terminate burst command initiates the burst terminate such that the data associated with the burst counter address at the beginning of the burst terminate cycle (M3 in Figure 8) is output to DQ after the number of clock cycles defined by the clock latency. On the next clock cycle, DQ goes to Hi-Z and the bank goes to the row active state. This last bit read out upon a terminate burst cycle is the subject of some controversy and needs clarification from customers whether or not the data stream should end one cycle earlier.

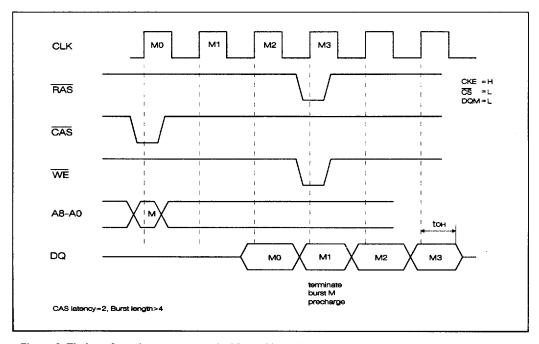

- 5. Issue a precharge command(for only the selected bank or for both banks, depending on the logic level of A10), terminate the burst, and return to the idle state after the precharge interval. Like the terminate burst command, the last data read out is that associated with burst address during the precharge command cycle. The major difference between a precharge command and a burst terminate command is that the burst terminate command returns the bank to its row active state while the precharge command returns the bank to its idle state after the designated precharge interval. The timing and control for the precharge cycle is shown in Figure 9 for the case where CAS latency is two and burst length is greater than four. Like the burst terminate the last data read out is the subject of controversy and needs clarification from customers whether or not the data stream should end one cycle earlier.

- 6. Suspend the clock. While in the clock suspended state, the state of both banks will remain unchanged.

4675088 0004910 388

Figure 7. Timing of write initiation with read burst in progress.

1SD02-00-MAY95

Figure 8. Timing of burst terminate command with read burst in progress.

Figure 9. Timing of precharge command with read burst in progress.

## 3.2. Read Bursts with Auto Precharge Selected.

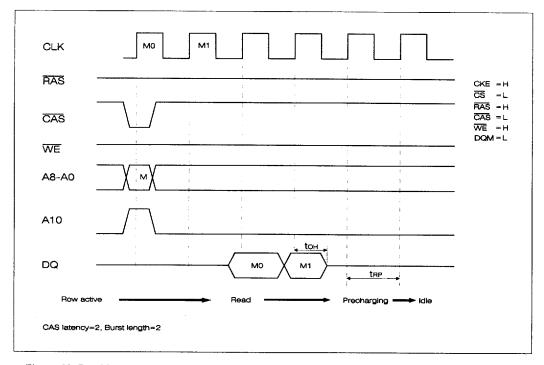

Read with Auto Precharge operation is similar to normal read(Auto Precharge deselected) operation except that the read burst cannot be terminated by issuing another command. Once the read with Auto Precharge command is invoked in a bank, only NOP commands can be issued to that bank. After the data from the last address in the burst sequence has been read out according to the selected CAS latency, burst length, and burst type, the bank will enter precharge and return to the idle state after the tRP period has expired. Figure 10 illustrates a burst read sequence with Auto Precharge selected for the case where CAS latency is two and burst length is two.

Figure 10. Read burst with Auto Precharge selected

## 4. Write Operation

902

There are several variations of write operation to the two banks of DRAM. Write bursts can be initiated to either bank with and without Auto Precharge selected. The basic write operation showing the relationship to the programmed burst length, and burst mode will be described first, and the variations for Auto Precharge will be described subsequently.

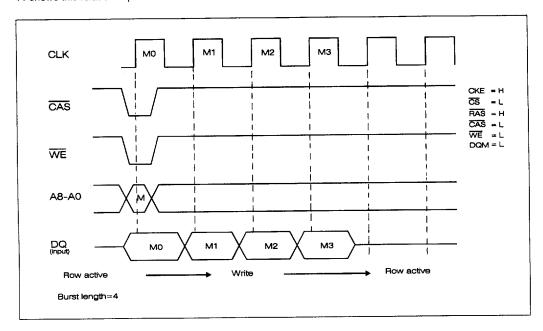

## 4.1. Write Operation with Auto Precharge Deselected

The latency for write operation is defined as the clock cycle difference between the clock where write command and column address are asserted and the clock cycle where the first data to be written is presented and is always equal to zero. That is the data for a write operation presented on the same clock cycle as its corresponding address, regardless of what value of CAS latency is programmed into the mode register. Figure 11 shows this relationship.

Figure 11. Write burst with Auto Precharge deselected.

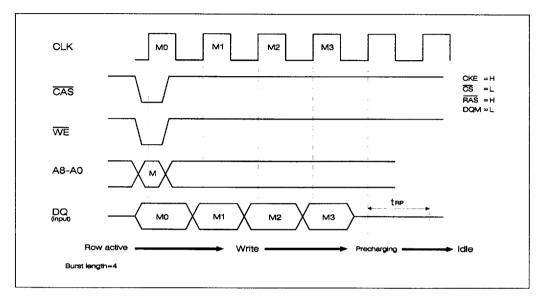

## 4.2. Write Operation with Auto Precharge

Write operation with Auto Precharge is similar to write operation without Auto Precharge except that once initiated the write burst cannot be terminated by another command. To complete the burst, NOPs must be executed and data input supplied for each address in the burst until the end of the burst has been reached. On the clock cycle following the last address in the burst, the bank will begin precharging and will re-enter the idle state after the precharge period, tRP. Figure 12 illustrates the sequence.

Figure 12. Write burst with Auto Precharge selected.

## 5. Refresh Operation

Since the SDRAM is a dynamic memory device, the stored data must be refreshed periodically or will be lost. To avoid data loss, all rows in both banks must be accessed during the maximum refresh interval specified by tREF. A row of data in either bank of RAM is refreshed whenever that row is activated. For example, activating a row for the purpose of reading or writing addresses along that row causes the data in that row to be refreshed. In addition to normal read and write operation, the SDRAM has two modes of refreshing the banks of memory: Auto Refresh and Self Refresh.

#### 5.1. Auto Refresh

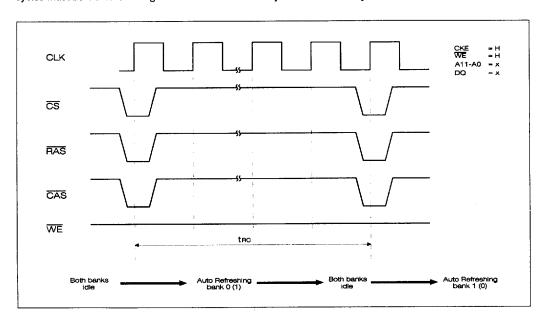

Auto Refresh is similar to CAS before RAS refresh found on previous generation asynchronous DRAMs. One Auto Refresh cycle refreshes one row of memory using 12 bits for 4K refresh parts (11 bits for 2K parts) on-chip refresh counter as the row address and bank select. The refresh counter is incremented during each Auto Refresh cycle. The upper 11 bits of the counter supply the address of one of the 2048 rows in each bank to be refreshed and the least significant bit selects the bank in which the refresh will occur. Thus, successive Auto Refresh cycles alternate between the two banks. Because Auto Refresh operation alternate between banks, both banks must be idle when Auto Refresh commands are invoked. Figure 13 shows two successive Auto Refresh cycles. Once an Auto Refresh cycle has been invoked, it is controlled internally until its duration. NOP cycles must be inserted during the entire Auto Refresh cycle time defined by tRC.

Figure 13. Timing and control for Auto Refresh Operation

#### 5.2. Self Refresh

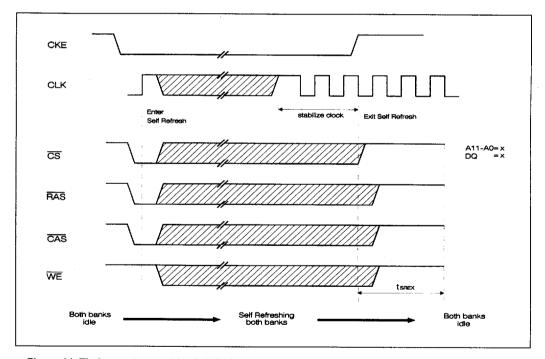

The SDRAM features an on-chip refresh cycle timing generator which can be used in conjunction with the row refresh counter(described in Section 5.1.) to completely refresh the two banks of DRAM entirely under internal control. Self Refresh can be invoked only when both banks are idle. While the device is in Self Refresh mode, CKE is the only enabled input to the device. All other inputs, including the clock are disabled and any input is ignored Self Refresh mode is entered by invoking an Auto Refresh command with CKE low transition. Once this command is invoked, the cycle timing generator performs a burst, refresh sequencing through, all 4096 rows (2048 rows in each bank) with a per row refresh cycle time of approximately 1 microsecond. To conserve power, once the burst refresh has been completed to all 4096 rows the cycle timing generator automatically slows down to a per row refresh period of approximately 32 microseconds and refresh operation continues until Self Refresh mode is exited (Important: The internal per row refresh cycle times are not guaranteed.) Upon exiting Self Refresh mode, the time elapsed since the least recently refreshed row was refreshed can vary from a few milliseconds to 32 milliseconds. Consequently, to be sure that all DRAM rows remain refreshed it is recommended that a burst of 4096 Auto Refresh commands be performed immediately after exiting Self Refresh mode. Self refresh mode is exited by starting the clock (if the clock had stopped) and then asserting CKE after the clock waveform has stabilized. The low-to-high transition of CKE will re-enable the clock and other inputs asynchronously. A minimum time, specified by tsrex, must be satisfied before any command other than Exit Self Refresh is invoked. Figure 14 shows how Self Refresh mode is entered and exited.

Note: Clarification from customers should be obtained to determine if Self Refresh mode is of sufficient value to customers to warrant its additional complexity and recurring manufacturing costs.

Figure 14. Timing and control for Self Refresh Operation

#### 6. Power Down

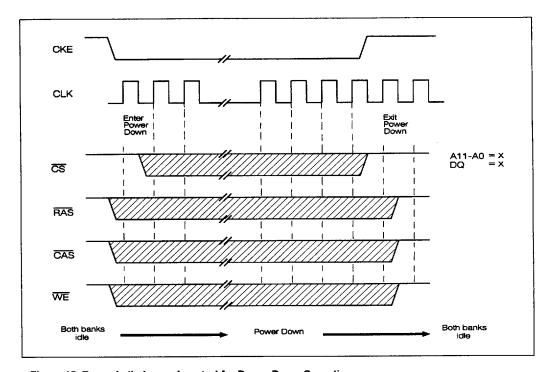

The SDRAM has two internal clock buffers. A low current capacity clock buffer feeds the CKE input buffer while a high current clock buffer feeds the state machine and all DRAM circuits. During the Power Down state, the large clock buffer is disabled but the small clock buffer is not. In contrast to the Self Refresh state, entering and exiting Power Down is completely synchronous with respect to CKE. That is, CKE is sampled on every clock cycle, rather than asynchronously changing the state of the SDRAM Power Down is the lowest power state available. During Power Down, the SDRAM is not refreshed. Therefore, the minimum refresh specification still applies during power down. Figure 15 shows an example of the timing and control for entering and exiting Power Down. Exiting Power Down requires one clock cycle, as shown in the figure. Other commands can be issued on the clock cycle following the Exit Power Down command cycle.

Figure 15. Example timing and control for Power Down Operation

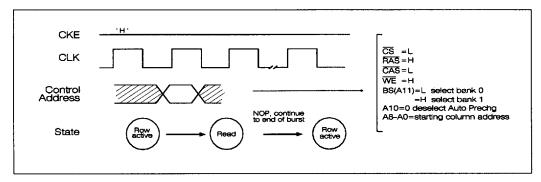

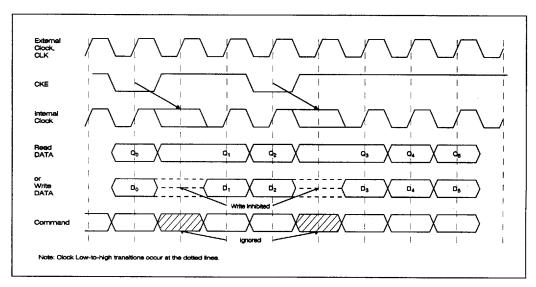

## 7. Clock Suspend

Clock Suspend is very similar to Power Down, except that the Clock Suspend command is invoked by sampling the CKE signal low while one or both banks are not idle. While the clock is suspended, only the CLK and CKE inputs are enabled, and the state of CKE is sampled on every clock cycle. Internally, the banks remain in the state they were in when the clock was suspended. For example, if bank 0 was in the middle of a read burst when the clock was suspended, the read state will be maintained after exiting Clock Suspend. On the next clock cycle, the burst can be resumed from the next memory location designated by the burst length and burst type programmed in the Mode Register, or other legal commands can be issued to the active or both banks. While the clock is suspended, the SDRAM is not refreshed. Therefore, the minimum refresh specification still applies during the period when the clock is suspended. Figure 16 illustrates how Clock Suspend is entered and exited.

Figure 16. Example timing and control for Clock Suspend Operation

#### 8. Test Mode

Test mode is used to check the functionality of refresh address counter in this SDRAM. For more details, refer to attached timing diagram 37 and 38.

#### 9. Power on Sequence

Once power has been applied, Synchronous DRAM must be initialized with proper power on sequence.(JEDEC standard)

- step 1) Pause a time of 200µs with NOPs, keeping CKE and DQM be high.

- step 2) Assert "Precharge command(s)" to ensure both banks are precharged.

- step 3) Wait tRP, then assert "Mode register set command" to program the mode register.

- step 4) Stay NOP for 2 clocks, then 2 or more "Auto refresh commands" should be performed.

For more details, refer to attached timming diagram 4.

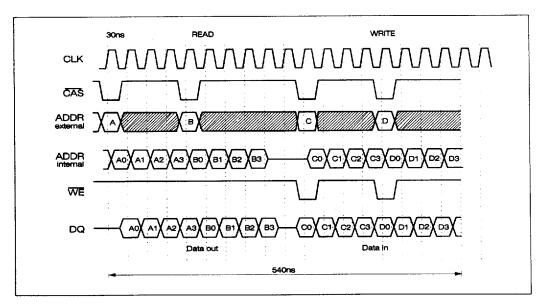

Figure 17. Timing of pipeline operation, latency=1, burst length=4.

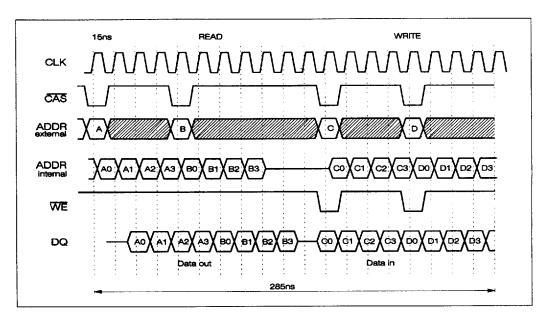

Figure 18. Timing of pipeline operation, latency=2, burst length=4.

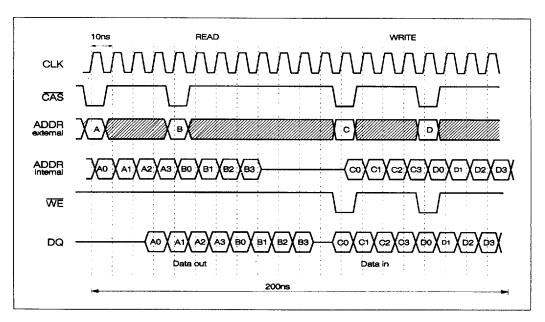

Figure 19. Timing of pipeline operation, latency=3, burst length=4

| Maximum Frequency       | 50MHz    | 66MHz    | 80MHz    | 100MHz   |

|-------------------------|----------|----------|----------|----------|

| CLK cycle time          | 20ns     | 15ns     | 12.5ns   | 10ns     |

| CAS latency (20ns)      | 2 cycles | 2 cycles | 2 cycles | 3 cycles |

| RCD min (20ns)          | 1 cycle  | 2 cycles | 2 cycles | 2 cycles |

| RAS to precharge (50ns) | 3 cycles | 4 cycles | 4 cycles | 5 cycles |

| RAS precharge (30ns)    | 2 cycles | 2 cycles | 3 cycles | 3 cycles |

| RAS cycle time (80ns)   | 5 cycles | 6 cycles | 7 cycles | 8 cycles |

Table 2. Performance Parameters and Frequency Versus Clock Latency

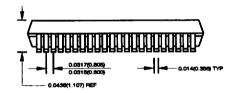

## PACKAGE INFORMATION

400mil 44 pin Thin Small Outline Package (TC)