# DS3RTA P and N Rail Device DS-3 Line Interface TXC™-02002

### PRELIMINARY DATA SHEET

TranSwitch © 1990

Patents Pending

#### FEATURES =

- Provides all functionality required to terminate a DS-3 signal:

- Clock recovery and filter

- All line equalization

- LOS/LOC detection and AIS generation

- P and N rail NRZ I/O

- Satisfies jitter tolerance requirements on the DS-3 inputs

- Transmits and receives at the STS-1 rate (51.84 MHz) as well as the DS-3 rate (44.736 MHz)

- · Provides two DS-3 loopbacks:

- Receive to transmit (digital)

- Transmit to receive (analog, no RX amplifiers)

- · Meets all applicable ANSI/Bellcore standards:

- T1.102, 107, 404

- TR-TSY-000009

- · CMOS for low power and enhanced reliability

#### **DESCRIPTION**

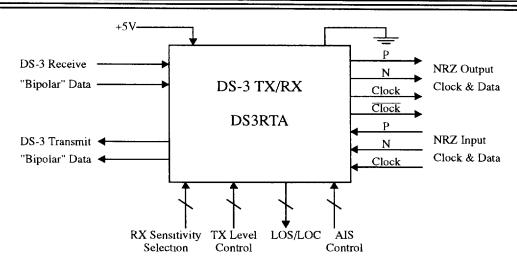

The DS3RTA is similar in function with the DS3RT (TXC-02001). The DS3RTA features P and N rail I/O on the NRZ terminal side of the device. The P and N data outputs correspond exactly to the received DS-3 line data, and the P and N data inputs cause corresponding pulses on the DS-3 line output without regard to line coding.

The DS3RTA efficiently replaces traditional means of receiving and transmitting DS-3 signals, and is especially useful for retrofit applications. It also may be used to transmit and receive SONET STS-1 signals on cable. The DS3RTA accepts a wide receive range of signals, and it has a unique built-in transversal filter for output pulse shaping. Line compensation is reduced to a simple output level setting using a hardware strap. On-chip filter and clock recovery circuits eliminate normally required external components. A built-in framed AIS generator may be enabled in the transmit direction with or without the transmit loss of clock.

#### **APPLICATIONS ≡**

- · Single board M13 multiplexer

- I/O for DS-3 or SONET DSX

- · Fractional T3

- · DCS and EDSX

- · CSU/DSU

TXC and TranSwitch are registered trademarks of TranSwitch Corporation

TXC-02002-AXXX-MB Ed. 1, September 1991

TranSwitch Corporation • 8 Progress Drive • Shelton, CT 06484 • USA • Tel: 203-929-8810 • Fax: 203-926-9453

I 9004152 0000832 T74 **■**

#### DS3RTA BLOCK DIAGRAM

#### □ BLOCK DIAGRAM DESCRIPTION

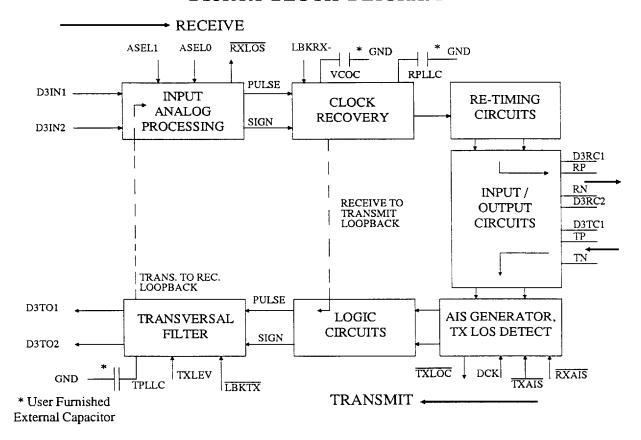

The DS3RTA accepts a wide range of signals, and it has two control leads to adjust the input sensitivity: ASEL0 and ASEL1. The Input Analog Processing block also has built-in thresholds for the detection of ones and zeros on the DS-3 line input. The clock recovery contains a phase-locked loop with substantial digital logic for the clock recovery algorithm.

The receive side of the DS3RTA recovers clock from the B3ZS encoded input signal. The average time to recover clock from the onset of received data is 1 millisecond with the recommended components connected to RPLCC and VCOC. Proper recovery depends only on the amplitude of the received pulses and the setting of the ASEL1 and ASEL2 leads. There is ample overlap of receive sensitivities to ease the selection of ASEL1 and ASEL2 (see the Control Function Table).

If the DS3RTA detects more than 128 zeros from the cable input, then  $\overline{\text{RXLOS}}$  becomes valid.

The P and N rail signals on the receive side of the DS3RTA are clocked NRZ duplicates of the B3ZS encoded DS-3 line input signals.

On the transmit side, the NRZ clock and P and N data are examined for loss of clock. If there is loss of clock for about 500 clock cycles then the TXLOC lead goes to ground, and this lead may be connected to the TXAIS lead so that AIS is sent automatically on TXLOC going low. Alternatively, the TXAIS lead may be taken to ground independently to generate a DS-3 AIS or blue signal.

The signals from this block feed a unique built-in transversal filter for output pulse shaping. Line compensation is reduced to a simple output level setting using a hardware strap, TXLEV. The DS-3 line signal corresponds exactly to the clocked NRZ P and N rail input to the DS3RTA.

The resulting output waveform is such that no external compensation networks are required to meet the requirements at the cross connect, regardless of the distance between it and the DS3RTA. The plots on pages 8 and 9 show the pulse shapes at the cross connect for three different cable lengths.

# CONTROL FUNCTION TABLE

| CONTROL      | STATE                                                | FUNCTION                                                                                 |

|--------------|------------------------------------------------------|------------------------------------------------------------------------------------------|

| LBKRX        | Open<br>Gnd.                                         | Loopback disabled, NRZ to NRZ<br>Loopback enabled, NRZ to NRZ                            |

| LBKTX        | Open<br>Gnd.                                         | Loopback disabled, bipolar to bipolar<br>Loopback enabled, bipolar to bipolar            |

| ASEL1, ASLE0 | Gnd., Open<br>Open, Gnd.<br>Open, Open<br>Gnd., Gnd. | NOT USED<br>150 to 360 mv peak input<br>400 mv to 1 v. peak input<br>200 to 570 mv input |

| TXLEV        | Open<br>Gnd.                                         | High level transmit<br>Low level transmit                                                |

| TXAIS        | Open<br>Gnd.                                         | Transmit AIS disabled<br>Transmit AIS enabled                                            |

#### □ OPERATING CONDITIONS

Absolute Maximum Ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VDD                      | 7V             |

|------------------------------------------|----------------|

| Input voltage, V <sub>I</sub>            | VDD            |

| Operating free-air temperature range, TA | 0°C to 70°C    |

| Storage temperature range, Ts            | ·65°C to 150°C |

#### **Functional Operating Range**

$V_{DD} = 5 + .5\%$ ;  $V_{SS} = 0$  (ground) supply voltage  $T_A = -0^{\circ}$ C to  $70^{\circ}$ C operating free-air temperature range

### INPUT PARAMETERS

| PARAMETER                                | MIN  | MAX                 | UNIT |

|------------------------------------------|------|---------------------|------|

| VIH High-level input voltage             | 2    | V <sub>DD</sub> +.5 | V    |

| VIL Low-level input voltage              | Vss5 | 0.8                 | V    |

| I <sub>IH</sub> High-level input current |      | -50                 | μΑ   |

| IIL Low-level input current              |      | 50                  | μA   |

| C <sub>IN</sub> input pin capacitance    |      | 10                  | pF   |

# **OUTPUT PARAMETERS**

| PARAMETER       | TEST CONDITIONS                 | MIN | MAX               | UNIT |

|-----------------|---------------------------------|-----|-------------------|------|

| VOH             | V <sub>DD</sub> =4.75 TO 5.25 V | 2.4 | V <sub>DD</sub> 5 | V    |

| V <sub>OL</sub> | V <sub>DD</sub> =5.25V          | Vss | 0.4               | V    |

| IOH*            | $V_{OH} = V_{DD}5 V$            | -1  | 4                 | mA   |

| IOL*            | $V_{OL} = 0.4 \text{ V}$        | -2  |                   | mA   |

| Cout            |                                 |     | 25                | pF   |

<sup>\*</sup> DS-3 NRZ clock and data outputs: IOH Min = -4 mA and IOL Min = 8 mA.

# Power Dissipation

At  $V_{DD} = 5.25$  volts and all ports active,  $I_{DD}$  Max = 95 milliamps. The maximum power is 500 milliwatts. The nominal power dissipation is 400 milliwatts.

#### Analog DS-3 Line I/O

### ANALOG INPUT AND OUTPUT PARAMETERS

| PARAMETER                         | MAX  | MIN  | UNIT |

|-----------------------------------|------|------|------|

| Peak input DS3                    | 1.0  | 0.15 | V    |

| Peak output DS3 (TXLVL open)      | 1.3  | 1.1  | V*   |

| Peak output DS3 (TXLVL gnd.)      | 0.95 | 0.85 | V*   |

| Input impedance                   | 7200 | 4800 | Ohms |

| Output 2nd harmonic (all 1s code) | -30  |      | dB   |

| Frequency range                   | 52   | 40   | MHz  |

<sup>\*</sup> In order to meet these output voltage levels, the output of the DS3RTA must be loaded with no more than 10 kohms in parallel with 2 pF. See application note TXC-02002-AXXX-AN for details.

#### **DS-3 B3ZS Jitter Tolerance**

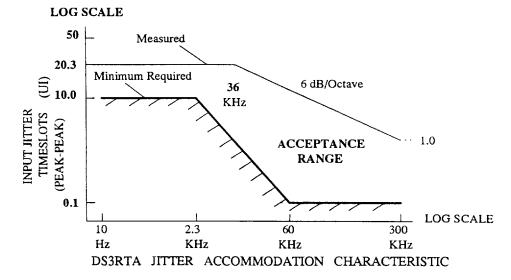

# **DS3RTA JITTER TOLERANCE**

This jitter tolerance curve applies at the line input of the DS3RTA (pin 29, DS3IN1). The DS3RTA recovers clock, and outputs P and N rail data and clock in the presence of the pictured input jitter characteristic.

With the selected values of components on pin 7, VCOC, the jitter transfer through the DS3RTA is unity or 0 dB and is independent of the frequency of the jitter. Please refer to the DS3RTA Application Note, TXC-02002-AXXX-AN, for component details.

#### ☐ TIMING CHARACTERISTICS

### **DS3RTA TIMING PARAMETERS**

| PARAMETER         | I/O, CONDITION                                                    | MIN | NOM                 | MAX | UNIT           |

|-------------------|-------------------------------------------------------------------|-----|---------------------|-----|----------------|

| tDCD, Delay*      | Clock high to data change, out                                    | 0.6 |                     | 3   | ns             |

| tsDC, Setup       | Data to clock low, in                                             | 5.5 |                     |     | ns             |

| tHCD, Hold        | Data stable after clock low, in                                   | 8.5 |                     |     | ns             |

| tF<br>tR<br>tCYC3 | Clock fall time<br>Clock rise time<br>Nominal DS-3 ck. cycle time |     | 2.5<br>3.5<br>22.35 |     | ns<br>ns<br>ns |

<sup>\*</sup> With respect to D3RC2, the positive edge reference

A voltage waveform is defined as "high" when it last exceeds VOH or VIH, as appropriate. Likewise, a voltage waveform is defined as "low" when it last goes below VOL or VIL. Timing intervals are defined as the time difference between the crossing of the voltage values on the same or different waveforms.

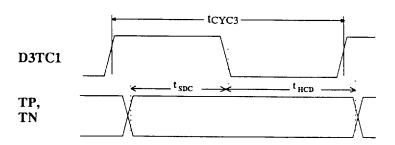

### **Timing Diagrams**

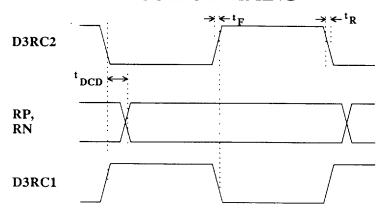

### **DS-3 OUTPUT TIMING**

This figure illustrates the propagation delay of the data on the RP and RN pins with respect to the two clocks, D3RC1 and D3RC2. The only difference between the clocks is that one is the inverse of the other.

This figure illustrates the DS-3 transmit signal that is on the TP and TN leads of the DS3RTA. The times illustrated in this figure and the figure for the RX data are not necessarily to scale. The values for tSCD and tHCD are given in the timing parameters table. The clock cycle time is nominally 22.35 nanoseconds and both receive and transmit clocks have a duty cycle of 50 +/- 5 %.

# **DS-3 INPUT TIMING**

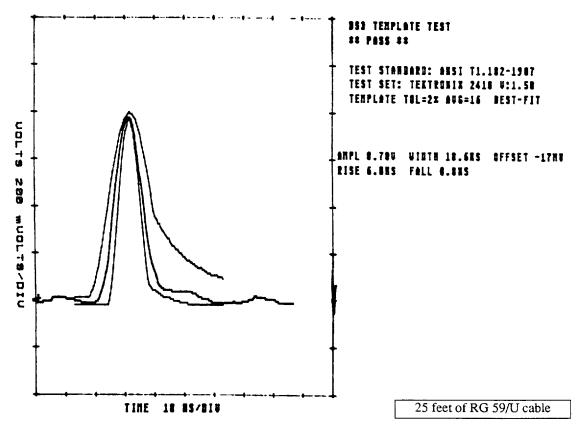

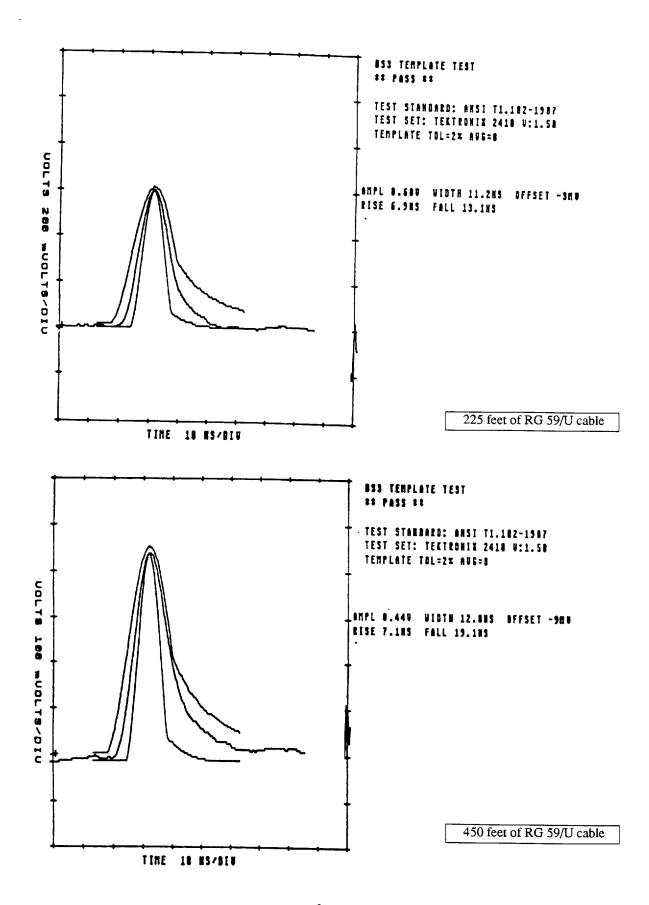

# PHOTOGRAPHS OF TRANSMITTED WAVEFORM DS3RTA WITH BUFFER AMPLIFIER AND TRANSFORMER

These plots (pages 8 and 9) were made from a Tektronics 2410 Digital Interface Test System using a 2% tolerance on the DS-3 mask given in ANSI T1.102-1987. ANSI has adopted a 3% tolerance on the DS-3 waveform mask. The DS3RTA requires no external build out, and its transmit waveform meets the mask at all lengths up to 450 feet, as required.

The peak amplitude of the pulse at the output of 25 feet of cable is 700 millivolts. The DS3RTA had the TXLEV lead (pin 35) at ground for the low level output (about 770 millivolts). The ANSI requirement at the DSX ranges from 850 to 360 millivolts. The observed amplitudes are within the required range for all cable lengths.

# □ PIN DEFINITION

# **DS3RTA PIN I/O AND FUNCTION**

| NAME                              | I/O         | PIN NO.                       | FUNCTION                                                                                                                                                   |

|-----------------------------------|-------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVDDT<br>AVDDR<br>DVDDT<br>DVDDR  |             | 37<br>23<br>42<br>10          | 5-volt supply voltage, +/- 5%, analog transmit " " analog receive " " digital transmit " " digital receive                                                 |

| AGNDR<br>AGNDR1<br>AGNDT<br>DGNDR |             | 31<br>16<br>36<br>11,44       | Vss or ground, 0 volts reference, analog receive " " analog receive (PLL) " " analog transmit " " digital receive                                          |

| DGNDT<br>TXLOC<br>VCOC<br>DCK     | O<br>I      | 6, 8<br>2<br>7<br>9           | " " digital transmit Ground-true indication of TX loss of clock External capacitor connection DS-3 external clock for AIS and loss of clock                |

| RN<br>RP<br>D3RC1<br>DS3C2        | 0 0 0       | 12<br>13<br>14<br>15          | N-rail received data output P-rail received data output Negative edge clock for output data Positive edge clock for output data                            |

| RPLLC<br>RXLOS<br>LBKRX<br>LBKTX  | O<br>I<br>I | 17<br>20<br>24<br>25          | External capacitor connection Ground-true indication of receive loss of signal Strap to ground to loop back RX to TX Strap to ground to loop back TX to RX |

| ASEL0<br>ASEL1                    | I<br>I      | 26<br>27                      | Receive gain control LSB<br>Receive gain control MSB                                                                                                       |

| D3IN1<br>D3IN2                    | I           | 29<br>30                      | DS3 line input (1 of 2)<br>DS3 line input (2 of 2)                                                                                                         |

| TPLLC<br>D3TO2<br>D3TO1<br>TXLEV  | 0<br>0<br>I | 32<br>33<br>34<br>35          | External capacitor connection  DS3 line output (2 of 2)  DS3 line output (1 of 2)  Line transmit level control                                             |

| D3TC1<br>TP<br>TN<br>TXAIS        | I<br>I<br>I | 38<br>40<br>41<br>43          | Clock input for transmit P and N rail data P-rail transmit data input N-rail transmit data input Strap to ground to enable transmit AIS                    |

| N.C.                              |             | 1,3,4,5,18,19,<br>21,22,28,39 | Connect to GND                                                                                                                                             |

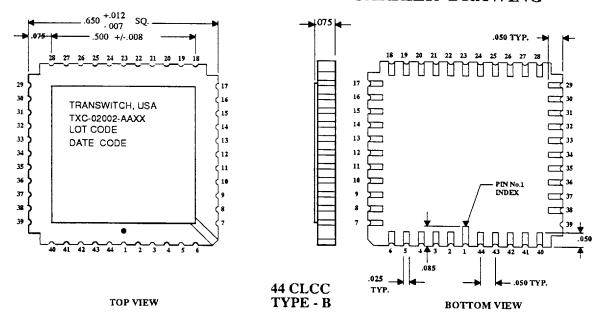

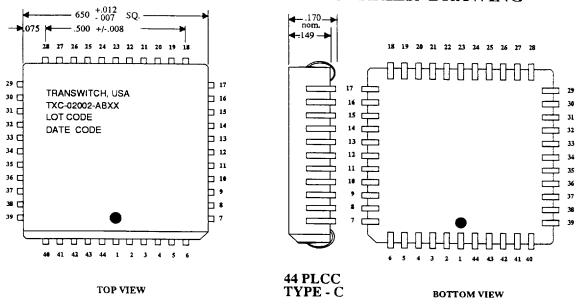

#### □ PACKAGING

Both ceramic and plastic packages are available for the DS3RTA. as illustrated below. The ceramic package has 44-pins (Type B) with pads for surface mounting. A similar plastic package (Type C) is illustrated below. These and other packaging options are available on request from TranSwitch. The TranSwitch family of DS-3 devices operates over the full commercial temperature range of -0°C to 70°C. Burn-in is a customer option.

# CERAMIC 44-PIN LEADLESS CHIP CARRIER DRAWING

# PLASTIC 44-PIN LEADED CHIP CARRIER DRAWING

**.** 9004152 0000842 913 **.**

#### □ ORDERING INFORMATION

TXC-02002-ACPL TXC-02002-ACCN

Plastic 44-Pin Leaded Chip Carrier, 0°C to +70°C Ceramic 44-Pin Leadless Chip Carrier, 0°C to +70°C

Future: -40°C to +85°C version is planned.

### ☐ FURTHER INFORMATION

Application information for the DS3RTA is available in TXC-02002-AXXX-AN

#### □ RELATED PRODUCTS

TXC-02001-AXXX DS3RT

Similar to the DS3RTA, but contains the B3ZS codec and provides NRZ clock and data on the terminal side I/O. It also includes an error estimate output based on coding violations to indicate a 10<sup>-6</sup> bit error rate. It also includes a raw coding violation output pulse when a coding violation occurs in the received DS-3 data pattern.

TXC-02003-AXXX DS3RX

Similar to the DS3RT (TXC-02001), but has the DS-3 receive function only.

TranSwitch reserves the right to make changes to the product(s) or circuit(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product or circuit.

■ 9004152 0000843 85T **■**

12

45846