**Preliminary User's Manual**

# VR5500™

# 64/32-Bit Microprocessor

μ**PD30550**

Document No. U16044EJ1V0UM00 (1st edition) Date Published August 2002 N CP(K)

NEC Corporation 2002

MIPS Technologies, Inc. 2001

Printed in Japan

[MEMO]

# **①** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

#### 2 HANDLING OF UNUSED INPUT PINS FOR CMOS

Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

VR Series, VR4000, VR4000 Series, VR4100 Series, VR4200, VR4300 Series, VR4400, VR5000, VR5000 Series, VR5000A, VR5432, VR5500, and VR10000 are trademarks of NEC Corporation.

MIPS is a registered trademark of MIPS Technologies, Inc. in the United States.

MC68000 is a trademark of Motorola Inc.

IBM370 is a trademark of IBM Corp.

Pentium is a trademark of Intel Corp.

DEC VAX is a trademark of Digital Equipment Corporation.

UNIX is a registered trademark in the United States and other countries, licensed exclusively through X/Open Company Ltd.

Exporting this product or equipment that includes this product may require a governmental license from the U.S.A. for some countries because this product utilizes technologies limited by the export control regulations of the U.S.A.

- The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

- Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

- NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

- Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software, and information in the design of the customer's equipment shall be done under the full responsibility of the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.

- While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

- NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

### NEC Electronics Inc. (U.S.)

Santa Clara, California Tel: 408-588-6000 800-366-9782 Fax: 408-588-6130 800-729-9288

#### NEC do Brasil S.A.

Electron Devices Division Guarulhos-SP, Brasil Tel: 11-6462-6810 Fax: 11-6462-6829

#### **NEC Electronics (Europe) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 01 Fax: 0211-65 03 327

- Sucursal en España Madrid, Spain Tel: 091-504 27 87 Fax: 091-504 28 60

- Succursale Française Vélizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

- Filiale Italiana Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

- Branch The Netherlands Eindhoven, The Netherlands Tel: 040-244 58 45 Fax: 040-244 45 80

- Branch Sweden Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

- United Kingdom Branch Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

NEC Electronics Hong Kong Ltd. Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

NEC Electronics Hong Kong Ltd. Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

NEC Electronics Shanghai, Ltd. Shanghai, P.R. China Tel: 021-6841-1138 Fax: 021-6841-1137

NEC Electronics Taiwan Ltd. Taipei, Taiwan Tel: 02-2719-2377 Fax: 02-2719-5951

NEC Electronics Singapore Pte. Ltd. Novena Square, Singapore Tel: 253-8311 Fax: 250-3583

J02.4

### INTRODUCTION

| Readers                 | This manual is intended for users who wish to understand the functions of the V <sub>R</sub> 5500 ( $\mu$ PD30550) and to develop application systems using this microprocessor.                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose                 | This manual introduces the architecture and hardware functions of the $V_{\rm R}5500$ to users, following the organization described below.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Organization            | This manual consists of the following contents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                         | <ul> <li>Introduction</li> <li>Pipeline operation</li> <li>Cache organization and memory management system</li> <li>Exception processing</li> <li>Floating-point unit operation</li> <li>Hardware</li> <li>Instruction set details</li> </ul>                                                                                                                                                                                                                                                                                                                            |

| How to read this manual | It is assumed that the reader of this manual has general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | The Vв4400 <sup>™</sup> in this manual includes the Vв4000 <sup>™</sup> .<br>The Vв4000 Series <sup>™</sup> in this document indicates the Vв4100 Series <sup>™</sup> , Vв4200 <sup>™</sup> ,<br>Vв4300 Series <sup>™</sup> , and Vв4400.                                                                                                                                                                                                                                                                                                                                |

|                         | To learn in detail about the function of a specific instruction,<br>→ Read CHAPTER 3 OUTLINE OF INSTRUCTION SET, CHAPTER 7<br>FLOATING-POINT UNIT, CHAPTER 17 CPU INSTRUCTION SET, and<br>CHAPTER 18 FPU INSTRUCTION SET.                                                                                                                                                                                                                                                                                                                                                |

|                         | To know about the overall functions of the V <sub>R</sub> 5500: $\rightarrow$ Read this manual in the order of the contents.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | To know about electrical specifications of the VR5500:<br>$\rightarrow$ Refer to <b>Data Sheet</b> which is separately available.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Conventions             | Data significance:Higher digits on the left and lower digits on the rightActive low representation:XX# (trailing # after pin and signal names)Note:Footnote for item marked with Note in the textCaution:Information requiring particular attentionRemark:Supplementary informationNumerical representation:Binary XXXX or XXXX2DecimalXXXXHexadecimal 0xXXXXPrefix indicating the power of 2 (address space, memory capacity):K (kilo) $2^{10} = 1,024$ M (mega) $2^{20} = 1,024^2$ G (giga) $2^{30} = 1,024^3$ T (tera) $2^{40} = 1,024^6$ P (peta) $2^{50} = 1,024^6$ |

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However preliminary versions are not marked as such.

#### **Documents Related to Devices**

| Document Name                                            | Document No.   |

|----------------------------------------------------------|----------------|

| $\mu$ PD30550 (V <sub>R</sub> 5500) Data Sheet           | To be prepared |

| VR5500 User's Manual                                     | This Manual    |

| V <sub>R</sub> 5432 <sup>™</sup> User's Manual Volume 1  | U13751E        |

| VR5432 User's Manual Volume 2                            | U15397E        |

| V₅5000 <sup>™</sup> , V₅5000A <sup>™</sup> User's Manual | U11761E        |

| V₅5000, V₅10000 <sup>™</sup> Instruction User's Manual   | U12754E        |

#### **Application Note**

| Document Name                                                         | Document No. |

|-----------------------------------------------------------------------|--------------|

| V <sub>R</sub> Series <sup>™</sup> Programming Guide Application Note | U10710E      |

#### CONTENTS

| CHAPTI     | ER 1 0         | GENERAL                                                         | 25 |

|------------|----------------|-----------------------------------------------------------------|----|

| 1.1        | Featu          | Ires                                                            | 25 |

| 1.2        | Orde           | ring Information                                                | 26 |

| 1.3        | Vr550          | 00 Processor                                                    | 26 |

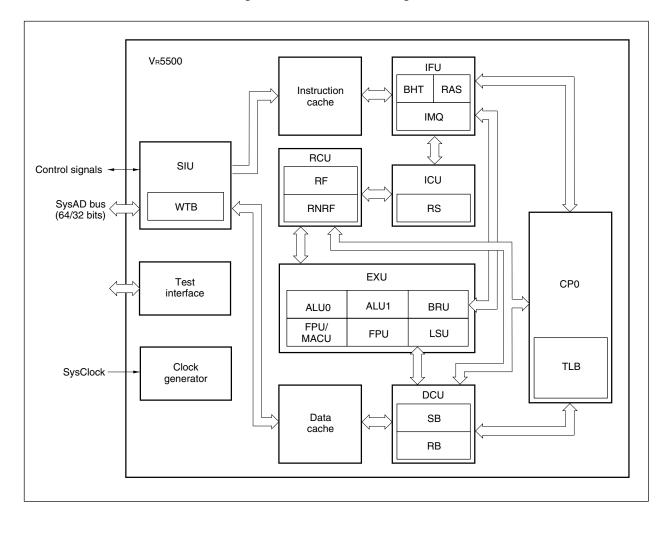

|            | 1.3.1          | Internal block configuration                                    |    |

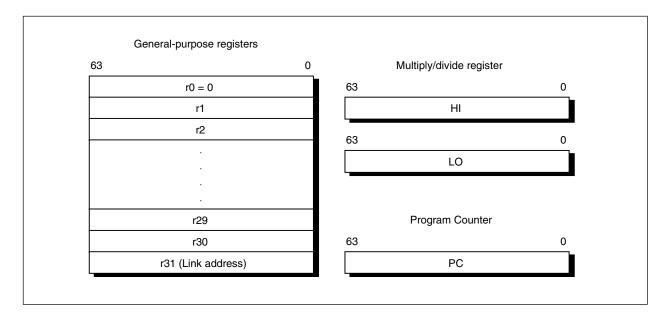

|            | 1.3.2          | CPU registers                                                   |    |

|            | 1.3.3          | Coprocessors                                                    | 31 |

|            | 1.3.4          | System control coprocessors (CP0)                               | 32 |

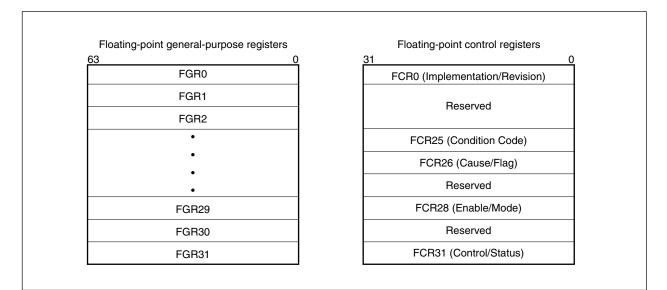

|            | 1.3.5          | Floating-point unit                                             |    |

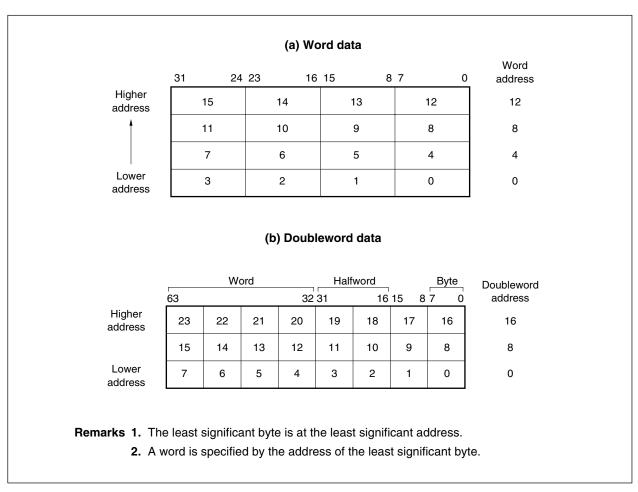

|            | 1.3.6          | Cache memory                                                    |    |

| 1.4        |                | ne of Instruction Set                                           |    |

| 1.5        |                | Format and Addressing                                           |    |

| 1.6        | Memo           | ory Management System                                           |    |

|            | 1.6.1          | High-speed translation lookaside buffer (TLB)                   |    |

|            | 1.6.2          | Processor modes                                                 |    |

| 1.7        | Instru         | uction Pipeline                                                 |    |

|            | 1.7.1          | Branch prediction                                               |    |

|            |                |                                                                 |    |

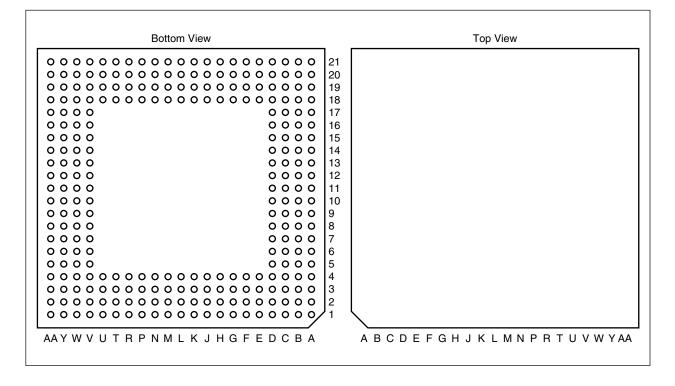

|            |                | PIN FUNCTIONS                                                   |    |

| 2.1<br>2.2 |                | onfiguration<br>unctions                                        |    |

| 2.2        |                |                                                                 |    |

|            | 2.2.1<br>2.2.2 | System interface signals                                        |    |

|            | 2.2.2          | Initialization interface signals<br>Interrupt interface signals |    |

|            | 2.2.3          | Clock interface signals                                         |    |

|            | 2.2.4          | Power supply                                                    |    |

|            | 2.2.5          | Test interface signal                                           |    |

| 23         |                | ling of Unused Pins                                             |    |

| 2.5        | 2.3.1          | System interface pin                                            |    |

|            | 2.3.1          | Test interface pins                                             |    |

|            | 2.0.2          |                                                                 |    |

| СНАРТІ     | ER 3           | OUTLINE OF INSTRUCTION SET                                      |    |

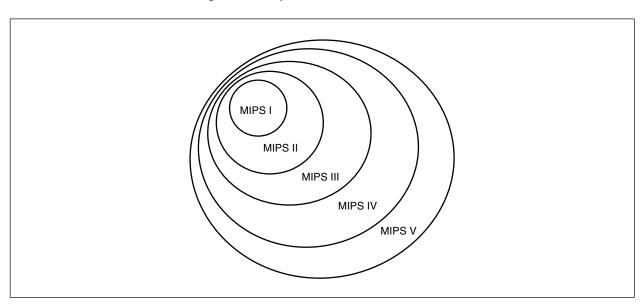

| 3.1        |                | uction Set Architecture                                         |    |

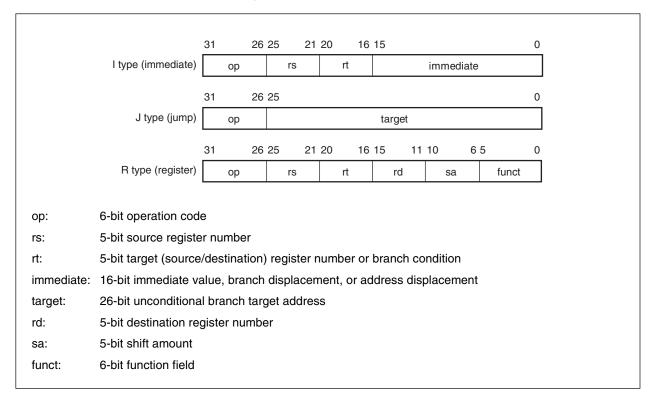

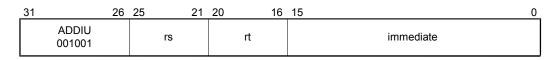

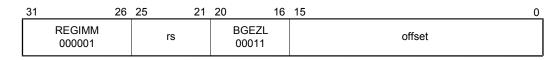

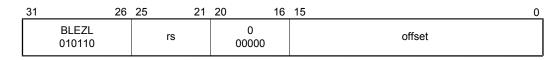

|            | 3.1.1          | Instruction format                                              | 51 |

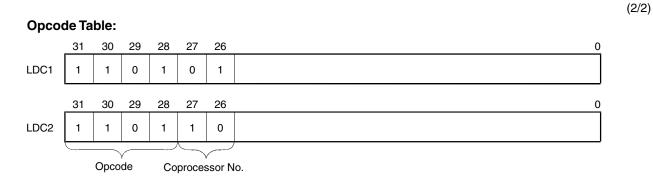

|            | 3.1.2          | Load/store instructions                                         |    |

|            | 3.1.3          | Operation instructions                                          | 55 |

|            | 3.1.4          | Jump/branch instructions                                        |    |

|            | 3.1.5          | Special instructions                                            |    |

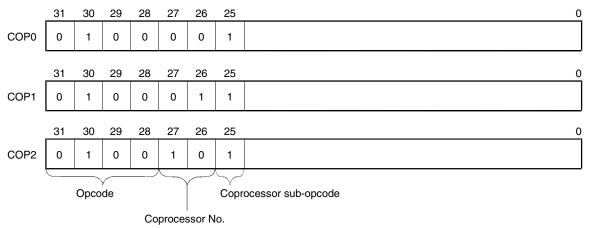

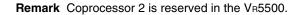

|            | 3.1.6          | Coprocessor instructions                                        |    |

| 3.2        | Addit          | tion and Modification of VR5500 Instructions                    | 57 |

|            | 3.2.1          | Integer rotate instructions                                     | 57 |

|            | 3.2.2          | Sum-of-products instructions                                    |    |

|            | 3.2.3          | Register scan instructions                                      | 59 |

|            | 3.2.4          | Floating-point load/store instructions                          | 59 |

|            | 3.2.5          | Other additional instructions                                   |    |

|                | 3.2.6 Instructions for which functions and operations were changed          |     |

|----------------|-----------------------------------------------------------------------------|-----|

| 3.3            | Outline of CPU Instruction Set                                              | 60  |

|                | 3.3.1 Load and store instructions                                           | 60  |

|                | 3.3.2 Computational instructions                                            |     |

|                | 3.3.3 Jump and branch instructions                                          |     |

|                | 3.3.4 Special instructions                                                  |     |

|                | 3.3.5 Coprocessor instructions                                              |     |

|                | 3.3.6 System control coprocessor (CP0) instructions                         |     |

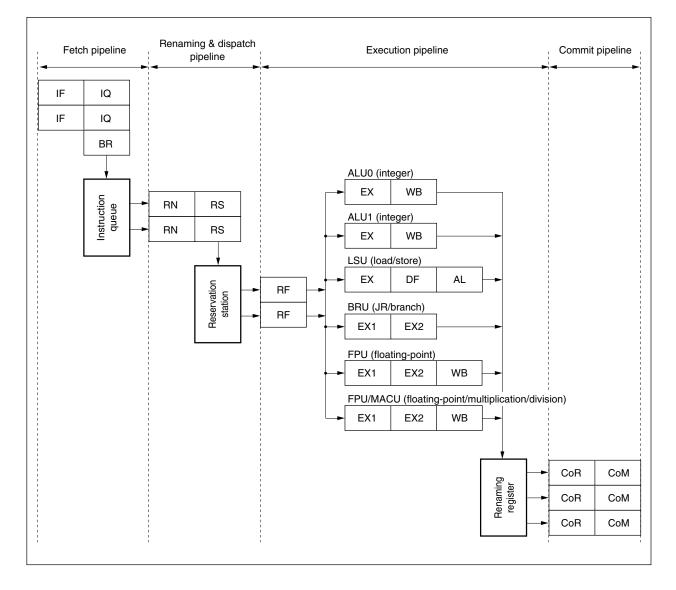

| СНАРТІ         | ER 4 PIPELINE                                                               |     |

| 4.1            | Overview                                                                    |     |

|                | 4.1.1 Pipeline stages                                                       |     |

|                | 4.1.2 Configuration of pipeline                                             |     |

| 4.2            | Branch Delay                                                                |     |

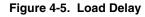

| 4.3            | Load Delay                                                                  |     |

|                | 4.3.1 Non-blocking load                                                     |     |

| 4.4            | Exception Processing                                                        |     |

| 4.5            | Store Buffer                                                                |     |

| 4.6            | Write Transaction Buffer                                                    |     |

|                |                                                                             |     |

| СПАР II<br>5.1 | ER 5 MEMORY MANAGEMENT SYSTEM                                               |     |

| 5.1            | Processor Modes                                                             |     |

|                | <ul><li>5.1.1 Operating modes</li><li>5.1.2 Instruction set modes</li></ul> |     |

|                | 5.1.2 Instruction set modes                                                 |     |

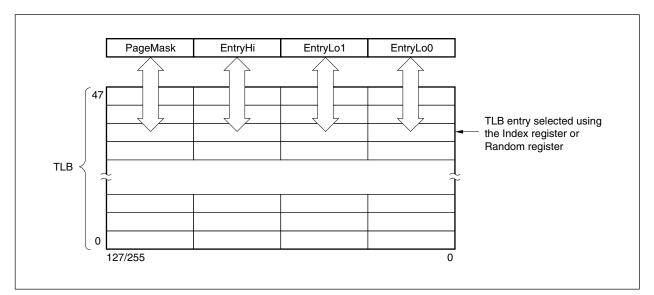

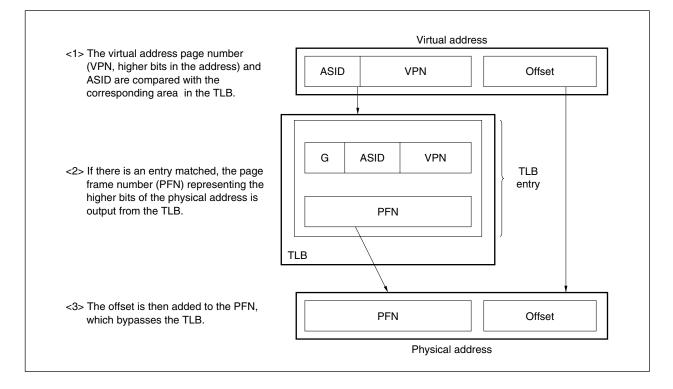

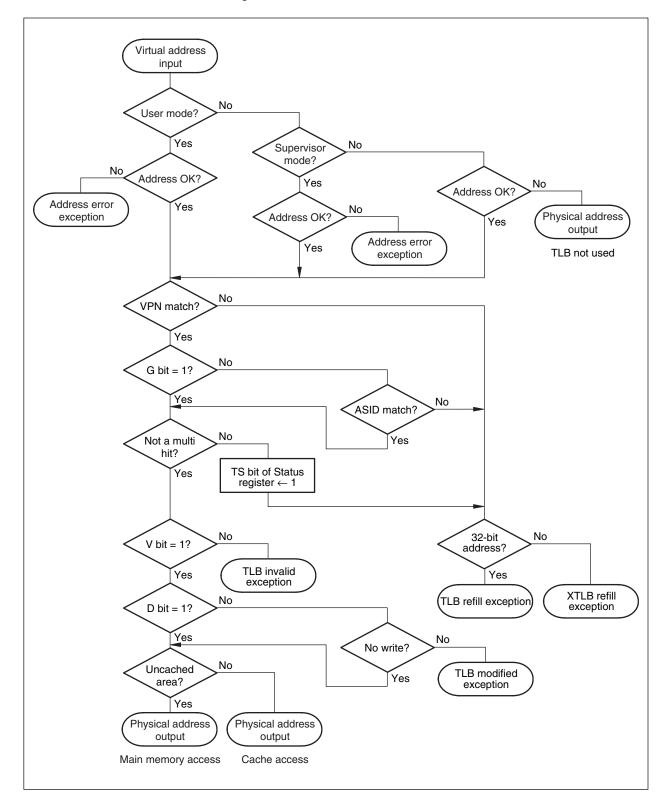

| 5.2            | Translation Lookaside Buffer (TLB)                                          |     |

| 5.2            | 5.2.1 Format of TLB entry.                                                  |     |

|                | 5.2.2 TLB instructions                                                      |     |

|                | 5.2.3 TLB exception                                                         |     |

| 5.3            | Virtual-to-Physical Address Translation                                     |     |

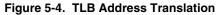

| 0.0            | 5.3.1 32-bit addressing mode address translation                            |     |

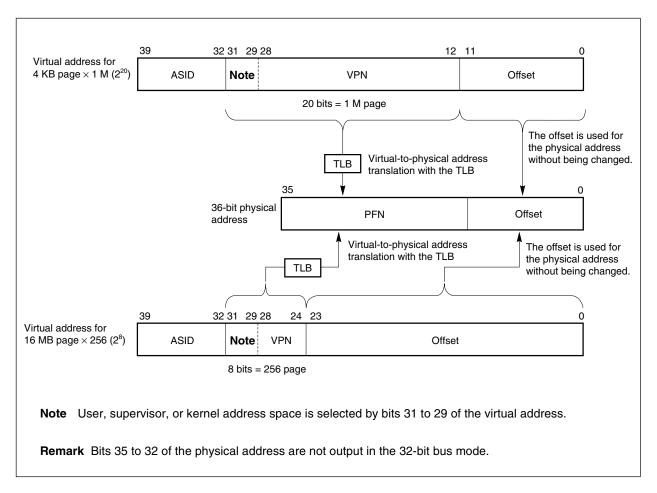

|                | 5.3.2 64-bit addressing mode address translation                            |     |

| 5.4            | Virtual Address Space                                                       |     |

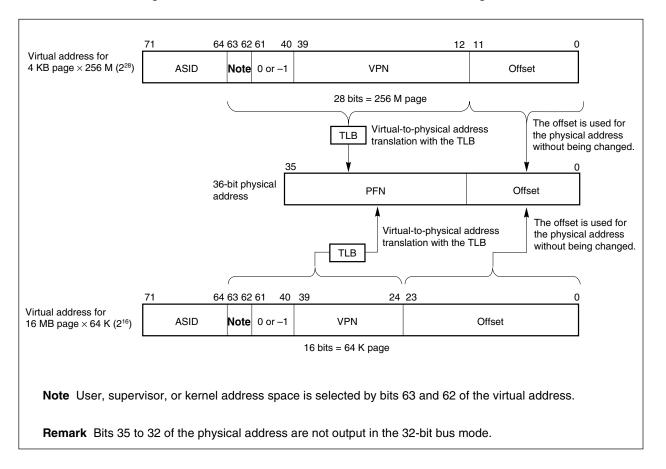

|                | 5.4.1 User mode virtual address space                                       |     |

|                | 5.4.2 Supervisor mode virtual address space                                 |     |

|                | 5.4.3 Kernel mode virtual address space                                     |     |

| 5.5            | Memory Management Registers                                                 |     |

|                | 5.5.1 Index register (0)                                                    |     |

|                | 5.5.2 Random register (1)                                                   |     |

|                | 5.5.3 EntryLo0 (2) and EntryLo1 (3) registers                               |     |

|                | 5.5.4 PageMask register (5)                                                 |     |

|                | 5.5.5 Wired register (6)                                                    |     |

|                | 5.5.6 EntryHi register (10)                                                 | 117 |

|                | 5.5.7 PRId (processor revision ID) register (15)                            |     |

|                | 5.5.8 Config register (16)                                                  | 118 |

|                | 5.5.9 LLAddr (load linked address) register (17)                            |     |

|                | 5.5.10 TagLo (28) and TagHi (29) registers                                  | 122 |

| СНАРТЕ | R 6 I  | EXCEPTION PROCESSING1                           | 123 |

|--------|--------|-------------------------------------------------|-----|

| 6.1    | Excep  | tion Processing Operation1                      | 123 |

| 6.2    | Excep  | tion Processing Registers1                      | 124 |

|        | 6.2.1  | Context register (4)                            | 125 |

|        | 6.2.2  | BadVAddr register (8)                           | 126 |

|        | 6.2.3  | Count register (9)                              | 127 |

|        | 6.2.4  | Compare register (11)                           | 127 |

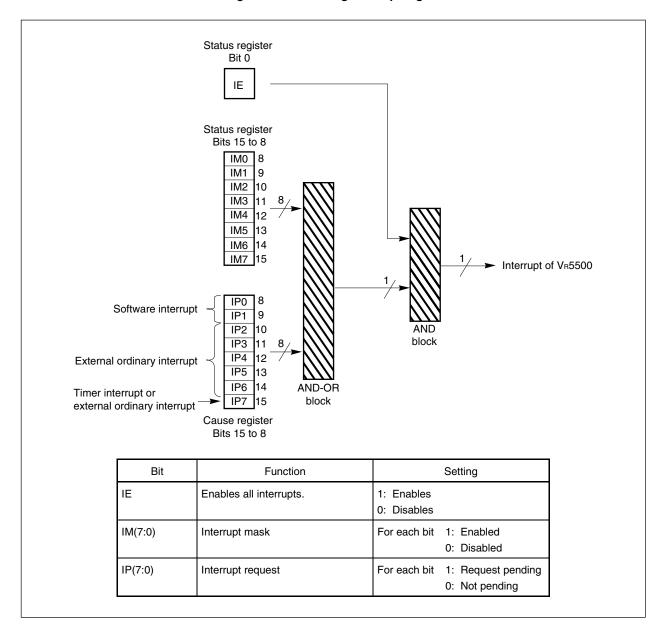

|        | 6.2.5  | Status register (12)                            | 128 |

|        | 6.2.6  | Cause register (13)                             | 131 |

|        | 6.2.7  | EPC (exception program counter) register (14)   | 133 |

|        | 6.2.8  | WatchLo (18) and WatchHi (19) registers         |     |

|        | 6.2.9  | XContext register (20)                          | 135 |

|        |        | Performance Counter register (25)               |     |

|        | 6.2.11 | Parity Error register (26)                      | 138 |

|        | 6.2.12 | Cache Error register (27)                       | 139 |

|        | 6.2.13 | ErrorEPC register (30)                          | 140 |

| 6.3    | Detail | s of Exceptions1                                | 141 |

|        | 6.3.1  | Exception types                                 | 141 |

|        | 6.3.2  | Exception vector address                        |     |

|        | 6.3.3  | Priority of exceptions                          | 146 |

| 6.4    | Detail | s of Exceptions1                                | 147 |

|        | 6.4.1  | Reset exception                                 | 147 |

|        | 6.4.2  | Soft reset exception                            | 148 |

|        | 6.4.3  | NMI exception                                   | 149 |

|        | 6.4.4  | Address error exception                         |     |

|        | 6.4.5  | TLB exceptions                                  |     |

|        | 6.4.6  | Cache error exception                           | 155 |

|        | 6.4.7  | Bus error exception                             |     |

|        | 6.4.8  | System call exception                           | 157 |

|        | 6.4.9  | Breakpoint exception                            |     |

|        |        | Coprocessor unusable exception                  |     |

|        |        | Reserved instruction exception                  |     |

|        | 6.4.12 | Trap exception                                  | 159 |

|        |        | Integer overflow exception                      |     |

|        |        | Floating-point operation exception              |     |

|        |        | Watch exception                                 |     |

|        |        | Interrupt exception                             |     |

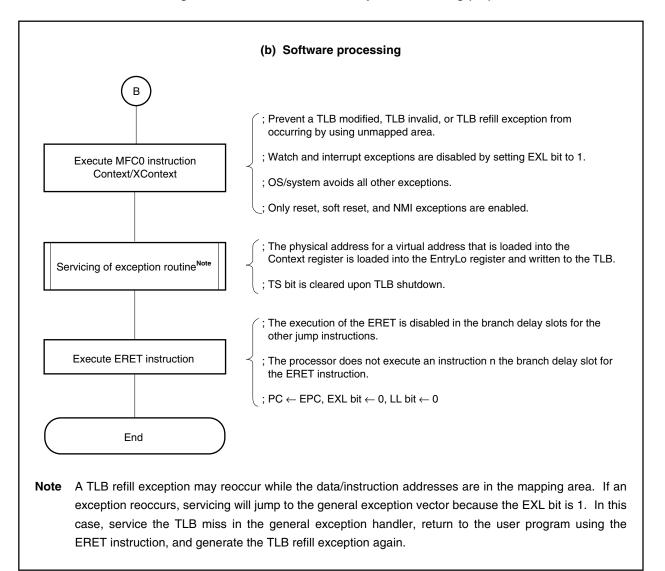

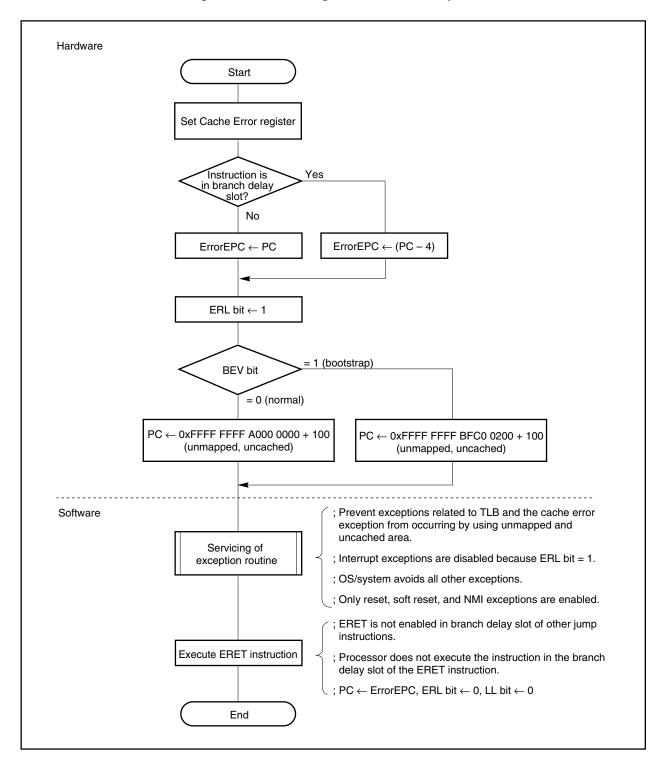

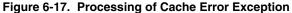

| 6.5    | Excep  | tion Processing Flowcharts1                     | 163 |

| СНАРТЕ | 87 E   | LOATING-POINT UNIT                              | 170 |

| 7.1    |        | iew1                                            |     |

| 7.1    |        | egisters1                                       |     |

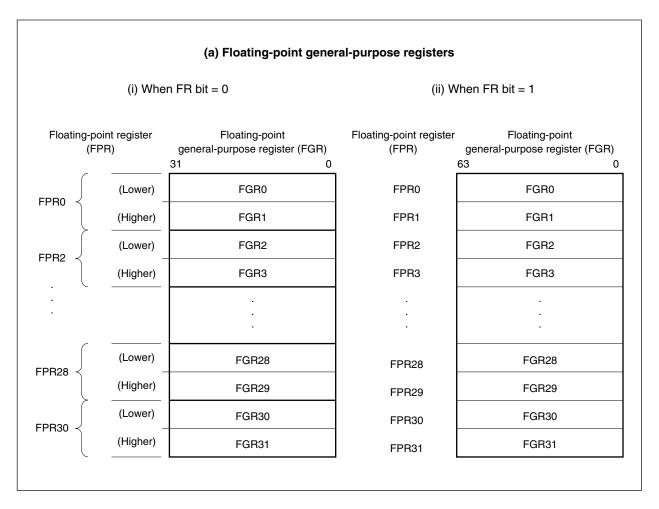

| 1.2    | 7.2.1  | Floating-point general-purpose registers (FGRs) |     |

|        | 7.2.1  | Floating-point general-purpose registers (FGRS) |     |

|        | 7.2.2  | Floating-point registers (FPRs)                 |     |

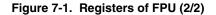

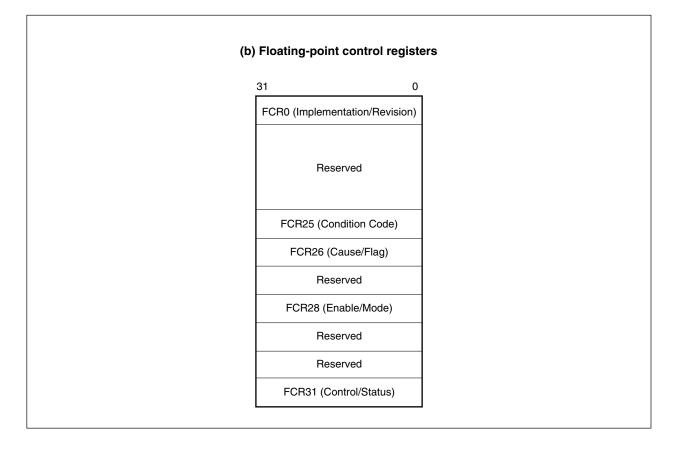

| 7.3    | -      | ng-Point Control Register1                      |     |

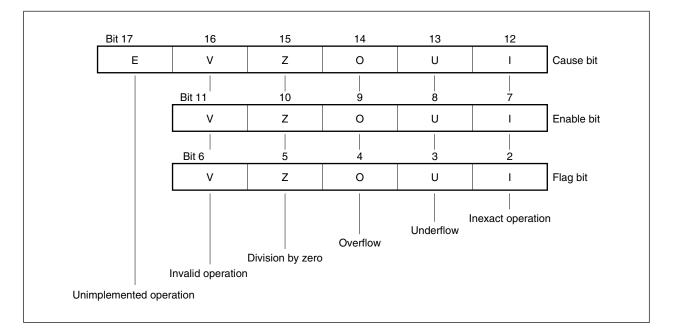

| 7.5    | 7.3.1  | Control/Status register (FCR31)                 |     |

|        | 7.3.1  | Enable/Mode register (FCR28)                    |     |

|        | 1.0.2  |                                                 | 110 |

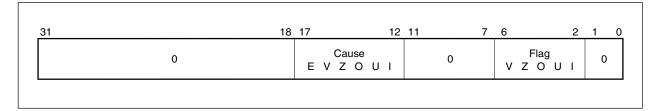

|       | 7.3.3  | Cause/Flag register (FCR26)                     | 176 |

|-------|--------|-------------------------------------------------|-----|

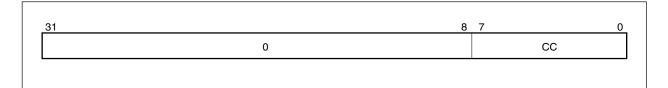

|       | 7.3.4  | Condition Code register (FCR25)                 | 176 |

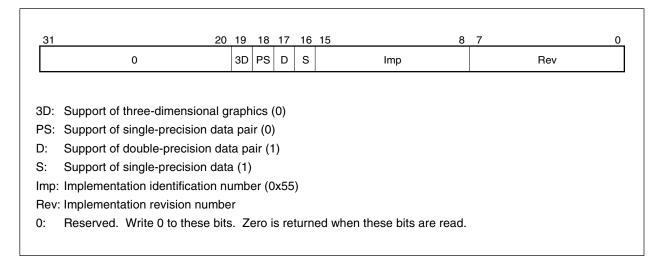

|       | 7.3.5  | Implementation/Revision register (FCR0)         | 177 |

| 7.4   | Data   | Format                                          |     |

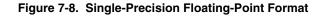

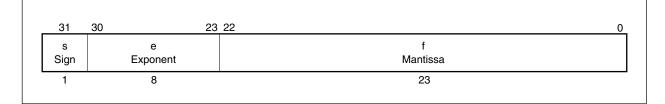

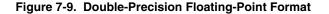

|       | 7.4.1  | Floating-point format                           | 178 |

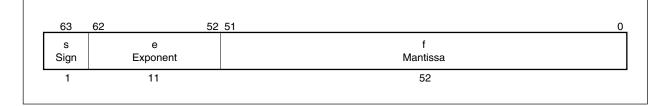

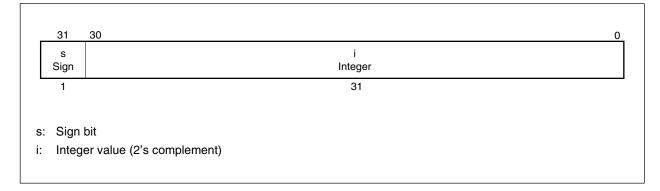

|       | 7.4.2  | Fixed-point format                              | 180 |

| 7.5   | Outli  | ne of FPU Instruction Set                       |     |

|       | 7.5.1  | Floating-point load/store/transfer instructions |     |

|       | 7.5.2  | Conversion instructions                         | 185 |

|       | 7.5.3  | Operation instructions                          | 187 |

|       | 7.5.4  | Comparison instruction                          | 189 |

|       | 7.5.5  | FPU branch instructions                         | 190 |

|       | 7.5.6  | Other instructions                              | 190 |

| 7.6   | Exec   | ution Time of FPU Instruction                   |     |

| CHAPT | ER 8   | FLOATING-POINT EXCEPTIONS                       |     |

| 8.1   |        | s of Exceptions                                 |     |

| 8.2   | •••    | ption Processing                                |     |

|       | 8.2.1  |                                                 |     |

| 8.3   | Detai  | Is of Exceptions                                |     |

|       | 8.3.1  | Inexact operation exception (I)                 |     |

|       | 8.3.2  | Invalid operation exception (V)                 |     |

|       | 8.3.3  | Division-by-zero exception (Z)                  |     |

|       | 8.3.4  | Overflow exception (O)                          |     |

|       | 8.3.5  | Underflow exception (U)                         |     |

|       | 8.3.6  | Unimplemented operation exception (E)           |     |

| 8.4   | Savir  | ng and Restoring Status                         |     |

| 8.5   | Hand   | ler for IEEE754 Exceptions                      |     |

| СНАРТ | ER 9   | NITIALIZATION INTERFACE                         |     |

| 9.1   |        | tional Outline                                  |     |

| 9.2   |        | t Sequence                                      |     |

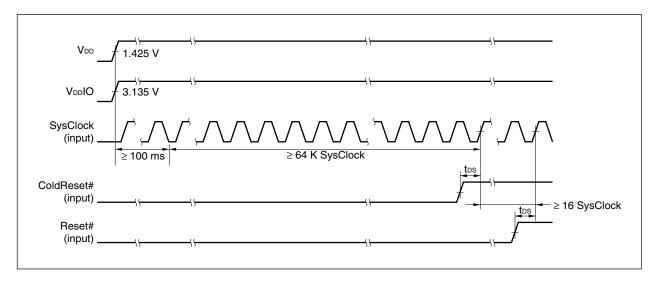

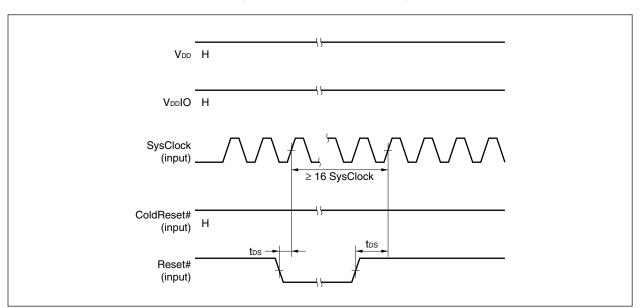

| •     | 9.2.1  | Power-on reset                                  |     |

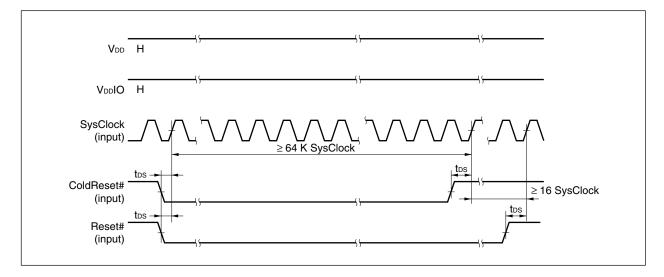

|       | 9.2.2  | Cold reset                                      |     |

|       | 9.2.3  | Warm reset                                      |     |

|       | 9.2.4  | Processor status at reset                       |     |

| 9.3   | Initia | lization Signals                                |     |

| СНАРТ | ER 10  | CLOCK INTERFACE                                 |     |

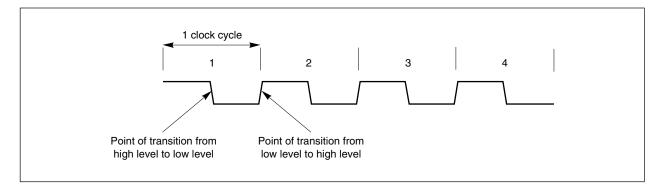

|       |        | Definitions                                     |     |

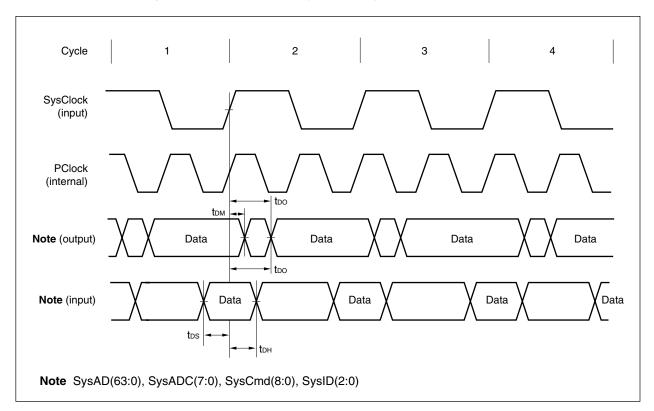

|       |        | System Clock                                    |     |

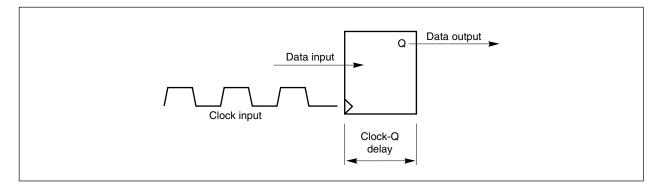

|       |        | Synchronization with SysClock                   |     |

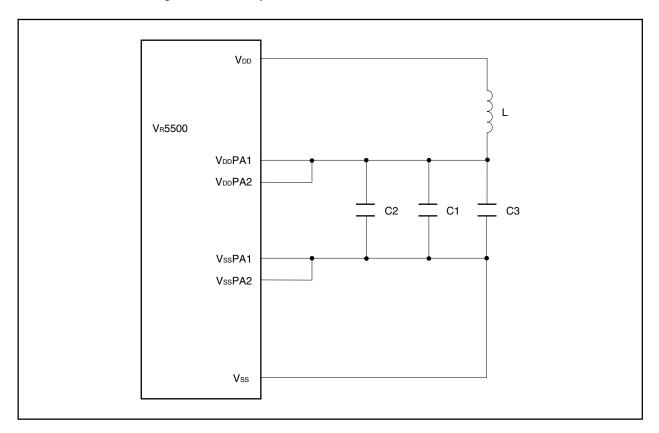

| 10.3  |        | e Lock Loop (PLL)                               |     |

| СНАРТ | ER 11  | CACHE MEMORY                                    | 209 |

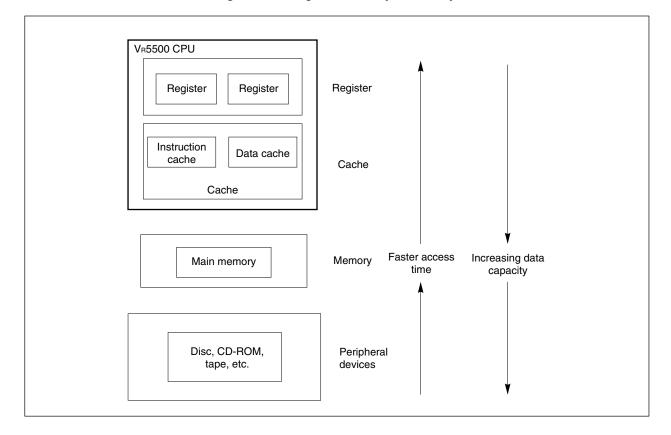

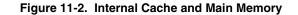

|       |        | ory Organization                                |     |

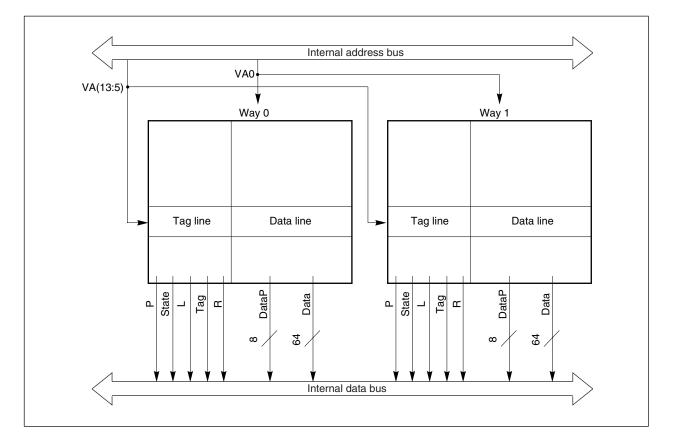

|       |        | Internal cache                                  |     |

| 11 2  |        | guration of Cache                               |     |

|       |        |                                                 |     |

|        | 11.2.1 Configuration of instruction cache         | .211  |

|--------|---------------------------------------------------|-------|

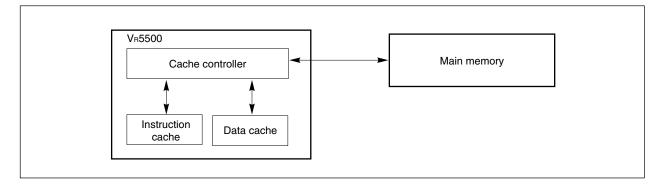

|        | 11.2.2 Configuration of data cache                | .212  |

|        | 11.2.3 Location of data cache                     | .212  |

| 11.3   | Cache Operations                                  | 213   |

|        | 11.3.1 Coherency of cache data                    | .213  |

|        | 11.3.2 Replacing instruction cache line           | .214  |

|        | 11.3.3 Replacing data cache line                  | .214  |

|        | 11.3.4 Speculative replacement of data cache line | .215  |

|        | 11.3.5 Accessing cache                            | .216  |

| 11.4   | Status of Cache                                   | 217   |

| 11.5   | Manipulating Cache by External Agent              | 217   |

|        |                                                   |       |

| СНАРТЕ | R 12 OVERVIEW OF SYSTEM INTERFACE                 | 218   |

| 12.1   | Definition of Terms                               | 218   |

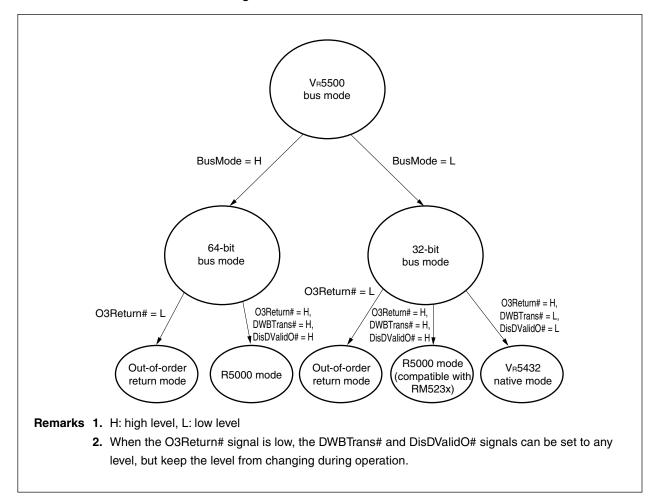

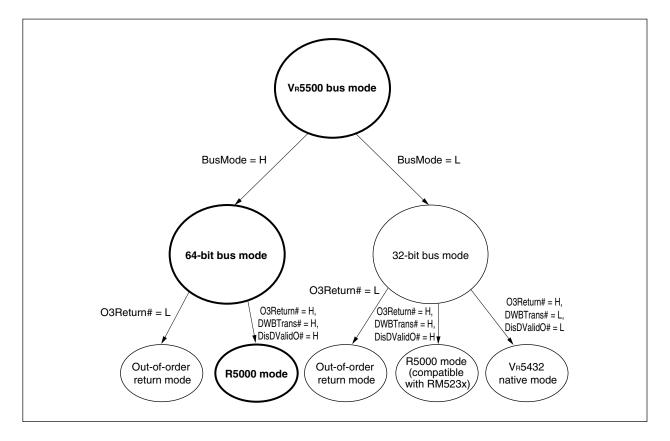

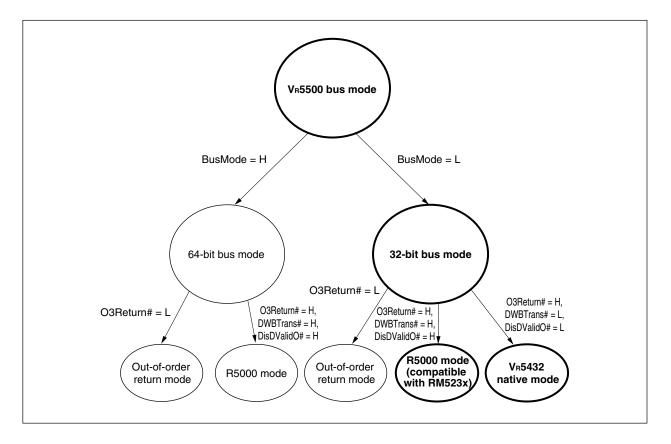

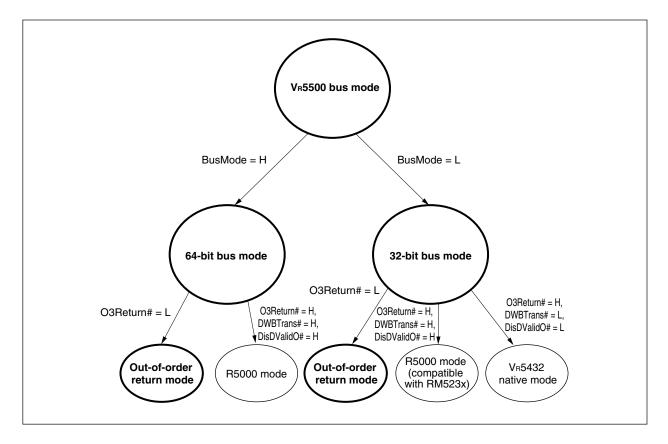

| 12.2   | Bus Modes                                         | 219   |

| 12.3   | Outline of System Interface                       | 220   |

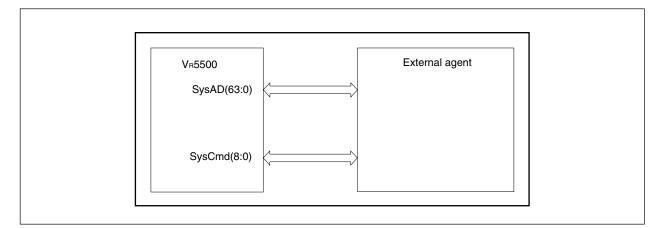

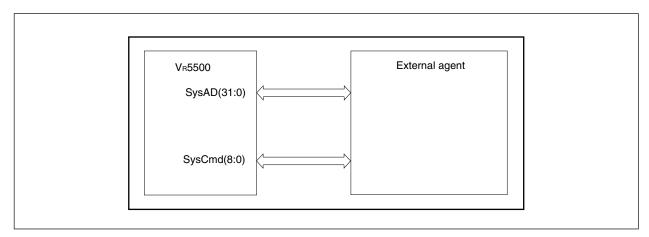

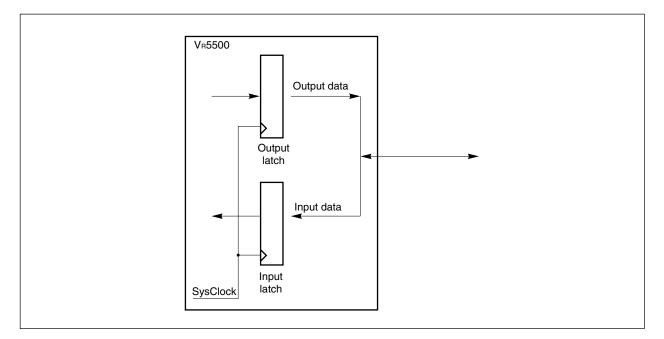

|        | 12.3.1 Interface bus                              | . 220 |

|        | 12.3.2 Address cycle and data cycle               | . 221 |

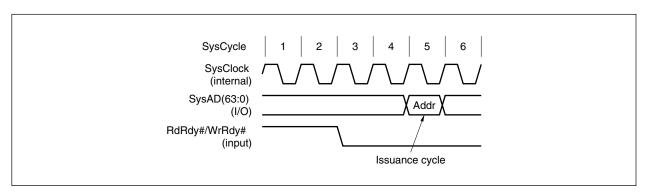

|        | 12.3.3 Issuance cycle                             | .221  |

|        | 12.3.4 Handshake signal                           | . 222 |

|        | 12.3.5 System interface bus data                  | . 223 |

| 12.4   | System Interface Protocol                         | 224   |

|        | 12.4.1 Master status and slave status             | . 224 |

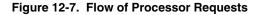

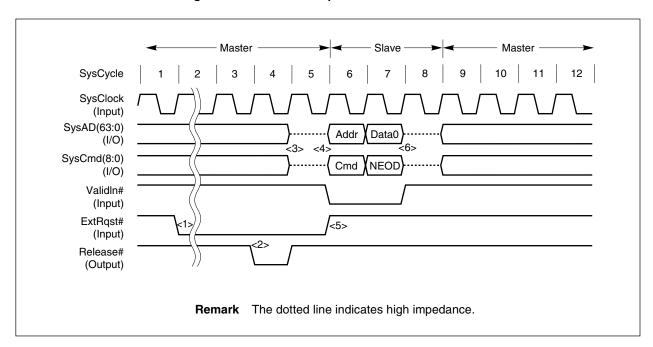

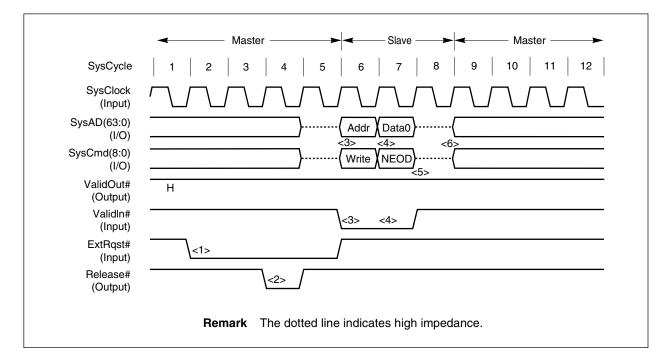

|        | 12.4.2 External arbitration                       | . 225 |

|        | 12.4.3 Uncompelled transition to slave status     | . 225 |

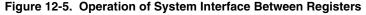

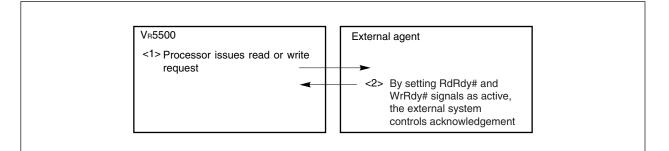

|        | 12.4.4 Processor requests and external requests   | . 226 |

| 12.5   | Processor Requests                                | 227   |

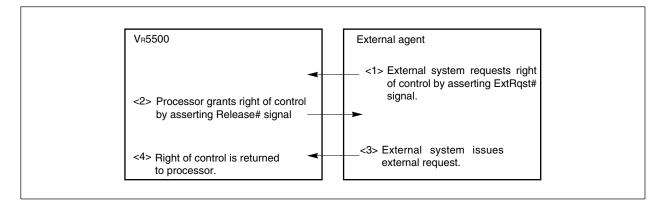

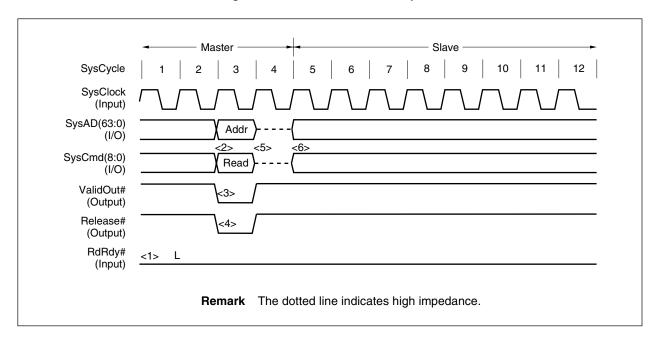

|        | 12.5.1 Processor read request                     | . 228 |

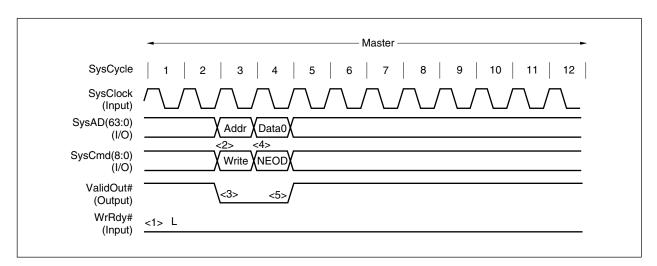

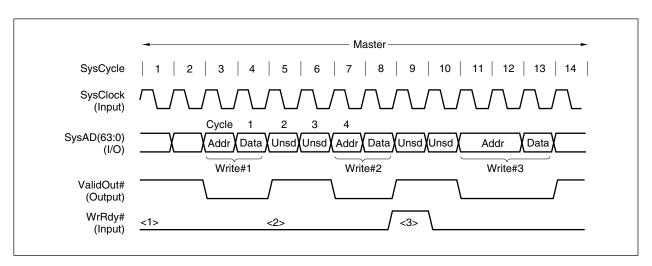

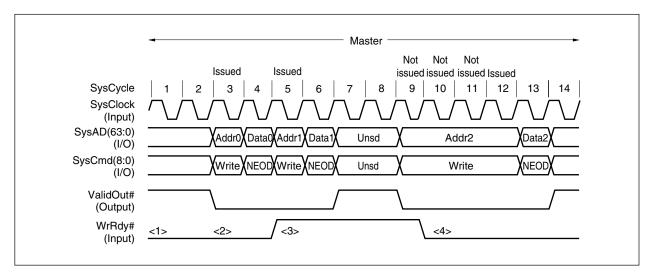

|        | 12.5.2 Processor write request                    | . 228 |

| 12.6   | External Requests                                 | 229   |

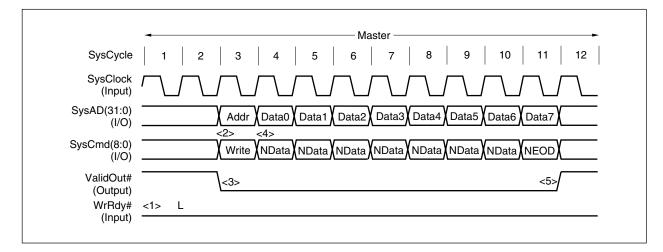

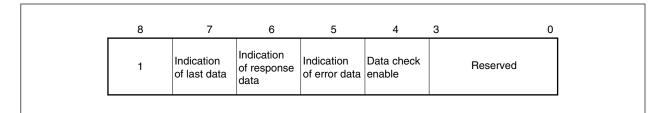

|        | 12.6.1 External write request                     | . 230 |

|        | 12.6.2 Read response                              | . 230 |

| 12.7   | Event Processing                                  | 231   |

|        | 12.7.1 Load miss                                  | . 231 |

|        | 12.7.2 Store miss                                 | . 232 |

|        | 12.7.3 Store hit                                  | . 232 |

|        | 12.7.4 Load/store in uncached area                | . 232 |

|        | 12.7.5 Accelerated store in uncached area         | . 232 |

|        | 12.7.6 Instruction fetch from uncached area       | . 233 |

|        | 12.7.7 Fetch miss                                 | . 233 |

| 12.8   | Error Check Function                              | 234   |

|        | 12.8.1 Parity error check                         | .234  |

|        | 12.8.2 Error check operation                      | .235  |

|        |                                                   |       |

|        | R 13 SYSTEM INTERFACE (64-BIT BUS MODE)           |       |

| 13.1   | Protocol of Processor Requests                    | 238   |

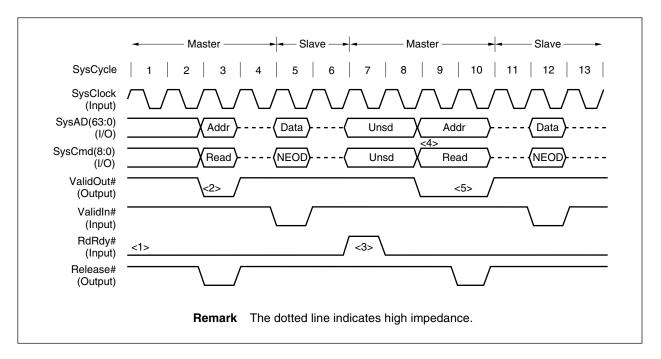

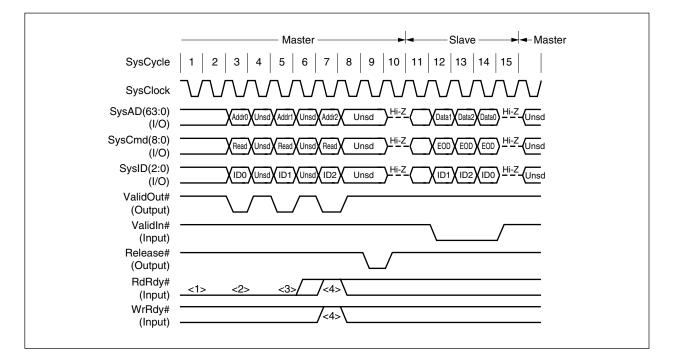

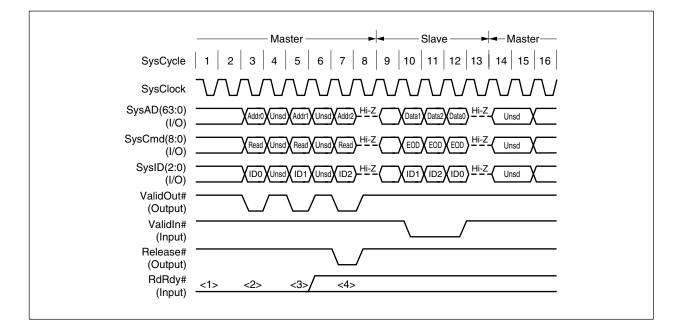

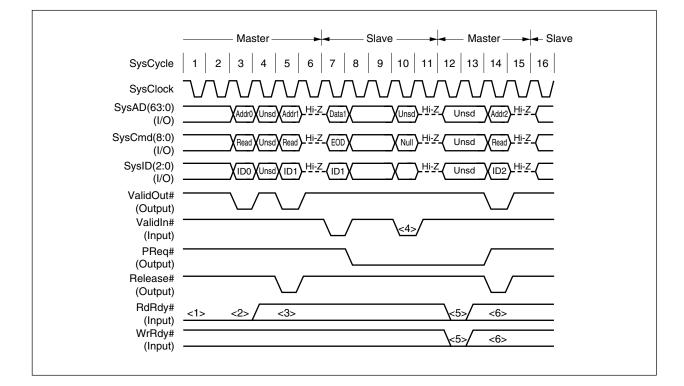

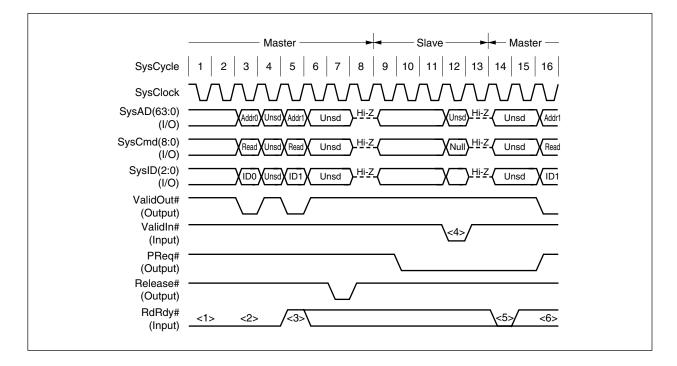

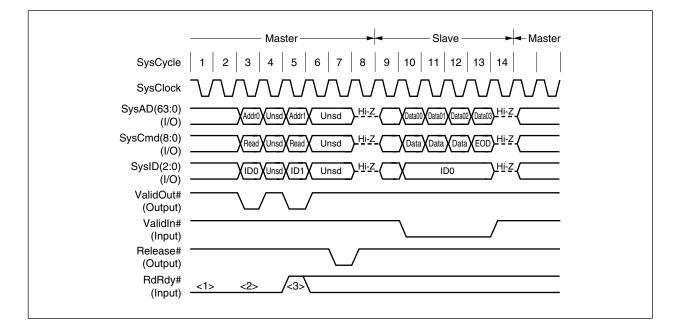

|        | 13.1.1 Processor read request protocol            | .238  |

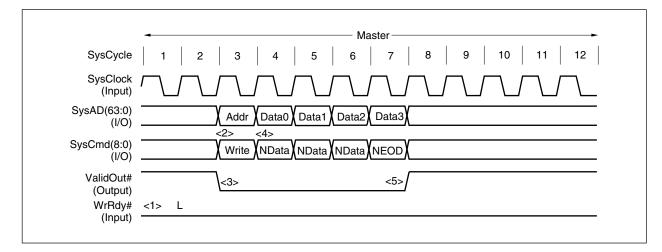

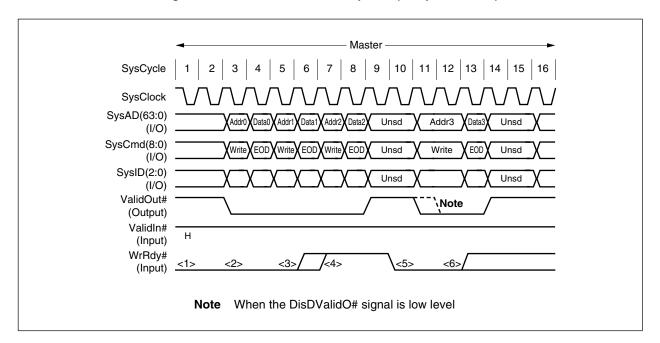

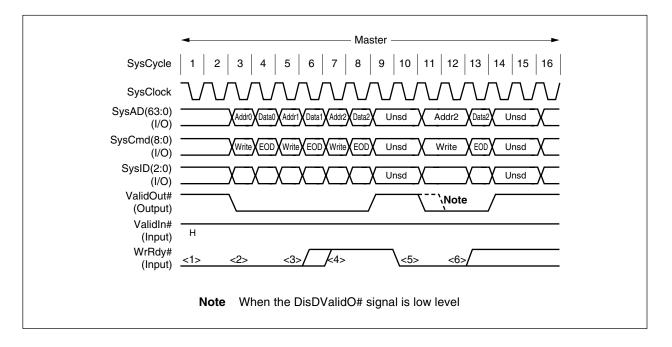

|        | 13.1.2 Processor write request protocol           | .239  |

|        |                                                   |       |

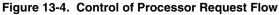

|    |                              | 13.1.3 Control of processor request flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 241                                                                                                                                             |

|----|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                              | 13.1.4 Timing mode of processor request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 242                                                                                                                                             |

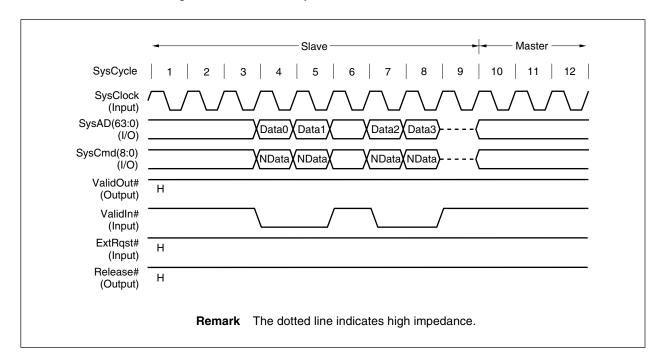

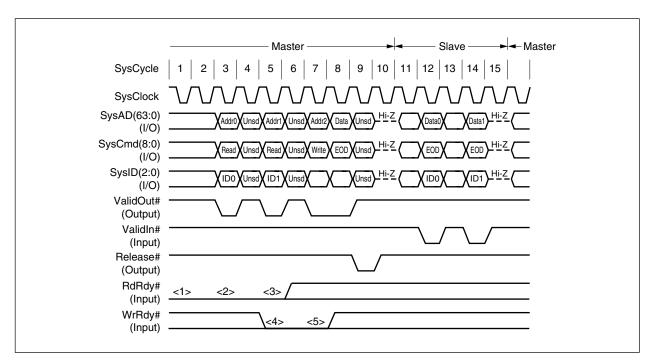

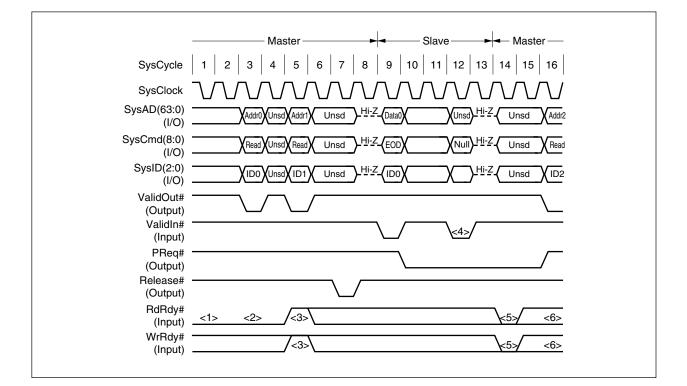

|    | 13.2                         | Protocol of External Request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 246                                                                                                                                             |

|    |                              | 13.2.1 External arbitration protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 246                                                                                                                                             |

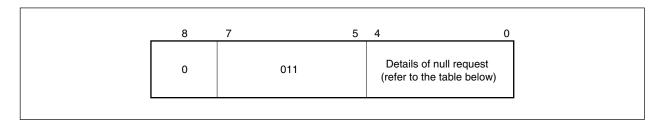

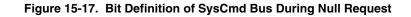

|    |                              | 13.2.2 External null request protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 248                                                                                                                                             |

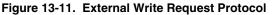

|    |                              | 13.2.3 External write request protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 249                                                                                                                                             |

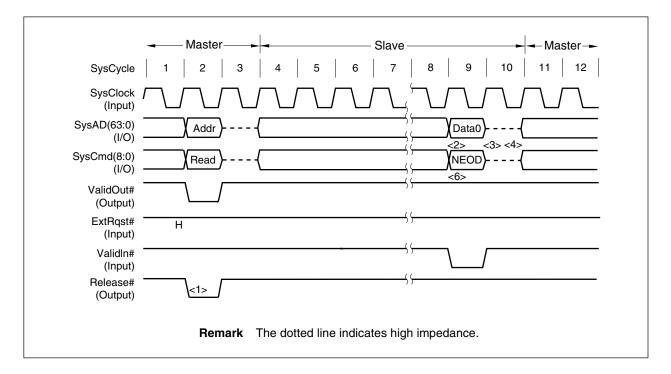

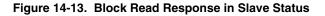

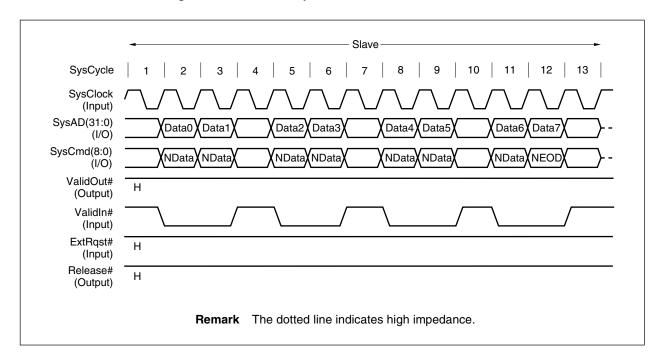

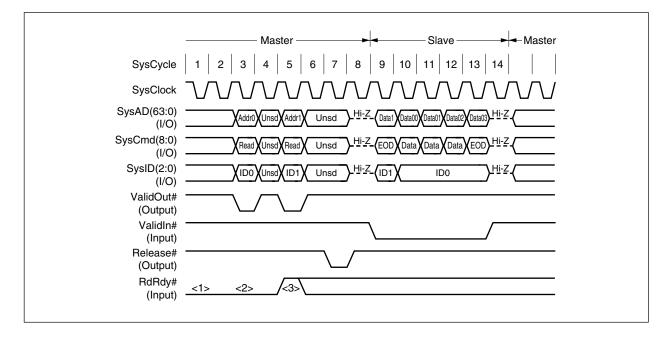

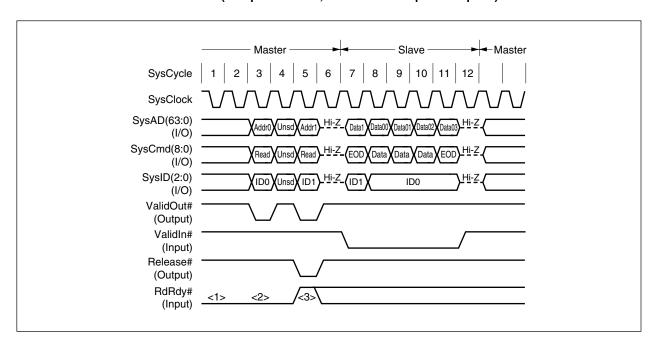

|    |                              | 13.2.4 Read response protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 250                                                                                                                                             |

|    |                              | 13.2.5 SysADC(7:0) protocol for block read response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 252                                                                                                                                             |

|    | 13.3                         | Data Flow Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 252                                                                                                                                             |

|    |                              | 13.3.1 Data rate control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 252                                                                                                                                             |

|    |                              | 13.3.2 Block write data transfer pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 253                                                                                                                                             |

|    |                              | 13.3.3 System endianness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 253                                                                                                                                             |

|    | 13.4                         | Independent Transfer with SysAD Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 254                                                                                                                                             |

|    | 13.5                         | System Interface Cycle Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 254                                                                                                                                             |

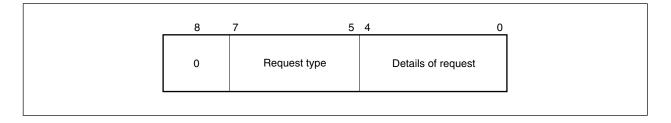

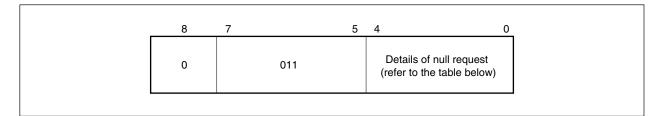

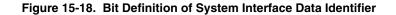

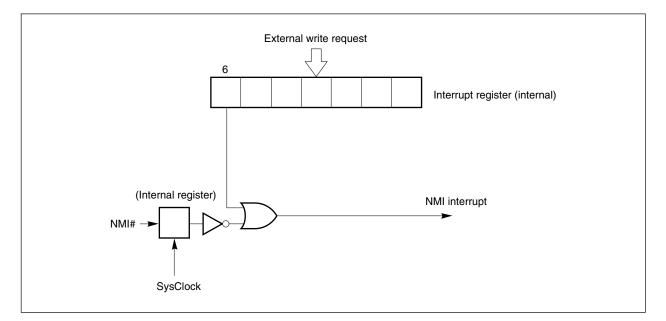

|    | 13.6                         | System Interface Commands and Data Identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 255                                                                                                                                             |

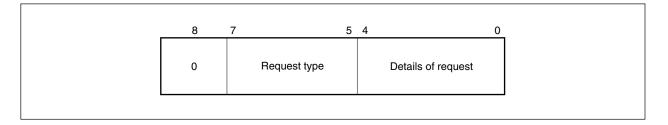

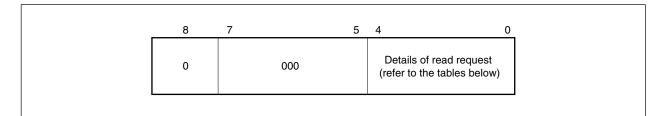

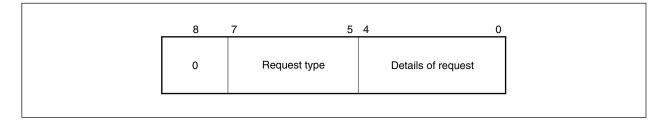

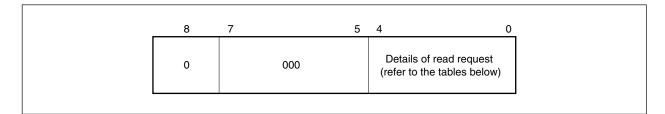

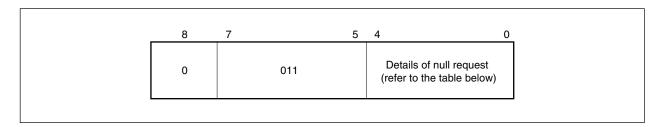

|    |                              | 13.6.1 Syntax of commands and data identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 255                                                                                                                                             |

|    |                              | 13.6.2 Syntax of command                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 255                                                                                                                                             |

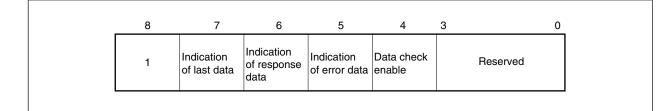

|    |                              | 13.6.3 Syntax of data identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 258                                                                                                                                             |

|    | 13.7                         | System Interface Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 260                                                                                                                                             |

|    |                              | 13.7.1 Address specification rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 260                                                                                                                                             |

|    |                              | 13.7.2 Sub-block ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 260                                                                                                                                             |

|    |                              | 13.7.3 Processor internal address map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 260                                                                                                                                             |

| СН |                              | R 14 SYSTEM INTERFACE (32-BIT BUS MODE)<br>Protocol of Processor Requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                 |

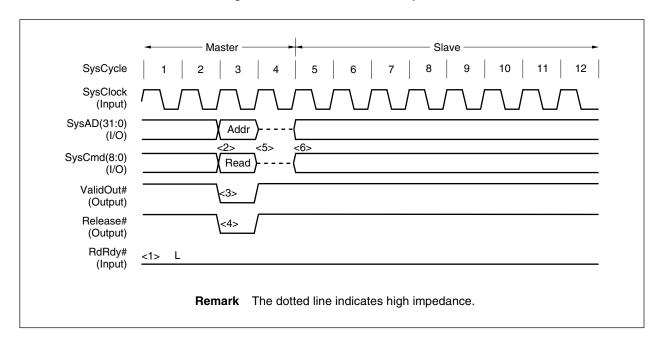

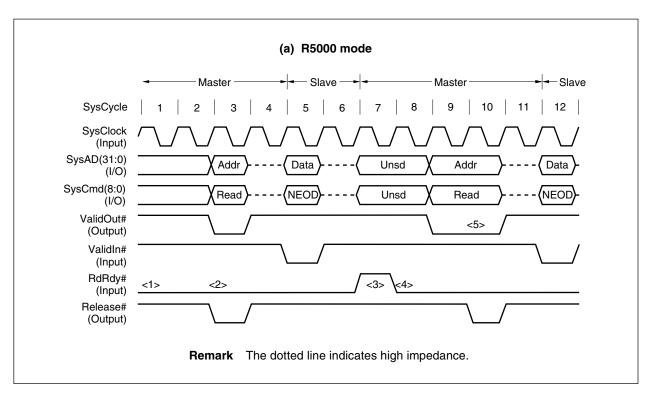

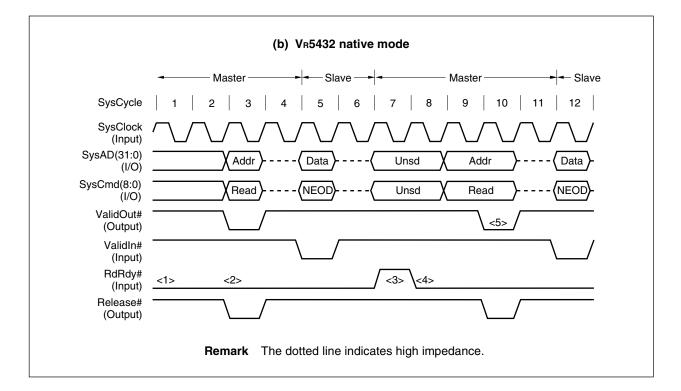

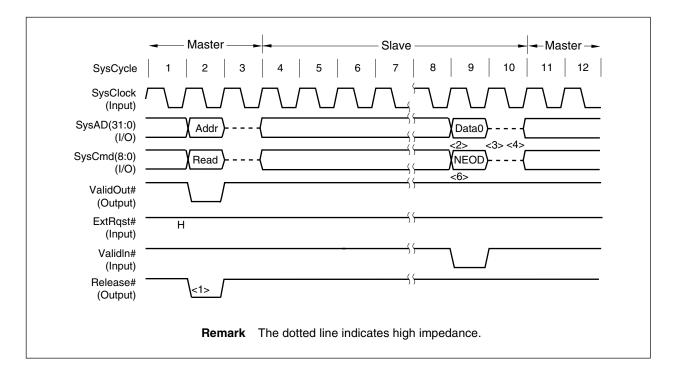

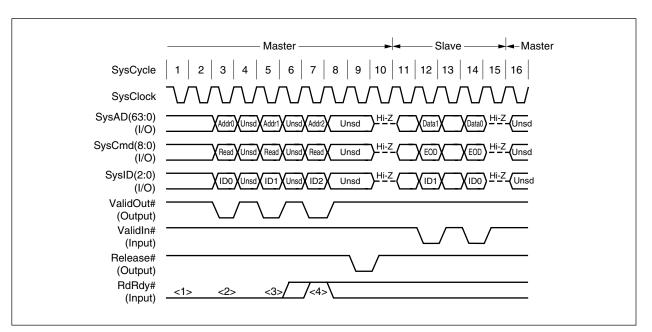

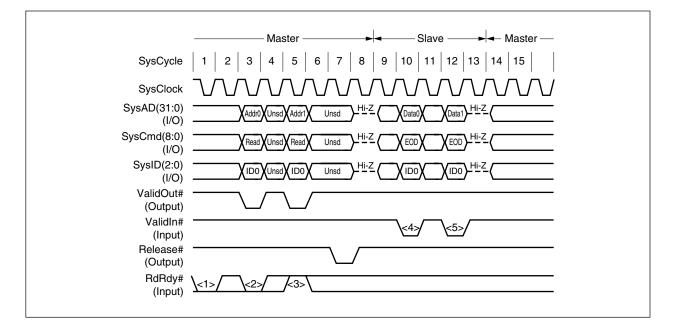

|    | 14.1                         | 14.1.1 Processor read request protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

|    |                              | 14.1.1 Flocessol lead lequest protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

|    |                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |

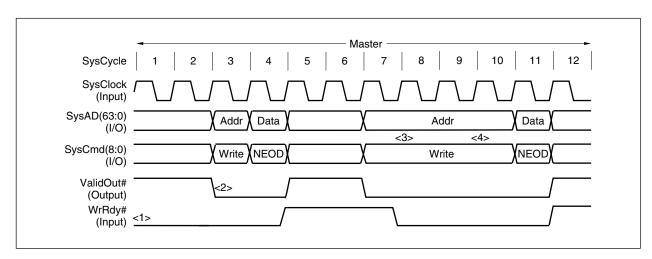

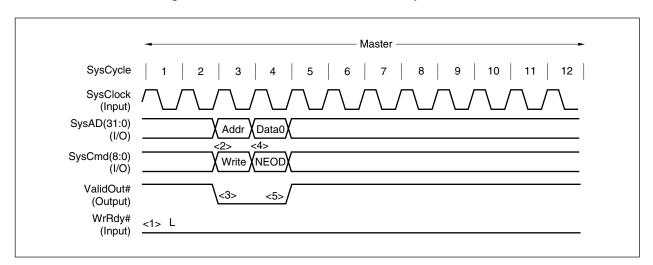

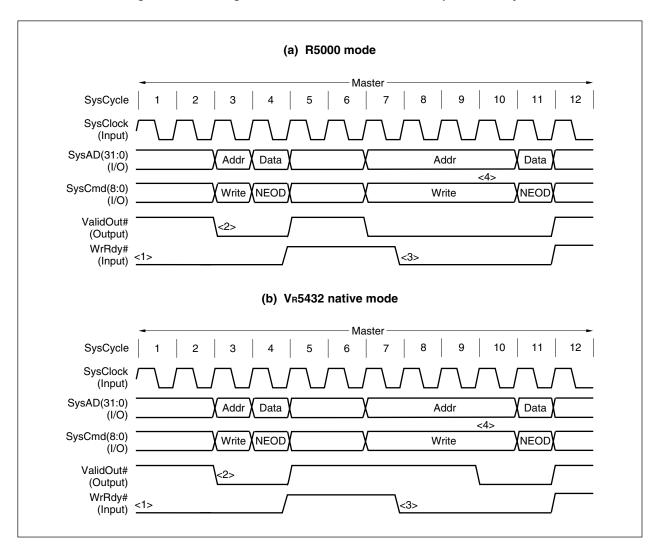

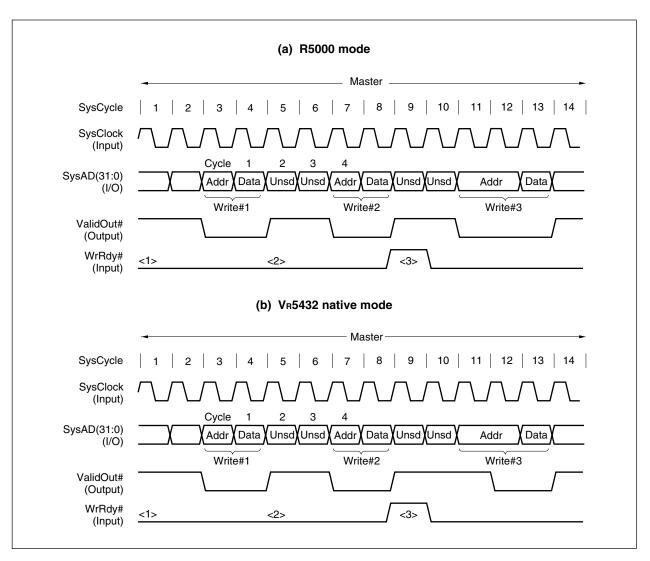

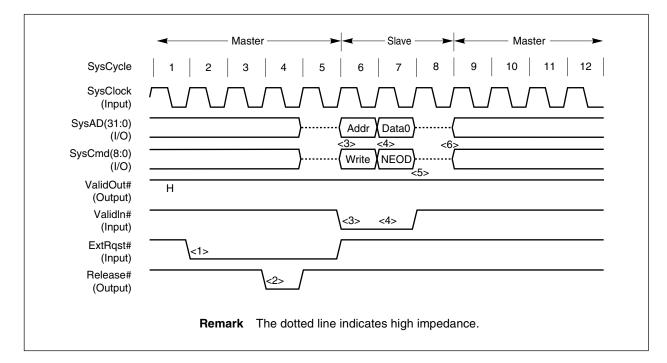

|    |                              | 14.1.2 Processor write request protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 263                                                                                                                                             |

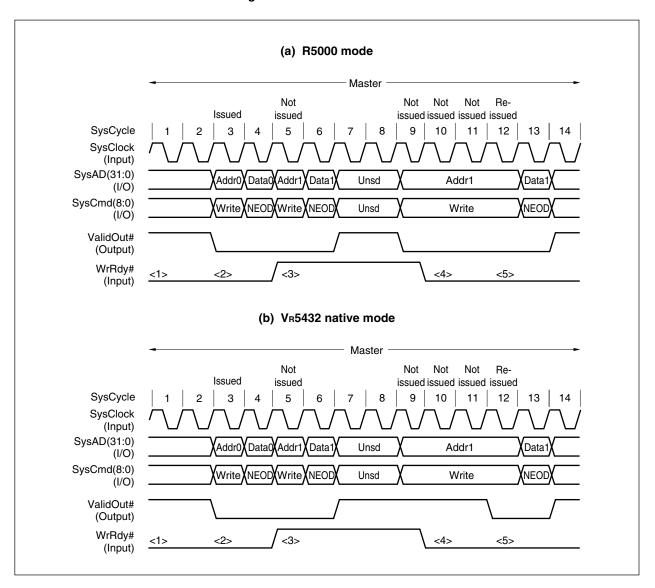

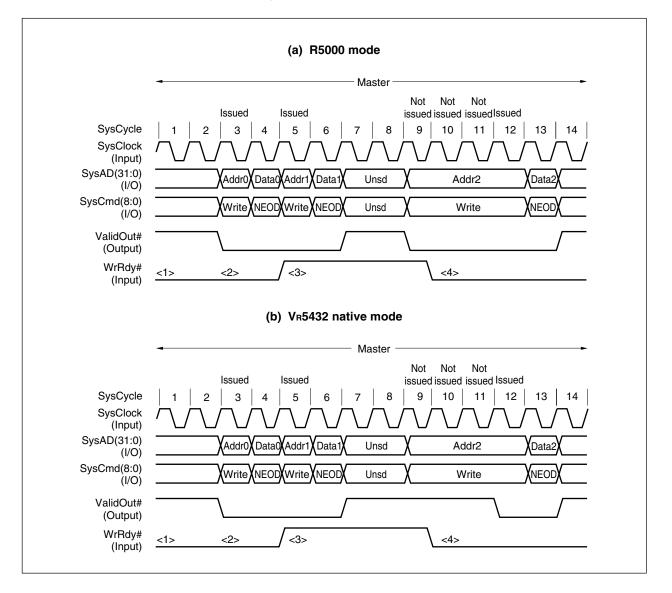

|    |                              | 14.1.2 Processor write request protocol         14.1.3 Control of processor request flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 263<br>265                                                                                                                                      |

|    | 14.0                         | <ul><li>14.1.2 Processor write request protocol</li><li>14.1.3 Control of processor request flow</li><li>14.1.4 Timing mode of processor request</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 263<br>265<br>267                                                                                                                               |

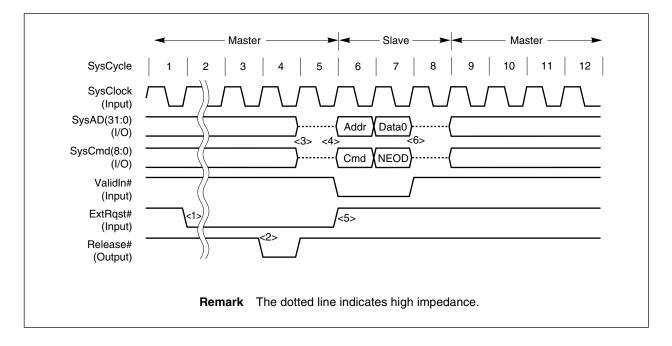

|    | 14.2                         | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 263<br>265<br>267<br><b>271</b>                                                                                                                 |

|    | 14.2                         | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 263<br>265<br>267<br><b>271</b><br>271                                                                                                          |

|    | 14.2                         | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 263<br>265<br>267<br><b>271</b><br>271<br>273                                                                                                   |

|    | 14.2                         | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 263<br>265<br>267<br><b>271</b><br>271<br>273<br>274                                                                                            |

|    | 14.2                         | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> <li>14.2.4 Read response protocol</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                       | 263<br>265<br>267<br><b>271</b><br>271<br>273<br>274<br>275                                                                                     |

|    |                              | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> <li>14.2.4 Read response protocol</li> <li>14.2.5 SysADC(3:0) protocol for block read response</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          | 263<br>265<br>267<br><b>271</b><br>271<br>273<br>274<br>275<br>277                                                                              |

|    |                              | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> <li>14.2.4 Read response protocol</li> <li>14.2.5 SysADC(3:0) protocol for block read response</li> <li>Data Flow Control</li> </ul>                                                                                                                                                                                                                                                                                                                                               | 263<br>265<br>267<br>271<br>271<br>273<br>274<br>275<br>277<br><b>277</b>                                                                       |

|    |                              | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> <li>14.2.4 Read response protocol</li> <li>14.2.5 SysADC(3:0) protocol for block read response</li> <li>Data Flow Control</li> <li>14.3.1 Data rate control</li> </ul>                                                                                                                                                                                                                                                                                                             | 263<br>265<br>267<br>271<br>271<br>273<br>274<br>275<br>277<br>277<br>277                                                                       |

|    |                              | <ul> <li>14.1.2 Processor write request protocol</li> <li>14.1.3 Control of processor request flow</li> <li>14.1.4 Timing mode of processor request</li> <li>Protocol of External Request</li> <li>14.2.1 External arbitration protocol</li> <li>14.2.2 External null request protocol</li> <li>14.2.3 External write request protocol</li> <li>14.2.4 Read response protocol</li> <li>14.2.5 SysADC(3:0) protocol for block read response</li> <li>Data Flow Control</li> <li>14.3.1 Data rate control</li> <li>14.3.2 Block write data transfer pattern</li> </ul>                                                                                                                                                                                                                                                           | 263<br>265<br>267<br>271<br>271<br>273<br>274<br>275<br>277<br>277<br>277<br>278                                                                |

|    |                              | 14.1.2 Processor write request protocol         14.1.3 Control of processor request flow         14.1.4 Timing mode of processor request <b>Protocol of External Request</b> 14.2.1 External arbitration protocol         14.2.2 External null request protocol         14.2.3 External write request protocol         14.2.4 Read response protocol         14.2.5 SysADC(3:0) protocol for block read response <b>Data Flow Control</b> 14.3.1 Data rate control         14.3.3 Word transfer pattern                                                                                                                                                                                                                                                                                                                        | 263<br>265<br>267<br>271<br>273<br>274<br>275<br>277<br>277<br>277<br>277<br>278<br>279                                                         |

|    | 14.3                         | 14.1.2 Processor write request protocol         14.1.3 Control of processor request flow         14.1.4 Timing mode of processor request <b>Protocol of External Request</b> 14.2.1 External arbitration protocol         14.2.2 External null request protocol         14.2.3 External write request protocol         14.2.4 Read response protocol         14.2.5 SysADC(3:0) protocol for block read response <b>Data Flow Control</b> 14.3.1 Data rate control         14.3.3 Word transfer sequence         14.3.4 System endianness                                                                                                                                                                                                                                                                                      | 263<br>265<br>267<br>271<br>273<br>274<br>275<br>277<br>277<br>277<br>277<br>277<br>278<br>279<br>281                                           |

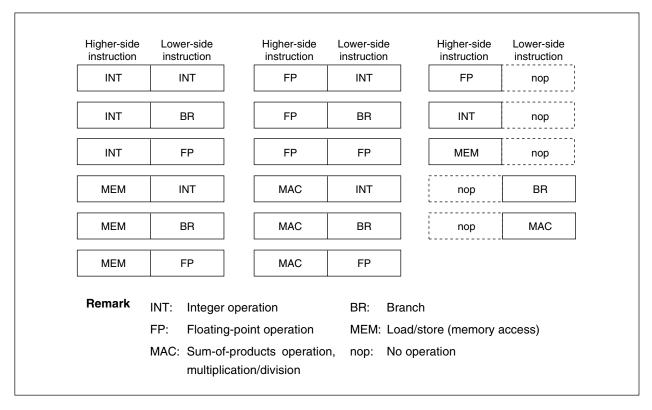

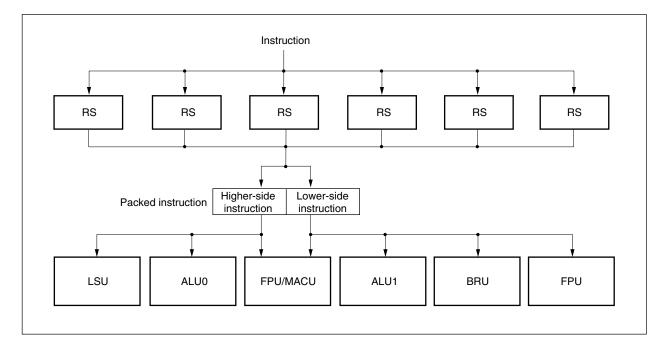

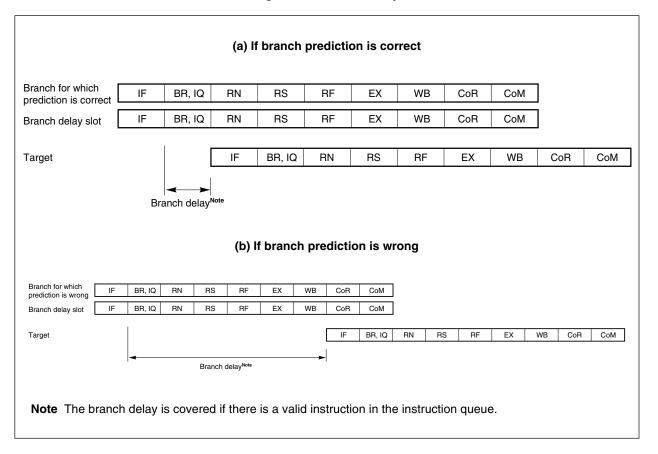

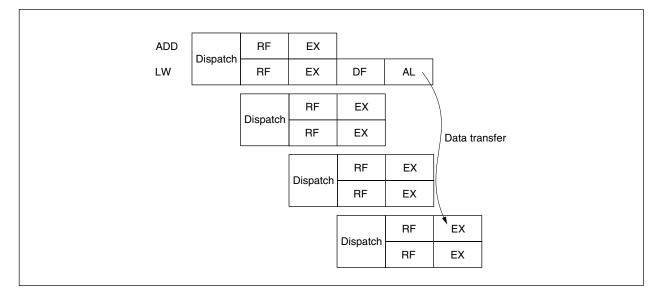

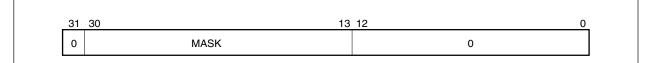

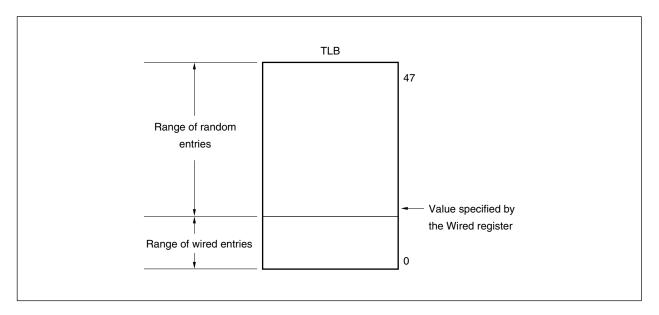

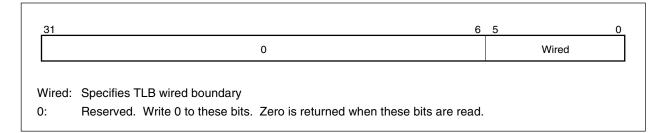

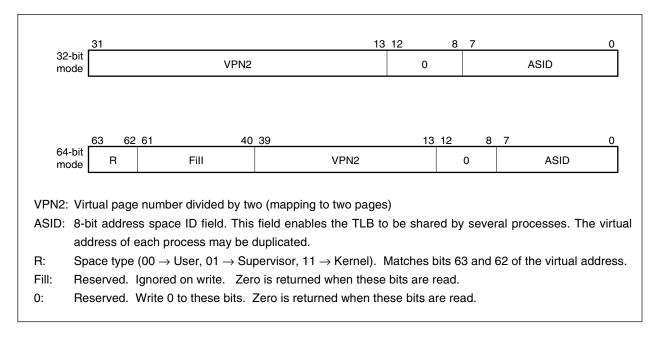

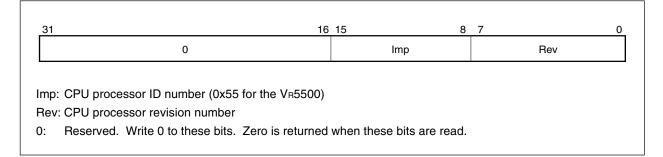

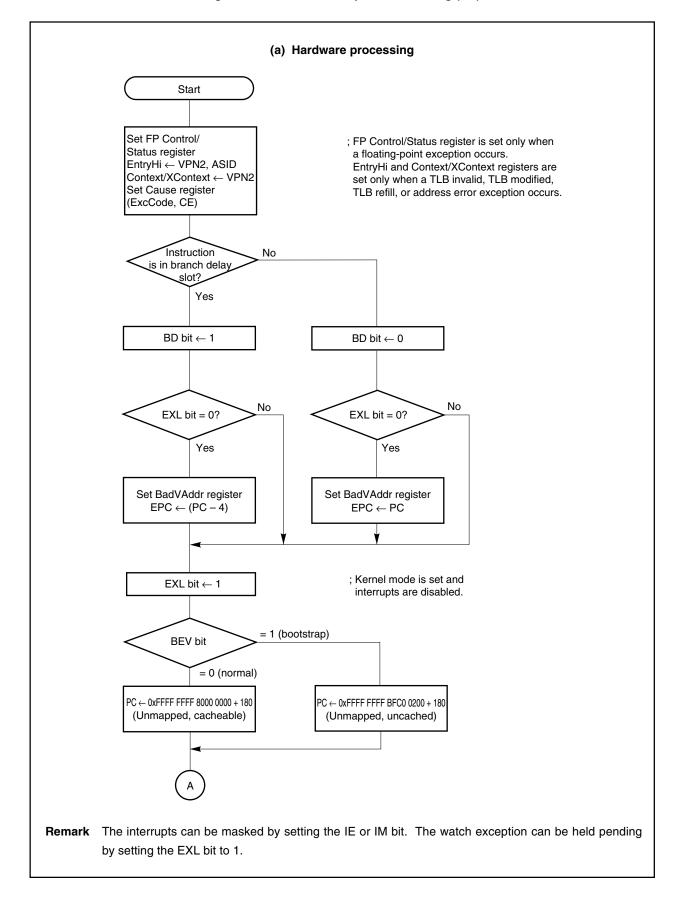

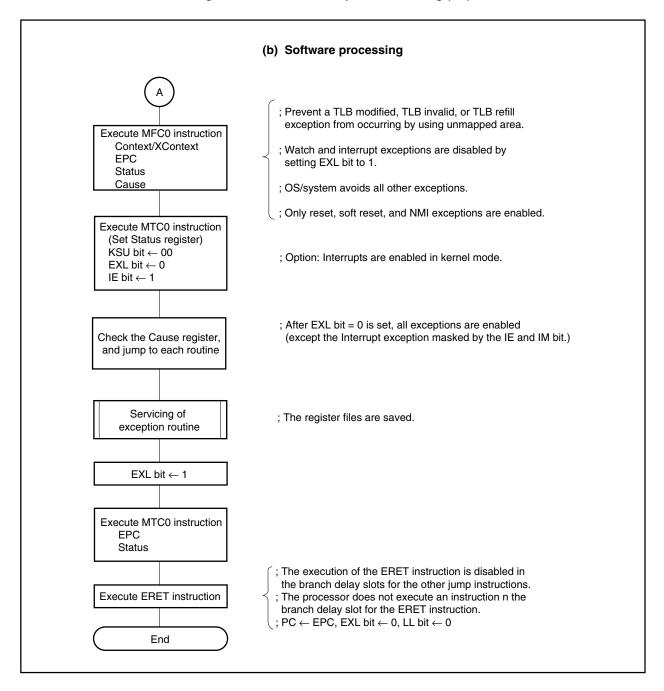

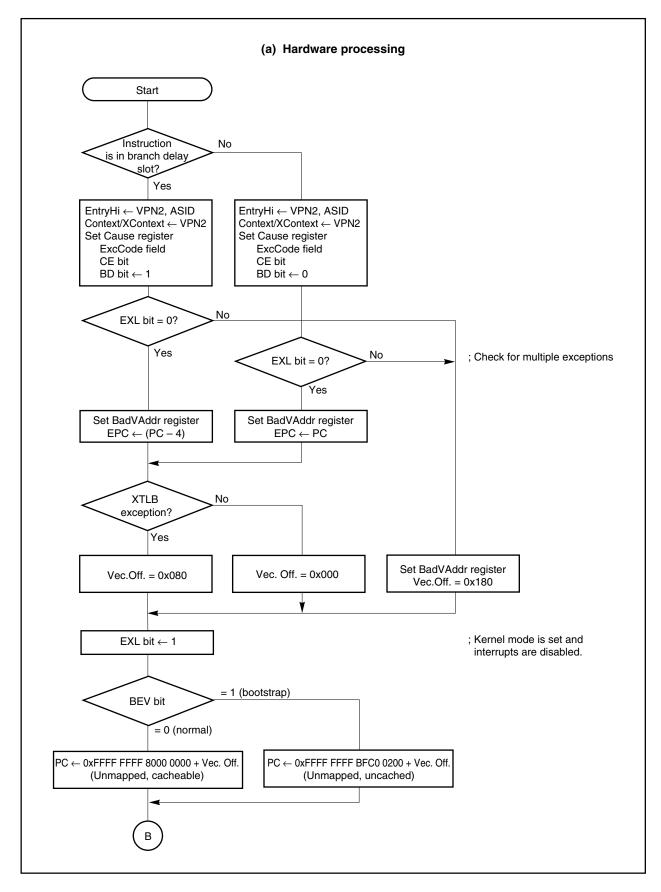

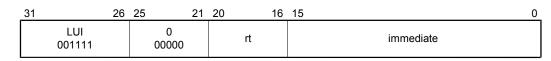

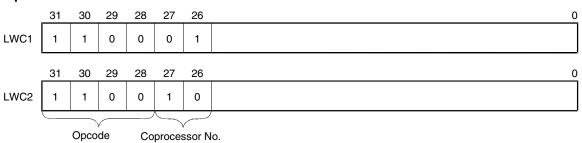

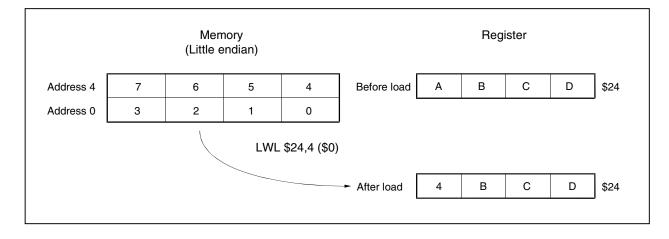

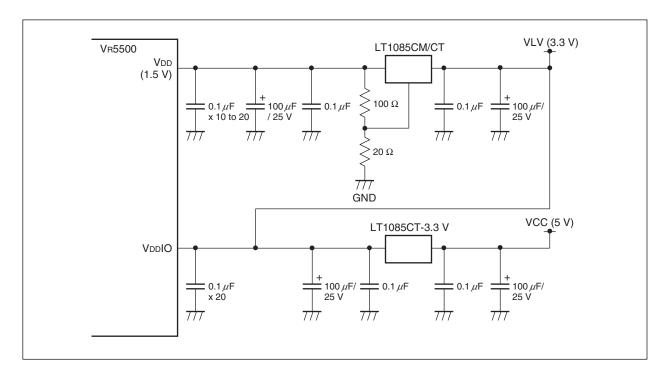

|    | 14.3                         | 14.1.2 Processor write request protocol         14.1.3 Control of processor request flow         14.1.4 Timing mode of processor request <b>Protocol of External Request</b> 14.2.1 External arbitration protocol         14.2.2 External null request protocol         14.2.3 External write request protocol         14.2.4 Read response protocol         14.2.5 SysADC(3:0) protocol for block read response <b>Data Flow Control</b> 14.3.1 Data rate control         14.3.2 Block write data transfer pattern         14.3.4 System endianness         Independent Transfer with SysAD Bus                                                                                                                                                                                                                               | 263<br>265<br>267<br>271<br>273<br>274<br>275<br>277<br>277<br>277<br>277<br>278<br>279<br>281<br>282                                           |