# μPD7533/75CG33E 4-Bit, Single-Chip CMOS Microcomputers With A/D Converter

### **Description**

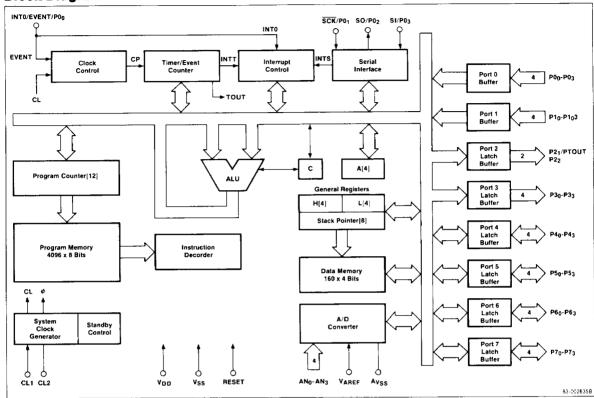

The  $\mu$ PD7533 is a 4-bit, single-chip CMOS microcomputer with a 4-channel, 8-bit A/D converter, 8-bit timer/event counter, and an 8-bit serial interface. The  $\mu$ PD7533 has 30 I/O lines, 8 of which can be used to directly drive LEDs. The  $\mu$ PD7533 executes 67 instructions of the  $\mu$ PD7500 series "A" instruction set.

The A/D converter has various temperature monitoring applications that can be used with household electrical appliances, such as air conditioners and electric ovens. Other applications include health monitoring equipment and cameras.

The µPD75CG33E consists of a 28-pin socket "piggy-backed" on the lower 42-pin ceramic DIP. This socket is configured to hold either a 2732A or 2764 EPROM. For engineering purposes, programs can be tried and debugged before ROM code submission.

#### **Features**

- ☐ 4-bit single chip microcomputer

- $\Box$  67 instructions (subset of  $\mu$ PD7500 series set A)

- ☐ Instruction cycle

- 5 μs at 5 V, 400-kHz clock at ceramic oscillation,

DIVSEL = high

- 10 μs at 5 V, 400-kHz clock at ceramic oscillation, DIVSEL = low

- ☐ Program memory (ROM): 4096 words x 8 bits

- External in the µPD75CG33E

- ☐ Data memory (RAM): 160 words x 4 bits

- ☐ 8 high current output lines for LED direct drive

- ☐ Input/output ports

- Two 4-bit input ports

- One 2-bit output port

- One 4-bit output port

- Three 4-bit input/output ports (two of these can function in 8-bit units)

- One 4-bit input/output port usable at bit level

- ☐ Interrupts: two internal and one external

- ☐ 8-bit serial interface

- ☐ Standby operation

- STOP mode

- HALT mode

- ☐ On-chip system clock oscillator

- Ceramic resonator

- Full or 1/2 oscillation frequency

- □ CMOS technology

- ☐ Low power consumption

- □ Single power supply

## **Ordering Information**

| Part<br>Number | Package<br>Type              | Maximum<br>Frequency<br>of Operation |  |

|----------------|------------------------------|--------------------------------------|--|

| μPD7533C       | 42-pin plastic DIP           | 510 kHz                              |  |

| μPD7533CU -    | 42-pin plastic shrink DIP    | 510 kHz                              |  |

| µPD7533G-22    | 44-pin plastic QFP           | 510 kHz                              |  |

| μPD75CG33E     | 42-pin ceramic piggyback DIP | 510 kHz                              |  |

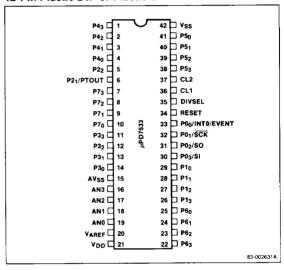

### **Pin Configurations**

### 42-Pin Plastic DIP or Plastic Shrink DIP

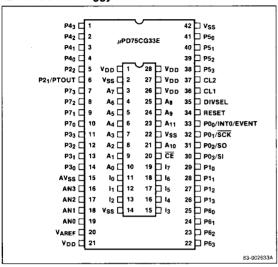

# Pin Configurations (cont)

#### 42-Pin Ceramic Piggyback DIP

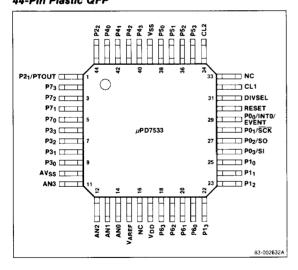

### 44-Pin Plastic QFP

### Pin Identification

### 42-Pin DIP, Shrink DIP, and Piggyback DIP

| No.    | Symbol                                   | Function                                   |

|--------|------------------------------------------|--------------------------------------------|

| 1-4    | P4 <sub>3</sub> -P4 <sub>0</sub>         | 1/0 port 4                                 |

| 5, 6   | P2 <sub>2</sub> , P2 <sub>1</sub> /PTOUT | Port 2 output                              |

| 7-10   | P7 <sub>3</sub> -P7 <sub>0</sub>         | I/O part 7                                 |

| 11-14  | P3 <sub>3</sub> -P3 <sub>0</sub>         | Port 3 output                              |

| 15     | Avss                                     | A/D converter ground                       |

| 16-19  | AN3-AN0                                  | Analog input                               |

| 20     | V <sub>AREF</sub>                        | A/D reference voltage input                |

| 21     | V <sub>DD</sub>                          | Positive power supply                      |

| 22-25  | P6 <sub>3</sub> -P6 <sub>0</sub>         | I/O port 6                                 |

| 26-29  | P1 <sub>3</sub> -P1 <sub>0</sub>         | Port 1 input                               |

| 30     | P0 <sub>3</sub> /SI                      | Port 0 input/Serial input                  |

| 31     | P0 <sub>2</sub> /S0                      | Port 0 input/Serial output                 |

| 32     | PO <sub>1</sub> /SCK                     | Port 0 input/(I/0) Serial clock            |

| 33     | PO <sub>0</sub> /INTO/EVENT              | Port 0 input/Interrupt 0/Event input       |

| 34     | RESET                                    | RESET input                                |

| 35     | DIVSEL                                   | System clock selection input               |

| 36, 37 | CL1, CL2                                 | External clock input/System clock terminal |

| 38-41  | P5 <sub>3</sub> -P5 <sub>0</sub>         | 1/0 port 5                                 |

| 42     | V <sub>SS</sub>                          | Ground                                     |

### Pin Identification (cont)

#### 44-Pin QFP

| No.    | Symbol                                  | Function                             |

|--------|-----------------------------------------|--------------------------------------|

| 1, 44  | P2 <sub>1</sub> /PTOUT, P2 <sub>2</sub> | Port 2 output                        |

| 2-5    | P7 <sub>3</sub> -P7 <sub>0</sub>        | 1/0 port 7                           |

| 6-9    | P3 <sub>3</sub> -P3 <sub>0</sub>        | Port 3 output                        |

| 10     | Avss                                    | A/D converter ground                 |

| 11-14  | AN3-AN0                                 | Analog input                         |

| 15     | V <sub>AREF</sub>                       | A/D reference voltage input          |

| 17     | V <sub>DD</sub>                         | Positive power supply                |

| 18-21  | P6 <sub>3</sub> -P6 <sub>0</sub>        | I/0 port 6                           |

| 22-25  | P1 <sub>3</sub> -P1 <sub>0</sub>        | Port 1 input                         |

| 26     | P0 <sub>3</sub> /SI                     | Port 0 input/Serial input            |

| 27     | P0 <sub>2</sub> /S0                     | Port 0 input/Serial output           |

| 28     | PO <sub>1</sub> /SCK                    | Port 0 input/(I/0) Serial clock      |

| 29     | PO <sub>0</sub> /INTO/EVENT             | Port 0 input/Interrupt 0/Event input |

| 30     | RESET                                   | RESET input                          |

| 31     | DIVSEL                                  | System clock selection input         |

| 32, 34 | CL1, CL2                                | External clock input/System clock    |

| 35-38  | P5 <sub>3</sub> -P5 <sub>0</sub>        | 1/0 port 5                           |

| 39     | V <sub>SS</sub>                         | Ground                               |

| 40-43  | P4 <sub>3</sub> -P4 <sub>0</sub>        | 1/0 port 4                           |

| 16, 33 | NC                                      | No connect                           |

#### 28-Pin EPROM Socket on 42-pin Piggyback DIP

| No.                                            | Symbol                          | Function              |  |  |

|------------------------------------------------|---------------------------------|-----------------------|--|--|

| 1, 26-28                                       | V <sub>DD</sub>                 | Positive power supply |  |  |

| 2, 14, 22                                      | V <sub>SS</sub>                 | Ground                |  |  |

| 20                                             | CE                              | Chip enable output    |  |  |

| 3-10, 21,<br>23-25                             | A <sub>0</sub> -A <sub>11</sub> | Address bus           |  |  |

| 11-13, ł <sub>0</sub> -l <sub>7</sub><br>15-19 |                                 | Data bus              |  |  |

#### Pin Functions

### P00-P03 [Port 0]

P0<sub>0</sub>-P0<sub>3</sub> function as port 0. P0<sub>0</sub> also functions as a count pulse input pin for the timer/event counter (EVENT) or as interrupt 0 (INT0). P0<sub>1</sub> also functions as a serial clock input/output pin ( $\overline{SCK}$ ) for the serial interface. P0<sub>2</sub> functions as a serial data output pin (SO) and pins P0<sub>3</sub> as a serial data input pin (SI). The P0<sub>1</sub>/ $\overline{SCK}$  and P0<sub>2</sub>/SO pins are three-state input/output.

The shift mode register ( $SM_0$ - $SM_3$ ) determines the operation mode of the port 0 input/output pins; however, the data on  $P0_0$ - $P0_3$  can be loaded into the accumulator at any time by executing a port input instruction (IP/IPL). This is possible even when  $P0_1$ - $P0_3$  are functioning as the serial interface.

After a RESET,  $P0_0$ - $P0_3$  become input ports (high impedance).

### P10-P13 [Port 1]

P1<sub>0</sub>-P1<sub>3</sub> function as port 1. Execution of an IP or IPL instruction reads data present on P1<sub>0</sub>-P1<sub>3</sub> into the accumulator. Tie any unused lines of P1<sub>0</sub>-P1<sub>3</sub> to  $V_{DD}$  or  $V_{SS}$ .

### P2<sub>1</sub>-P2<sub>2</sub> [Port 2]

$P2_1-P2_2$  function as port 2 with an output latch. When an output instruction (OP/OPL) to port 2 is executed, the middle 2 bits (A<sub>1</sub> and A<sub>2</sub>) of the accumulator are latched by the output latch and, at the same time, output to  $P2_1-P2_2$ .

After being written once, the output latch contents remain until they are rewritten by an output instruction or a reset. The status of the corresponding output signal also remains. After a reset, the output latch contents become undefined, all output signals are disabled, and the output drivers are turned off.

P2<sub>1</sub> is also used as an output pin (PTOUT) for the timer-out F/F signal (PTOUT). Bit 3 (CM<sub>3</sub>) of the clock mode register controls the PTOUT output. When CM<sub>3</sub> is 1, TOUT is ORed with the P2<sub>1</sub> output latch contents and sent to the output driver. Therefore, to output the P2<sub>1</sub> output latch contents, reset CM<sub>3</sub> to 0 to inhibit the TOUT signal.

Note that soon after the RESET signal is asserted,  $CM_3$  is reset and TOUT is inhibited. However, since the output latch contents are undefined after a reset, to output the TOUT signal, first write 0 in the P2<sub>1</sub> output latch and then set  $CM_3$  to 1 to output TOUT.

### P3n-P33 [Port 3]

P3<sub>0</sub>-P3<sub>3</sub> function as port 3 with an output latch. When an output instruction to port 3 is executed, the accumulator contents are latched and output.

Once data is written in the output latch, the data is held until the next output instruction to port 3 is executed or RESET is asserted. After a reset, the output latch contents become undefined and the output driver is turned off

### P4<sub>0</sub>-P4<sub>3</sub> [Port 4] P5<sub>0</sub>-P5<sub>3</sub> [Port 5]

P4<sub>0</sub>-P4<sub>3</sub> function as port 4 and P5<sub>0</sub>-P5<sub>3</sub> function as port 5. When an input instruction is executed, the data on these pins is read into the accumulator. When an output instruction is executed, the accumulator contents are latched and output. After the data is written into the latch, it is held until the next output instruction to ports 4 or 5 is executed, or RESET is asserted.

Ports 4 and 5 can work as a pair enabling data (input with the IP54 instruction and output with the OP54 instruction) in 8-bit units. The high four bits of data are from the accumulator and the low four bits are from memory (addressed by HL).

Ports 4 and 5 automatically set in the input mode (high impedance output) after a reset or when the input instructions to these ports are executed. After a reset, the output latch contents become undefined. Both ports 4 and 5 can drive LEDs directly.

Note that after the port changes from output mode to input mode, the data on the line is unstable when the input instruction that changes the mode is first executed. It is strongly recommended that you re-execute the input instruction considering the input/output mode switching time. This will insure reading stable data.

The bit manipulation instruction affects the specified bit only. So when the output latch contents are undefined, (immediately after a reset), initialize the output latch contents with an output instruction before the bit manipulation instruction is executed.

### P60-P63 [Port 6]

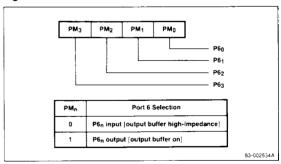

P6<sub>0</sub>-P6<sub>3</sub> function as the 4-bit input latched, three-state output port. The individual lines can be programmed as either inputs or outputs.

In input mode, data present at this port is read into the accumulator by the execution of an IP or IPL instruction. Accumulator data written to this port by the execution of an OP, OPL, ANP, or ORP instruction is statically latched, and remains unchanged until rewritten. This data, however, is not output since the output buffer is disabled and placed in the high impedance state.

In output mode, accumulator data written to the specified port line by the execution of the OP, OPL, ANP, or ORP instruction is statically latched and output to the P6<sub>n</sub> pin. Data present at P6<sub>n</sub> is read into the accumulator by the execution of the IP or IPL instruction, making it possible to read the contents of the P6<sub>n</sub> output latch.

All lines of port 6 are initialized to the high impedance state at Reset. Leave any unused lines open (if outputs) or tied to  $V_{DD}$  or  $V_{SS}$  (if inputs).

The port 6 mode select register (MSR) controls the function of the individual port 6 lines. The execution of the OP or OPL instruction loads the port 6 MSR with the accumulator contents. The 4-bit immediate data operand or the contents of the L register must be set to 0EH. Figure 1 shows the format of the port 6 MSR.

Figure 1. Port 6 MSR Format

### P70-P73 [Port 7]

Port 7 is a 4-bit input or latched three-state output port. The execution of an IP or IPL instruction execution reads data present at this port into the accumulator. Accumulator data written to this port by the execution of an OP, OPL, ANP, or ORP instruction is statically latched and remains unchanged until rewritten.

Upon reset, all lines are initialized to the high-impedance state. Leave any unused lines open (if outputs) or tied to  $V_{DD}$  or  $V_{SS}$  (if inputs).

# AN0-AN3 [A/D Input Terminal]

AN0-AN3 are the 4-channel A/D converter input terminals. The A/D converter uses a successive approximation method.

### VAREE [A/D Converter Positive Reference]

The voltage on  $V_{AREF}$  determines the full scale analog voltage.

### Avss [A/D Converter Ground]

AVSS is the ground for the A/D circuit.

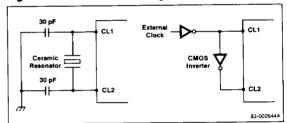

### CL1, CL2 [Clock]

CL1 and CL2 connect external oscillator elements to the system clock. Connect a ceramic resonator to these pins. If an external clock is used, place a buffer between the clock source and the CL1 and CL2 pins.

When connecting the oscillation parts to the CL1 and CL2 pins, use the shortest wiring possible. Ground the capacitor as close to the  $V_{\rm SS}$  pin as possible.

#### DIVSEL [System Clock Divider Selection Input]

DIVSEL selects whether the system clock runs at ceramic oscillation frequency, or at one-half the ceramic oscillation frequency. If a logic 0 ( $V_{SS}$ ) is connected to DIVSEL, the system clock is one-fourth the ceramic oscillation. If DIVSEL is high, then the system clock will be one-half of the ceramic oscillation.

#### RESET [Reset]

A high on RESET activates this input.

### **VDD** [Power Supply]

V<sub>DD</sub> is the positive power supply pin.

### Vss [Ground]

VSS is the ground pin.

### Pin Functions, µPD75CG33 EPROM

### A<sub>0</sub>-A<sub>11</sub> [EPROM Address]

$A_0$ - $A_{11}$  output the contents of the EPROM program address counter. A reset leaves  $A_0$ - $A_{11}$  undefined.

### Io-I7 [Data Bus]

I<sub>0</sub>-I<sub>7</sub> input the contents of the EPROM data bus.

# CE [Chip Enable]

CE outputs the EPROM chip enable signal. (Active low.)

### V<sub>DD</sub> [Power Supply], V<sub>SS</sub> [Ground]

$V_{DD}$  is the positive power supply pin with the same voltage as the lower portion pin 21.  $V_{SS}$  is the ground pin with the same voltage as the lower portion pin 42. The following voltages are supplied to the 2764 or 2732A pins from  $V_{DD}$  or  $V_{SS}$ .

| Pin Number |       |                 |                               |

|------------|-------|-----------------|-------------------------------|

| 2764       | 2732A | Symbol          | Voltage                       |

| 1          | 20    | V <sub>PP</sub> | $V_{DD}$ pin 21 = +5 V        |

| 28         | 24    | V <sub>CC</sub> | V <sub>DD</sub> pin 21 = +5 V |

| 22         | 20    | ŌĒ              | V <sub>SS</sub> pin 42 = 0 V  |

| 2          | _     | A <sub>12</sub> | $V_{DD}$ pin 21 = +5 V        |

| 14         | 12    | V <sub>SS</sub> | V <sub>SS</sub> pin 42 = 0 V  |

# **Block Diagram**

### **Absolute Maximum Ratings**

TA = 25 °C

| -A                                         |                                   |

|--------------------------------------------|-----------------------------------|

| Power supply voltage, V <sub>DD</sub>      | 0.3 to +7.0 V                     |

| Input voltage, V <sub>I</sub>              | -0.3 V to V <sub>DD</sub> + 0.3 V |

| Output voltage, V <sub>0</sub>             | -0.3 V to V <sub>DD</sub> + 0.3 V |

| High level output current, I <sub>OH</sub> | —17 mA (1 pin)                    |

|                                            | -20 mA (all output ports)         |

| Low level output current, I <sub>OL</sub>  | 17 mA (1 pin)                     |

|                                            | 80 mA ports 2,3,4,7 (total pins)  |

|                                            | 80 mA ports 0,5,6                 |

| Operating temperature, T <sub>OPT</sub>    | -10 to +70°C                      |

| Storage temperature, T <sub>STG</sub>      | −65 to +150°C                     |

| A/D V <sub>SS</sub> , A <sub>VSS</sub>     | -0.3 to +0.3 V                    |

| A/D reference, V <sub>AREF</sub>           | −0.3 V to V <sub>DD</sub>         |

|                                            |                                   |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Capacitance

$T_A = 25$ °C,  $V_{DD} = 0$  V

|                       |                 | Lin | nits |      | Test                   |  |

|-----------------------|-----------------|-----|------|------|------------------------|--|

| Parameter             | Symbol          | Min | Max  | Unit | Conditions             |  |

| Input<br>capacitance  | C <sub>IN</sub> |     | 15   | pF   | f =1 MHz<br>Unmeasured |  |

| Output<br>capacitance | Соит            |     | 15   | pF   | pins are 0 V.          |  |

| I/O<br>capacitance    | C <sub>IO</sub> |     | 15   | pF   |                        |  |

### **DC Characteristics**

$T_A = -10 \text{ to } +70 \,^{\circ}\text{C}, V_{DD} = 2.7 \text{ to } 6.0 \text{ V}, \text{ DIVSEL} = 1$

|                                                                 |                   | Lim                   | its                   |      | Test                                                                 |

|-----------------------------------------------------------------|-------------------|-----------------------|-----------------------|------|----------------------------------------------------------------------|

| Parameter                                                       | Symbol            | Min                   | Max                   | Unit | Conditions                                                           |

| High level<br>input voltage<br>(other than<br>CL1, CL2)         | V <sub>IH1</sub>  | 0.7 V <sub>DD</sub>   | V <sub>DD</sub>       | ٧    | Conditions<br>specified by<br>oscillation<br>characteristics         |

| High level<br>input voltage<br>(CL1, CL2)                       | V <sub>IH2</sub>  | V <sub>DO</sub> - 0.5 | V <sub>DD</sub>       | V    |                                                                      |

| Low level<br>input voltage<br>(other than<br>CL1, CL2)          | V <sub>IL1</sub>  | 0                     | 0.3 V <sub>DD</sub>   | V    |                                                                      |

| Low level<br>input voltage<br>(CL1, CL2)                        | V <sub>IL2</sub>  | 0                     | 0.5                   | ٧    |                                                                      |

| rligh level<br>output voltage                                   | V <sub>OH</sub>   | V <sub>DD</sub> — 1.0 |                       | ٧    | V <sub>DD</sub> = 4.5-6.0 V<br>I <sub>OH</sub> = -1 mA<br>except P63 |

|                                                                 |                   | V <sub>DD</sub> — 0.5 |                       | ٧    | $I_{OH} = -100  \mu A$                                               |

|                                                                 |                   | V <sub>DD</sub> — 0.5 | V <sub>DD</sub> — 0.2 | ٧    | $V_{DD} = 4.5 - 6.0 \text{ V}$ $I_{OH} = -2 \text{ mA}$ (P63 only)   |

| Low level output voltage                                        | V <sub>OL</sub>   | 0.6 (typ)             | 2.0                   | ٧    | $V_{DD} = 4.5 - 6.0 \text{ V}$ $I_{OL} = 15 \text{ mA}$              |

|                                                                 |                   | 0.7 (typ)             | 2.5                   | ٧    | $(75CG33: V_{DD} = 4.5 - 6.0 V)$                                     |

|                                                                 |                   |                       | 0.4                   | ٧    | $I_{OL} = 1.6 \text{ mA}$                                            |

|                                                                 |                   |                       | 0.5                   | ٧    | $I_{OL} = 400  \mu A$                                                |

| High level<br>input leakage<br>current (other<br>than CL1, CL2) | luh1              |                       | 3                     | μΑ   | $V_{IN} = V_{DD}$                                                    |

| High level<br>input leakage<br>current (CL1,<br>CL2)            | I <sub>LIH2</sub> |                       | 20                    | μΑ   | $V_{IN} = V_{DD}$                                                    |

| Low level<br>input leakage<br>current (other<br>than CL1, CL2)  | lul1              |                       | -3                    | μΑ   | V <sub>IN</sub> = 0 V                                                |

| Low level<br>input leakage<br>current (CL1,<br>CL2)             | LIL2              |                       | -20                   | μΑ   | V <sub>IN</sub> = 0 V                                                |

| High level<br>output leakage<br>current                         | I <sub>LOH</sub>  |                       | 3                     | μΑ   | $V_{OUT} = V_{DD}$                                                   |

| Low level<br>output leakage<br>current                          | ILOL              |                       | -3                    | μΑ   | V <sub>OUT</sub> = 0 V                                               |

### **DC Characteristics**

T<sub>A</sub> = -10 to +70 °C, V<sub>DD</sub> = 2.7 to 6.0 V, DIVSEL = 1

|                |                  | Limi      | Limits |      | Test                                                           |

|----------------|------------------|-----------|--------|------|----------------------------------------------------------------|

| Parameter      | Symbol           | Min       | Max    | Unit | Conditions                                                     |

| Supply current | I <sub>DD1</sub> | 1.0 (typ) | 3.0    | mA   | Operating mode:<br>f <sub>CC</sub> = 500 kHz                   |

|                | I <sub>DD2</sub> | 250 (typ) | 750    | μΑ   | HALT mode:<br>f <sub>CC</sub> = 500 kHz                        |

|                |                  | 300 (typ) | 900    | μΑ   | $V_{DD} = 4.5 - 6.0 \text{ V};$<br>$f_{CC} = 500 \text{ kHz})$ |

|                | I <sub>DD3</sub> | 0.1 (typ) | 10     | μA   | STOP mode                                                      |

|                |                  | 25 (typ)  | 200    | μΑ   | (75CG33:<br>V <sub>DD</sub> = 4.5 - 6.0 V)                     |

# **AC Characteristics**

$T_A = -10 \text{ to } +70 \,^{\circ}\text{C}, V_{DD} = 2.7 \text{ to } 6.0 \text{ V}$

|                                      |                                        | Lin  | iits |      | Test                                  |  |  |

|--------------------------------------|----------------------------------------|------|------|------|---------------------------------------|--|--|

| Parameter                            | Symbol                                 | Min  | Max  | Unit | Cenditions                            |  |  |

| Cycle time                           | tcy                                    | 3.92 | 200  | μS   | $V_{DD} = 4.5 - 6.0 \text{ V}$        |  |  |

|                                      |                                        | 9.52 | 200  | μS   | · ·                                   |  |  |

| EVENT input                          | fE                                     | 0    | 510  | kHz  | $V_{DD} = 4.5 - 6.0 \text{ V}$        |  |  |

| frequency                            |                                        | 0    | 210  | kHz  |                                       |  |  |

| EVENT input<br>high duration         | t <sub>EH</sub>                        | 0.8  |      | μS   | $V_{DD} = 4.5 - 6.0 V$                |  |  |

| EVENT input low duration             | t <sub>EL</sub>                        | 2.2  |      | μS   |                                       |  |  |

| SCK cycle<br>time                    | tKCY                                   | 4.0  |      | μS   | Input<br>V <sub>DD</sub> = 4.5–6.0 V  |  |  |

|                                      |                                        | 3.92 |      | μS   | Output<br>V <sub>DO</sub> = 4.5–6.0 V |  |  |

|                                      |                                        | 10.0 |      | μS   | Input                                 |  |  |

|                                      |                                        | 9.52 |      | μS   | Output                                |  |  |

| SCK high,<br>low level               | t <sub>KH</sub> ,<br>t <sub>KL</sub>   | 1.8  |      | μS   | Input<br>V <sub>DD</sub> = 4.5-6.0 V  |  |  |

| duration                             |                                        | 1.76 | ·    | μS   | Output<br>V <sub>DD</sub> = 4.5–6.0 V |  |  |

|                                      |                                        | 4.8  |      | μS   | Input                                 |  |  |

|                                      |                                        | 4.6  |      | μS   | Output                                |  |  |

| SI setup<br>time (SCK high)          | tsik                                   | 300  |      | ns   |                                       |  |  |

| SI hold<br>time (SCK high)           | t <sub>KSI</sub>                       | 450  |      | ns   |                                       |  |  |

| SCK low                              | t <sub>KS0</sub>                       |      | 850  | ns   | $V_{DD} = 4.5 - 6.0 \text{ V}$        |  |  |

| to SO<br>output delay<br>time        |                                        |      | 1200 |      |                                       |  |  |

| INTO high,<br>low level<br>duration  | t <sub>IOH</sub> ,<br>t <sub>IOL</sub> | 10   |      | μS   |                                       |  |  |

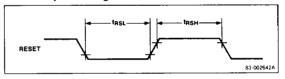

| RESET high,<br>low level<br>duration | t <sub>RSH</sub> ,<br>t <sub>RSL</sub> | 10   |      | μS   |                                       |  |  |

# **Data Memory, STOP Mode Data Retention** Characteristics

$T_A = -10 \text{ to } +70 \,^{\circ}\text{C}$

|                                     |                   |     | Limits |     |      | Tast                                                                   |

|-------------------------------------|-------------------|-----|--------|-----|------|------------------------------------------------------------------------|

| Parameter                           | Symbol            | Min | Тур    | Max | Unit | Conditions                                                             |

| Data<br>retention<br>supply voltage | V <sub>DDDR</sub> | 2.0 |        | 6.0 | ٧    |                                                                        |

| Data retention<br>supply current    | IDDDR             |     | 0.1    | 10  | μΑ   | $V_{DDDR} = 2.0 \text{ V}$                                             |

| RESET setup<br>time                 | tsrs              | 0   |        |     | μ\$  |                                                                        |

| Oscillation<br>stabilizing<br>time  | t <sub>OS</sub>   | 20  |        |     | ms   | Ceramic<br>resonator:<br>when V <sub>DD</sub><br>greater than<br>4.5 V |

A/D Converter Characteristics  $T_A = -10 \text{ to } +70 \,^{\circ}\text{C}, \ V_{DD} = +5.0 \text{ V} \pm 5\%, \\ V_{SS} = A_{VSS} = 0 \text{ V}, \ V_{AREF} = V_{DD} - 0.5 \text{ V to } V_{DD}$

| · · ·                     |                   | -    |      | Test  |                    |                                                                |

|---------------------------|-------------------|------|------|-------|--------------------|----------------------------------------------------------------|

| Parameter                 | Symbol            | Min  | Тур  | Max   | Unit               | Conditions                                                     |

| Resolution                |                   | 8    |      |       | Bits               |                                                                |

| Absolute<br>accuracy      |                   |      | -    | ±1.5  | LSB                |                                                                |

| Conversion<br>time        | tconv             | 9    | -    |       | t <sub>CYC</sub> * | V <sub>DD</sub> - 0.5<br>≤ V <sub>AREF</sub> ≤ V <sub>DD</sub> |

| Sampling<br>time          | <sup>t</sup> SAMP |      | 1    |       | t <sub>CYC</sub> * |                                                                |

| Analog input voltage      | VIAN              | Avss |      | VAREF | ٧                  |                                                                |

| Analog input impedance    | R <sub>AN</sub>   | -    | 1000 |       | MΩ                 |                                                                |

| V <sub>AREF</sub> current | AREF              | 0.4  | 1    | 2     | mΑ                 |                                                                |

\*

$$t_{CYC} = \frac{2}{f_{CC}}$$

(DIVSEL = 1)

# **Data Retention Timing**

### **Oscillator Characteristics**

$T_A = -10 \text{ to } +70 \,^{\circ}\text{C}, V_{DD} = 2.7 \text{ to } 6.0 \text{ V}, \text{ DIVSEL} = 1$

|                | Configuration | Parameter                                                              | Limits |     |     | Test |                                              |

|----------------|---------------|------------------------------------------------------------------------|--------|-----|-----|------|----------------------------------------------|

| Oscillation    |               |                                                                        | Min    | Тур | Max | Unit | Conditions                                   |

| Ceramic        | See figure 3  | Oscillation frequency (f <sub>CC</sub> )                               | 390    | 500 | 510 | kHz  | V <sub>DD</sub> = 4.5 to 6.0 V               |

|                |               |                                                                        | 390    | 500 | 510 | kHz  | V <sub>DD</sub> = 4.0 to 6.0 V               |

|                |               |                                                                        | 390    | 500 | 510 | kHz  | V <sub>DD</sub> = 3.0 to 6.0 V<br>DIVSEL = 0 |

|                |               |                                                                        | 390    | 400 | 410 | kHz  | V <sub>DD</sub> = 2.7 to 6.0 V<br>DIVSEL = 0 |

| <del> </del>   |               | Stabilization time                                                     | 20     |     |     | ms   | V <sub>DD</sub> greater than 4.5 V           |

| External clock | See figure 3  | CL1 input frequency                                                    | 10     |     | 510 | kHz  | V <sub>DD</sub> = 4.5 to 6.0 V               |

|                |               |                                                                        | 10     |     | 210 | kHz  |                                              |

|                |               | CL1 input high, low level duration (t <sub>CH</sub> ,t <sub>CL</sub> ) | 1.0    |     | 50  | μS   | V <sub>DD</sub> = 4.5 to 6.0 V               |

|                |               |                                                                        | 1.0    |     | 50  | μS   |                                              |

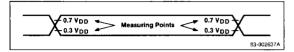

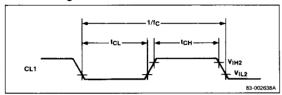

# **Timing Waveforms**

# AC Timing Measuring Points (Except CL1)

# **Clock Timing**

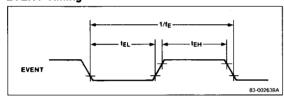

### **EVENT Timing**

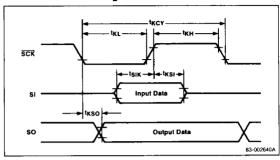

### Serial Transfer Timing

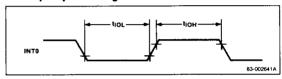

### Interrupt Input Timing

# **RESET Input Timing**

### **Functional Description**

### **System Clock Generator**

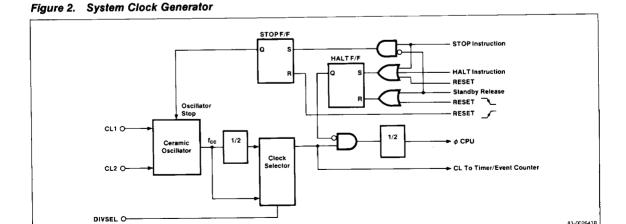

The ceramic oscillator circuit generates the system clock for the  $\mu$ PD7533. Figure 2 shows that the oscillator circuit for the  $\mu$ PD7533 includes a ceramic oscillator, two divide-by-two circuits, the DIVSEL input, and control circuitry for the standby modes, HALT and STOP.

Figure 3 shows that the ceramic oscillator requires that a ceramic resonator be connected to the CL1 and CL2 pins. An external clock can also be input at CL1. In this case, the oscillator operates as an inverted buffer.

Figure 2 shows that the output frequency from the ceramic oscillator connects either directly to the clock selector or via a divide-by-two circuit. The selector is controlled by the DIVSEL line. If DIVSEL is low, the divide-by-two frequency is selected. This option is used during a low power operating mode. If DIVSEL is high, then the direct frequency is chosen. The output of the selector is used as system clock (CL), and is also divided by two to supply the CPU clock  $(\phi)$ .

Table 1 shows how DIVSEL selects the system and CPU clocks, and machine cycle timing.

Table 1. Clock Selection

| DIVSEL | System Clock<br>(CL) | CPU Cleck<br>{φ} | Machine Cycle |

|--------|----------------------|------------------|---------------|

| Low    | 200 kHz              | 100 kHz          | 10 <i>μ</i> s |

| High   | 400 kHz              | 200 kHz          | 5 μs          |

### **Standby Control**

The HALT F/F and the STOP F/F comprise the control circuitry for standby mode (figure 2). The STOP F/F is set by the STOP instruction. When the STOP F/F is set, the ceramic oscillator stops. The rising edge of the RESET input resets the STOP F/F.

The HALT instruction sets the HALT F/F and inhibits the input of the half-frequency divider which generates the CPU clock. As a result, only the CPU clock is stopped in HALT mode. The RELEASE signal resets the HALT F/F. RELEASE becomes active when any interrupt request flag is set, or at the falling edge of the RESET input.

While RESET is active, the HALT F/F is set, and the chip goes into the HALT mode. At a power-on Reset, the ceramic oscillation is driven when the RESET input signal becomes high.

Figure 3. Clock Driver Configuration

It takes a short period of time for the oscillator output to become stable. To prevent errors due to an unstable clock, the HALT F/F is set to inhibit the CPU clock while the RESET input is high. Therefore, the high-level pulse width for the RESET input should be wide enough to cover the required time for the ceramic resonator oscillation to stabilize.

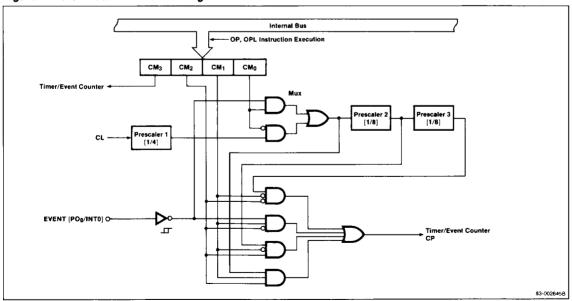

#### **Clock Control**

Figure 4 shows that the clock controller contains a 4-bit clock mode register (CM0-CM3), prescalers 1-3, and multiplexers. The clock controller selects the clock sources and prescalers, and supplies the count pulses (CP) to the timer/event counter. The clock sources are the system clock generator output (CL) or the EVENT pulse.

The OP 12 or OPL (L = 12) instruction sets codes in the clock mode register. CM3 designates the output of the timer-out signals. If CM3 = 1, the output of the timer-out F/F (TOUT) is available at the PTOUT (P21) pin.

Figure 5 shows the format of the clock mode register.

Figure 5. Format of Clock Mode Register

Figure 4. Clock Controller Block Diagram

#### **Timer/Event Counter**

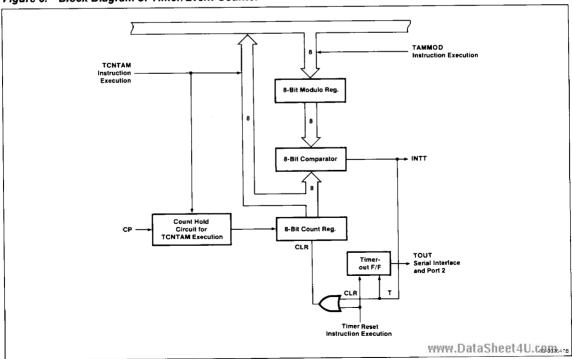

Figure 6 shows the timer/event counter has an 8-bit count register, 8-bit modulo register, an 8-bit comparator, and a timer-out flip flop.

### **Timer Operation**

After the TAMMOD instruction sets a count value in the modulo register and the TIMER instruction clears the contents of the count register, the timer starts counting count pulses (CP). If an external clock is used, the count pulses are synchronized with the rising edge of CL1 or the  $P0_0$  input.

When the value of the modulo register equals the value of the count register, the comparator generates a coincidence signal (INTT) to set an interrupt request flag. Then it clears the count register to repeat the counting. In this manner, the timer functions as an interval timer whose interval is set by the modulo register.

Regardless of any instructions, the count pulses are always input into the count register, updating the count value. If the contents of the count register are equal to those of the modulo register, the INTT request flag is then set. For this reason, inhibit INTT interrupts when not using the timer.

### **Event Counter Operation**

To use the timer/event counter as an event counter, input the external event pulse into the  $P0_0$  pin, and select  $P0_0$ ' as the count pulse (CP) for the clock controller. The count register counts the external event pulses input at the  $P0_0$  pin, either as they are, or frequency divided.

As a result, the timer/event counter operates as an event counter that generates interrupts after observing the number of counts (events) specified by the modulo register. The TCNTAM instruction can read the current count at any time.

Set the modulo register with the number of count pulses minus one. If set to 0, no counting will occur because the counter register is held at 0 (both the detection of coincidence and zero-clearing are simultaneously made).

Figure 6. Block Diagram of Timer/Event Counter

#### Serial Interface

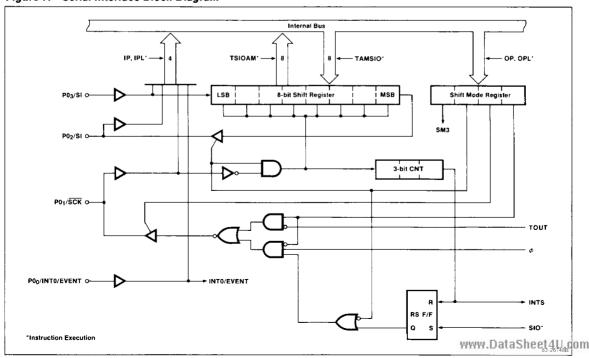

As figure 7 shows, the serial interface includes an 8-bit shift register, a 4-bit shift mode register, and a 3-bit counter.

The serial clock controls serial data I/O. At the falling edge of the serial clock ( $\overline{SCK}$ ), the SO line outputs the most significant bit (7) of the shift register. The contents of the shift register are shifted by one bit at the rising edge of the next serial clock ( $n \leftarrow 0 n+1$ ). At the same time, the data on the SI line is loaded into the least significant bit (0) of the shift register.

The 3-bit counter (octal counter) counts up the serial clocks and generates an internal interrupt signal INTS at every count of 8 clocks (at the end of a 1-byte serial data transfer). It then sets the interrupt request flag (INTO/S RQF). The TAMSIO instruction sets data in the shift register during the transmission of serial data, then starts transmission. At the end of the transmission of each byte (8 bits) an internal interrupt (INTS) is generated.

The SIO instruction also starts the reception of serial data. The received data is taken from the shift register by executing the TSIOAM instruction after an interrupt (INTS) is generated by the reception of one byte of data.

The end of a 1-byte transfer can be confirmed by testing the INTS RQF with the SKI instruction instead of interrupt processing.

The following three types of serial clock sources are available: system clock  $\phi$ , external clock ( $\overline{SCK}$  input), and timer-out F/F output signal (TOUT). Bits  $SM_2$ - $SM_0$  of the shift mode register select the clock source.

If the system clock  $\phi$  is chosen, execute the SIO instruction to supply the clock to the serial interface, controlling the input/output of serial data while  $\phi$  is output from the  $\overline{SCK}$  pin.

After eight  $\phi$  pulses, the clock is automatically discontinued by holding the  $\overline{SCK}$  output at a high level. Therefore, the input/output of serial data automatically stops after each byte has been transferred. Consequently, the software does not need to control the serial clock and the transfer rate is determined by the system clock frequency.

In this mode, after six machine cycles from the execution of the SIO, the TSIOAM instruction can read out the received data from the shift register or can write in the next transmit data.

Figure 8 shows the shift mode register format.

Figure 7. Serial Interface Block Diagram

Figure 8. Format of Shift Mode Register

| SM <sub>2</sub> | SM <sub>1</sub> | SMo | PO <sub>3</sub> /SI | PO <sub>2</sub> /80 | PO <sub>1</sub> /SCK        | Serial Operation             |

|-----------------|-----------------|-----|---------------------|---------------------|-----------------------------|------------------------------|

| 0               | 0               | 0   | Port input          | Port input          | Port input                  | Stops                        |

| 0               | 1               | 0   | -                   |                     | Outputs $\phi$ continuously |                              |

| 0               | 1               | 1   | -                   |                     | Outputs TOUT continuously   |                              |

| 1               | 0               | 0   | SI input            | S0 output           | SCK input                   | Operates with external clock |

| 1               | 1               | 0   | -                   |                     | SCK output ( $\phi$ x 8)    | Operates with $\phi$         |

| 1               | 1               | 1   | -                   |                     | SCK output (TOUT)           | Operates with TOUT           |

Bit SM<sub>3</sub> selects the interrupt source in the following manner:

| SM <sub>3</sub> | Interrupt Source |  |  |

|-----------------|------------------|--|--|

| 0               | INTS             |  |  |

| 1               | INTO             |  |  |

If the external clock (SCK input) is selected, the serial clocks are input from SCK. When the eighth external serial clock is input, an internal interrupt (INTS) is generated, signalling the end of a 1-byte data transfer.

Since the serial clocks are not internally inhibited, the external clock must hold the signal high after eight clocks. The external serial clock determines the transfer rate. The serial interface can be operated from DC to the maximum rate in the electrical specifications.

If TOUT is selected, the half-frequency divided coincidence signal of the timer/event counter is the serial clock. This serial clock controls the input/output of the serial data and is output from the SCK pin. The count pulse supplied to the timer/event counter and the value set in the modulo register determine the transfer rate. The end of a 1-byte data transfer is signalled by INTS. TOUT is not inhibited automatically, therefore the program should stop TOUT at intervals of 16

To use the external clock or the TOUT signal, execute the SIO, TAMSIO or TSIOAM instructions while the serial clock (SCK) is held high. Operation cannot be guaranteed if these intructions are executed over the rising or falling edge of SCK, or at the low level.

In a system that does not require serial data transfer, the 8-bit shift register can be ued as a register with the serial operation stopped. The TSIOAM or TAMSIO instruction can read or write data.

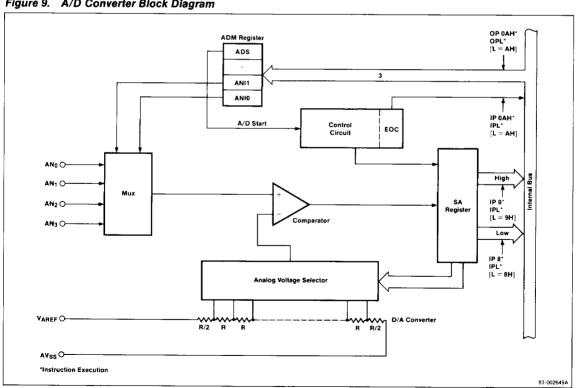

### **Analog to Digital Converter**

The µPD7533 integrates a 4-channel 8-bit A/D converter with separate positive reference and ground from the device power supply. Figure 9 shows that the A/D converter includes an A/D converter mode register, successive approximation (SA) register, and end of conversion (EOC) control circuitry.

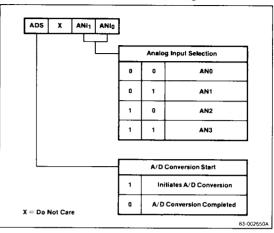

### A/D Converter Mode Register

The A/D converter mode register is a 4-bit internal port that controls the A/D circuitry. The lower two bits, ANI0 and ANI1, select which analog signal (AN0-AN3) is input to the A/D converter. The most significant bit, ADS, initiates the A/D conversion. If ADS is set to a logic 1, the analog signal selected by ANI1 and ANI0 is converted to 8-bit digital data. Upon completion of the data conversion, ADS is cleared to 0.

Figure 10 shows the format for the A/D conversion mode register.

Figure 10. A/D Conversion Mode Register Format

Figure 9. A/D Converter Block Diagram

### Successive Approximation [SA]

The 8-bit data converted from the analog signal using the successive approximation method is stored in the SA register. When ADS is set to a logic 1, the contents of the SA register are undetermined. The SA register is set to 7FH after a reset.

### End of Conversion [EOC] Flag

The EOC flag specifies the completion of an A/D conversion. When ADS is set to 1, the EOC flag is set to a logic 0 and an A/D conversion starts. When the 8-bit A/D conversion is complete, the EOC flag is set to a logic 1. The EOC flag resides in bit 2 of internal Port A. The IP 0AH or IPL instruction can read the contents of Port A when the L register is set to 0AH. The contents of Port A (other than bit 2) will be read as a logic 0. The EOC flag is set to 1 after a reset.

### A/D Converter Operation

An OP 0AH or OPL instruction selects one of four analog signals and starts a conversion when the L register is set to OAH. The lower two bits of the accumulator specify which analog signal will be converted. Bit 3 of the accumulator sets to 1 to initiate the A/D conversion. The A/D conversion requires 9 machine cycles for completion. When the conversion is complete, the EOC flag is set.

In order to assure an accurate data conversion, do not execute an output instruction when EOC is a logic 0.

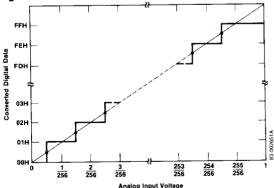

Figure 11 shows how the analog input voltage corresponds to the converted digital data.

### Reading Converted Data

Internal port 9 specifies the upper four bits of the SA register. Therefore, execute an IP 9 or IPL (L = 9) instruction to read the data in the accumulator.

Internal port 8 specifies the lower four bits of the SA register. Therefore, execute an IP 8 or IPL (L = 8) instruction to read the data in the accumulator. Do not read the SA register until EOC is set to 1.

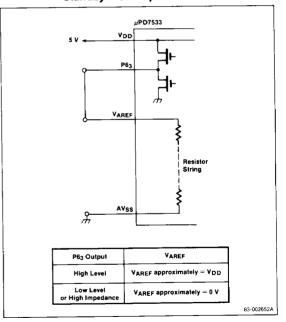

Figure 12 shows the configuration for the A/D converter reference voltage during standby mode.

### Interrupt Function

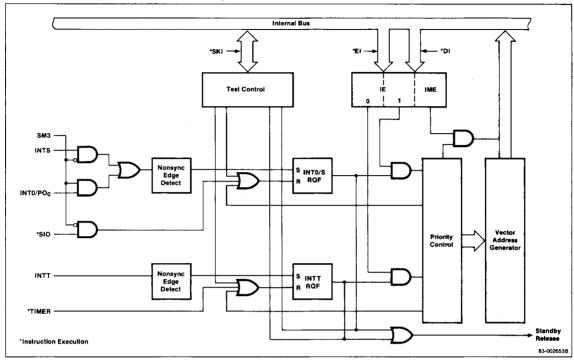

The µPD7533 provides one external interrupt and two types of internal interrupts. The POo pin is used as the input pin for external interrupt INTO. INTO shares priority and vectored addresses with internal interrupt INTS. Figure 13 shows the interrupt controller block diagram.

Configuration of VAREF for Figure 12. Standby Mode Operation

Figure 13. Interrupt Controller Block Diagram

### **Standby Function**

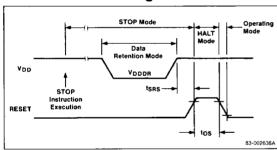

The µPD7533 has two types of standby modes (STOP and HALT) to minimize power consumption during a program standby state. STOP mode is set by the STOP instruction and HALT mode by the HALT instruction.

When standby mode is set, program execution is stopped, and the contents of all internal registers and data memory are held. However, it is possible to operate the shift register and the timer/event counter. An interrupt or reset releases standby mode. Since an interrupt releases standby mode, neither STOP nor HALT modes can be set if an interrupt request flag is set. Therefore, when setting standby mode when there is a possibility of a request flag being set, first reset the interrupt request flag by processing the interrupt in advance or by executing the SKI instruction.

The major difference in the two modes is that crystal oscillation (CL) stops in STOP mode but does not stop in HALT mode.

In STOP mode, it is possible to go into data retention mode by lowering the power supply voltage. During data retention mode, all operation stops and only the data RAM stays intact.

Table 2 shows the differences between STOP and HALT modes.

Table 2. Differences Between STOP and HALT Modes

|                            | Mode      |                                      |  |  |

|----------------------------|-----------|--------------------------------------|--|--|

| Operation                  | STOP Mode | HALT Mode                            |  |  |

| Ceramic Oscillation        | X (1)     | 0 (2)                                |  |  |

| 1/2 Ceramic Oscillation    | X (1)     | X (1)                                |  |  |

| СРИ                        | X (1)     | X (1)                                |  |  |

| Serial I/O                 | (3)       | (2)                                  |  |  |

| Timer/Event Counter        | X (1)     | 0 (2)                                |  |  |

| A/D Converter              | X (1)     | 0 (2)                                |  |  |

| Release of Standby<br>Mode | RESET     | INTO/S RQF<br>NTT RQF<br>RESET Input |  |  |

#### Note:

- (1) Not possible

- (2) Possible

- (3) Possible depending on clock source selected

#### **STOP Mode**

In STOP mode, ceramic oscillation and the half-frequency divider stop. The CPU stops and the operations requiring the system clock (CL, 0) stop.

Release from STOP mode is with the RESET input only. All other functions cease to operate.

In order to minimize power consumption, the current flowing through the resistor ladder of the A/D converter must be minimized. To minimize power consumption, turn off the power to the  $V_{AREF}$  pin.

Note that ceramic oscillation stops and disables the system clock during STOP mode by bringing CL2 to ground. Therefore, if the external clock is connected to CL1 and a STOP instruction is executed, the CPU will enter HALT mode instead.

#### **HALT Mode**

In HALT mode, only the half-frequency divider circuit stops in the clock generator circuit (CL operates,  $\phi$  stops). Therefore, the CPU and the operation of the serial interface (when using  $\phi$  as a serial clock) stop.

However, since the clock control circuit is still in operation, it can select the CL signal from the clock generator or the EVENT input and supply the count pulse (CP) to the timer/event counter.

Consequently, the timer/event counter can be operated in HALT mode. The serial interface operates if a serial clock other than  $\phi$  (such as the external clock, TOUT signal) is selected. The HALT mode is released by the RESET input or an interrupt, even if the interrupt is disabled.

# Release from Standby Mode by Interrupt

The standby mode is released when the interrupt request flag is set by an interrupt source, whether interrupts are disabled or enabled. However, the operations after release differ in each case.

If the interrupt master enable F/F is enabled, and if the interrupt is enabled, the corresponding interrupt routine is initiated after execution of one instruction after the STOP/HALT instruction. Then, the result flag is reset. If the corresponding bit of the interrupt enable register has been reset, execution of instructions starts after the STOP/HALT instruction, and the interrupt routine is not initiated. In this case, the request flag for release remains set. If necessary, reset the request flag with the SKI instruction.

If the interrupt master enable F/F is disabled, the instruction following the STOP/HALT instruction is executed regardless of the state of the interrupt enable register (interrupt routine is not initiated). In this case, the interrupt request flag is left set. If necessary, it can be reset by the SKI instruction.

After any release, operation resumes with the same register contents as before standby mode.

# Release From Standby Mode with RESET

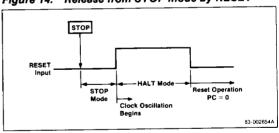

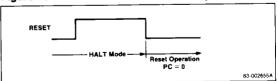

Both STOP and HALT modes are released unconditionally by the RESET input. Figure 14 shows the release timing.

If the device is reset during STOP mode, the low to high transition of the RESET pin will take the processor from STOP mode to HALT mode. When RESET goes high to low, the HALT mode is abandoned, and after a normal reset operation, the PC is initialized to 0. Only the data memory will stay intact during the HALT mode, but all registers become undefined.

If the device is reset during HALT mode, the high to low transition of RESET will release the device from standby mode. After a normal reset operation, the PC is initialized to 0. Only the data memory will stay intact during the HALT mode, but all registers become undefined.

Figure 15 shows the release from HALT mode by RESET.

Figure 14. Release from STOP mode by RESET

Figure 15. Release from HALT Mode by RESET

#### **Reset Function**

The  $\mu$ PD7533 is reset and initialized by the input of the RESET signal (active high).

A RESET causes the CPU to initialize in the following manner:

- · Program counter (PC) is cleared to 0

- Skip flags (SK1, SK0) and program status word (PSW) are reset to 0

- Timer/event counter:

- Count register = 00H

- Modulo register = FFH

- Timer-out F/F = 0

- · Clock control circuitry:

- Clock mode register ( $CM_3$ - $CM_0$ ) = 0

$$- CP = \frac{CL}{256}$$

- Timer-out FF signal not output to PTOUT

- Prescalers 1-3 = 0

- Shift Mode Register (SM3-SM0) is cleared to 0.

- Shift operation stops

- Port 0 is in input mode (high impedance)

- INTS is selected interrupt source of INTO/S

- A/D converter circuit:

- ADM register is set to 0

- AN0 is selected

- SA register is set to 7FH

- EOC flag is set to logic 1

- · Interrupt control circuit:

- Interrupt request flags = 0

- Interrupt master enable F/F = 0

- Interrupt enable register = 0

- All pending interrupts are cancelled

- All interrupts are disabled

- · All Port 2-7 output buffers are turned off

- Contents of data memory and the following registers are undefined:

- Stack pointer (SP)

- Accumulator (A)

- Carry flag (C)

- General purpose registers (H,L)

- All port output latches

- Shift register

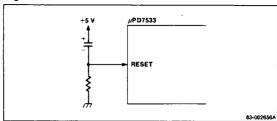

#### **Power-on Reset Circuit**

Figure 16 shows an example of the simplest power-on reset circuit using a resistor and a capacitor.

Figure 16. Power-on Reset Circuit