December 1993

#### DESCRIPTION

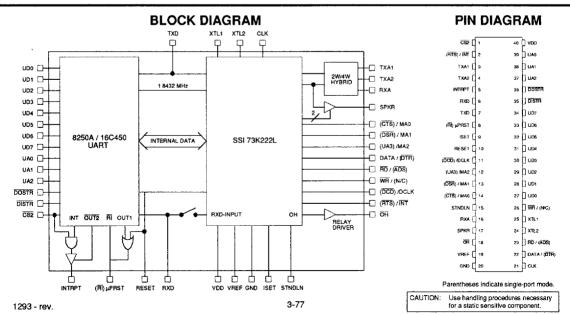

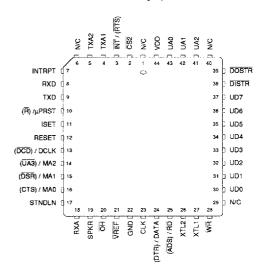

The SSI 73K222U is a compact, high-performance modern which includes a 8250A/16C450 compatible UART with the 1200 bit/s modem function on a single chip. Based on the SSI 73K222L 5V low power CMOS modem IC, the SSI 73K222U is the perfect modem/ UART component for integral modern applications. It is ideal for applications such as portable terminals and laptop computers. The SSI 73K222U is the first fully featured modern IC which can function as an intelligent modem in integral applications without requiring a separate dedicated microcontroller. It provides for data communication at 1200, 600, and 300 bit/s in a multimode manner that allows operation compatible with both Bell 212A/103 and CCITT V.22/V.21 standards. The digital interface section contains a high speed version of the industrystandard 8250A/16C450 UART. commonly used in personal computer products. A unique feature of the SSI 73K222U is that the UART section can be used without the modern function. providing an additional asynchronous port at no added cost. The SSI 73K222U is designed in CMOS technology and operates from a single +5V supply. Available packaging includes 40-pin DIP or 44-pin PLCC for surface mount applications.

#### **FEATURES**

- Modem/UART combination optimized for integral bus applications

- Includes features of SSI 73K222L single-chip modem

- Fully compatible 16C450/8250 UART with 8250B or 8250A selectable interrupt emulation

- High speed UART will interface directly with high clock rate bus with no wait states

- Single-port mode allows full modem and UART control from CPU bus, with no dedicated microprocessor required

- Dual-port mode suits conventional designs using local microprocessor for transparent modem operation

- Complete modem functions for 1200 bit/s (Bell 212A, V.22) and 0-300 bit/s (Bell 103, V.21)

- Includes DTMF generator, carrier, call-progress and precise answer-tone detectors for intelligent dialing capability

- On chip 2-wire/4-wire hybrid driver and off-hook relay buffer

- Speaker output with four-level software driven volume control

- Low power CMOS (40 mW) with power down mode (15 mW)

- Operates from single +5V supply

#### **FUNCTIONAL DESCRIPTION**

The SSI 73K222U integrates an industry standard 8250/16C450 UART function with the modem capability provided by the SSI 73K222L single chip modem IC. The SSI 73K222U is designed specifically for integral microprocessor bus intelligent modem products. These designs typically require the standard 8250 or higher speed 16450 UART to perform parallel-to-serial and serial-to-parallel conversion process necessary to interface a parallel bus with the inherently serial modem function. The SSI 73K222U provides a highly integrated design which can eliminate multiple components in any integral bus modem application, and is ideal for internal PC modem applications.

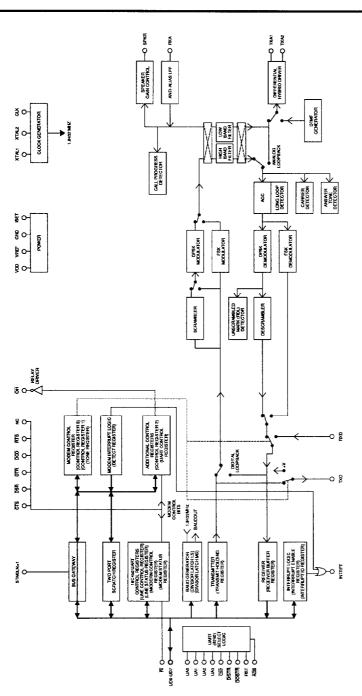

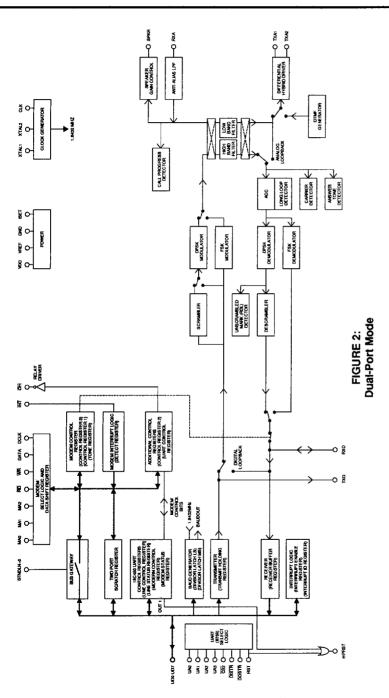

The SSI 73K222U includes two possible operating modes. In the dual-port mode, the device is suitable for conventional plug-in modem card designs which use a separate local microprocessor for command interpretation and control of the modem function. In this mode, a dedicated microcontroller communicates with the SSI 73K222U using a separate serial command port. In the single-port mode the main CPU can control both the UART and modem function using the parallel data bus. This allows very efficient modem design with no local microprocessor required for dedicated applications such as laptop PC's or specialized terminals.

To make designs more space efficient, the SSI 73K222U includes the 2-wire to 4-wire hybrid drivers, off-hook relay driver, and an audio monitor output with software volume control for audible call progress monitoring. As an added feature the UART function can be used independent of the modern function, providing an added asynchronous port in a typical PC application with no additional circuitry required.

#### **UART FUNCTION (16C450)**

The UART section of the SSI 73K222U is completely compatible with the industry standard 16C450 and the 8250 UART devices. The bus interface is identical to the 16450, except that only a single polarity for the control signals is supported. The register contents and addresses are also the same as the 16C450. To insure compatibility with all existing releases of the 8250 UART design, external circuitry normally used in PC applications to emulate 8250B or 8250A interrupt operation has been included on the SSI 73K222U. A select line is then provided to enable the desired

interrupt operation. The UART used in the SSI 73K222U can be used with faster bus read and write cycles than a conventional 16C450 UART. This allows it to interface directly with higher clock rate microprocessors with no need for external circuitry to generate wait states.

The primary function of the UART is to perform parallel-to-serial conversion on data received from the CPU and serial-to-parallel conversion on data received from the internal modem or an external device. The UART can program the number of bits per character, parity bit generation and checking, and the number of stop bits. The UART also provides break generation and detection, detection of error conditions, and reporting of status at any time. A prioritized maskable interrupt is also provided.

The UART block has a progammable baud rate generator which divides an internal 1.8432 MHz clock to generate a clock at 16 x the data rate. The data rate for the transmit and receive sections must be the same. For DPSK modulation, the data rate must be 1200 Hz or 600 Hz. For FSK modulation, the data rate must be 300 Hz or less. The baud generator can create a clock that supports digital transfer at up to 115.2 kHz. The output of the baud generator can be made available at the CLK pin under program control.

#### **MODEM FUNCTION (SSI 73K222L)**

The modem section of the SSI 73K222U provides all necessary analog functions required to create a single chip Bell 212A/103 and CCITT V.22/V.21 modem, controlled by the system CPU or a local dedicated microprocessor. Asynchronous 1200 bit/s DPSK (Bell 212A and V.22) and 300 baud FSK (Bell 103 and V.21) modes are supported.

The modern portion acts as a peripheral to the microprocessor. In both modes of operation, control information is stored in register memory at specific address locations. In the single-port mode, the modern section can be controlled through the 16C450 interface, with no external microcontroller required. The primary analog blocks are the DPSK modulator/demodulator, the FSK modulator/demodulator, the high and low band filters, the AGC, the special detect circuitry, and the DTMF tone generator. The analog functions are performed with switched capacitor technology.

#### PSK MODULATOR / DEMODULATOR

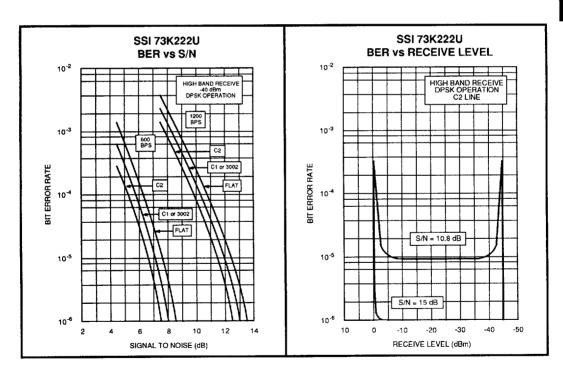

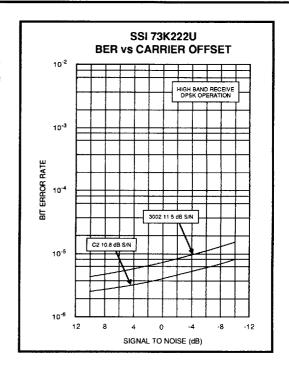

The SSI 73K222U modulates a serial bit stream into dibit pairs that are represented by four possible phase shifts as prescribed by the Bell 212A or V.22 standard. The baseband signal is then filtered to reduce intersymbol interference on the band limited 2-wire PSTN line. Transmission occurs using either a 1200 Hz (originate mode) or 2400 Hz carrier (answer mode). Demodulation is the reverse of the modulation process, with the incoming analog signal eventually decoded into dibits and converted back to a serial bit stream. The demodulator also recovers the clock which was encoded into the analog signal during modulation. The demodulator decodes either a 1200 Hz carrier (originate carrier) or a 2400 Hz carrier (answer carrier). The SSI 73K222U uses a phase-locked-loop coherent demodulation technique that offers inherently better performance than typical DPSK demodulators used by other manufacturers.

#### FSK MODULATOR/DEMODULATOR

The FSK modulator frequency modulates the analog output signal using two discrete frequencies to represent the binary data. In Bell 103, the standard frequencies of 1270 Hz and 1070 Hz (originate mark and space) and 2225Hz and 2025 Hz (answer mark and space) are used. V.21 mode uses 980 Hz and 1180 Hz (originate, mark and space) or 1650 Hz and 1850 Hz (answer, mark and space). Demodulation involves detecting the received frequencies and decoding them into the appropriate binary value.

#### **PASSBAND FILTERS AND EQUALIZERS**

A high and low band filter is included to shape the amplitude and phase response of the transmit signal and provide compromise delay equalization and rejection of out-of-band signals in the receive channel. Amplitude and phase equalization is necessary to compensate for distortion of the transmission line and to reduce intersymbol interference in the band limited receive signal. The transmit signal filtering approximates a 75% square root of raised Cosine frequency response characteristic.

#### **AGC**

The automatic gain control maintains a signal level at the input to the demodulators which is constant to within 1 dB. It corrects quickly for increases in signal which would cause clipping, and provides a total dynamic range of >45 dB.

#### SPECIAL DETECT CIRCUITRY

The special detect circuitry monitors the received analog signal to determine status or presence of carrier, call-progress tones, answer tone, and weak received signal (long loop condition). An unscrambled mark signal is also detected when the received data out of the DPSK demodulator before the descrambler has been high for 165.5 mS  $\pm 13.5$  mS. The appropriate status bit is set when one of these conditions changes and an interrupt is generated for all monitored conditions except long loop. The interrupts are disabled (masked) when the enable interrupt bit is set to a 0.

#### **DTMF GENERATOR**

The DTMF generator will output one of 16 standard dual-tones determined by a 4-bit binary value and TX DTMF mode bit previously loaded into the tone register. Tone generation is initiated when the DTMF mode is selected and the transmit enable (CR0 bit D1) is changed from a 0 to a 1.

#### **TEST FEATURES**

Test features such as analog loopback (ALB), remote digital loopback, local digital loopback, and internal pattern generators are also included.

#### LINE INTERFACE

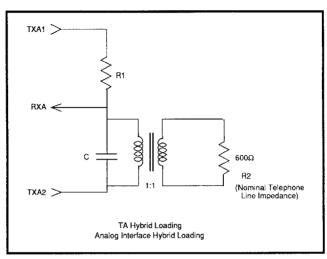

The line interface of the SSI 73K222U consists of a two-to-four wire hybrid, and an off-hook relay driver.

The two-to-four wire converter has a differential transmit output and requires only a line transformer and an external impedance matching resistor. Four-wire operation is also available by simply using either of the transmit output signals.

The relay driver output of the SSI 73K222U is an open drain signal capable of sinking 20 mA, which can control a line closure relay used to take the line off hook and to perform pulse dialing.

#### **AUDIO MONITOR**

An audio monitor output is provided which has a software programmable volume control. Its output is the received signal. The audio monitor output can directly drive a high impedance load, but an external power amplifier is necessary to drive a low-impedance

### PIN DESCRIPTION

#### **GENERAL**

| NAME   | DIP | PLCC | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                    |  |

|--------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VDD    | 40  | 44   | ı    | +5V Supply ±10%, bypass with a .1 and a 22μF capacitor to GND                                                                                                                                                                                                                                                                                                                  |  |

| GND    | 20  | 22   | 1    | System Ground                                                                                                                                                                                                                                                                                                                                                                  |  |

| VREF   | 19  | 21   | 0    | VREF is an internally generated reference voltage which is externally bypassed by a 0.1µF capacitor to the system ground.                                                                                                                                                                                                                                                      |  |

| ISET   | 9   | 11   |      | The analog current is set by connecting this pin to VDD through a $2M\Omega$ resistor. ISET should be bypassed to GND. Alternatively, an internal bias can be selected by connecting ISET to GND, which will result in a larger worst-case supply current due to the tolerance of on-chip resistors. Bypass with .1 $\mu$ F capacitor if resistor is used.                     |  |

| XTL1   | 25  | 27   | ı    | These pins are connections for the internal crystal                                                                                                                                                                                                                                                                                                                            |  |

| XTL2   | 24  | 26   | I    | oscillator requiring an 11.0592 MHz crystal (9216Hz x 1200). XTL2 can also be TTL driven from an external clock.                                                                                                                                                                                                                                                               |  |

| CLK    | 21  | 23   | 0    | Output Clock. This pin is selectable under processor control to be either the crystal frequency (which might be used as a processor clock) or the output of the baud generator.                                                                                                                                                                                                |  |

| RESET  | 10  | 12   |      | Reset. An active signal (high) on this pin will put the chip into an inactive state. The control register bits (except the Receiver Buffer, Transmitter Holding, and Divisor latches) will be reset. The output of the CLK pin will be set to the crystal frequency. An internal pull-down resistor permits power-on reset using a 0.1µF capacitor connected to the 5V supply. |  |

| STNDLN | 15  | 17   | l    | Single-port mode select (active high). In a single-port system there is no local microprocessor and all the modem control is done through the 16C450 parallel bus interface. The local microprocessor interface is replaced with UART control signals which allow the device to function as a digital UART as well as modem.                                                   |  |

### PIN DESCRIPTION (continued)

#### **UART INTERFACE**

| NAME           | DIP         | PLCC        | TYPE | DESCRIPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ION                                                                                                                                                 |                                                                    |  |

|----------------|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|

| UA0-UA2<br>UA3 | 37-39<br>12 | 41-43<br>14 |      | UART Address. These pins determine which of the UART registers is being selected during a read or write on the UART data bus. The contents of the DLAB bit in the UART's Line Control Register also control which register is referenced. In single-port mode, UA0-UA3 are latched when ADS goes high. In dual-port, only UA0-UA2 are used.                                                                                                                                                                        |                                                                                                                                                     |                                                                    |  |

| UDO-UD7        | 27-34       | 30-37       | 1/0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     | Data. Data or control information to the carried over these lines. |  |

| DISTR          | 35          | 38          | l    | internal UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Input Strobe. A low on this pin requests a read of the internal UART registers. Data is output on the D0-D7 lines if DISTR and CS2 are active. |                                                                    |  |

| DOSTR          | 36          | 39          | I    | Data Output Strobe. A low on this pin requests a write of the internal UART registers. Data on the D0-D7 lines are latched on the rising edge of DOSTR. Data is only written if both DOSTR and CS2 are active.                                                                                                                                                                                                                                                                                                     |                                                                                                                                                     |                                                                    |  |

| CS2            | 1           | 2           | l    | Chip Select. A low on this pin allows a read or write to the UART registers to occur. In single port mode, CS2 is latched on ADS.                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                     |                                                                    |  |

| INTRPT         | 5           | 7           | 0    | (3 state) UART Interrupt. This signal indicates that an interrupt condition on the UART side has occurred. If the Enable 8250A interrupt bit in the interrupt Enable Register is 0 the interrupt is gated by the DISTR signal to provide compatibility with the 8250B. The output can be put in a high impedance state with the OUT2 register bit in the Modem Control Register. In single-port mode, INTRPT also becomes valid when a modem interrupt signal is generated by the modem section's Detect Register. |                                                                                                                                                     |                                                                    |  |

| RXD            | 6           | 8           | I/O  | Function is<br>Control Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                     | mined by STNDLN pin and bit 7, Tone                                |  |

|                |             |             |      | STNDLN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D7                                                                                                                                                  |                                                                    |  |

| :              |             |             |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                   | RXD outputs data received by modem.                                |  |

|                |             |             |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                                   | RXD is electrically an input but signal is ignored.                |  |

|                |             |             |      | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                   | RXD is a serial input to UART.                                     |  |

### PIN DESCRIPTION (continued)

### **UART INTERFACE** (continued)

| TXD | 7 | 9 | 0 | Function is determined by STNDLN pin and bit 7, Tone Control Register: |    |                                 |

|-----|---|---|---|------------------------------------------------------------------------|----|---------------------------------|

|     |   |   |   | STNDLN                                                                 | D7 |                                 |

|     |   |   |   | 0                                                                      | 0  | TXD is a serial output of UART. |

|     |   |   |   | 1                                                                      | 0  | TXD is forced to a mark.        |

|     |   |   |   | Х                                                                      | 1  | TXD is a serial output of UART. |

#### **ANALOG / LINE INTERFACE**

| NAME         | DIP    | PLCC   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                         |

|--------------|--------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXA1<br>TXA2 | 3<br>4 | 4<br>5 | 0    | (differential) Transmitted Analog. These pins provide the analog output signals to be transmitted to the phone line. The drivers will differentially drive the impedance of the line transformer and the line matching resistor. An external hybrid can also be built using TXA1 as a single ended transmit signal. |

| RXA          | 16     | 18     | l    | Received Analog. This pin inputs analog information that is being received by the two-to-four wire hybrid. This input can also be taken directly from an external hybrid.                                                                                                                                           |

| SPKR         | 17     | 19     | 0    | Speaker Output. This pin outputs the received signal through a programmable attenuator stage, which can be used for volume control and disabling the speaker.                                                                                                                                                       |

| ÖН           | 18     | 20     | 0    | Off-hook relay driver. This signal is an open drain output capable of sinking 20mA and is used for controlling a relay. The output is the complement of the OH register bit in CR3.                                                                                                                                 |

### PIN DESCRIPTION (continued)

### **UART CONTROL INTERFACE (STNDLN = 1)**

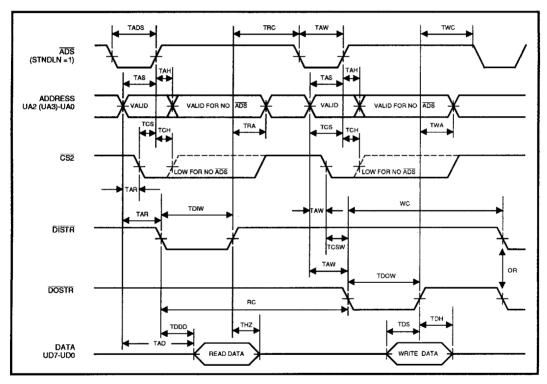

(See Figure 1: Single-port mode)

|      | 1. Single-po | r    |          |                                                                                                                                                                                                                                                                        |

|------|--------------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | DIP          | PLCC | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                            |

| ADS  | 23           | 25   |          | Address Strobe. ADS is used to latch address and chip select to simplify interfacing to a multiplexed Address/Data Bus. UA0-UA3 and CS2 are latched when the ADS signal goes high.                                                                                     |

| UA3  | 12           | 14   | <b>!</b> | UART Address Bit 3. UA3 is used in single-port mode to address the modem registers from the 16C450 interface. If UA3 is 0, the normal 16C450 registers are addressed by UA0-UA2 and if UA3 is 1, the modem registers are addressed. UA3 is latched when ADS goes high. |

| CTS  | 14           | 16   | l        | Clear to Send. This pin is the complement of CTS bit in the Modem Status Register. The signal is used in modem handshake control to signify that communications have been established and that data can be transmitted.                                                |

| DSR  | 13           | 15   |          | Data Set Ready. This pin is the complement of DSR bit in the Modem Status Register. The signal is used in modem handshake to signify that the modem is ready to establish communications.                                                                              |

| DCD  | 11           | 13   | l        | Data Carrier Detect. This pin is the complement of DCD bit in the Modem Status Register. The signal is used in modem control handshake to signify that the modem is receiving a carrier.                                                                               |

| DTR  | 22           | 24   | 0        | Data Terminal Ready.The DTR output is programmed through a bit in the Modem Control Register. The signal is used in modem handshake to signify that the 16C450 is available to communicate.                                                                            |

| RTS  | 2            | 3    | 0        | Request to Send. The RTS output is programmed through a bit in the Modem Control Register. The signal is used in modem handshake to signify that the 16C450 has data to transmit.                                                                                      |

| Rī   | 8            | 10   | l        | Ring Indicator. This Indicates that a telephone ringing signal is being received. This pin is the complement of the RI bit in the Modern Status Register.                                                                                                              |

### PIN DESCRIPTION (continued)

### MICROPROCESSOR INTERFACE (STNDLN = 0)

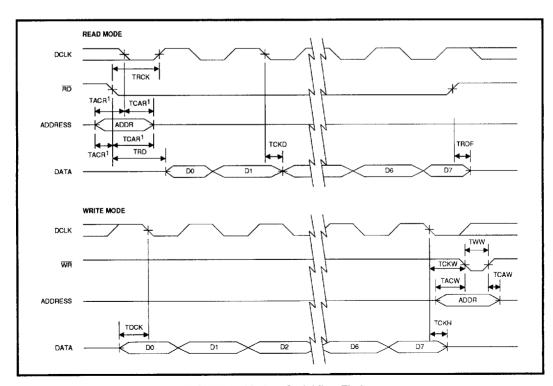

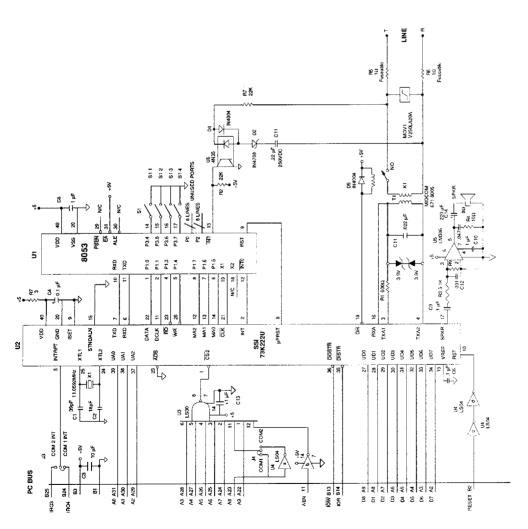

(See Figure 2: Dual-port mode)

| NAME    | DIP   | PLCC  | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA0-MA2 | 12-14 | 14-16 | I    | Modem Address Control. These lines carry register addresses for the modem registers and should be valid throughout any read or write operation.                                                                                                                                                                                                                                                                                                                                                                                                   |

| DATA    | 22    | 24    | I/O  | Serial Control Data. Serial control data to be read/written is clocked in/out on the falling edge of the DCLK pin. The direction of data transfer is controlled by the state of the RD pin. If the RD pin is active (low) the DATA line is an output. Conversely, if the RD pin is inactive (high) the DATA line is an input.                                                                                                                                                                                                                     |

| RD      | 23    | 25    | l    | Read. A low on this input informs the SSI 73K222U that control data or status information is being read by the processor from a modem register.                                                                                                                                                                                                                                                                                                                                                                                                   |

| WR      | 26    | 28    | l    | Write. A low on this input informs the SSI 73K222U that control data or status information is available for writing into a modem register. The procedure for writing is to shift in data LSB first on the DATA pin for eight consecutive cycles of DCLK and then to pulse WR low. Data is written on the rising edge of WR.                                                                                                                                                                                                                       |

| DCLK    | 11    | 13    | ı    | Data Clock. The falling edge of this clock is used to strobe control data for the modem registers in or out on the DATA pin. The normal procedure for a write is to shift in data LSB first on the DATA pin for eight consecutive cycles of DCLK and then to pulse WR low. Data is written on the rising edge of WR. The falling edge of the RD signal must continue for eight cycles of DCLK in order to read all eight bits of the reference register. Read data is provided LSB first. Data will not be output unless the RD signal is active. |

| INT     | 2     | 3     | 0    | (with weak pull-up) Modem Interrupt. This output signal is used to inform the modem processor that a change in a modem detect flag has occurred. The processor must then read the Modem Detect Register to determine which detect triggered the interrupt. INT will stay active until the processor reads the Modem Detect Register or does a full reset.                                                                                                                                                                                         |

| mPRST*  | 8     | 10    | 0    | Microprocessor Reset. This output signal is used to provide a hardware reset to the microprocessor. This signal is high if the RESET pin is high or the MCR bit D3 (OUT1) bit is set.                                                                                                                                                                                                                                                                                                                                                             |

<sup>\*</sup> NOTE: The mPRST pin is an upgraded function which was not included in the initial definition of the SSI 73K222U.

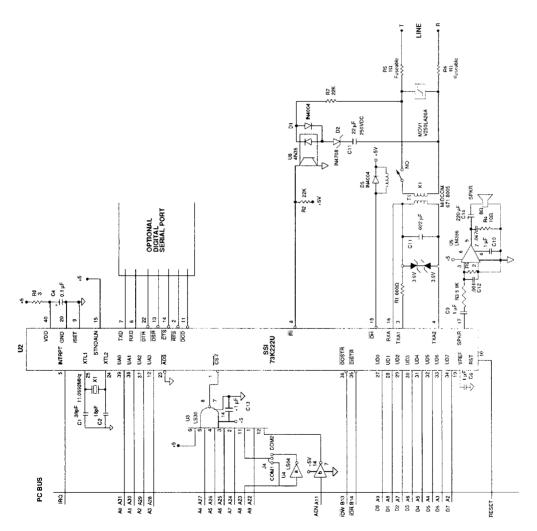

FIGURE 1: Single-Port Mode

In the single-port mode, the SSI 73K222U is designed to be accessed only by the main CPU using the same parallel bus utilized for data transfer. This mode is enabled when the STNDLN pin is at a logic "1". In the single port mode, internal registers are accessed by the main CPU to configure both the UART section and the

modem function, eliminating the need for a separate microcontroller. In this mode, multiplexed pins provide the  $\overline{CTS}$ ,  $\overline{DSR}$ ,  $\overline{DTR}$ ,  $\overline{DED}$  and  $\overline{Rl}$  signals normally associated with the UART function. A separate pin,  $\overline{ADS}$ , is used for bus control.

The serial control interface allows access to the control and status registers via a serial command port. In this mode the MA0, MA1, and MA2 lines provide register addresses for data passed through the DATA pin under control of the RD and WR lines. A read operation is initiated when the RD line is taken low. The next eight cycles of DCLK will then transfer out eight bits of the selected address location LSB first. A write takes place by shifting in eight bits of data LSB first for eight consecutive cycles of DCLK. WR is then pulsed low and data transfer into the selected register occurs on the rising edge of WR.

The dual-port mode allows use of a dedicated microprocessor for control of the modem function, and is enabled when the STNDLN pin = "0". This mode is useful for conventional plug-in card modem designs where it is necessary to make the modem function transparent to the main CPU. In this mode, the SSI 73K222U's multiplexed pins form the serial command bus used to communicate with the external microprocessor. The RI, CTS, DSR, DTR, and DCD logic functions must then be implemented using ports from the dedicated microprocessor.

#### **UART CONTROL REGISTER OVERVIEW**

|                                                 |     |                             |                                      |                                           |                                                | DATA BIT                                | NUMBER                                     |                                              | ***                                  |                                               |

|-------------------------------------------------|-----|-----------------------------|--------------------------------------|-------------------------------------------|------------------------------------------------|-----------------------------------------|--------------------------------------------|----------------------------------------------|--------------------------------------|-----------------------------------------------|

| REGISTE                                         | R   | UART<br>ADDRESS<br>UA3-UA0* | D7                                   | D6                                        | D5                                             | D4                                      | D3                                         | D2                                           | D1                                   | Do                                            |

| RECEIVER<br>BUFFER<br>REGISTER<br>(READ ONLY)   | RBR | 0000<br>DLAB = 0            | BIT 7<br>(MSB)                       | BIT 6                                     | BIT 5                                          | BIT 4                                   | BIT 3                                      | BIT 2                                        | BiT 1                                | BIT 0<br>(LSB)                                |

| TRANSMIT<br>HOLDING<br>REGISTER<br>(WRITE ONLY) | THR | 0000<br>DLAB = 0            | BIT 7<br>(MSB)                       | BIT 6                                     | BiT 5                                          | BIT 4                                   | ВІТ З                                      | BIT 2                                        | BIT 1                                | BIT 0<br>(LSB)                                |

| INTERRUPT<br>ENABLE<br>REGISTER                 | IER | 0001<br>DLAB = 0            | 0                                    | 0                                         | 0                                              | ENABLE<br>8250A/<br>16C450<br>INTERRUPT | ENABLE<br>MODEM<br>STATUS<br>INTERRUPT     | ENABLE<br>REC. LINE<br>STATUS<br>INTERRUPT   | ENABLE<br>THR<br>EMPTY<br>INTERRUPT  | ENABLE<br>REC. DATA<br>AVAILABLE<br>INTERRUPT |

| INTERRUPT<br>ID<br>REGISTER<br>(READ ONLY)      | IIR | 0010                        | 0                                    | 0                                         | D                                              | 0                                       | 0                                          | INTERRUPT<br>ID<br>BIT 1                     | INTERRUPT<br>ID<br>BIT 0             | "0" IF<br>INTERRUPT<br>PENDING                |

| LINE<br>CONTROL<br>REGISTER                     | LCR | 0011                        | DIVISOR<br>LATCH<br>ACCESS<br>(DLAB) | SET<br>BREAK                              | STICK<br>PARITY                                | EVEN<br>PARITY<br>SELECT<br>(EPS)       | PARITY<br>ENABLE<br>(PEN)                  | NUMBER<br>OF STOP<br>BITS<br>(STB)           | WORD<br>LENGTH<br>SELECT 1<br>(WLS1) | WORD<br>LENGTH<br>SELECT 0<br>(WLS0)          |

| MODEM<br>CONTROL<br>REGISTER                    | мся | 0100                        | 0                                    | 0                                         | 0                                              | LOOP                                    | ENABLE<br>INTERRUPT<br>(OUT2<br>IN 16C450) | mPRST<br>(OUT) IN<br>16C450)                 | REQUEST<br>TO SEND<br>(RTS)          | DATA<br>TERMINAL<br>READY<br>(DTR)            |

| LINE<br>STATUS<br>REGISTER                      | LSR | 0101                        | O                                    | TRANSMIT<br>SHIFT REG.<br>EMPTY<br>(TSRE) | TRANSMIT<br>HOLDING<br>REGISTER<br>EMPTY(THRE) | BREAK<br>INTERRUPT<br>(BI)              | FRAMING<br>ERROR<br>(FE)                   | PARITY<br>ERROR<br>(PE)                      | OVERRUN<br>ERROR<br>(OE)             | DATA<br>READY<br>(DR)                         |

| MODEM<br>STATUS<br>REGISTER<br>(READ ONLY)      | MSR | 0110                        | DATA<br>CARRIER<br>DETECT<br>(DCD)   | RING<br>INDICATOR<br>(RI)                 | DATA<br>SET READY<br>(DSR)                     | CLEAR<br>TO SEND<br>(CTS)               | DELTA<br>DATA CARR.<br>DETECT<br>(DDCD)    | TRAILING<br>EDGE RING<br>INDICATOR<br>(TERI) | DELTA<br>DATA SET<br>READY<br>(DDSR) | DELTA<br>CLEAR<br>TO SEND<br>(DCTS)           |

| SCRATCH<br>REGISTER                             | SCR | 0111                        | BIT 7                                | BIT 6                                     | BIT 5                                          | BIT 4                                   | BIT 3                                      | BIT 2                                        | BIT 1                                | ВІТ О                                         |

| DIVISOR<br>LATCH<br>(LS)                        | DLL | 0000<br>DLAB = 1            | BIT 7                                | BIT 6                                     | BIT 5                                          | BIT 4                                   | BIT 3                                      | BIT 2                                        | BIT 1                                | BIT 0                                         |

| DIVISOR<br>LATCH<br>(MS)                        | DLM | 0001<br>DLAB = 1            | BIT 15                               | BIT 14                                    | BIT 13                                         | BIT 12                                  | BIT 11                                     | BIT 10                                       | BIT 9                                | BIT 8                                         |

<sup>\*</sup> In single-port mode (STNDLN pin = 1), all four address lines UA3-UA0 are used to address the UART Control Registers.

<sup>\*</sup> In dual-port mode (STNDLN pin = 0), only three address lines UA2-UA0 are used to address the UART Control Registers; the UA3 pin becomes the MA2 pin in this mode.

### **MODEM CONTROL REGISTER OVERVIEW**

|                             |      | ADD         | RESS        |                          |                           |                                            | DATA BIT                                    | NUMBER                             |                                    |                               |                              |

|-----------------------------|------|-------------|-------------|--------------------------|---------------------------|--------------------------------------------|---------------------------------------------|------------------------------------|------------------------------------|-------------------------------|------------------------------|

| REGISTER                    |      | STN<br>0    | IDLN<br>1   | D7                       | D6                        | D5                                         | D4                                          | D3                                 | D2                                 | D1                            | Do                           |

| (120.0)                     |      | MA2-<br>MA0 | UA3-<br>UA0 |                          |                           |                                            |                                             |                                    |                                    |                               |                              |

| CONTROL<br>REGISTER<br>0    | CRO  | 000         | 1000        | MODULATION<br>OPTION     | 0                         | MODULATION<br>MODE                         | POWER<br>ON                                 | CHARACTER<br>SIZE 1<br>(READ ONLY) | CHARACTER<br>SIZE 0<br>(READ ONLY) | TRANSMIT<br>ENABLE            | ORIGINATE/<br>ANSWER         |

| CONTROL<br>REGISTER<br>1    | CR1  | 001         | 1001        | TRANSMIT<br>PATTERN<br>1 | TRANSMIT<br>PATTERN<br>0  | ENABLE<br>DETECT<br>INTERRUPT              | BYPASS<br>SCRAMBLER                         | CLK<br>CONTROL                     | RESET                              | TEST<br>MODE<br>1             | TEST<br>MODE<br>0            |

| DETECT<br>REGISTER          | DR   | 010         | 1010        | DEVICE<br>SIGNATURE<br>1 | DEVICE<br>SIGNATURE<br>0  | RECEIVE<br>DATA                            | UNSCR.<br>MARK<br>DETECT                    | CARRIER<br>DETECT                  | ANSWER<br>TONE<br>DETECT           | CALL<br>PROGRESS<br>DETECT    | LONG<br>LOOP<br>DETECT       |

| TONE<br>CONTROL<br>REGISTER | TONE | 011         | 1011        | RXD/TXD<br>CONTROL       | TRANSMIT<br>GUARD<br>TONE | TRANSMIT<br>ANSWER<br>TONE                 | TRANSMIT<br>DTMF                            | DTMF<br>3                          | DTMF<br>2                          | DTMF<br>1                     | DTMF 0<br>GUARD/ANS~<br>TONE |

| CONTROL<br>REGISTER<br>2    | CR2  | 100         | 1100        |                          |                           |                                            | RESERVED FO                                 | R FUTURE USE                       |                                    |                               |                              |

| CONTROL<br>REGISTER<br>3    | CR3  | 101         | 1101        | SPEAKER<br>VOLUME<br>1   | SPEAKER<br>VOLUME<br>0    | OFF-HOOK                                   | x                                           | x                                  | х                                  | х                             | x                            |

| SCRATCH<br>REGISTER         | SCR  | 110         | 1110        | BIT 7                    | BIT 6                     | BIT 5                                      | 8IT 4                                       | BIT 3                              | BIT 2                              | BIT 1                         | BIT 0                        |

| UART<br>CONTROL<br>REGISTER | UCR  | 111         | 1111        | TXCLK<br>(READ ONLY)     | х                         | REQUEST<br>TO SEND<br>(RTS)<br>(READ ONLY) | DATA<br>TERM. READY<br>(DTR)<br>(READ ONLY) | RING<br>INDICATOR<br>(RI)          | DATA<br>CARRIER<br>DETECT (DCD)    | DATA<br>SET<br>READY<br>(DSR) | CLEAR<br>TO<br>SEND<br>(CTS) |

#### **UART REGISTER BIT DESCRIPTIONS**

**UART SECTION**

RECEIVER BUFFER REGISTER (RBR) (READ ONLY)

STNDLN:

ADDRESS:

UA2 - UA0 = 000, DLAB = 0

UA3 - UA0 = 0000, DLAB = 0

This read only register contains the parallel received data with start, stop, and parity bits (if any) removed. The high order bits for less than 8 data bits/character will be set to 0.

TRANSMIT HOLDING REGISTER (THR) (WRITE ONLY)

STNDLN: ADDRESS:

UA2 - UA0 = 000, DLAB = 0

UA3 - UA0 = 0000, DLAB = 0

This write only register contains the parallel data to be transmitted. The data is sent LSB first with start, stop, and parity bits (if any) added to the serial bit stream as the data is transferred.

INTERRUPT ENABLE REGISTER (IER)

STNDLN: ADDRESS:

UA2 - UA0 = 001, DLAB = 0

UA3 - UA0 = 0001, DLAB = 0

This 8-bit register enables the four types of interrupts of the UART to separately activate the chip Interrupt (INTRPT) output signal. It is possible to totally disable the interrupt system by resetting bits 0 through 3 of the Interrupt Enable Register. Similarly, by setting the appropriate bits of this register to a logic 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INTRPT output from the chip. All other system functions operate in their normal manner, including the setting of the Line Status and Modern Status Registers.

| BIT NO. | NAME                                  | CONDITION | DESCRIPTION                                                                                                                                                                     |

|---------|---------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0      | Received Data                         | 1         | This bit enables the Received Data Available Interrupt when set to logic 1.                                                                                                     |

| D1      | Transmitter Holding<br>Register Empty | 1         | This bit enables the Transmitter Holding Register<br>Empty Interrupt, when set to logic 1.                                                                                      |

| D2      | Receiver Line<br>Status Interrupt     | 1         | This bit enables the Receiver Line Status Interrupt, when set to logic 1.                                                                                                       |

| D3      | Modem Status                          | 1         | This bit enables the Modem Status Register Interrupt when set to interrupt logic 1.                                                                                             |

| D4      | 8250A/16450                           | 1/0       | Set for compatibility with 8250A/16C450 UARTS. Reset this bit to disable the gating of the INTRPT interrupt line with the DISTR signal which is needed for 8250B compatibility. |

| D5 - D7 | Not Used                              | 0         | These three bits are always logic 0.                                                                                                                                            |

INTERRUPT ID REGISTER (IIR) (READ ONLY)

1

STNDLN: ADDRESS:

UA2 - UA0 = 010

**UA3 - UA0 = 0010**

**UART SECTION**

The IIR register gives prioritized information as to the status of interrupt conditions. When accessed, the IIR freezes the highest priority interrupt pending and no other interrupts are acknowledged until the particular interrupt is serviced by the CPU.

| BIT NO. | NAME                   | CONDITION   | DESCRIPTION                                                                                                                                                                                                                                                           |

|---------|------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0      | Interrupt Pending      | 0           | This bit can be used in either a hardwired priortized or polled environment to indicate whether an interrupt is pending. When bit 0 is a logic 0, an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. |

|         |                        | 1           | When bit 0 is a logic 1, no interrupt is pending.                                                                                                                                                                                                                     |

| D1, D2  | Interrupt ID bits 0, 1 | Table below | These two bits of the IIR are used to identify the highest priority interrupt pending as indicated in the following table.                                                                                                                                            |

| D3 - D7 | Not Used               | 0           | These five bits of the IIR are always logic 0.                                                                                                                                                                                                                        |

#### INTERRUPT PRIORITY TABLE

| D2 | D1 | D0 | PRIORITY | TYPE                               | SOURCE                                                                          | RESET                                                                                          |

|----|----|----|----------|------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 0  | 0  | 1  |          | None                               | None                                                                            | -                                                                                              |

| 1  | 1  | 0  | Highest  | Receiver Line Status               | Overrun Error,<br>Parity Error,<br>Framing Error or<br>Break Interrupt          | Reading the Line<br>Status Register                                                            |

| 1  | 0  | 0  | Second   | Receive Data<br>Available          | Receive Data<br>Available                                                       | Reading the Rovr.<br>Buffer Register                                                           |

| 0  | 1  | 0  | Third    | Transmit Holding<br>Register Empty | Transmit Holding<br>Register Empty                                              | Reading IIR Register<br>(if source of interrupt)<br>or Writing to Transmit<br>Holding Register |

| 0  | 0  | 0  | Fourth   | Modem Status                       | Clear to Send or<br>Data Set Ready or<br>Ring Indicator or<br>Data Carrier Det. | Reading the Modem<br>Status Register                                                           |

**LINE CONTROL REGISTER (LCR)**

STNDLN: ADDRESS: 0 UA2 - UA0 = 011

1 UA3 - UA0 = 0011 **UART SECTION**

The user specifies the format of the asynchronous data communications exchange via the Line Control Register. In addition to controlling the format, the user may retrieve the contents of the Line Control Register for inspection. This feature simplifies system programming and eliminates the need for separate storage in system memory of the line characteristics.

| BIT NO.  | NAME                 | COND   | ITION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|----------------------|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0       | Word Length Select 0 |        |       | Bits D0 and D1 select the number of data bits per character as shown:                                                                                                                                                                                                                                                                                                                                                                                                          |

| D1       | Word Length Select 1 | D1     | D0    | Word Length                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                      | 0      | 0     | 5 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                      | 0      | 1     | 6 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                      | 1      | 0     | 7 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>[</b> |                      | 1      | 1     | 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D2       | Number of Stop Bits  | 0 or 1 |       | This bit specifies the number of stop bits in each transmitted character. If bit 2 is a logic 0, one stop bit is generated in the transmitted data. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one-and-a-half stop bits are generated. If bit 2 is a logic 1 when either a 6, 7, or 8-bit word length is selected, two stop bits are generated. The receiver checks the first stop bit only, regardless of the number of stop bits selected. |

| D3       | Parity Enable        | 1      |       | This bit is the Parity Enable bit. When bit 3 is a logic 1, a parity bit is generated (transmit data) or checked (receive data) between the last data word bit and stop bit of the serial data. (The parity bit is used to produce an even or odd number of 1's when the data word bits and the parity bit are summed).                                                                                                                                                        |

| D4       | Even Parity Select   | 1 or 0 |       | This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, an odd number of logic 1's are transmitted or checked in the data word bits and parity bit. When bit 3 is a logic 1 and bit 4 is a logic 1, an even number of logic 1's are transmitted or checked.                                                                                                                                                                                    |

#### LINE CONTROL REGISTER (LCR) (Continued)

#### **UART SECTION**

| BIT NO. | NAME                               | CONDITION |    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |

|---------|------------------------------------|-----------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5      | Stick Parity                       | 1 or 0    |    | This bit is the Stick Parity bit. When bit 3 is a logic 1 and bit 5 is a logic 1, the parity bit is transmitted and checked by the receiver as a logic 0 if bit 4 is a logic 1 or as a logic 1 if bit 4 is a logic 0.                                                                                                                                   |

|         |                                    | D5        | D4 | Parity                                                                                                                                                                                                                                                                                                                                                  |

|         |                                    | 0         | 0  | ODD Parity                                                                                                                                                                                                                                                                                                                                              |

|         |                                    | 0         | 1  | EVEN Parity                                                                                                                                                                                                                                                                                                                                             |

|         |                                    | 1         | 0  | MARK Parity                                                                                                                                                                                                                                                                                                                                             |

|         |                                    | 1         | 1  | SPACE Parity                                                                                                                                                                                                                                                                                                                                            |

| D6      | Set Break                          | 1         |    | Output of modem is set to a spacing state. When the modem is transmitting DPSK data if the Set Break bit is held for one full character (start, data, parity, stop) the break will be extended to 2 N + 3 space bits (where N = # data bits + parity bit + 1 start + 1 stop). Any data bits generated during this time will be ignored. See note below. |

| D7      | Divisor Latch Access<br>Bit (DLAB) | 1         |    | This bit is the Divisor Latch Access Bit (DLAB). It must be set high (logic 1) to access the Divisor Latches of the baud generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.                                                    |

NOTE: This feature enables the CPU to alert a terminal in a computer communications system. If the following sequence is followed, no erroneous or extraneous characters will be transmitted because of the break.

- 1. Load an all 0's pad character in response to THRE.

- 2. Set break in response to the next THRE.

- 3. Wait for the Transmitter to be idle. (TSRE = 1), and clear break when normal transmission has to be restored.

During the break, the Transmitter can be used as a character timer to accurately establish the break duration.

**MODEM CONTROL REGISTER (MCR)**

STNDLN: ADDRESS: 0 UA2 - UA0 = 100

1 UA3 - UA0 = 0100 **UART SECTION**

The MCR register controls the interface with the modem. Bits D1 and D0 are also available as read only bits in the UART Control Register in the Modem Registers. In single-port mode, bits D1 and D0 are available inverted at the  $\overline{\text{RTS}}$  and  $\overline{\text{DTR}}$  pins.

| BIT NO.       | NAME                                 | CONDITION              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|---------------|--------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0            | DTR                                  | 1                      | This bit controls the Data Terminal Ready (DTR) output. When bit 0 is set to a logic 1, the DTR output is forced to a logic 0. When bit 0 is reset to a logic 0, the DTR output is forced to a logic 1.                                                                                                                                         |

| D1            | RTS                                  | 1                      | This bit controls the Request to Send (RTS) output. When bit 1 is set to a logic 1, the RTS output is forced to a logic 0. When bit 1 is reset to a logic 0, the RTS output is forced to a logic 1.                                                                                                                                             |

| D2            | mPRST*<br>(OUT1 in 16C450)           | 1                      | In single-port mode inactive unless loop = 1, then functions as below (D4). In dual-port mode the mPRST pin is the logical OR of this bit and the RESET pin.                                                                                                                                                                                    |

| D3            | Enable Interrupt<br>(OUT2 in 16C450) | 0                      | Sets INTRPT pin to high impedance if STNDLN = 1.                                                                                                                                                                                                                                                                                                |

|               |                                      | 1                      | INTRPT output enabled.                                                                                                                                                                                                                                                                                                                          |

| D4            | LOOP                                 | 1                      | This bit provides a local loopback feature for diagnostic testing of the UART portion of the SSI 73K222U. When bit D4 is set to logic 1, the following occurs:                                                                                                                                                                                  |

|               |                                      |                        | TXD is forced to mark, RXD is ignored.                                                                                                                                                                                                                                                                                                          |

|               |                                      |                        | The output of the Transmitter is looped to the Receiver.                                                                                                                                                                                                                                                                                        |

|               |                                      |                        | The four modem control inputs to the UART (CTS, DSR, DCD, and RI) are ignored and the UART signals RTS, DTR, Enable Interrupt, and mPRST are forced inactive.                                                                                                                                                                                   |

|               |                                      |                        | 4. The UART signals RTS, DTR, Enable Interrupt, and mPRST are internally connected to the four control signals CTS, DSR, DCD and RI respectively. Note that the Modem Status Register Interrupts are now controlled by the lower four bits of the Modem Control Register. The interrupts are still controlled by the Interrupt Enable Register. |

| D5 - D7       |                                      | 0                      | These bits are permanently set to logic 0.                                                                                                                                                                                                                                                                                                      |

| * Note: The m | nPRST bit has an upgraded funct      | ion which was not incl | uded in the initial definition of the SSI 73K222U.                                                                                                                                                                                                                                                                                              |

LINE STATUS REGISTER (LSR)

STNDLN: ADDRESS:

0 UA2 - UA0 = 101 1

UA3 - UA0 = 0101

**UART SECTION**

This register provides status information to the CPU concerning the data transfer.

| BIT NO. | NAME | CONDITION | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |

|---------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0      | DR   | 1         | The Data Ready (DR) bit is set to a 1 whenever a complete incoming character has been received and transferred into the Receiver Buffer Register. Data Ready is reset to 0 by reading the data in the Receiver Buffer Register or by writing a 0 into it from the processor.                                                  |

| D1      | OE   | 1         | The Overrun Error (OE) bit indicates that the data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, thereby destroying the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register. |

| D2      | PE   | 1         | The Parity Error (PE) bit indicates that the received character did not have the correct parity. The bit is reset to 0 whenever the CPU reads the Line Status Register.                                                                                                                                                       |

| D3      | FE   | 1         | The Framing Error (FE) bit indicates that the received character did not have a valid stop bit. The FE indicator is reset whenever the CPU reads the contents of the Line Status Register. A framing error will not occur in DPSK receive from the modem due to the fact that missing stop bits are reinserted.               |

| D4      | Ві   | 1         | The Break Interrupt (BI) bit indicates that a break has been received. A break occurs whenever the received data is held to 0 for a full data word (start + data + stop) or for two full data words when receiving in DPSK mode from the modem. The BI bit is reset to 0 whenever the CPU reads the Line Status Register.     |

| D5      | THRE | 1         | The Transmit Holding Register Empty (THRE) indicates that the Transmitter is ready to accept a new character for transmission. The THRE bit is reset when the CPU loads a character into the Transmit Holding Register.                                                                                                       |

| D6      | TSRE | 1         | The Transmit Shift Empty (TSRE) indicates that both the Transmit Holding Register and the Transmit Shift Registers are empty.                                                                                                                                                                                                 |

| D7      | -    | 0         | Always zero.                                                                                                                                                                                                                                                                                                                  |

**MODEM STATUS REGISTER (MSR) (READ ONLY)**

STNDLN: ADDRESS: 0 UA2 - UA0 = 110

UA3 - UA0 = 0110

**UART SECTION**