# S1D15E06 Series

| NOTICE                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No part of this material may be reproduced or duplicated in any from or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notics. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material                           |

| or due to its application or use in any product or circuit and, further, there is no repersesnation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that |

| anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products                                                                                                                                 |

| under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.                                                                                                                                             |

©SEIKO EPSON CORPORATION 2003, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

# **Contents**

| 1.  | DESCRIPTION                                        | 1    |

|-----|----------------------------------------------------|------|

| 2.  | FEATURES                                           | 1    |

| 3.  | BLOCK DIAGRAM                                      | 2    |

| 4.  | PIN ASSIGNMENT                                     | 3    |

| 5.  | PIN DESCRIPTION                                    | 7    |

| 6.  | FUNCTIONAL DESCRIPTION                             | . 11 |

| 7.  | COMMAND                                            | . 27 |

| 8.  | ABSOLUTE MAXIMUM RATINGS                           | 50   |

| 9.  | DC CHARACTERISTICS                                 | . 51 |

| 10. | TIMING CHARACTERISTICS                             | . 58 |

| 11. | MPU INTERFACE (Reference example)                  | 66   |

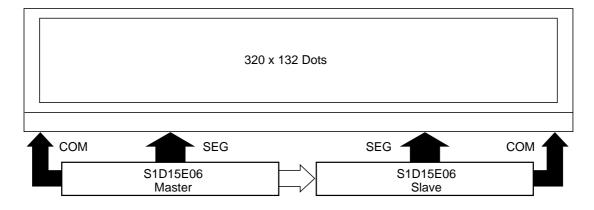

| 12. | CONNECTION BETWEEN LCD DRIVERS (Reference example) | 67   |

| 13. | LCD PANEL WIRING (Reference example)               | 68   |

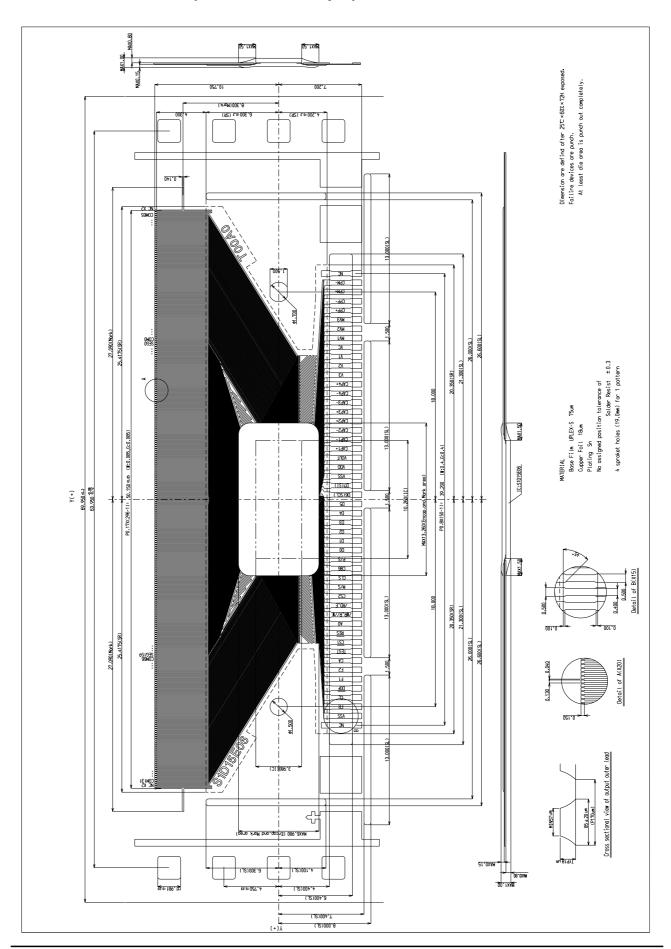

| 14. | S1D15E06T00A*** TCP PIN LAYOUT                     | 69   |

| 15. | TCP DIMENSIONS (Reference example)                 | . 70 |

| 16. | CAUTIONS                                           | . 71 |

#### 1. DESCRIPTION

The S1D15E06 series is a single chip MLS driver for dot matrix liquid crystal displays which can be directly connected to the microcomputer bus. It accepts the 8-bit parallel or serial display data from the microcomputer to store the data in the on-chip display data RAM, and issues liquid crystal drive signals independently of the microcomputer.

The S1D15E06 series provides both 4 gray-scale display and binary display. It incorporates a display data RAM  $(132 \times 160 \times 2 \text{ bits})$ . In the case of 4 gray-scale display, 2 bits of the on-chip RAM respond to one-dot pixels, while in the case of binary display, 1 bit of the on-chip RAM respond to one-dot pixels.

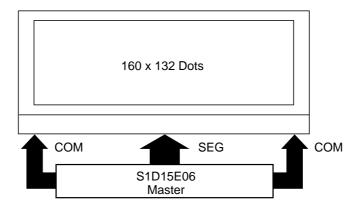

The S1D15E06 series features 132 common output circuits and 160 segment output circuits. A single chip provides a display of 10 characters by 8 lines with 132  $\times$  160 dots (16  $\times$  16 dots) and display of 13 characters by 11 lines by the 12  $\times$  12 dot-character font.

Display data RAM read/write operations do not require operation clock from outside, thereby ensuring operation with the minimum current consumption. Furthermore, it incorporates a LCD-drive power supply characterized by low power consumption and a CR oscillator circuit for display clock; therefore, the display system of a handy and high-performance instrument can be realized by use of the minimum current consumption and minimum chip configuration.

### 2. FEATURES

• Direct RAM data display by display data RAM

• 4 gray-scale display

(Normally white in normal display mode) RAM bit data (high order and low order)

(1,1): gray-scale 3, black

(1,0): gray-scale 2

(0,1): gray-scale 1

(0,0): gray-scale 0, white

· Binary display

(Normally white display is in normal mode) RAM bit data

"1": On and black

"0": Off and white

• RAM capacity

$132 \times 160 \times 2 = 42,240$  bits

Liquid crystal drive circuit

132 common outputs and 160 segment outputs

- High-speed 8-bit MPU interface (directly connectable to the MPUs of both 80/68 series) /serial interface possible

- A variety of command functions

Area scroll display, partial display, n-line reversal,

display data RAM address control, contrast control,

display ON/OFF, display normal/reverse rotation,

display all lighting ON/OFF, liquid crystal drive

power supply circuit control, display clock built-in

oscillator circuit control

- Lower power MLS drive technology Built-in high precision voltage regulation function

- High precision CR oscillator circuit incorporated

- Very low power consumption

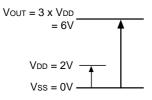

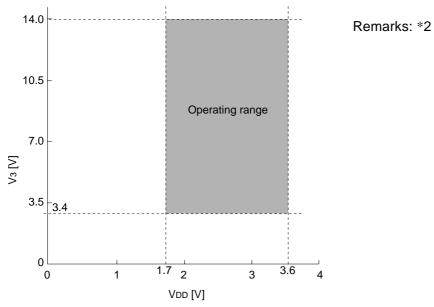

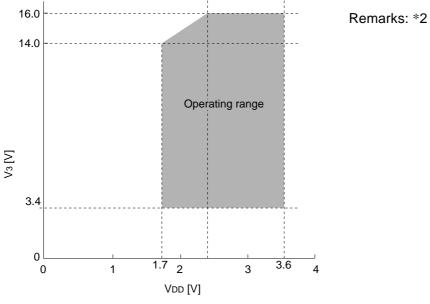

• Power supply

Logic power supply: VDD - VSS = 1.7 to 3.6 V Liquid crystal drive power supply:

$V_3 - V_{SS} = 3.4 \text{ to } 14.0 \text{ V } (S1D15E06D01****),$

$V_3 - V_{SS} = 3.4 \text{ to } 16.0 \text{ V } (S1D15E06D03****)$

- Wide operation temperature range: -40 to 85°C

- CMOS process

- Shipping form : Bare chips, TCP

- Light and radiation proof measures are not taken in designing.

# Series specifications

| Product name    | Bias | LCD driving voltage range | Duty (Max.) | Form of shipping | Chip thickness |

|-----------------|------|---------------------------|-------------|------------------|----------------|

| S1D15E06D01B000 | 1/7  | 3.4V~14.0V                | 1/132       | Bare chip        | 0.400mm        |

| S1D15E06D03B000 | 1/7  | 3.4V~16.0V                | 1/132       | Bare chip        | 0.400mm        |

| S1D15E06D01E000 | 1/7  | 3.4V~14.0V                | 1/132       | Bare chip        | 0.625mm        |

| S1D15E06D03E000 | 1/7  | 3.4V~16.0V                | 1/132       | Bare chip        | 0.625mm        |

| S1D15E06T00A00A | 1/7  | 3.4V~14.0V                | 1/132       | TCP              | _              |

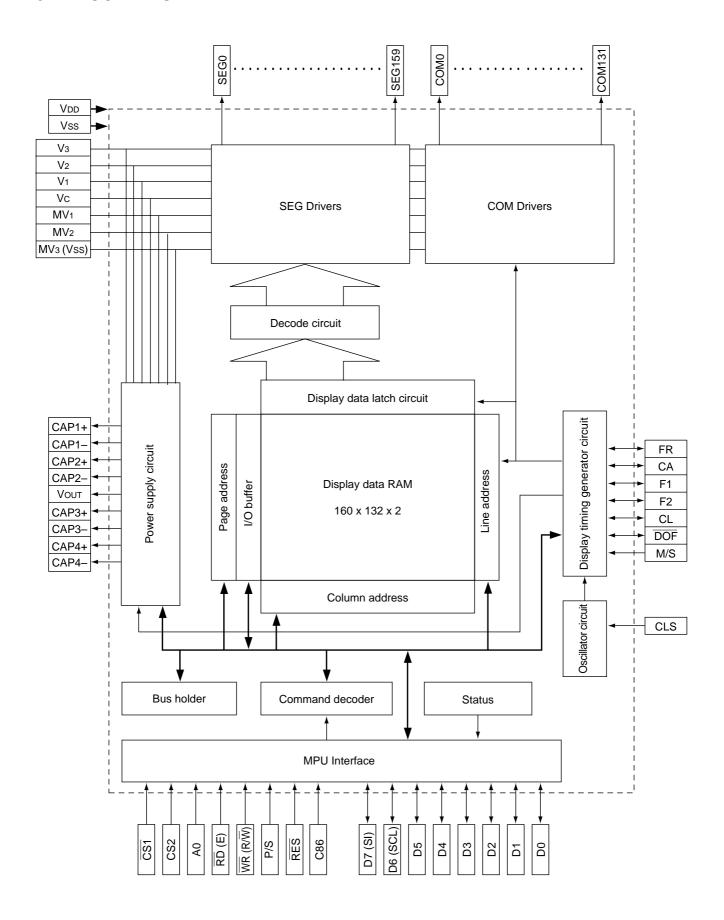

# 3. BLOCK DIAGRAM

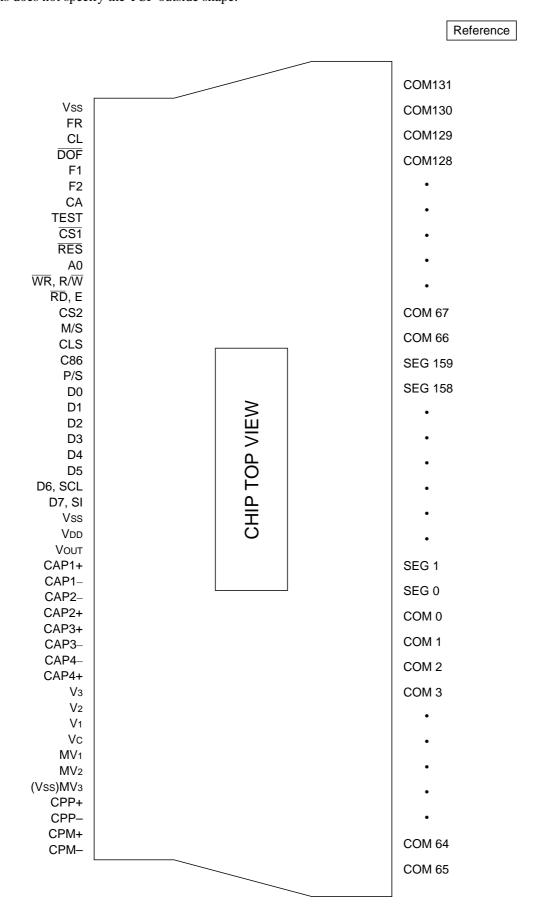

# 4. PIN ASSIGNMENT

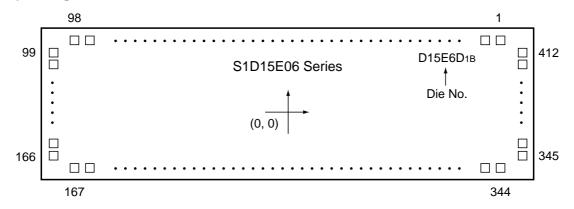

# 4.1 Chip Assignment

|           | ltom                          | Size    | <b>;</b> | l l m i t |  |  |

|-----------|-------------------------------|---------|----------|-----------|--|--|

|           | Item                          | X       | Υ        | Unit      |  |  |

|           | Chip size                     | 10.26 × | 3.98     | mm        |  |  |

|           | Chip thickness                | 0.4/0.6 | 25       | mm        |  |  |

|           | Bump pitch                    | 50 (Mi  | μm       |           |  |  |

| Bump size | PAD No.1 to 98                | 70 ×    | 92       | μm        |  |  |

|           | PAD No.99 to 166, 345 to 412  | 116 ×   | 33       | μm        |  |  |

|           | PAD No.167 to 175, 336 to 344 | 61 ×    | 61       | μm        |  |  |

|           | PAD No.176 to 335             | 33 ×    | 116      | μm        |  |  |

|           | Bump height                   | 22.5 (T | yp.)     | μm        |  |  |

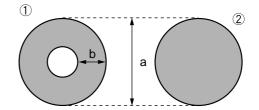

# 4.2 Alignment mark

Alignment coordinate

Mark size

$a=80\;\mu m$

$b = 20 \mu m$

# 4.3 Pad Center Coordinates

Unit: µm

|            |             |      |      | _          |             |          |      |            |             |       | nii: μm         |

|------------|-------------|------|------|------------|-------------|----------|------|------------|-------------|-------|-----------------|

| PAD<br>No. | Pin<br>Name | X    | Y    | PAD<br>No. | Pin<br>Name | X        | Y    | PAD<br>No. | Pin<br>Name | X     | Y               |

| 1          | NC          | 4494 | 1830 | 51         | D4          | -170     | 1830 | 101        | COM64       | -4958 | 1575            |

| 2          | NC          | 4402 |      | 52         | D5          | -262     |      | 102        | COM63       |       | 1525            |

| 3          | TEST0       | 4310 |      | 53         | D6, SCL     | -354     |      | 103        | COM62       |       | 1475            |

| 4          | TEST1       | 4218 |      | 54         | D7, SI      | -446     |      | 104        | COM61       |       | 1425            |

| 5          | TEST2       | 4126 |      | 55         | Vss         | -538     |      | 105        | COM60       |       | 1375            |

| 6          | TEST3       | 4034 |      | 56         | Vss         | -630     |      | 106        | COM59       |       | 1325            |

| 7          | TEST4       | 3942 |      | 57         | Vss         | -722     |      | 107        | COM58       |       | 1275            |

| 8          | TEST5       | 3850 |      | 58         | Vdd         | -814     |      | 108        | COM57       |       | 1225            |

| 9          | Vss         | 3742 |      | 59         | VDD         | -906     |      | 109        | COM56       |       | 1175            |

| 10         | TEST6       | 3634 |      | 60         | VDD         | -998     |      | 110        | COM55       |       | 1125            |

| 11         | TEST7       | 3542 |      | 61         | Vout        | -1090    |      | 111        | COM54       |       | 1075            |

| 12         | TEST8       | 3450 |      | 62         | Vout        | -1182    |      | 112        | COM53       |       | 1025            |

| 13         | TEST9       | 3358 |      | 63         | CAP1+       | -1274    |      | 113        | COM52       |       | 975             |

| 14         | TEST10      | 3266 |      | 64         | CAP1+       | -1366    |      | 114        | COM51       |       | 925             |

| 15         | TEST11      | 3174 |      | 65         | CAP1-       | -1458    |      | 115        | COM50       |       | 875             |

| 16         | TEST12      | 3082 |      | 66         | CAP1-       | -1550    |      | 116        | COM49       |       | 825             |

| 17         | TEST13      | 2990 |      | 67         | CAP2-       | -1642    |      | 117        | COM48       |       | 775             |

| 18         | TEST14      | 2898 |      | 68         | CAP2-       | -1734    |      | 118        | COM47       |       | 725             |

| 19         | TEST15      | 2806 |      | 69         | CAP2+       | -1826    |      | 119        | COM46       |       | 675             |

| 20         | TEST16      | 2714 |      | 70         | CAP2+       | -1918    |      | 120        | COM45       |       | 625             |

| 21         | TEST17      | 2622 |      | 71         | CAP3+       | -2010    |      | 121        | COM44       |       | 575             |

| 22         | TEST18      | 2530 |      | 72         | CAP3+       | -2102    |      | 122        | COM43       |       | 525             |

| 23         | Vss         | 2422 |      | 73         | CAP3-       | -2194    |      | 123        | COM42       |       | 475             |

| 24         | FR          | 2314 |      | 74         | CAP3-       | -2286    |      | 124        | COM41       |       | 425             |

| 25         | CL          | 2222 |      | 75         | CAP4-       | -2378    |      | 125        | COM40       |       | 375             |

| 26         | DOF         | 2130 |      | 76         | CAP4-       | -2470    |      | 126        | COM39       |       | 325             |

| 27         | F1          | 2038 |      | 77         | CAP4+       | -2562    |      | 127        | COM38       |       | 275             |

| 28         | F2          | 1946 |      | 78         | CAP4+       | -2654    |      | 128        | COM37       |       | 225             |

| 29         | CA          | 1854 |      | 79         | V3          | -2746    |      | 129        | COM36       |       | 175             |

| 30         | Vss         | 1762 |      | 80         | V3          | -2838    |      | 130        | COM35       |       | 125             |

| 31         | TEST        | 1670 |      | 81         | V2          | -2930    |      | 131        | COM34       |       | 75              |

| 32         | CS1         | 1578 |      | 82         | V2          | -3022    |      | 132        | COM33       |       | 25              |

| 33         | RES         | 1486 |      | 83         | V1          | -3114    |      | 133        | COM32       |       | -25             |

| 34         | A0          | 1394 |      | 84         | V1          | -3206    |      | 134        | COM31       |       | -75             |

| 35         | WR, R/W     | 1302 |      | 85         | Vc          | -3298    |      | 135        | COM30       |       | -125            |

| 36         | RD, E       | 1210 |      | 86         | Vc          | -3390    |      | 136        | COM29       |       | <b>-175</b>     |

| 37         | CS2         | 1118 |      | 87         | MV1         | -3482    |      | 137        | COM28       |       | -225            |

| 38         | VDD         | 1026 |      | 88         | MV1         | -3574    |      | 138        | COM27       |       | -275            |

| 39         | M/S         | 934  |      | 89         | MV2         | -3666    |      | 139        | COM26       |       | -325            |

| 40         | Vss         | 842  |      | 90         | MV2         | -3758    |      | 140        | COM25       |       | -375            |

| 41         | CLS         | 750  |      | 91         | МVз         | -3850    |      | 141        | COM24       |       | -425            |

| 42         | VDD         | 658  |      | 92         | MV3         | -3942    |      | 142        | COM23       |       | -475            |

| 43         | C86         | 566  |      | 93         | CPP+        | -4034    |      | 143        | COM22       |       | <b>-525</b>     |

| 44         | Vss         | 474  |      | 94         | CPP-        | -4126    |      | 144        | COM21       |       | <b>-575</b>     |

| 45         | P/S         | 382  |      | 95         | CPM+        | -4218    |      | 145        | COM20       |       | -625            |

| 46         | VDD         | 290  |      | 96         | CPM-        | -4310    |      | 146        | COM19       |       | <del>-675</del> |

| 47         | D0          | 198  |      | 97         | NC          | -4402    |      | 147        | COM18       |       | -725            |

| 48         | D1          | 106  |      | 98         | NC          | -4494    | 4075 | 148        | COM17       |       | -775            |

| 49         | D2          | 14   |      | 99         | NC          | -4958    | 1675 | 149        | COM16       | ]     | -825            |

| 50         | D3          | -78  | ▼    | 100        | COM65       | <b>↓</b> | 1625 | 150        | COM15       | _ ▼   | -875            |

Unit: µm

| PAD Pin<br>No. Name          |                  | I I   |     |       |                  |       |     |                  |      |       |  |

|------------------------------|------------------|-------|-----|-------|------------------|-------|-----|------------------|------|-------|--|

| No. Name                     | X                | Υ     | PAD | Pin   | X                | Υ     | PAD | Pin              | X    | Y     |  |

|                              |                  |       | No. | Name  | ^                | •     | No. | Name             | ^    | •     |  |

| 151   COM14                  | -4958            | -925  | 201 | SEG25 | -2725            | -1818 | 251 | SEG75            | -225 | -1818 |  |

| 152   COM13                  |                  | -975  | 202 | SEG26 | -2675            |       | 252 | SEG76            | -175 |       |  |

| 153   COM12                  |                  | -1025 | 203 | SEG27 | -2625            |       | 253 | SEG77            | -125 |       |  |

| 154   COM11                  |                  | -1075 | 204 | SEG28 | -2575            |       | 254 | SEG78            | -75  |       |  |

| 155   COM10                  |                  | -1125 | 205 | SEG29 | -2525            |       | 255 | SEG79            | -25  |       |  |

| 156 COM9                     |                  | -1175 | 206 | SEG30 | -2475            |       | 256 | SEG80            | 25   |       |  |

| 157 COM8                     |                  | -1225 | 207 | SEG31 | -2425            |       | 257 | SEG81            | 75   |       |  |

| 158 COM7                     |                  | -1275 | 208 | SEG32 | -2375            |       | 258 | SEG82            | 125  |       |  |

| 159 COM6                     |                  | -1325 | 209 | SEG33 | -2325            |       | 259 | SEG83            | 175  |       |  |

| 160 COM5                     |                  | -1375 | 210 | SEG34 | -2275            |       | 260 | SEG84            | 225  |       |  |

| 161 COM4                     |                  | -1425 | 211 | SEG35 | -2225            |       | 261 | SEG85            | 275  |       |  |

| 162 COM3                     |                  | -1475 | 212 | SEG36 | -2175            |       | 262 | SEG86            | 325  |       |  |

| 163 COM2                     |                  | -1525 | 213 | SEG37 | -2125            |       | 263 | SEG87            | 375  |       |  |

| 164 COM1                     |                  | -1575 | 214 | SEG38 | -2075            |       | 264 | SEG88            | 425  |       |  |

| 165 COM0                     |                  | -1625 | 215 | SEG39 | -2025            |       | 265 | SEG89            | 475  |       |  |

| 166 NC                       | ↓                | -1675 | 216 | SEG40 | -1975            |       | 266 | SEG90            | 525  |       |  |

| 167 NC                       | <del>-4704</del> | -1846 | 217 | SEG41 | -1925            |       | 267 | SEG91            | 575  |       |  |

| 167 NC                       | -4621            | -1040 | 218 | SEG42 | -1875            |       | 268 | SEG92            | 625  |       |  |

| 169 NC                       | -4539            |       | 219 | SEG43 | -1825            |       | 269 | SEG93            | 675  |       |  |

|                              | 1                |       |     |       |                  |       |     |                  |      |       |  |

| 170 NC                       | -4456<br>4274    |       | 220 | SEG44 | -1775            |       | 270 | SEG94            | 725  |       |  |

| 171 NC                       | -4374            |       | 221 | SEG45 | -1725            |       | 271 | SEG95            | 775  |       |  |

| 172 NC                       | -4291            |       | 222 | SEG46 | -1675            |       | 272 | SEG96            | 825  |       |  |

| 173 NC                       | -4209            |       | 223 | SEG47 | -1625            |       | 273 | SEG97            | 875  |       |  |

| 174 NC                       | -4126            |       | 224 | SEG48 | -1575            |       | 274 | SEG98            | 925  |       |  |

| 175 NC                       | -4044            | •     | 225 | SEG49 | -1525            |       | 275 | SEG99            | 975  |       |  |

| 176   SEG0                   | -3975            | -1818 | 226 | SEG50 | -1475            |       | 276 | SEG100           | 1025 |       |  |

| 177   SEG1                   | -3925            |       | 227 | SEG51 | -1425            |       | 277 | SEG101           | 1075 |       |  |

| 178   SEG2                   | -3875            |       | 228 | SEG52 | -1375            |       | 278 | SEG102           | 1125 |       |  |

| 179   SEG3                   | -3825            |       | 229 | SEG53 | -1325            |       | 279 | SEG103           | 1175 |       |  |

| 180   SEG4                   | -3775            |       | 230 | SEG54 | -1275            |       | 280 | SEG104           | 1225 |       |  |

| 181 SEG5                     | -3725            |       | 231 | SEG55 | -1225            |       | 281 | SEG105           | 1275 |       |  |

| 182 SEG6                     | -3675            |       | 232 | SEG56 | -1175            |       | 282 | SEG106           | 1325 |       |  |

| 183 SEG7                     | -3625            |       | 233 | SEG57 | -1125            |       | 283 | SEG107           | 1375 |       |  |

| 184 SEG8                     | -3575            |       | 234 | SEG58 | -1075            |       | 284 | SEG108           | 1425 |       |  |

| 185 SEG9                     | -3525            |       | 235 | SEG59 | -1025            |       | 285 | SEG109           | 1475 |       |  |

| 186 SEG10                    | -3475            |       | 236 | SEG60 | -975             |       | 286 | SEG110           | 1525 |       |  |

| 187 SEG11                    | -3425            |       | 237 | SEG61 | -925             |       | 287 | SEG111           | 1575 |       |  |

| 188 SEG12                    | -3375            |       | 238 | SEG62 | <del>-875</del>  |       | 288 | SEG112           | 1625 |       |  |

| 189 SEG13                    | -3325            |       | 239 | SEG63 | <del>-</del> 825 |       | 289 | SEG113           | 1675 |       |  |

| 190 SEG14                    | -3275            |       | 240 | SEG64 | -775             |       | 290 | SEG114           | 1725 |       |  |

| 191 SEG15                    | -3225            |       | 241 | SEG65 | -725             |       | 291 | SEG115           | 1775 |       |  |

| 191   SEG15                  | -3175            |       | 242 | SEG66 | -675             |       | 292 | SEG116           | 1825 |       |  |

| 192   SEG 16<br>193   SEG 17 | -3175<br>-3125   |       | 242 | SEG67 | -675<br>-625     |       | 292 | SEG116<br>SEG117 | 1875 |       |  |

|                              | 1                |       |     |       |                  |       |     |                  |      |       |  |

| 194   SEG18                  | -3075            |       | 244 | SEG68 | -575<br>525      |       | 294 | SEG118           | 1925 |       |  |

| 195   SEG19                  | -3025            |       | 245 | SEG69 | -525             |       | 295 | SEG119           | 1975 |       |  |

| 196   SEG20                  | -2975            |       | 246 | SEG70 | -475             |       | 296 | SEG120           | 2025 |       |  |

| 197   SEG21                  | -2925            |       | 247 | SEG71 | <b>-425</b>      |       | 297 | SEG121           | 2075 |       |  |

| 198 SEG22                    | -2875            |       | 248 | SEG72 | -375             |       | 298 | SEG122           | 2125 |       |  |

| 199 SEG23                    | -2825            |       | 249 | SEG73 | -325             |       | 299 | SEG123           | 2175 |       |  |

| 200   SEG24                  | <del>-2775</del> | 🗼     | 250 | SEG74 | -275             |       | 300 | SEG124           | 2225 | ♦     |  |

Unit: µm

|            | 1           |      |       |            |             |      |                  |            |             | `    | חונ: μm |

|------------|-------------|------|-------|------------|-------------|------|------------------|------------|-------------|------|---------|

| PAD<br>No. | Pin<br>Name | X    | Y     | PAD<br>No. | Pin<br>Name | X    | Y                | PAD<br>No. | Pin<br>Name | X    | Y       |

| 301        | SEG125      | 2275 | -1818 | 351        | COM71       | 4958 | -1375            | 401        | COM121      | 4958 | 1125    |

| 302        | SEG126      | 2325 |       | 352        | COM72       |      | -1325            | 402        | COM122      |      | 1175    |

| 303        | SEG127      | 2375 |       | 353        | COM73       |      | -1275            | 403        | COM123      |      | 1225    |

| 304        | SEG128      | 2425 |       | 354        | COM74       |      | -1225            | 404        | COM124      |      | 1275    |

| 305        | SEG129      | 2475 |       | 355        | COM75       |      | -1175            | 405        | COM125      |      | 1325    |

| 306        | SEG130      | 2525 |       | 356        | COM76       |      | -1125            | 406        | COM126      |      | 1375    |

| 307        | SEG131      | 2575 |       | 357        | COM77       |      | -1075            | 407        | COM127      |      | 1425    |

| 308        | SEG132      | 2625 |       | 358        | COM78       |      | -1025            | 408        | COM128      |      | 1475    |

| 309        | SEG133      | 2675 |       | 359        | COM79       |      | <b>-</b> 975     | 409        | COM129      |      | 1525    |

| 310        | SEG134      | 2725 |       | 360        | COM80       |      | -925             | 410        | COM130      |      | 1575    |

| 311        | SEG135      | 2775 |       | 361        | COM81       |      | <del>-</del> 875 | 411        | COM131      |      | 1625    |

| 312        | SEG136      | 2825 |       | 362        | COM82       |      | -825             | 412        | NC          | ▼    | 1675    |

| 313        | SEG137      | 2875 |       | 363        | COM83       |      | <b>−775</b>      |            |             |      |         |

| 314        | SEG138      | 2925 |       | 364        | COM84       |      | <del>-</del> 725 |            |             |      |         |

| 315        | SEG139      | 2975 |       | 365        | COM85       |      | <i>−</i> 675     |            |             |      |         |

| 316        | SEG140      | 3025 |       | 366        | COM86       |      | -625             |            |             |      |         |

| 317        | SEG141      | 3075 |       | 367        | COM87       |      | <i>–</i> 575     |            |             |      |         |

| 318        | SEG142      | 3125 |       | 368        | COM88       |      | -525             |            |             |      |         |

| 319        | SEG143      | 3175 |       | 369        | COM89       |      | <i>–</i> 475     |            |             |      |         |

| 320        | SEG144      | 3225 |       | 370        | COM90       |      | -425             |            |             |      |         |

| 321        | SEG145      | 3275 |       | 371        | COM91       |      | -375             |            |             |      |         |

| 322        | SEG146      | 3325 |       | 372        | COM92       |      | -325             |            |             |      |         |

| 323        | SEG147      | 3375 |       | 373        | COM93       |      | -275             |            |             |      |         |

| 324        | SEG148      | 3425 |       | 374        | COM94       |      | -225             |            |             |      |         |

| 325        | SEG149      | 3475 |       | 375        | COM95       |      | -175             |            |             |      |         |

| 326        | SEG150      | 3525 |       | 376        | COM96       |      | -125             |            |             |      |         |

| 327        | SEG151      | 3575 |       | 377        | COM97       |      | -75              |            |             |      |         |

| 328        | SEG152      | 3625 |       | 378        | COM98       |      | -25              |            |             |      |         |

| 329        | SEG153      | 3675 |       | 379        | COM99       |      | 25               |            |             |      |         |

| 330        | SEG154      | 3725 |       | 380        | COM100      |      | 75               |            |             |      |         |

| 331        | SEG155      | 3775 |       | 381        | COM101      |      | 125              |            |             |      |         |

| 332        | SEG156      | 3825 |       | 382        | COM102      |      | 175              |            |             |      |         |

| 333        | SEG157      | 3875 |       | 383        | COM103      |      | 225              |            |             |      |         |

| 334        | SEG158      | 3925 |       | 384        | COM104      |      | 275              |            |             |      |         |

| 335        | SEG159      | 3975 | 1040  | 385        | COM105      |      | 325              |            |             |      |         |

| 336        | NC          | 4044 | -1846 | 386        | COM106      |      | 375              |            |             |      |         |

| 337        | NC          | 4126 |       | 387        | COM107      |      | 425              |            |             |      |         |

| 338        | NC          | 4209 |       | 388        | COM108      |      | 475              |            |             |      |         |

| 339        | NC          | 4291 |       | 389        | COM109      |      | 525              |            |             |      |         |

| 340        | NC          | 4374 |       | 390        | COM110      |      | 575              |            |             |      |         |

| 341        | NC          | 4456 |       | 391        | COM111      |      | 625              |            |             |      |         |

| 342        | NC          | 4539 |       | 392        | COM112      |      | 675              |            |             |      |         |

| 343        | NC          | 4621 |       | 393        | COM113      |      | 725              |            |             |      |         |

| 344        | NC          | 4704 | 4075  | 394        | COM114      |      | 775              |            |             |      |         |

| 345        | NC          | 4958 | -1675 | 395        | COM115      |      | 825              |            |             |      |         |

| 346        | COM66       |      | -1625 | 396        | COM116      |      | 875              |            |             |      |         |

| 347        | COM67       |      | -1575 | 397        | COM117      |      | 925              |            |             |      |         |

| 348        | COM68       |      | -1525 | 398        | COM118      |      | 975              |            |             |      |         |

| 349        | COM69       |      | -1475 | 399        | COM119      |      | 1025             |            |             |      |         |

| 350        | COM70       |      | -1425 | 400        | COM120      | ▼    | 1075             |            |             |      |         |

# 5. PIN DESCRIPTION

# 5.1 Power Pin

| Pin name                                       | I/O             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Number of pins |

|------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| VDD                                            | Power supply    | Connect to system MPU power supply pin Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6              |

| Vss                                            | Power supply    | Connect to the system GND. MV3 is short circuited with Mv3 inside the IC chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8              |

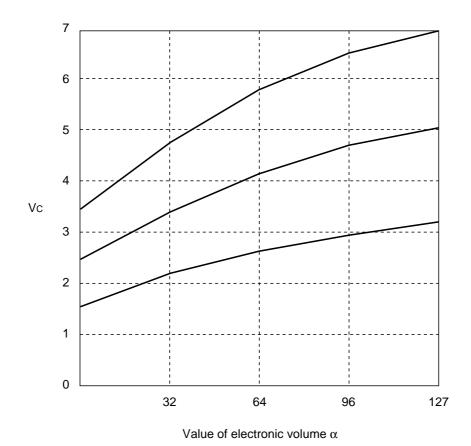

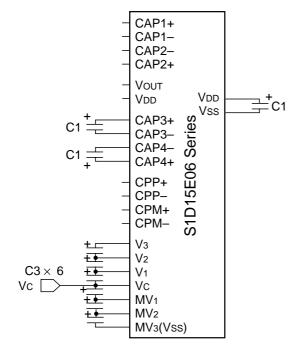

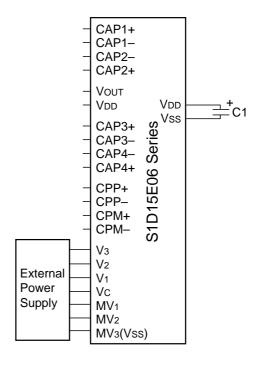

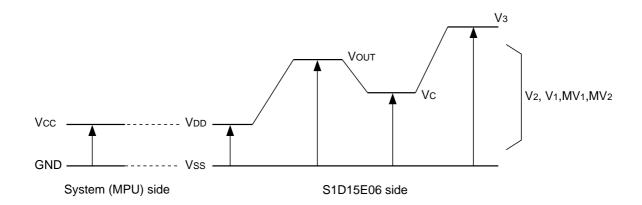

| V3, V2, V1,<br>VC, MV1,<br>MV2, MV3,<br>(=VSS) | Power<br>supply | A liquid crystal drive multi-level power supply. The voltages determined by the liquid crystal cell are impedance-converted by resistive divider and operational amplifier for application. The following order must be maintained: $V3 \geq V2 \geq V1 \geq VC \geq MV1 \geq MV2 \geq MV3 \text{ (=Vss)}$ Master operation: When power supply is turned on, the following voltage is applied to each pin by the built-in power supply circuit. $MV3 \text{ is connected to with Vss inside the IC chip.}$ $V2 \qquad 11/14 \bullet V3 \qquad V1 \qquad 9/14 \bullet V3 \qquad V2 \qquad 7/14 \bullet V3 \qquad V3 \qquad V4 \qquad 5/14 \bullet V3 \qquad V4 \qquad 3/14 \bullet V3 \qquad V4 \qquad 3/14 \bullet V3 \qquad V5 \qquad V4 \qquad 3/14 \bullet V3 \qquad V5 \qquad V5 \qquad V6 \qquad 3/14 \bullet V3 \qquad V6 \qquad 3/14 \bullet V3 \qquad V7 \qquad$ | 14<br>(2 each) |

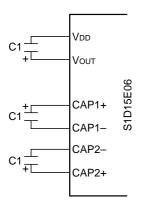

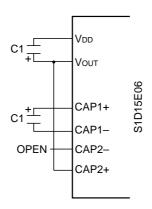

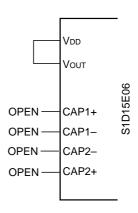

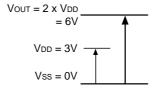

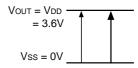

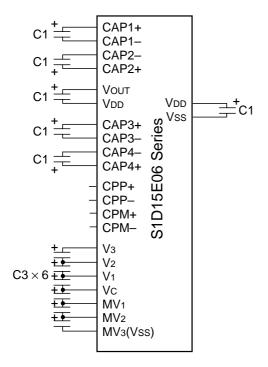

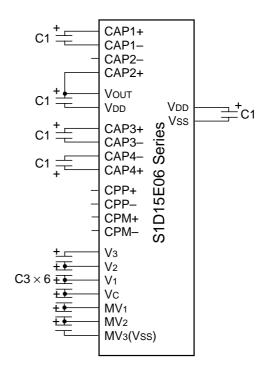

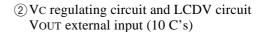

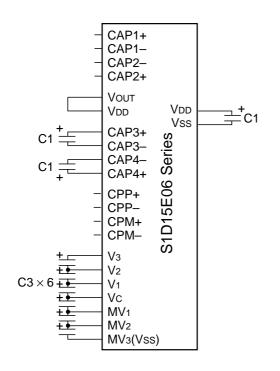

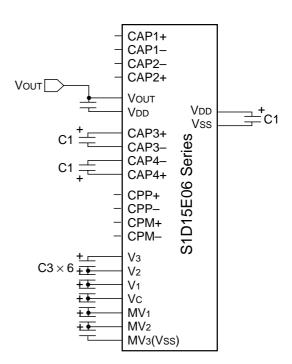

# 5.2 LCD Power Supply Circuit Pin

| Pin name | I/O | Description                                                                                                          | Number of pins |

|----------|-----|----------------------------------------------------------------------------------------------------------------------|----------------|

| CAP1+    | 0   | Pin connected to the positive side of the step-up capacitor. Connect the capacitor between this pin and CAP1– pin.   | 2              |

| CAP1-    | 0   | Pin connected to the negative side of the step-up capacitor. Connect the capacitor between this pin and CAP1+ pin.   | 2              |

| CAP2+    | 0   | Pin connected to the positive side of the step-up capacitor.<br>Connect the capacitor between this pin and CAP2—pin. | 2              |

| CAP2-    | 0   | Pin connected to the negative side of the step-up capacitor. Connect the capacitor between this pin and CAP2+ pin.   | 2              |

| Vouт     | 0   | Output pin for step-up. Connect the capacitor between this pin and VDD.                                              | 2              |

| CAP3+    | 0   | Pin connected to the positive side of the step-up capacitor. Connect the capacitor between this pin and CAP3– pin.   | 2              |

| CAP3-    | 0   | Pin connected to the negative side of the step-up capacitor. Connect the capacitor between this pin and CAP3+ pin.   | 2              |

| CAP4+    | 0   | Pin connected to the positive side of the step-up capacitor. Connect the capacitor between this pin and CAP4– pin.   | 2              |

| CAP4-    | 0   | Pin connected to the negative side of the step-up capacitor. Connect the capacitor between this pin and CAP4+ pin.   | 2              |

| CPP+     | 0   | Keep it open.                                                                                                        | 1              |

| CPP-     | 0   | Keep it open.                                                                                                        | 1              |

| CPM+     | 0   | Keep it open.                                                                                                        | 1              |

| CPM-     | 0   | Keep it open.                                                                                                        | 1              |

# **5.3 System Bus Connection Pin**

| Pin name            | I/O |                                    |                                                                                                                                                                                                                                                                                                                                             | Descriptio                         | n                         |                  | Number of pins |  |  |  |

|---------------------|-----|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------|------------------|----------------|--|--|--|

| D7 to D0 (SI) (SCL) | I/O | serial d                           | 8-bit ' serves as the ck input (SCL), ate. When the pedance state.                                                                                                                                                                                                                                                                          | 8                                  |                           |                  |                |  |  |  |

| A0                  | I   | to distir<br>A0 :                  | ly, the least signif<br>nguish between da<br>= HIGH: indicates tha<br>= LOW: indicates                                                                                                                                                                                                                                                      | ata and comm<br>at D0 to D7 are di | and.<br>splay data or com | mand parameters. | 1              |  |  |  |

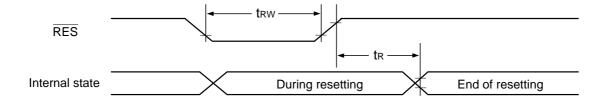

| RES                 | Ι   |                                    | he $\overline{RES}$ is LOW, in $\overline{RES}$                                                                                                                                                                                                                                                                                             |                                    |                           | signal.          | 1              |  |  |  |

| CS1<br>CS2          | _   |                                    | select signal. Whive, and data/com                                                                                                                                                                                                                                                                                                          |                                    |                           |                  | 2              |  |  |  |

| RD<br>(E)           | I   | A p<br>Wh<br>is i                  | <ul> <li>When the 80 series MPU is connected. A pin for connection of the RD signal of the 80 series MPU. When this signal is LOW, the data bus of the S1D15E06 series is in the output state. </li> <li>When the 68 series MPU is connected. Serves as a 68 series MPU enable clock input pin.</li> </ul>                                  |                                    |                           |                  |                |  |  |  |

| WR<br>(R/W)         | ı   | A p<br>Sig<br>WF<br>• Serve<br>MPU | <ul> <li>When the 80 series MPU is connected.         A pin for connection of the WR signal of the 80 series MPU.         Signals on the data bus are latched at the leading edge of the WR signal.     </li> <li>Serves as a read/write control signal input pin when the 68 series MPU is connected.</li> <li>R/W = HIGH: Read</li> </ul> |                                    |                           |                  |                |  |  |  |

| C86                 | I   | C86                                | interface switchir<br>= HIGH: 68 serie<br>= LOW: 80 serie                                                                                                                                                                                                                                                                                   | es MPU interfa                     |                           |                  | 1              |  |  |  |

| P/S                 | I   | P/S = H<br>P/S = L                 | Parallel data input/serial data input select pin P/S = HIGH: Parallel data input P/S = LOW: Serial data input The following Table shows the summary:                                                                                                                                                                                        |                                    |                           |                  |                |  |  |  |

|                     |     | P/S                                | P/S Data/Command Data Read/Write Serial clock                                                                                                                                                                                                                                                                                               |                                    |                           |                  |                |  |  |  |

|                     |     | HIGH                               |                                                                                                                                                                                                                                                                                                                                             |                                    |                           |                  |                |  |  |  |

|                     |     | LOW                                |                                                                                                                                                                                                                                                                                                                                             |                                    |                           |                  |                |  |  |  |

|                     |     | D0 to D                            | P/S = LOW, D0 to<br>05 c <u>an be HIG</u> H, L<br>and WR(R/W) are<br>rial data input doe                                                                                                                                                                                                                                                    | OW or open.                        | GH or LOW.                | data to be read. |                |  |  |  |

| Pin name      | I/O |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                      | Γ                                                                                                    | Descrip                                                | tion                         |                                      |                                    |               | Number of pins |  |

|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------|--------------------------------------|------------------------------------|---------------|----------------|--|

| CLS           | I   | circuit f<br>CLS<br>CLS<br>When 0<br>the S1I                                                                                                                                                                      | A pin used to select Enable/Disable state of the built-in oscillator circuit for display clock.  CLS = HIGH: Built-in oscillator circuit Enabled  CLS = LOW: Built-in oscillator circuit Disabled (External input)  When CLS is LOW, display clock is input from the CL pin. When the S1D15E06 series is used in the master/slave mode, each CLS pins must be set to the same level. |                                                                                                      |                                                        |                              |                                      |                                    |               |                |  |

|               |     |                                                                                                                                                                                                                   | Display clock Master Slave                                                                                                                                                                                                                                                                                                                                                           |                                                                                                      |                                                        |                              |                                      |                                    |               |                |  |

|               |     | Bui                                                                                                                                                                                                               | lt-in os                                                                                                                                                                                                                                                                                                                                                                             | cillator circuit                                                                                     | used                                                   |                              | GH                                   | HIGH                               |               |                |  |

|               |     |                                                                                                                                                                                                                   | Ext                                                                                                                                                                                                                                                                                                                                                                                  | ernal input                                                                                          |                                                        | LC                           | DW                                   | LOW                                |               |                |  |

| M/S           | I   | Liquid (<br>operation<br>display<br>for liqui<br>M/S =<br>M/S =                                                                                                                                                   | crystal on outp<br>, while<br>id cryst<br>= HIGH<br>= LOW                                                                                                                                                                                                                                                                                                                            | display systen<br>outs the timing<br>the slave oper<br>al display.<br>: Master oper<br>: Slave opera | n is synd<br>signal r<br>ration in<br>eration<br>ation | chroniz<br>equire<br>puts th | zed wher<br>od for liqu<br>ne timing |                                    | d             | 1              |  |

|               |     | M/S                                                                                                                                                                                                               | CLS                                                                                                                                                                                                                                                                                                                                                                                  | Oscillation circuit                                                                                  | Pow<br>circ                                            | _                            | CL                                   | FR, <del>DOF</del> ,<br>F1, F2, CA |               |                |  |

|               |     | HIGH                                                                                                                                                                                                              | HIGH<br>LOW                                                                                                                                                                                                                                                                                                                                                                          | Enabled<br>Disabled                                                                                  | Enab<br>Enab                                           |                              | Output<br>Input                      | Output<br>Output                   |               |                |  |

|               |     | LOW                                                                                                                                                                                                               | HIGH<br>LOW                                                                                                                                                                                                                                                                                                                                                                          | Disabled<br>Disabled                                                                                 | Disab<br>Disab                                         |                              | Input<br>Input                       | Input<br>Input                     |               |                |  |

|               |     | The sla                                                                                                                                                                                                           | ve pow                                                                                                                                                                                                                                                                                                                                                                               | er supply circ                                                                                       | uit can a                                              | also op                      | erate, b                             | ut do not use it                   |               |                |  |

| CL            | I/O |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                      | nput/output pi<br>ble shows the rel<br>CL<br>Output<br>Input<br>Input<br>Input                       |                                                        | onforma                      | ance to the                          | M/S and CLS sta                    | ate:          | 1              |  |

|               |     |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |                                                        | 06 seri                      | es in the                            | e master/slave                     |               |                |  |

| FR            | I/O | mode, connect each CL pin.  A liquid crystal alternating current input/output pin.  M/S = HIGH: Output  M/S = LOW: Input  When you want to use the S1D15E06 series in the master/slave mode, connect each FR pin. |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |                                                        |                              |                                      |                                    | 1             |                |  |

| F1, F2,<br>CA | I/O | A liquid crystal sync signal input/output pin.  M/S = HIGH: Output  M/S = LOW: Input  When you want to use the S1D15E06 series in the master/slave mode, connect each F1, F2 and CA pins.                         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                      |                                                        |                              |                                      |                                    | 3<br>(1 each) |                |  |

| DOF           | I/O | M/S =<br>M/S =<br>When y                                                                                                                                                                                          | = HIGH<br>= LOW<br>/ou war                                                                                                                                                                                                                                                                                                                                                           | I blanking con<br>: Output<br>: Input<br>nt to use the S<br>t each DOF pi                            | 31D15E(                                                | 06 seri                      | es in the                            | master/slave                       |               | 1              |  |

# 5.4 Liquid crystal drive pin

| Pin name          | I/O | Description                                                                                                                                                        |     |  |  |  |  |  |

|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|

| SEG0 to<br>SEG159 | 0   | Liquid crystal segment drive output pins. One of the V2, V1, VC, MV1, and MV2 levels is selected by a combination of the display RAM content and FR/F1/F2 signals. | 160 |  |  |  |  |  |

| COM0 to<br>COM131 | 0   | Liquid crystal common drive output pins. One of the V3, Vc, MV3 (Vss) levels is selected by a combination of the scan data and FR/F1/F2 signals.                   | 132 |  |  |  |  |  |

# 5.5 Test pins

| Pin name          | I/O | Description                                                                                  | Number of pins |

|-------------------|-----|----------------------------------------------------------------------------------------------|----------------|

| TEST,             | I   | IC chip test pins. Lock them to LOW.                                                         | 5              |

| TEST2 to 5        |     |                                                                                              |                |

| TEST0, 1, 6 to 18 | I/O | IC chip test pins. Open them and make sure that the capacity is not consumed by wiring, etc. | 15             |

## 6. FUNCTIONAL DESCRIPTION

## 6.1 MPU Interface

## 6.1.1 Selection of Interface Type

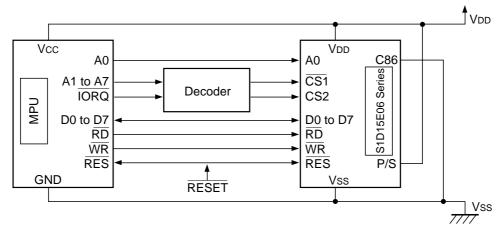

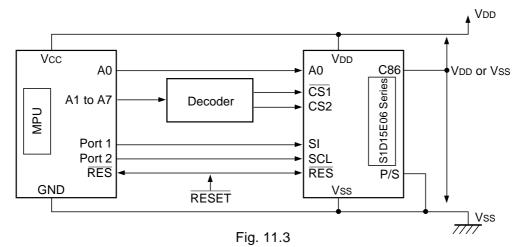

S1D15E06 series allows data to be sent via the 8-bit bi-directional data buses (D7 to D0) or serial data input (SI). By setting the polarity of the P/S pin to HIGH or LOW, you can select either 8-bit parallel data input or serial data input, as shown in Table 6.1.

Table 6.1

| P/S                  | CS1 | CS2 | A0 | RD | WR | C86 | D7 | D6  | D5 to D0 |

|----------------------|-----|-----|----|----|----|-----|----|-----|----------|

| HIGH: Parallel input | CS1 | CS2 | A0 | RD | WR | C86 | D7 | D6  | D5 to D0 |

| LOW : Serial input   | CS1 | CS2 | A0 | _  | _  | _   | SI | SCL | (HZ)     |

—: Fixed to HIGH or LOW HZ: High impedance state

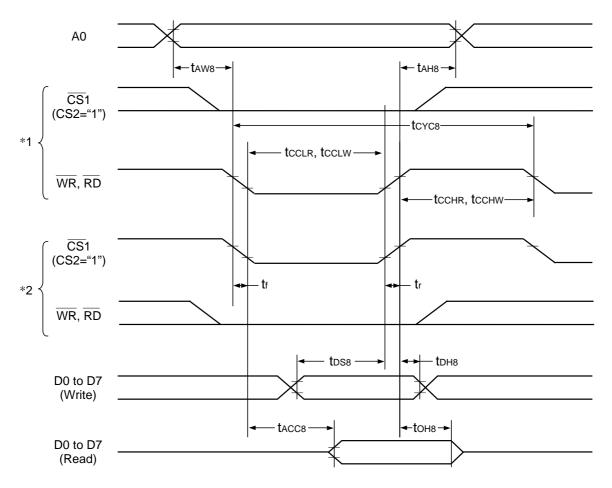

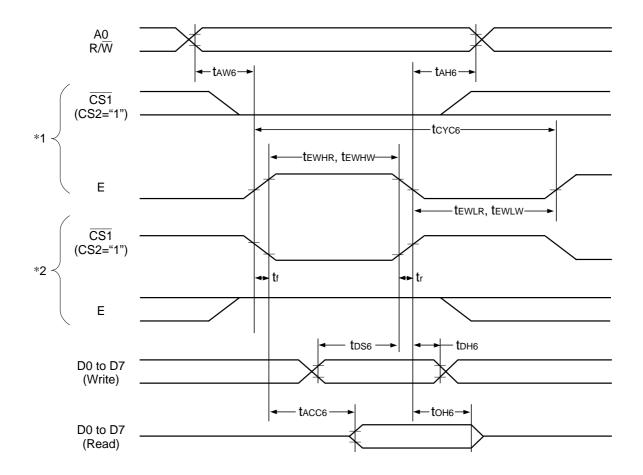

#### 6.1.2 parallel interface

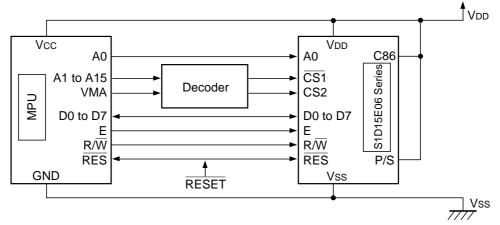

When the parallel interface is selected (P/S = HIGH), direction connection to the MPU bus of either 80 series MPU or 68 series MPU is performed by setting the 86 pin to either HIGH or LOW, as shown in Table 6.2.

Table 6.2

| P/S                     | CS1 | CS2 | A0 | RD | $\overline{WR}$ | D7 to D0 |

|-------------------------|-----|-----|----|----|-----------------|----------|

| HIGH: 68 series MPU bus | CS1 | CS2 | A0 | Е  | R/W             | D7 to D0 |

| LOW: 80 series MPU bus  | CS1 | CS2 | A0 | RD | WR              | D7 to D0 |

The data bus signals are identified by a combination of A0,  $\overline{RD}$  (E), and  $\overline{WR}$  (R/W) signals as shown in Table 6.3.

Table 6.3

| Common | 68 series | 80 series |    | Formation                                   |

|--------|-----------|-----------|----|---------------------------------------------|

| A0     | R/W       | RD        | WR | Function                                    |

| 1      | 1         | 0         | 1  | Display data read, status read              |

| 1      | 0         | 1         | 0  | Display data write, command parameter write |

| 0      | 1         | 1         | 0  | Command write                               |

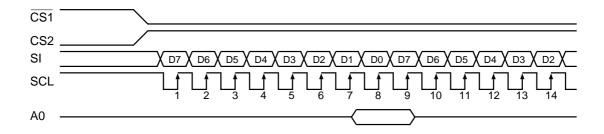

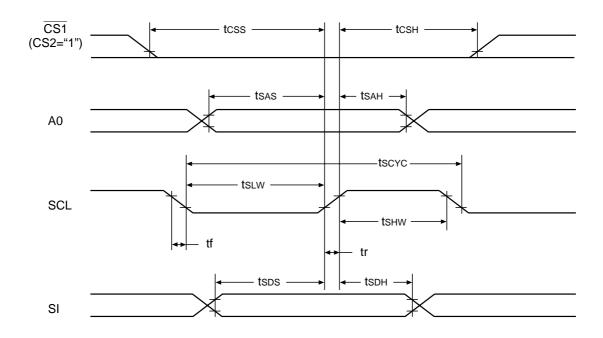

## 6.1.3 Serial interface

When the serial interface is selected (P/S =LOW), the chip is active  $\overline{(CS1}$  = LOW, CS2 = HIGH), and reception of serial data input (SI) and serial clock input (SCL) is enabled. Serial interface comprises a 8-bit shift register and 3-bit counter. The serial data are latched by the rising edge of serial clock signals in the order of D7, D6, .... and D0 starting from the serial data input pin. On the rising edge of 8th serial clock signal, they are converted into 8-bit parallel data to be processed.

Whether serial data input is a display data or command is identified by A0 input. A0 = HIGH indicates display data, while A0 = LOW shows command data. The A0 input is read and identified at every  $8 \times n$ -th rising edge of the serial clock after the chip has turned active.

Fig. 6.1 shows the serial interface signal chart.

Fig. 6.1

- \* When the chip is inactive, the counter is reset to the initials state.

- \* Reading is not performed in the case of serial interface.

- \* For the SCL signal, a sufficient care must be taken against terminal reflection of the wiring and external noise. Recommend to use an actual equipment to verify the operation.

# 6.1.4 Chip Selection

The S1D15E06 series has two chip select pins;  $\overline{CS1}$  and  $\overline{CS2}$ .  $\overline{MPU}$  interface or serial interface is enabled only when  $\overline{CS1} = LOW$  and  $\overline{CS2} = HIGH$ .

When the chip select pin is inactive,  $\underline{D0}$  to  $\underline{D5}$  are in the state of high impedance, while A0,  $\overline{RD}$  and  $\overline{WR}$  inputs are disabled. When serial interface is selected, the shift register and counter are reset.

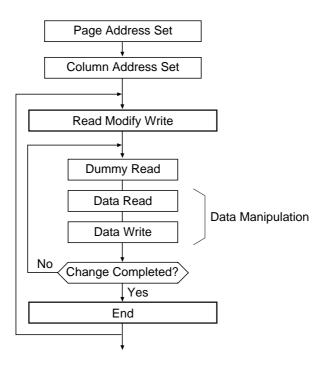

# 6.1.5 Access to display data RAM and internal register

Access to S1D15E06 series viewed from the MPU side is enabled only if the cycle time requirements are kept. This does not required waiting time; hence, high-speed data transfer is allowed.

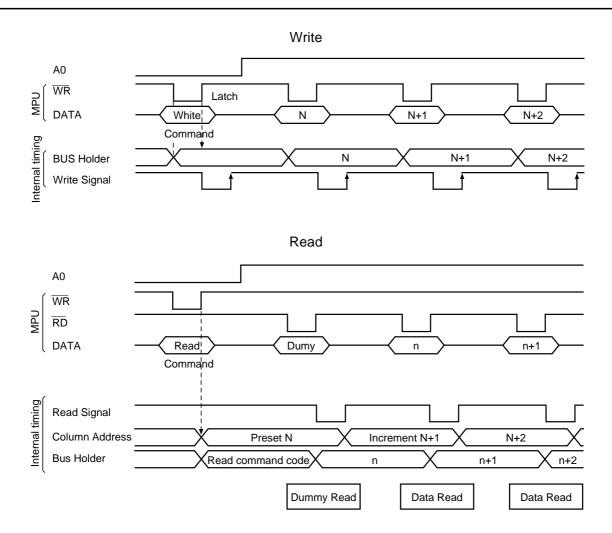

Furthermore, at the time of data transfer with the MPU, S1D15E06 series provides a kind of inter-LSI pipe line

processing via the bus holder accompanying the internal data bus.

For example, when data is written to the display data RAM by the MPU, the data is once held by the bus holder. It is written to the display data RAM before the next data write cycle comes.

On the other hand, when the MPU reads the content of the display data RAM, it is read in the first data read cycle (dummy), and the data is held in the bus holder. Then it is read onto on the system bus from the bus holder in the next data read cycle. Restrictions are imposed on the display data RAM read sequence. When the address has been set, specified address data is not output to the Read command immediately after that. The specified address data is output in the second data reading. This must be carefully noted. Therefore, one dummy read operation is mandatory subsequent to address setting or write cycle. Fig. 6.2 illustrates this relationship.

Fig. 6.2

# 6.2 Display data RAM

# 6.2.1 Display Data RAM

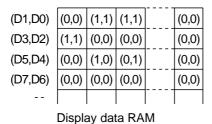

This is a RAM to store the display dot data, and comprises  $132 \times 160 \times 2$  bits. Access to the desired bit is enabled by specifying the page address and column address. When the 4 gray-scale is selected by the Display Mode command, display data input for gray-scale display are processed as a two-bit pair. Combination is as follows:

$$(MSB, LSB) = (D1,D0), (D3,D2), (DS,D4), (D7,D6)$$

When the RAM bit data is gray-scale 1 and 2, gray-scale display is realized according to the parameter of the Gray-scale Pattern Set command.

RAM bit data (high order and low order)

(1,1): gray-scale 3 Black (when display is in normal mode)

(1,0): gray-scale 2 (0,1): gray-scale 1

(0,0): gray-scale 0 White (when display is in

normal mode)

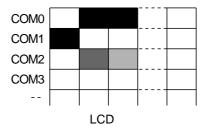

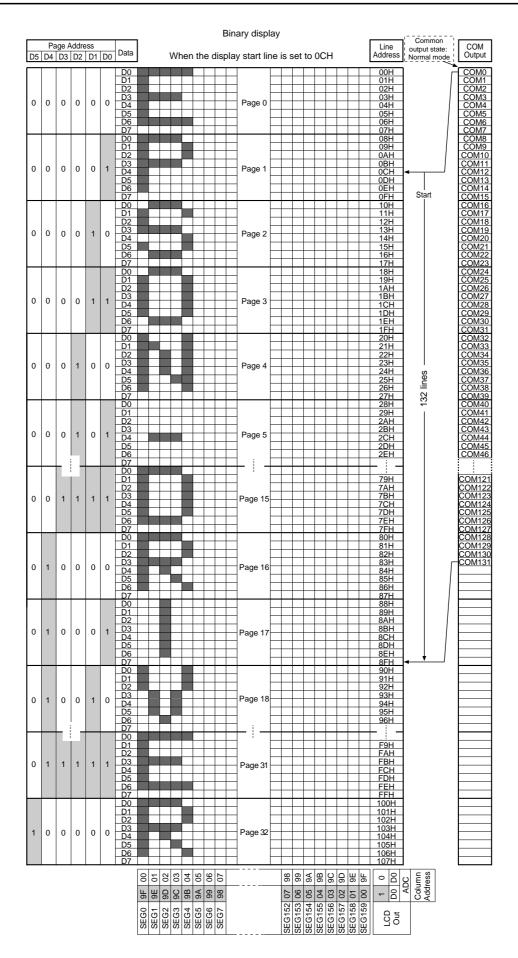

When binary display is selected by the Display Mode command, the RAM 1 bit built in the one-dot pixel responds to it. When the RAM bit data is "1", the display is black. If it is "0", the display is given in white.

RAM bit data

"1": Light On Black (when display is in

normal mode)

"0": Light Off White (when display is in

normal mode)

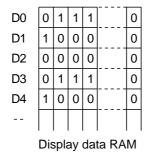

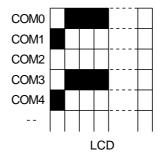

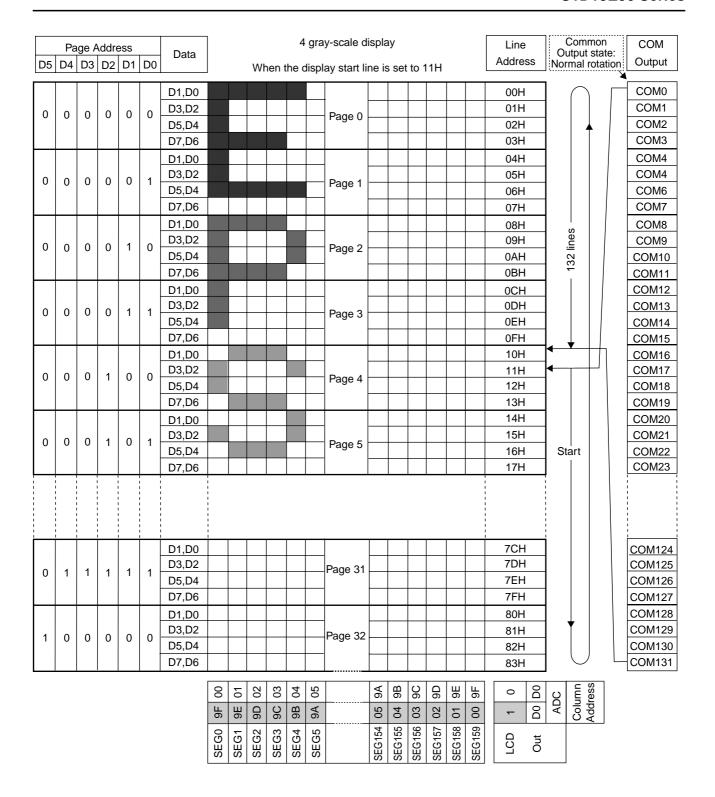

Display data D7 to D0 from the MPU correspond to LCD common direction, as shown in Fig. 6.3 and 6.4. Therefore, less restrictions when multi-chip usage. Furthermore, read/write operations from the MPU to the RAM are carried out via the input/output buffer.

The read operation from Display data RAM is designed as an independent operation. Accordingly, even if the MPU accesses the RAM asynchronously during LCD display, no adverse effect is given to display.

Fig. 6.3 4 gray-scale

Fig. 6.4 Binary

#### 6.2.2 Gray-scale display

When the 4 gray-scale is selected by the Display Mode command, gray-scale is represented by the FRM control carried out according to the gray-scale data written in the display data RAM.

Of the 4 gray-scale, 2 gray-scale of halftones (gray-scale 2 and 1) has its level of contrast specified by the Gray-scale Set command. Gray-scale can be selected from 6 levels of contrast.

# 6.2.3 Page address circuit/column address circuit

The address of the display data RAM to be accessed is specified by the Page Address Set command and Column Address Set command, as shown in Fig. 6.5 and Fig. 6.6. For Address incremental direction, either the column direction or page direction can be selected by the Address Direction command. Whichever direction is chosen, increment is carried out by positive one (+1) after write

or read operation.

When the column direction is selected for address increment, the column address is increased by +1 for every write or read operation. After the column address has accessed up to 9FH, the page address is incremented by +1 and the column address shifts to 0H.

When the page direction is selected for address increment, the page address is increased with the column address locked in position. When the page address has accessed up to 32H, the column address is incremented by +1, and the page address goes to 0H.

Whichever direction is selected for address increment, the page address goes back to 0H and the column address to 0H after access up to the column address 9FH of page address 32H.

As shown in Fig. 6.4, relationship between the display data RAM column address and segment output can be reversed by the Column Address Set Direction command. This will reduce restrictions on IC layout during LCD module assembling.

Table 6.4

| SEG ou | ıtput | SEG0   |                | SEG159 |

|--------|-------|--------|----------------|--------|

| ADC    | "0"   | 0(H)→  | Column Address | →9F(H) |

| (D0)   | "1"   | 9F(H)← | Column Address | ←0(H)  |

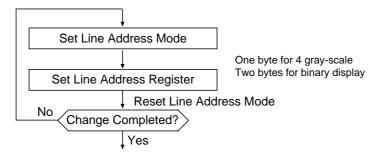

#### 6.2.4 Line address circuit

The line address circuit specifies the line address corresponding to COM output when the contents of the display data RAM is displayed, as shown in Fig. 6.5 and 6.6. Normally, the top line of the display (COM0 output in the case of normal rotation of the common output status and COM131 output in the case of reverse rotation) is specified by the Display Start Line Address Set command. The display area starts from the specified display start line address to cover the area corresponding to the lines specified by the DUTY Set command in the direction where the line address increments.

If the display start line address set command is used for

dynamic modification of the line address, screen scroll and page change are enabled.

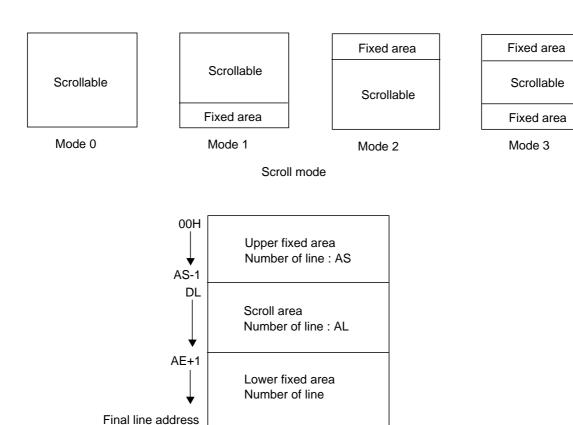

#### 6.2.5 Area scroll

The display area can be divided into the display area fixed in the COM direction and scrollable area by the area scroll command. The scroll area is set by a scroll mode, scroll start line address (AS), scroll end address (AE), and scroll display line count (AL) as parameters for the area scroll command. Display start line address (DL) in the scroll area can be specified by the display start line address set command.

#### 6.2.5.1 Mode 0 (full screen scroll)

This mode releases the area scroll. Parameters AS, AE and AL are disabled,

# 6.2.5.2 Mode 1 (Upper scroll)

Reading starts from the line address DL to read AL lines as a scroll area. If the line address AE is read in the

middle of reading the scroll area, the line address to be read next will be 00H. When all the AL lines have been read, the address to be read next will be AE+1. When reading is completed up to the final line address, the control goes back to the line address DL, and parameter AS is disabled. DL can be specified in the range from 00H to AE.

## 6.2.5.3 Mode 2 (lower scroll)

Reading starts from line address 00H to reach the line address AS-1 in the continuous reading mode. Upon completion of reading of line address AS-1, the line address moves to the DL to read the area corresponding to AL lines from the line address DL as a scroll area. If the final line address is read in the middle of reading the scroll area, the line address to be read next will be AS. When all AL lines have been read, the control goes back to the line address 00H, and parameter AE is disabled. DL can be specified in the range from AS to the final line address.

#### 6.2.5.4 Mode 3 (Center scroll)

Reading starts from line address 00H to reach the line address AS-1 in the continuous reading mode.

Upon completion of reading of line address AS-1, the line address moves to the DL to read the area corresponding to AL lines from the line address DL as a scroll area. If the final line address is read in the middle of reading the scroll area, the line address to be read next will be AS. When all AL lines have been read, the line address will be AE+1. When up to the final line address has been read, the control goes back to the line address 00H, DL can be specified in the range from AS to AE.

## 6.2.6 Display data latch circuit

The display data latch circuit is a latch to temporarily latch the display data output from then display data RAM to the liquid crystal drive circuit. Display normal/reverse, display ON/OFF, and display all lighting ON/OFF commands control the data in this latch, without the data in the display data RAM being controlled.

# 6.2.7 Partial display

Partial display of the screen is provided by the partial display ON/OFF command. The partial area (display start line, number of display lines) are set by the partial display set command.

The display start line of the parameter shows the line assigned in the COM direction of the liquid crystal screen. It is different from the line address given in Fig. 6.5 and 6.6.

Example: When the point is set at 1 (COM4 to 7) by the Duty Reset command, the display line is assigned as shown below. If the display start line 4 and display line count 3 are specified by the partial display set command, the display area is COM8 to COM10.

| Display line | LCD panel |       |

|--------------|-----------|-------|

| 0            |           | COM4  |

| 1            |           | COM5  |

| 2            |           | COM6  |

| 3            |           | COM7  |

| 4            |           | COM8  |

| 5            |           | СОМ9  |

| 6            |           | COM10 |

| 7            |           | COM11 |

| 8            |           | COM12 |

| 9            |           | COM13 |

| 10           |           | COM14 |

|              |           |       |

Fig. 6.5 4 gray-scale

Fig. 6.6 Binary display

#### 6.3 Oscillator circuit

A display clock is generated by the CR oscillator. The oscillator circuit is enabled only when M/S = HIGH and CLS = HIGH. Oscillation starts after input of the built-in oscillator circuit ON command input.

When CLS = LOW, oscillation stops, and display clock is input from the CL pin.

# 6.4 Display timing generation circuit

Timing signals are generated from the display clock to the line address circuit and display data latch circuit. Synchronized with display clock, display data is latched in display data latch circuit, and is output to the segment drive output pin. Reading of the display data into the LCD drive circuit is completely independent of access from the MPU to the display data RAM. Accordingly, asynchronous access to the display data RAM during LCD display does not give any adverse effect; like as

flicker.

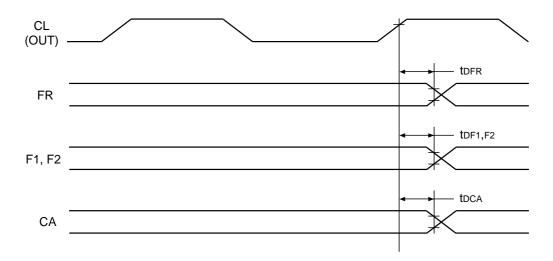

Furthermore, the display clock generates internal common timing, liquid crystal alternating signal(FR), field start signal (CA) and drive pattern signal (Fl and F2).

The FR normally generates 2-frame alternating drive system drive waveform to the liquid crystal drive circuit. The n-line reverse alternating drive waveform is generated for each  $4 \times (a+1)$  line by setting data on the n-line reverse drive register. When there is a display quality problem including crosstalk, the problem may be solved using the n-line reverse alternating drive. Execute liquid crystal display to determine the number

Execute liquid crystal display to determine the number of lines "n" for alternation.

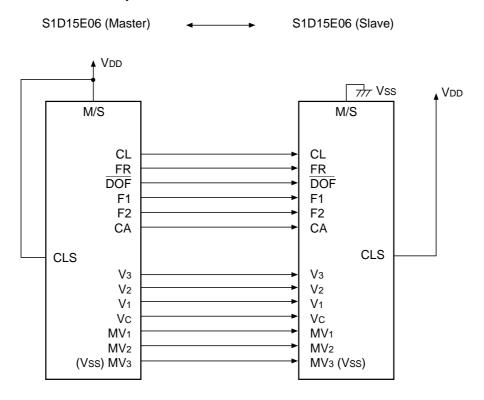

When you want to use the S1D15E06 series in multichip configuration, supply display timing signal (FR, CA, F1, F2, CL, DOF) to the slave side from the master side. Table 6.5 shows the statuses of FR, CA, F1, F2, CL, DOF.

Table 6.5

| Operating mode                                                      | CL        | FR, CA, F1, F2, DOF |

|---------------------------------------------------------------------|-----------|---------------------|

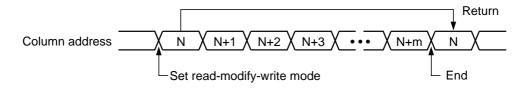

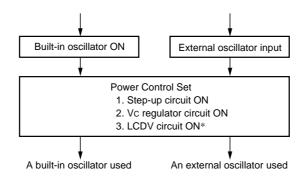

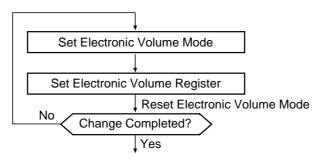

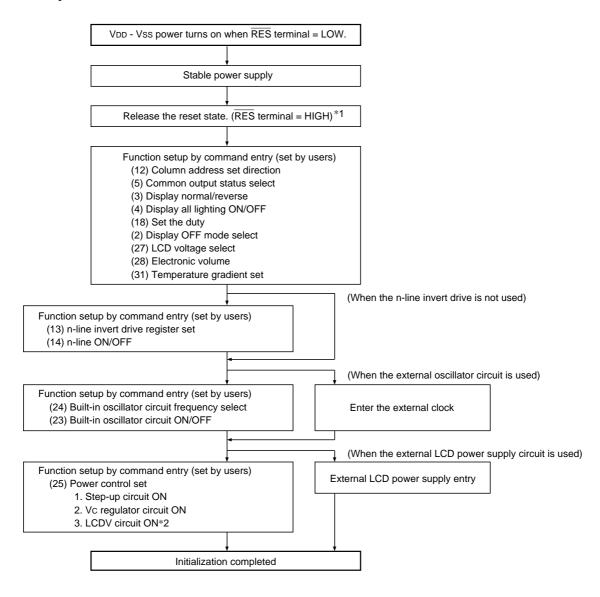

| Master (M/S = HIGH) Built-in oscillator circuit enabled (CLS = HIGH | l) Output | Output              |