A TDK Group Company

6

December 1992

#### DESCRIPTION

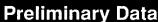

The SSI 78Q8360 is a combination Media Access Controller (MAC) and 10 Mbit/s Manchester encoder/ decoder (ENDEC) with Attachment Unit Interface (AUI) for IEEE 802.3 applications. It is connected to the transmission medium through the AUI with a transceiver circuit such as the SSI 78Q8330 Ethernet Coax Transceiver or the 78Q902 10BaseT Transceiver, Connection to the host is accomplished via external bus decoding logic.

An intelligent Buffer Manager is controlled by the host read, host write, receive and transmit pointers, and the 8360 manages the pointers internally without any host intervention. The 8360 interleaves access to the buffer memory so that accesses from the host and from the network media seem to operate concurrently.

The 8360 has a sophisticated power management capability with three different operating modes allowing the user to maximize power savings. Interface with the host can be accomplished in several different ways: memory mapping, I/O mapping, programmable DMA or a combination of these. Big and little endian byte orderings make for simple bus interface to all standard microprocessors. The 78Q8360 is packaged in a 100-pin QFP or TQFP and uses a single 5V supply.

#### **FEATURES**

T-75-49

- IEEE 802.3 and Ethernet 2.0 compliant

- Power management options include:

- Intelligent power mode automatically shuts off unused circuitry

- Standby mode reduces power while not in operation

- Full power-down mode offers maximum power savings

- Advanced Buffer Manager architecture:

- Automatic management of all pointers

- Allows "simultaneous" access to data in buffer memory by both the network and host

- High-speed received packet skip

- Configurable Buffer Memory for design flexibility:

- Two-bank transmit buffer in 2, 4, 8, or 16 Kbyte

- Ring-structure receive buffer from 4 to 62 Kbytes

- Software-configurable system bus structure:

- Compatible with major microprocessors

- 8- or 16-bit wide data path

- Supports single and programmable burst DMA, I/O and Interrupt operations

- Three different loopback modes

- Multicast address filtering via 64-element hash table

FIGURE 1: System Diagram

1292 - rev.

6-27

#### **FUNCTIONAL DESCRIPTION**

The 78Q8360 consists of five major blocks:

- Buffer Manager (and SRAM Interface)

- Data Link Controller

- · Host Interface

- Manchester ENDEC

- Power Management

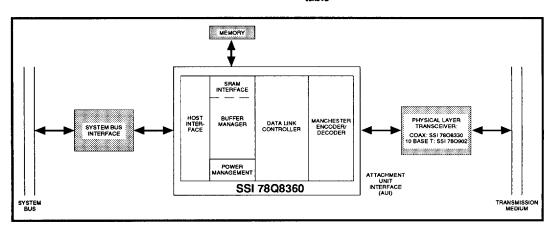

A block diagram of the 78Q8360 is shown in Figure 2.

#### **BUFFER MANAGER**

The Buffer Manager manages all accesses to the buffer memory through the SRAM interface. The buffer memory is connected directly to the Data Link Controller (DLC), thus eliminating the need for a local microprocessor. The Buffer Manager also keeps track of all buffer memory pointers automatically, simplifying the software driver task. Together with intelligent arbitration, this makes the 8360 a high performance LAN controller.

The buffer memory is divided into two portions: transmit memory portion and receive memory portion. The transmit memory portion can be partitioned into 2K, 4K, 8K or 16 Kbyte buffer sizes. There is only one transmit bank if a 2 KB transmit buffer size is selected. If the transmit buffer size is greater than 2 KB, then the transmit buffer is configured into two banks of equal size. With the two bank configuration, one transmit bank may be tied up during transmission but the host can still continue to load data packets into the second transmit bank to be transmitted later. The receive buffer has a ring architecture which can be configured from 4K to 62 KB depending on the buffer memory configuration which has a range of 8K to 64 KB.

A central arbitrator inside the Buffer Manager prioritizes and services requests for access to the buffer memory from 4 sources: the Transmitter, the Receiver, Host Read and Host Write. If necessary, the 8360 will assert a 'not ready' handshake to the host while servicing the Transmitter and/or Receiver. The 8360 arbitration mechanism provides packet management by interleaving packet data accesses to the buffer memory such that the operation appears to be simultaneous.

For instance, in the situation where 2 transmit banks are configured, the host can load the first transmit bank and initiate a transmission. While the first transmit bank is being transmitted, the host can continue to load packets in the second transmit bank. At this stage, the 8360 can potentially be receiving data from the medium and loading it into the receive buffer (if the 8360 is in a loop back mode or if self-reception occurs).

#### DATA LINK CONTROLLER

The Data Link Controller (DLC) implements the ISO/ ANSI/IEEE 8802-3 CSMA/CD protocol. It consists of a Transmitter, a Receiver and CRC logic (which is shared by both transmit and receive operations). Automatic generation and stripping of the 64-bit preamble and the 32-bit CRC code are provided on-chip.

#### HOST INTERFACE

The Host Interface (HIF) provides connection to the host system. It consists of the various registers, DMA circuits and ready logic. Both word and byte interfaces are supported as well as big endian and little endian data ordering. Host access to the buffer memory is through BMR8 (and BMR9). Reading from BMR8 will read a byte or word from the receive buffer and writing to BMR8 will write a byte or word to the transmit buffer. The ready logic is capable of delaying host access to the buffer memory with a time-out mechanism. Both single and burst DMA transfer modes are supported.

#### MANCHESTER ENDEC

This block implements Manchester encoding and decoding. Serial NRZ data from the DLC is converted to Manchester encoded data and sent to TDP and TDN outputs through the Attachment Unit Interface (AUI) driver. The decoder section performs three functions on the data received at RDP and RDN: clock recovery, carrier detection and Manchester decoding. The recovered receive clock will be low at the end of reception and during idle to save power. Jitter of up to 20 nsec can be tolerated by the decoder. Collisions detected at the transceiver are presented as a 10 MHz signal at CDP and CDN and are then converted to a logic level signal and passed to the DLC.

#### **POWER MANAGEMENT**

One very useful and important feature that the 8360 offers is intelligent power management. It supports three different power saving modes: Intelligent, Standby, and Full Shutdown. All modes are configurable through registers. In the Intelligent mode, clocks are active only when they are needed. For example, when not transmitting, the clock supplied to the transmitter circuit

in the DLC block is not active while host read from buffer memory may be active. In Standby mode, the oscillator clock is disconnected from the rest of the circuits, so that only the oscillator circuits draw power. Full Shutdown turns off the oscillator, resulting in maximum power savings. Note that this mode is not available when using an external clock source.

FIGURE 2: 78Q8360 Block Diagram

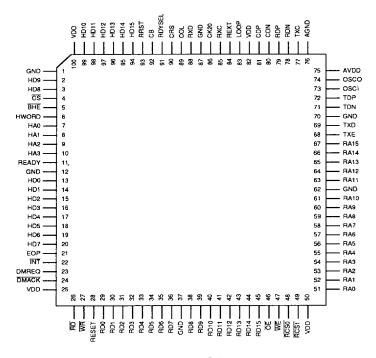

#### PIN ASSIGNMENT TABLE - 100-Pin QFP

| PIN# | PIN NAME | TYPE | PIN# | PIN NAME | TYPE           | PIN# | PIN NAME | TYPE | PIN# | PIN NAME | TYPE           |

|------|----------|------|------|----------|----------------|------|----------|------|------|----------|----------------|

| 1    | HD11     | U8OI | 26   | DMREQ    | O16            | 51   | RCS0     | 04   | 76   | osci     | J <sup>2</sup> |

| 2    | HD10     | IO8U | 27   | DMACK    | ı              | 52   | RCS1     | 04   | 77   | osco     | O <sup>2</sup> |

| 3    | VDD      | Р    | 28   | VDD      | Р              | 53   | VDD      | Ρ    | 78   | AVDD     | Р              |

| 4    | GND      | Р    | 29   | RD       | ı              | 54   | RA0      | O4   | 79   | AGND     | Р              |

| 5    | HD9      | IO8U | 30   | WR       | 1              | 55   | RA1      | O4   | 80   | TXC      | IO4U           |

| 6    | HD8      | IO8U | 31   | RESET    | I <sup>1</sup> | 56   | RA2      | O4   | 81   | RDN      | Al             |

| 7    | CS       | 1    | 32   | RD0      | 104U           | 57   | RA3      | 04   | 82   | RDP      | Al             |

| 8    | BHE      | 1.   | 33   | RD1      | 104U           | 58   | RA4      | 04   | 83   | CDN      | Al             |

| 9    | HWORD    | O4   | 34   | RD2      | 104U           | 59   | RA5      | 04   | 84   | CDP      | Al             |

| 10   | HA0      | - 1  | 35   | RD3      | 104U           | 60   | RA6      | O4   | 85   | VDD      | Р              |

| 11   | HA1      | 1    | 36   | RD4      | 104U           | 61   | RA7      | O4   | 86   | LOOP     | IO4U           |

| 12   | HA2      | - 1  | 37   | RD5      | 104U           | 62   | RA8      | O4   | 87   | REXT     | _3             |

| 13   | HA3      | I    | 38   | RD6      | IO4U           | 63   | RA9      | O4   | 88   | RXC      | IO4U           |

| 14   | READY    | 04   | 39   | RD7      | IO4U           | 64   | RA10     | 04   | 89   | CK20     | O2             |

| 15   | GND      | Р    | 40   | GND      | Р              | 65   | GND      | Р    | 90   | GND      | Р              |

| 16   | HD0      | 108  | 41   | RD8      | IO4U           | 66   | RA11     | 04   | 91   | RXD      | IO4U           |

| 17   | HD1      | 108  | 42   | RD9      | IO4U           | 67   | RA12     | 04   | 92   | COL      | IO4U           |

| 18   | HD2      | 108  | 43   | RD10     | 104U           | 68   | RA13     | 04   | 93   | CRS      | 104U           |

| 19   | HD3      | IO8  | 44   | RD11     | IO4U           | 69   | RA14     | 04   | 94   | RDYSEL   | -              |

| 20   | HD4      | 108  | 45   | RD12     | IO4U           | 70   | RA15     | 04   | 95   | СВ       | 04             |

| 21   | HD5      | IO8  | 46   | RD13     | IO4U           | 71   | TXE      | IO4U | 96   | RRST     | 04             |

| 22   | HD6      | IO8  | 47   | RD14     | 104U           | 72   | TXD      | 104U | 97   | HD15     | U8OI           |

| 23   | HD7      | IO8  | 48   | RD15     | IO4U           | 73   | GND      | Р    | 98   | HD14     | U8OI           |

| 24   | EOP      | I    | 49   | ŌĒ       | O4             | 74   | TDN      | AO   | 99   | HD13     | U8OI           |

| 25   | ĪNT      | O4   | 50   | WE       | O4             | 75   | TDP      | AO   | 100  | HD12     | IQ8U           |

#### Legend:

I: Input (TTL level)

On: Output with IOL = n mA

IOn: Input (TTL level) and Output with IOL = n mA IOnU: IOn with "controlled" internal pull-up resistor

Al: Analog Input

AO: Analog Output

P: Power

#### Notes:

- [1] RESET has a Schmitt trigger and a pull-down resistor.

- [2] OSCI and OSCO have CMOS level.

- [3] REXT is connected to a resistor and then to analog ground.

6-30

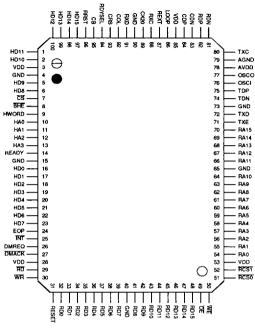

#### PIN ASSIGNMENT TABLE - 100-Pin TQFP

| PIN# | PIN NAME  | TYPE | PIN# | PIN NAME | TYPE           | PIN# | PIN NAME | TYPE           | PIN# | PIN NAME | TYPE |

|------|-----------|------|------|----------|----------------|------|----------|----------------|------|----------|------|

| 1    | GND       | Р    | 26   | RD       | ı              | 51   | RA0      | O4             | 76   | AGND     | Р    |

| 2    | HD9       | IO8U | 27   | WR       | ı              | 52   | RA1      | 04             | 77   | TXC      | IO4U |

| 3    | HD8       | IO8U | 28   | RESET    | l <sup>1</sup> | 53   | RA2      | 04             | 78   | RDN      | Al   |

| 4    | <u>cs</u> | _    | 29   | RD0      | 104U           | 54   | RA3      | 04             | 79   | RDP      | Al   |

| 5    | BHE       | _    | 30   | RD1      | IO4U           | 55   | RA4      | O4             | 80   | CDN      | Al   |

| 6    | HWORD     | 04   | 31   | RD2      | IO4U           | 56   | RA5      | 04             | 81   | CDP      | Al   |

| 7    | HA0       | _    | 32   | RD3      | IO4U           | 57   | RA6      | 04             | 82   | VDD      | Р    |

| 8    | HA1       |      | 33   | RD4      | IO4U           | 58   | RA7      | O4             | 83   | LOOP     | IO4U |

| 9    | HA2       | ı    | 34   | RD5      | 104U           | 59   | RA8      | O4             | 84   | REXT     | _3   |

| 10   | HA3       | _    | 35   | RD6      | IO4U           | 60   | RA9      | 04             | 85   | RXC      | IO4U |

| 11   | READY     | O4   | 36   | RD7      | 104U           | 61   | RA10     | 04             | 86   | CK20     | O2   |

| 12   | GND       | Р    | 37   | GND      | Р              | 62   | GND      | Р              | 87   | GND      | Р    |

| 13   | HD0       | IO8  | 38   | RD8      | 104U           | 63   | RA11     | 04             | 88   | RXD      | 104U |

| 14   | HD1       | 108  | 39   | RD9      | IO4U           | 64   | RA12     | 04             | 89   | COL      | 104U |

| 15   | HD2       | 108  | 40   | RD10     | 104U           | 65   | RA13     | O4             | 90   | CRS      | IO4U |

| 16   | HDЗ       | 108  | 41   | RD11     | 104U           | 66   | RA14     | O4             | 91   | RDYSEL   | -    |

| 17   | HD4       | 108  | 42   | RD12     | 104U           | 67   | RA15     | O4             | 92   | СВ       | O4   |

| 18   | HD5       | 108  | 43   | RD13     | 104U           | 68   | TXE      | IO4U           | 93   | RRST     | 04   |

| 19   | HD6       | 108  | 44   | RD14     | 104U           | 69   | TXD      | 104U           | 94   | HD15     | U8OI |

| 20   | HD7       | IO8  | 45   | RD15     | IO4U           | 70   | GND      | Р              | 95   | HD14     | IO8U |

| 21   | EOP       | I    | 46   | ŌĒ       | 04             | 71   | TDN      | AO             | 96   | HD13     | 108U |

| 22   | ÎNT       | 04   | 47   | WE       | 04             | 72   | TDP      | AO             | 97   | HD12     | IO8U |

| 23   | DMREQ     | 016  | 48   | RCS0     | 04             | 73   | osci     | l <sup>2</sup> | 98   | HD11     | IO8U |

| 24   | DMACK     | t    | 49   | RCS1     | 04             | 74   | osco     | O <sup>2</sup> | 99   | HD10     | IO8U |

| 25   | VDD       | Р    | 50   | VDD      | Р              | 75   | AVDD     | Р              | 100  | VDD      | Р    |

#### Legend:

I: input (TTL level)

On: Output with IOL = n mA

On: Input (TTL level) and Output with IOL = n mA

OnU: On with "controlled" internal pull-up resistor

AI: Analog Input AO: Analog Output

P: Power

#### Notes:

- [1] RESET has a Schmitt trigger and a pull-down resistor.

- [2] OSCI and OSCO have CMOS level.

- [3] REXT is connected to a resistor and then to analog ground.

6-31

#### PIN DESCRIPTION

#### **HOST BUS INTERFACE**

| NAME          | TYPE | DESCRIPT                                                                                                                                                                                                                | ION                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                                                                                                                      |  |  |  |

|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET         | l    | required. Th                                                                                                                                                                                                            | HARDWARE RESET. Active high. A minimum pulse length of 200 ns is required. This pin resets the 8360's internal pointers and registers to their appropriate states. NB: the 8360 must be reset after power on before usage.                                                                                                                                                                                                                                      |                               |                                                                                                                      |  |  |  |

| READY         | 0    | to complete<br>device is un<br>situations, t<br>(DLCR1 <6:                                                                                                                                                              | READY. This output is asserted to indicate to the host that the 8360 is ready to complete the requested read or write operation. It will also be used if the device is unable to respond to read or write requests within 2.4 $\mu$ s. In these situations, the 8360 will also assert $\overline{\text{INT}}$ and the host read error status bit (DLCR1 <6>) or host write error status bit (DLCR0 <0>). The polarity of the READY pin is determined by RDYSEL. |                               |                                                                                                                      |  |  |  |

| RDYSEL        | I    | pin. When F                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | '1', READY                    | input to select the polarity of the READY will be active high. If RDYSEL is a '0',                                   |  |  |  |

| WR            | I    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               | nput that enables a write operation from s as selected by the host address inputs                                    |  |  |  |

| RD            | I    |                                                                                                                                                                                                                         | READ. The $\overline{RD}$ pin is an active low input that enables a read operation by the host from the 8360's internal registers as selected by the host address inputs HA[0:3].                                                                                                                                                                                                                                                                               |                               |                                                                                                                      |  |  |  |

| <del>cs</del> |      | CHIP SELE                                                                                                                                                                                                               | CT. An activ                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e low input s                 | ignal as the chip select for the 8360.                                                                               |  |  |  |

| BHE           | ı    | when the 83<br>Combination                                                                                                                                                                                              | 360 is config                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ured for word<br>nd HA0 are u | ive low byte/word control pin used only d transfer by HBYTE bit (DLCR6 <5>). used to select word, upper byte only or |  |  |  |

|               |      | HBYTE                                                                                                                                                                                                                   | BHE                                                                                                                                                                                                                                                                                                                                                                                                                                                             | HA0                           | FUNCTION                                                                                                             |  |  |  |

|               |      | 0                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                             | Word transfer                                                                                                        |  |  |  |

|               |      | 0                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                             | Byte transfer on high bus HD[8:15].                                                                                  |  |  |  |

|               |      | 0                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                             | Byte transfer on low bus HD[0:7].                                                                                    |  |  |  |

|               |      | 0                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                             | Reserved                                                                                                             |  |  |  |

|               |      | 1                                                                                                                                                                                                                       | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ×                             | Byte transfer (HD[0:7])                                                                                              |  |  |  |

| INT           | 0    | INTERRUPT. This active low signal is asserted when the 8360 requires the intervention of the Host in the situations as depicted in DLCR0&1. The INT signal is masked by writing a '0' to the interrupt enable register. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                                                                                                                      |  |  |  |

| EOP           | 1    | END OF PROCESS. Asserted at the end of a DMA transfer by the Host DMA controller. Further DMA requests (DMREQ) will be discontinued after EOP is asserted. Polarity can be selected via register bit (DLCR7 <1>).       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                                                                                                                      |  |  |  |

| DMREQ         | 0    |                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               | DMREQ to the Host DMA controller to a read from its receive buffer.                                                  |  |  |  |

**ENDEC Combo**

#### PIN DESCRIPTION (continued)

| NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                               |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMACK    | 1    | DMA ACKNOWLEDGE. An active low signal issued by the Host DMA controller when it is ready to perform data transfers between the Host and the 8360's buffer memory via BMR8.                                                                                                                                                                                |

| HA[0:3]  | ı    | HOST ADDRESS. Selects the set of internal registers to be accessible by the 8360 for read or write operations.                                                                                                                                                                                                                                            |

| HD[0:15] | 1/0  | HOST DATA BUS. A bi-directional, tri-state bus for data, command and status transfers between the Host and the 8360 with the direction being controlled by RD and WR. The combinations of HBYTE, BHE and HA0 control the portion of the bus that is being utilized. HA[0:3] and RBNK <0:1> (DLCR7 <2:3>) select the set of internal registers for access. |

| HWORD    | 0    | HOST WORD CONFIGURATION. This pin is the complement of the register bit HBYTE (DLCR6 <5>). If HBYTE is a '0', the Host interface is configured for word transfers. If HBYTE is a '1', the Host interface is configured for byte transfers on the lower bus, HD[0:7].                                                                                      |

#### **BUFFER MEMORY INTERFACE**

| RCS0, RCS1 | 0   | RAM CHIP SELECT. RCSO and RCS1 are active low chip select lines for the SRAM with RCSO as the least significant byte.                                                                                                                                                                                        |

|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ŌĒ         | 0   | RAM OUTPUT ENABLE. Active low. This is the output enable asserted by the 8360 during buffer memory read cycles for the SRAM.                                                                                                                                                                                 |

| WE         | 0   | RAM WRITE ENABLE. Active low. This is the write enable asserted by the 8360 during buffer memory write cycles for the SRAM.                                                                                                                                                                                  |

| RD[0:15]   | 1/0 | RAM DATA BUS. This is the data bus between the 8360 and the buffer memory. It can be configured for byte or word transfer depending on register bit RBYTE (DLCR6 <4>) RAM BYTE. For word transfers, the ordering of the most and least significant byte is defined by the register bit, INTLMOT (DLCR7 <0>). |

| RA[0:15]   | 0   | RAM ADDRESS BUS. Addresses up to 64 KByte of SRAM buffer memory.                                                                                                                                                                                                                                             |

#### **NETWORK INTERFACE**

| TDN, TDP | 0 | TRANSMIT DATA NEGATIVE and POSITIVE. Differential outputs to the transceiver for transmission.                                                          |

|----------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDN, RDP | I | RECEIVE DATA NEGATIVE and POSITIVE. Manchester differential inputs from the transceiver for reception.                                                  |

| CDN, CDP | I | COLLISION DETECT NEGATIVE and POSITIVE. When the transceiver detects a collision on the media, these differential inputs are driven by a 10 MHz signal. |

| REXT     | - | EXTERNAL RESISTOR. External biasing resistor for the Attachment Unit Interface (AUI).                                                                   |

#### EXTERNAL ENCODER/DECODER INTERFACE

The following eight pins are provided for connection to an external encoder/decoder in the optional mode of using an external encoder/decoder with the 78Q8360. They are also used as monitor pins for test purposes. In normal network interface applications these pins are not used and are pulled-up internally. Optional modes of configuration are determined by the EEDCNTL <1:0> register bits DLCR7<7:6>.

#### CONTROLLER-ENCODER/DECODER INTERFACE

| NAME | TYPE | DESCRIPTION                                                                                                  |

|------|------|--------------------------------------------------------------------------------------------------------------|

| TXD  | 1/0  | TRANSMIT DATA. Normally not used. (Non-Return to Zero) NRZ transmit serial data.                             |

| TXC  | 1/0  | TRANSMIT CLOCK. Normally not used. A synchronous 10 MHz clock with the serially transmitted data, TXD.       |

| TXE  | 1/0  | TRANSMIT ENABLE. Normally not used. Enable for transmission.                                                 |

| COL  | 1/0  | COLLISION. Normally not used. Active high collision signal.                                                  |

| LOOP | 1/0  | LOOP BACK. Normally not used. ENDEC loop back test signal.                                                   |

| RXD  | 1/0  | RECEIVE DATA. Normally not used. NRZ serial receive data.                                                    |

| RXC  | 1/0  | RECEIVE CLOCK. Normally not used. A synchronous 10 MHz recovered clock with the serially received data, RXD. |

| CRS  | I/O  | CARRIER SENSE. Normally not used. When asserted high, it signifies that a carrier is active in the media.    |

#### **ENCODER/DECODER PIN INPUT/OUTPUT TABLE**

| EEDCNTL <1:0> | MODE     | TXD                                                                  | TXC                                          | TXE | LOOP | RXD | RXC | CRS | COL |

|---------------|----------|----------------------------------------------------------------------|----------------------------------------------|-----|------|-----|-----|-----|-----|

| 00            | Normal   | On-chip                                                              | On-chip internal ENDEC is used with the 8360 |     |      |     |     |     |     |

|               | 78Q8360  | ZU                                                                   | ΖU                                           | ZU  | ZU   | ZU  | ZU  | ZU  | ZU  |

| 01            | 78Q8360  | On-chip internal ENDEC is used with the 8360                         |                                              |     |      |     |     |     |     |

|               | Monitor  | 0                                                                    | 0                                            | 0   | 0    | 0   | 0   | 0   | 0   |

| 10            | External | External External ENDEC is used with the 8360, internal ENDEC is off |                                              |     |      |     |     |     |     |

|               | ENDEC    | 0                                                                    | I                                            | 0   | 0    | ı   | 1   | I   | l   |

| 11            | ENDEC    | DEC On-chip internal ENDEC is used only, the 8360 controller is off  |                                              |     |      |     |     |     |     |

|               | Test     | 1                                                                    | 0                                            | 1   | I    | 0   | 0   | 0   | 0   |

ZU: High impedance with internal pull-up

# 61E D ■ 8253965 0008311 462 ■ SIL SSI 78Q8360 Ethernet Controller/ ENDEC Combo

#### PIN DESCRIPTION (continued)

#### **DEVICE POWER**

| NAME | TYPE | DESCRIPTION                                                                                                                                                                 |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD  | Р    | POWER SUPPLY. A +5V DC (±5%) supply is required.                                                                                                                            |

| GND  | Р    | SYSTEM GROUND.                                                                                                                                                              |

| AVDD | Р    | ANALOG VDD. The analog VDD pin required by the internal encoder/decoder is to be connected to a different VDD path from the digital VDD. A +5V DC (±5%) supply is required. |

| AGND | Р    | ANALOG GROUND. The analog ground required by the internal encoder/ decoder is to be connected to a separate GND path from the digital GND.                                  |

#### **CRYSTAL OSCILLATOR**

| OSCI | 1 | OSCILLATOR IN. Connection for one side of the 20 MHz crystal or an input for an external 20 MHz clock source.   |

|------|---|-----------------------------------------------------------------------------------------------------------------|

| osco | 0 | OSCILLATOR OUT. Connection for other side of the 20 MHz crystal. Left unconnected if an external clock is used. |

#### **MISCELLANEOUS**

| СВ   | 0 | CONTROL BIT. A complement of the internal register bit, DLCR4 <2>, which is used to activate any external hardware.                                                                                                                                                                                  |

|------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRST | 0 | REMOTE RESET. This pin follows the RMTRST register bit (DLCR1 <4>). The RMTRST bit is '1' only if a packet with the pattern 0900H in the Type Field is detected and ENA_RMTRST (DLCR5 <2>) is activated. This feature can be used by the nodes on the network to remotely-control external hardware. |

| CK20 | 0 | 20 MHz CLOCK: A 20 MHz free-running buffered clock output provided by the crystal oscillator circuit.                                                                                                                                                                                                |

#### **CONTROL AND STATUS REGISTERS**

The registers in the 8360 can be divided into 5 groups: the Data Link Control Registers (DLCR0-7), Node ID registers (IDR8-13), Time Domain Reflectometry Registers (TDR14-15), Hash Table Registers (HTR8-15) and Buffer Memory Registers (BMR8-15).

The Data Link Control Registers contain the transmit and receive status information, interrupt enable, 8360 setup and software reset bit (DLCR6<7>). They are accessed through direct register addresses xxx0H through xxx7H. The Ethernet Node ID is stored in IDR 8-15. The TDR14-15 registers are used to provide the count value of the number of bits transmitted for each packet. This value can indicate whether a packet has completed its transmission or has encountered a collision. Both the Node ID and the Time Domain Reflectometry Registers can be accessed through direct register addresses xxx8H through xxxFH.

The Hash Table Registers (HTR8-15) provide a means for filtering incoming multicast packets. Any packet that does not match the hash table coding will be rejected. The HTR8-15 can be accessed by the bankswitching addresses RBNK<1:0> (DLCR7 <3:2>).

The final group of the registers belongs to the Buffer Memory Registers (BMR8-15). The tasks performed by these registers include transferring of packets between the host and the 8360 (via BMR8-9), collision control. DMA operations and activation of the transmit operation. A summary table of the registers and their addresses are tabulated below:

| RBNK<1:0> | НАЗ | HA2 | HA1 | HA0 | ADDRESS | DESCRIPTION             |

|-----------|-----|-----|-----|-----|---------|-------------------------|

| XX        | 0   | 0   | 0   | 0   | DLCR0   | Transmit Status         |

| XX        | 0   | 0   | 0   | 1   | DLCR1   | Receive Status          |

| xx        | 0   | 0   | 1   | 0   | DLCR2   | Transmit Interrupt Mask |

| XX        | 0   | 0   | 1   | 1   | DLCR3   | Receive Interrupt Mask  |

| XX        | 0   | 1   | 0   | 0   | DLCR4   | Transmit Mode           |

| XX        | 0   | 1   | 0   | 1   | DLCR5   | Receive Mode            |

| XX        | 0   | 1   | 1   | 0   | DLCR6   | Configuration 1         |

| xx        | 0   | 1   | 1   | 1   | DLCR7   | Configuration 2         |

| 00        | 1   | 0   | 0   | 0   | IDR8    | NODE ID 0               |

| 00        | 1   | 0   | 0   | 1   | IDR9    | NODE ID 1               |

| 00        | 1   | 0   | 1   | 0   | IDR 10  | NODE ID 2               |

| 00        | 1   | 0   | 1   | 1   | IDR11   | NODE ID 3               |

| 00        | 1   | 1   | 0   | 0   | IDR12   | NODE ID 4               |

| 00        | 1   | 1   | 0   | 1   | IDR13   | NODE ID 5               |

| 00        | 1   | 1   | 1   | 0   | TDR14   | TDR 0 (LSB)             |

| 00        | 1   | 1   | 1   | 1   | TDR15   | TDR 1 (MSB)             |

#### **CONTROL AND STATUS REGISTERS** (continued)

| RBNK<1:0> | НАЗ | HA2 | HA1 | HA0 | ADDRESS | DESCRIPTION                        |

|-----------|-----|-----|-----|-----|---------|------------------------------------|

| 01        | 1   | 0   | 0   | 0   | HTR8    | Hash Table 0                       |

| 01        | 1   | 0   | 0   | 1   | HTR9    | Hash Table 1                       |

| 01        | 1   | 0   | 1   | 0   | HTR10   | Hash Table 2                       |

| 01        | 1   | 0   | 1   | 1   | HTR11   | Hash Table 3                       |

| 01        | 1   | 1   | 0   | 0   | HTR12   | Hash Table 4                       |

| 01        | 1   | 1   | 0   | 1   | HTR13   | Hash Table 5                       |

| 01        | 1   | 1   | 1   | 0   | HTR14   | Hash Table 6                       |

| 01        | 1   | 1   | 1   | 1   | HTR15   | Hash Table 7                       |

| 10        | 1   | 0   | 0   | 0   | BMR8    | Buffer Memory I/O Port             |

| 10        | 1   | 0   | 0   | 1   | BMR9    | Buffer Memory I/O Port (word mode) |

| 10        | 1   | 0   | 1   | 0   | BMR10   | Transmit Start + Packet Count      |

| 10        | 1   | 0   | 1   | 1   | BMR11   | 16 Collisions Control              |

| 10        | 1   | 1   | 0   | 0   | BMR12   | DMA Enable                         |

| 10        | 1   | 1   | 0   | 1   | BMR13   | DMA Burst                          |

| 10        | 1   | 1   | 1   | 0   | BMR14   | Skip Packet                        |

| 10        | 1   | 1   | 1   | 1   | BMR15   | Reserved                           |

| 11        | Х   | ×   | Х   | ×   | -       | RESERVED                           |

Note: All registers are both word and byte accessible. In word mode, register bytes are paired up. IDR and HTR can only be accessed when ENADLC (DLCR 6<7>) is a '1'. In byte mode, only BMR8 will be used.

#### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

Operation beyond the maximum ratings may damage the device.

| PARAMETER                                  | RATING                         |

|--------------------------------------------|--------------------------------|

| Supply voltage, V <sub>DD</sub>            | -0.5 to 6.0V                   |

| Input voltage, V <sub>IN</sub>             | -0.5 to V <sub>DD</sub> + 0.5V |

| Output voltage, V <sub>OUT</sub>           | -0.5 to V <sub>DO</sub> + 0.5V |

| Storage temperature, T <sub>STG</sub>      | -55 to 150°C                   |

| Lead temperature (max 10 sec soldering), T | 250°C max                      |

#### DC CHARACTERISTICS

$(TA = 0^{\circ}C \text{ to } +70^{\circ}C, V_{DD} = 5V \pm 5\%)$

| PARAMETER                                                                 | CONDITIONS               | MIN NO                | MAX             | UNIT |

|---------------------------------------------------------------------------|--------------------------|-----------------------|-----------------|------|

| Low level input voltage V                                                 | TTL inputs               | 0                     | 0.8             | V    |

| , -                                                                       | OSCI pin                 | 0                     | 1.4             | ٧    |

|                                                                           | RESET pin                | 0                     | 1.2             | ٧    |

| High level input voltage V                                                | H TTL inputs             | 2.0                   | V <sub>DD</sub> | ٧    |

|                                                                           | OSCI pin                 | 3.2                   | V <sub>DD</sub> | V    |

|                                                                           | RESET pin                | 1.8                   | V <sub>DD</sub> | ٧    |

| Low level output voltage V <sub>c</sub>                                   | Rated I <sub>OL</sub>    | 0                     | 0.4             | V    |

|                                                                           | I <sub>OL</sub> = 20 μA  | 0                     | 0.1             | ٧    |

| High level output voltage V <sub>c</sub>                                  | Rated I <sub>OH</sub>    | 2.4                   | V <sub>DD</sub> | ٧    |

|                                                                           | I <sub>OH</sub> = -20 μA | V <sub>DD</sub> - 0.1 | V <sub>DD</sub> | V    |

| Low level output current (1) Io(pin types On, IOn and IOnU)               | $V_{OL} = 0.4V$          | n                     |                 | mA   |

| High level output current (1) I <sub>C</sub> (pin types On, IOn and IOnU) | $V_{OH} = 2.4V$          | -n                    |                 | mA   |

| Leakage current (input/output)                                            | I,                       | -10                   | 10              | μΑ   |

| Supply current (2)                                                        | Fully active             |                       | 50              | mA   |

|                                                                           | Idle                     |                       | 25              | mA   |

| Power down supply                                                         |                          |                       |                 |      |

| current (2)                                                               | Osc. on                  |                       | 5               | mA   |

|                                                                           | Osc. off                 | 1 1                   | 1               | mA   |

Note: (1) "n" refers to the rated output current and takes the value of 2, 4, 8, 16 depending on the pins.

(2) Inputs at VCC or GND. Fully active means 3 "simultaneous" operations: transmitting, receiving and either host write or read.

#### **ELECTRICAL SPECIFICATIONS** (continued)

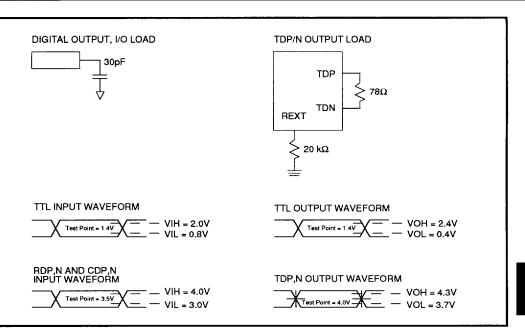

#### **AUI CHARACTERISITICS**

$(TA = 0 \text{ to } 70 \text{ °C}, VDD = 5V \pm 5\%)$

Input refers to RDP, N and CDP, N. Output refers to TDP, N.

| PARAMETER                                           | CONDITIONS                                        | MIN  | NOM  | MAX                      | UNIT |

|-----------------------------------------------------|---------------------------------------------------|------|------|--------------------------|------|

| AC Common Mode Output Voltage V <sub>ACCM</sub>     |                                                   |      |      | ±40                      | mV   |

| DC Common Mode Output Voltage V <sub>DCCM</sub>     |                                                   | 3.0  | 4.0  | V <sub>DD</sub> -<br>0.5 | ٧    |

| Differential Peak Output Voltage<br>V <sub>OP</sub> | $R_{EXT} = 20 \text{ k}\Omega$ $R_{T} = 78\Omega$ | 0.7  | 0.9  | 1.1                      | ٧    |

| Output Current I <sub>OP</sub>                      | $R_{EXT} = 20 \text{ k}\Omega$                    | 9    | 11   | 13                       | mA   |

| Input Squeich Threshold Voltage<br>V <sub>SQ</sub>  |                                                   | -140 | -190 | -260                     | mV   |

| Open Circuit Input Bias Voltage                     |                                                   | 2.5  | 3.5  | V <sub>DD</sub> -        | ٧    |

| V <sub>BIAS</sub>                                   |                                                   |      |      | 0.5                      |      |

#### CAPACITANCE

| Input pin capacitance  | C <sub>IN</sub>  |  | 10 | pF |

|------------------------|------------------|--|----|----|

| Output pin capacitance | C <sub>OUT</sub> |  | 10 | pF |

| I/O pin capacitance    | c <sup>ю</sup>   |  | 10 | рF |

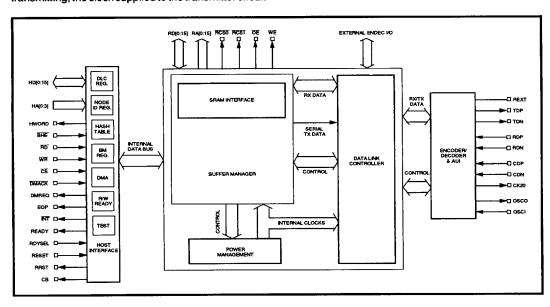

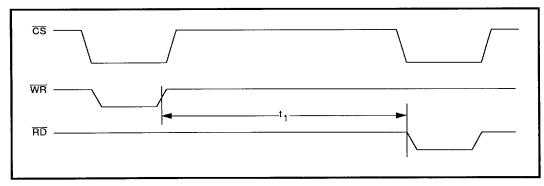

FIGURE 3: Read Cycle

**TABLE 1: Read Cycle**

| PARAMETER                                                     | CONDITIONS      | MIN | NOM | MAX | UNIT |

|---------------------------------------------------------------|-----------------|-----|-----|-----|------|

| CS low to RD low;<br>HA[0:3] valid to RD low t <sub>1</sub>   |                 | 0   |     |     | ns   |

| RD high to CS high; RD high to HA[0:3] invalid t <sub>2</sub> |                 | 0   |     |     | ns   |

| RD low pulse width t <sub>3</sub>                             |                 | 30  | 1   |     | ns   |

| RD low to READY low t <sub>4</sub>                            | (a)             | 0   |     | 35  | ns   |

| RD low to READY high (1) t <sub>5</sub>                       | (a)             |     |     | 400 | ns   |

| RD low to READY low (1) t <sub>6</sub>                        | (b)             | 0   |     | 400 | ns   |

| RD high to READY high t <sub>7</sub>                          | (b)             | 0   |     | 25  | ns   |

| RD low to READY low t <sub>8</sub>                            | (d)             | 0   |     | 25  | ns   |

| RD high to READY high t <sub>9</sub>                          | (d)             | 0   |     | 25  | ns   |

| RD low to HD[0:15] valid t <sub>10</sub>                      | Register access |     |     | 45  | ns   |

| READY high to HD[0:15] validt <sub>11</sub>                   | Port access     |     |     | 0   | ns   |

| READY low to HD[0:15] valid t <sub>12</sub>                   | Port access     |     |     | 0   | ns   |

| RD high to HD[0:15] invalid (data hold) t <sub>13</sub>       |                 | 10  |     |     | ns   |

Note: (1) Maximum of 400 ns may occur if system makes contiguous system read cycles at less than 100 ns intervals, and both the transmitter and receiver are active in "loopback" reception (if the transmitter and receiver are idle, the max value becomes 250 ns). 2.4 µs max for host read error.

- (a) For Buffer Memory Port when port is busy and RDYSEL = 1.

- (b) For Buffer Memory Port when port is busy and RDYSEL = 0.

- (c) For register or port is not busy and RDYSEL = 1.

- (d) For register or port is not busy and RDYSEL = 0.

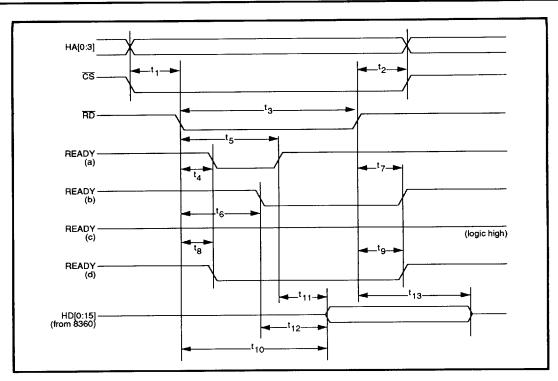

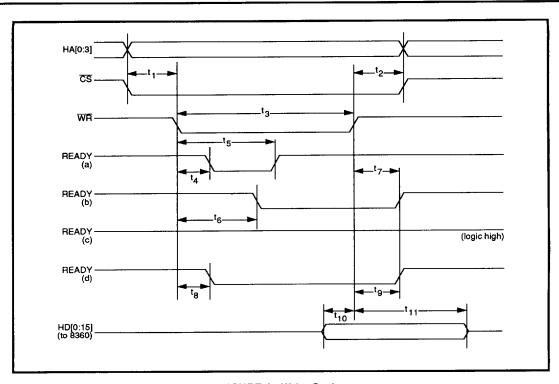

FIGURE 4: Write Cycle

**TABLE 2: Write Cycle**

| PARAMETER                                      |                 | CONDITIONS | MIN | NOM | MAX | UNIT |

|------------------------------------------------|-----------------|------------|-----|-----|-----|------|

| CS low to WR low;<br>HA[0:3] valid to WR low   | t,              |            | 0   |     |     | ns   |

| WR high to CS high; WR high to HA[0:3] invalid | t <sub>2</sub>  | :          | 0   |     |     | ns   |

| WR low pulse width                             | t <sub>3</sub>  |            | 30  |     |     | ns   |

| WR low to READY low                            | t <sub>4</sub>  | (a)        | 0   | 1   | 35  | ns   |

| WR low to READY high (1)                       | t <sub>5</sub>  | (a)        |     |     | 400 | ns   |

| WR low to READY low (1)                        | t <sub>6</sub>  | (b)        | 0   |     | 400 | ns   |

| WR high to READY high                          | t <sub>7</sub>  | (b)        |     |     | 25  | ns   |

| WR low to READY low                            | t <sub>e</sub>  | (d)        | 0   |     | 25  | ns   |

| WR high to READY high                          | t <sub>g</sub>  | (d)        | 0   |     | 25  | ns   |

| HD[0:15] valid to WR high (data setup)         | t <sub>10</sub> |            | 15  |     |     | ns   |

| WR high to HD[0:15] invalid (data hold)        | t <sub>11</sub> |            | 10  |     |     | ns   |

Note: (1) Maximum of 400 ns may occur if system makes contiguous system read cycles at less than 100 ns intervals, and both the transmitter and receiver are active on "loopback" reception (if the transmitter and receiver are idle, the max value becomes 250 ns). 2.4 µs max for host write error.

- (a) For Buffer Memory Port when port is busy and RDYSEL = 1.

- (b) For Buffer Memory Port when port is busy and RDYSEL = 0.

- (c) For register or port is not busy and RDYSEL = 1.

- (d) For register or port is not busy and RDYSEL = 0.

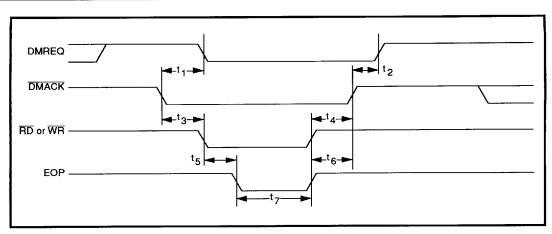

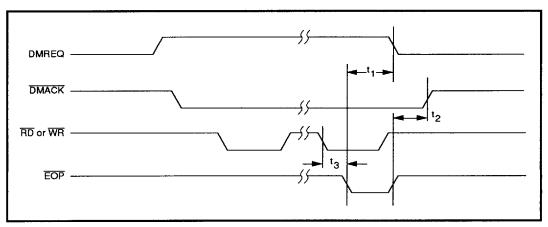

FIGURE 5: Single-Cycle DMA Timing

TABLE 3: Single-Cycle DMA Timing

| PARAMETER                                  | CONDITIONS | MIN | МОМ | MAX | UNIT |

|--------------------------------------------|------------|-----|-----|-----|------|

| DMACK low to DMREQ low t <sub>1</sub>      |            | 0   |     | 20  | ns   |

| DMACK high to DMREQ high t <sub>2</sub>    |            | 0   |     | 20  | ns   |

| DMACK low to RD or WR low t <sub>3</sub>   |            | 0   |     |     | ns   |

| RD or WR high to DMACK high t <sub>4</sub> |            | 0   |     |     | ns   |

| RD or WR low to EOP low t <sub>5</sub>     |            | 0   |     |     | ns   |

| EOP high to DMACK high t <sub>6</sub>      |            | 0   |     |     | ns   |

| EOP low pulse width t <sub>7</sub>         | 774        | 10  |     |     | ns   |

Note: (1) An asserted EOP terminates any further DMREQ after DMACK returns high.

- (2) The DMA cycle uses DMACK as the chip select. DMACK overrides CS and HA[0:3] if they are both asserted at the same time, forcing selection of the Buffer Memory Port as in a DMA cycle.

- (3) For READY timing and HD[0:15] timing, see Figure 3, t<sub>4</sub>-t<sub>13</sub>, and Figure 4, t<sub>4</sub>-t<sub>11</sub>.

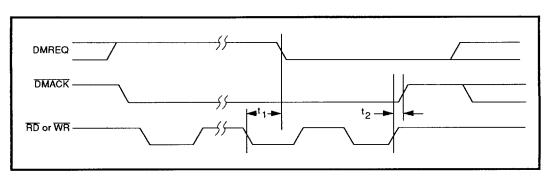

FIGURE 6: Burst DMA Timing

**TABLE 4: Burst DMA Timing**

| PARAMETER                                                               | CONDITIONS | MIN | NOM | MAX | UNIT |

|-------------------------------------------------------------------------|------------|-----|-----|-----|------|

| $\overline{\text{RD}}$ or $\overline{\text{WR}}$ low to DMREQ low $t_1$ |            |     |     | 30  | ns   |

| RD or WR high to DMACK high t <sub>2</sub>                              |            | 0   |     |     | ns   |

Note: (1) DMREQ goes low during the next-to-last transfer of the burst. DMACK should not go high until after the RD or WR pulse of the last transfer cycle goes high

- (2) The DMA cycle uses DMACK as the chip select. DMACK overrides CS and HA[0:3] if they are both asserted at the same time, forcing selection of the Buffer Memory Port as in a DMA cycle.

- (3) For READY timing and HD[0:15] timing, see Figure 3, t<sub>4</sub>-t<sub>13</sub>, and Figure 4, t<sub>4</sub>-t<sub>11</sub>.

61E D ■ 8253965 0008322 248 ■ SIL

SSI 78Q8360 Ethernet Controller/ ENDEC Combo

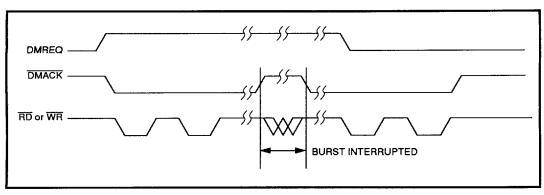

FIGURE 7: Burst DMA Interrupted by DMACK

Note: Burst can be interrupted by DMACK high-going pulse during the burst. Burst will resume when DMACK returns low.

FIGURE 8: Burst DMA Terminated by EOP

**TABLE 5: Burst DMA Terminated by EOP**

| PARAMETER               |                | CONDITIONS | MIN | NOM | MAX | UNIT |

|-------------------------|----------------|------------|-----|-----|-----|------|

| EOP low to DMREQ low    | t,             |            | 4   |     | 28  | ns   |

| EOP high to DMACK high  | t <sub>2</sub> |            | 3   |     |     | ns   |

| RD or WR low to EOP low | t <sub>3</sub> |            | 0   |     |     | ns   |

Note: EOP can be asserted during any transfer of the burst to terminate the process following that transfer.

#

FIGURE 9: RESET Timing

**TABLE 6: RESET Timing**

| PARAMETER                 |                | CONDITIONS | MIN | МОМ | MAX | UNIT |

|---------------------------|----------------|------------|-----|-----|-----|------|

| RESET pulse width         | t,             |            | 200 |     |     | ns   |

| RESET low to first CS low | t <sub>2</sub> |            | 300 |     |     | ns   |

Note: Before enabling transmit and receive functions (ENADLC), wait 10 µs after reset pulse for internal calibration of DPLL.

FIGURE 10: Skip Packet Timing

**TABLE 7: Skip Packet Timing**

| PARAMETER                                                   | CONDITIONS | MIN | МОМ | MAX | UNIT |  |  |  |  |  |

|-------------------------------------------------------------|------------|-----|-----|-----|------|--|--|--|--|--|

| Writing Skip Packet high to next Buffer Memory Port read t, |            | 200 |     |     | ns   |  |  |  |  |  |

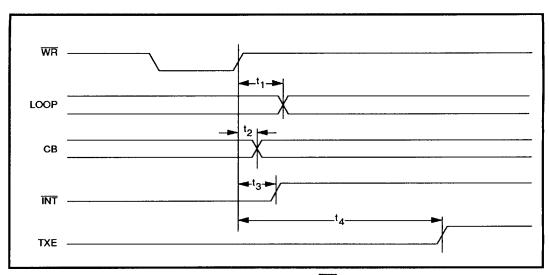

FIGURE 11: LOOP, CB and INT Timing

TABLE 8: LOOP, CB and INT Timing

| PARAMETER                     |                | CONDITIONS                 | MIN | NOM | MAX | UNIT |

|-------------------------------|----------------|----------------------------|-----|-----|-----|------|

| Loopback Control (LOOP) delay | t,             |                            | 5   | :   | 30  | ns   |

| CB delay                      | t <sub>2</sub> |                            | 5   |     | 30  | ns   |

| INT signal clearing delay     | t <sub>3</sub> |                            | 7   |     | 40  | ns   |

| Transmit enable delay after   |                | Network free and 8360 idle |     |     |     |      |

| setting TXST high             | t <sub>4</sub> |                            |     |     | 1   | μs   |

Note: TXST is BMR10<7>

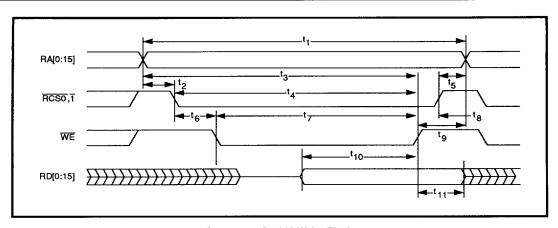

# RA[0:15] RCS0,1 RD[0:15] RD[0:15]

FIGURE 12: SRAM Read Timing

TABLE 9: SRAM Read Timing

| PARAMETER                      |                | CONDITIONS | MIN | NOM | MAX | UNIT |

|--------------------------------|----------------|------------|-----|-----|-----|------|

| Read cycle                     | t,             | RAMSP = 1  | 95  |     |     | ns   |

|                                | ·              | RAMSP = 0  | 145 |     |     | ns   |

| Address access time            | t,             | RAMSP = 1  |     |     | 80  | ns   |

|                                | _              | RAMSP = 0  |     |     | 130 | ns   |

| Address valid to RCS0,1 low    | t <sub>3</sub> |            | 0   |     | 5   | ns   |

| RCS0,1 high to address invalid | t <sub>4</sub> |            | 0   |     |     | ns   |

| Chip select access time        | t <sub>5</sub> | RAMSP = 1  |     |     | 80  | ns   |

|                                | _              | RAMSP = 0  |     |     | 130 | ns   |

| OE high to RCS0, 1 high        | t <sub>6</sub> |            | 0   |     | 2   | ns   |

| Output enable access time      | t <sub>7</sub> |            |     |     | 50  | ns   |

| Data hold time                 | t <sub>8</sub> |            | 0   |     |     | ns   |

| Address valid to OE low        | t <sub>9</sub> |            |     |     | 30  | ns   |

Note: Use SRAM with address access time of 80 ns or less for RAMSP = 1 and 130 ns or less for RAMSP = 0. RAMSP is DLCR6 <6>.

FIGURE 13: SRAM Write Timing

TABLE 10: SRAM Write Timing

| PARAMETER                      |                 | CONDITIONS | MIN | NOM | MAX | UNIT |

|--------------------------------|-----------------|------------|-----|-----|-----|------|

| Write Cycle                    | t,              | RAMSP = 1  | 95  |     |     | ns   |

|                                | ·               | RAMSP= 0   | 145 |     |     | ns   |

| Address Valid to RCS0, 1 low   | t <sub>2</sub>  |            | 0   |     | 5   | ns   |

| Address Valid to WE high       | t <sub>3</sub>  | RAMSP = 1  | 70  |     |     | ns   |

|                                | •               | RAMSP = 0  | 120 |     |     | ns   |

| RCS0,1 low to WE high          | t,              | RAMSP = 1  | 70  |     |     | ns   |

|                                | •               | RAMSP = 0  | 120 |     |     | ns   |

| RCS0,1 high to Address Invalid | t <sub>5</sub>  |            | 0   |     |     | ns   |

| RCS0,1 low to WE low           | t <sub>6</sub>  |            | 0   |     |     | ns   |

| WE Pulse Width                 | t,              | RAMSP = 1  | 70  |     |     | ns   |

|                                | ŕ               | RAMSP = 0  | 120 |     |     | ns   |

| WE high to RCS0,1 high         | t <sub>8</sub>  |            | 0   |     |     | ns   |

| WE high to Address Invalid     | t <sub>9</sub>  |            | 20  |     |     | ns   |

| Data Setup Time                | t <sub>10</sub> |            | 40  |     |     | ns   |

|                                | t <sub>11</sub> |            | 20  |     |     | ns   |

Note: Use SRAM with address access time of 80 ns or less for RAMSP = 1 and 130 ns or less for RAMSP = 0. RAMSP is DLCR6 <6>.

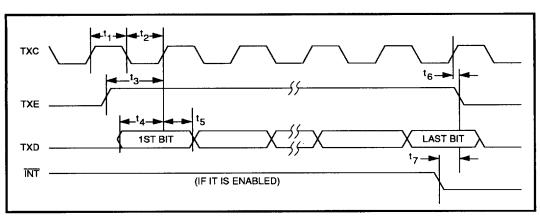

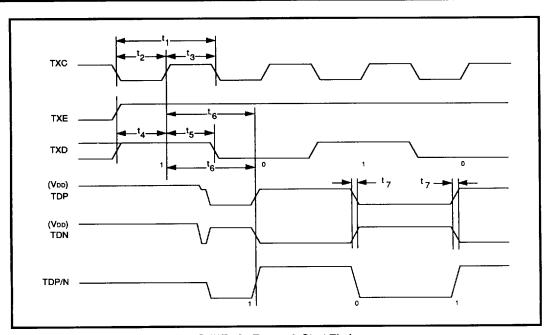

FIGURE 14: Transmit Timing

FIGURE 15: Transmit Timing

FIGURE 16: Transmit Timing

6-51

FIGURE 17: Transmit Timing

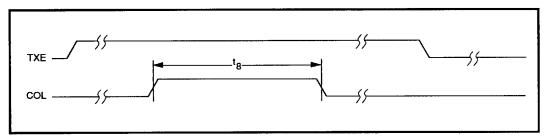

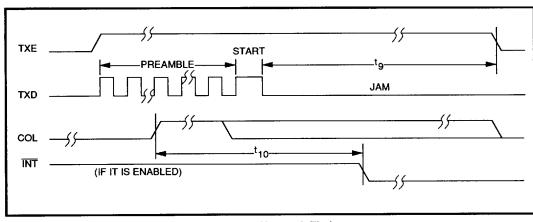

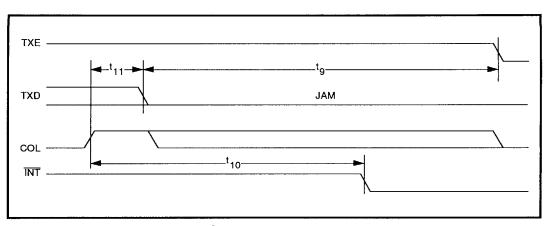

TABLE 11: Transmit Timing: Figure 14-17 (for external Encoder/Decoder mode)

| PARAMETER                                     |                 | CONDITIONS | MIN | NOM | MAX | UNIT       |

|-----------------------------------------------|-----------------|------------|-----|-----|-----|------------|

| Transmit clock high width                     | t,              |            | 45  | 50  | 55  | ns         |

| Transmit clock low width                      | t <sub>2</sub>  |            | 45  | 50  | 55  | ns         |

| TXE high to TXC high                          | t <sub>3</sub>  |            | 65  | -   | -   | ns         |

| Transmit data setup                           | t <sub>4</sub>  |            | 55  | -   | -   | ns         |

| Transmit data hold                            | t <sub>s</sub>  |            | 5   | -   | -   | ns         |

| TXC high to TXE low                           | t <sub>6</sub>  |            | -   | -   | 35  | ns         |

| Transmit interrupt low to transmit enable low | t <sub>7</sub>  |            | -   | 1   | _   | TXC cycles |

| Minimum collision length                      | t <sub>g</sub>  |            | 200 | -   | -   | ns         |

| Jam period <sup>(1)</sup>                     | t <sub>9</sub>  |            | -   | 32  | -   | TXC cycles |

| Transmit interrupt from collision             | t <sub>10</sub> |            | -   | -   | 5   | TXC cycles |

| Collision at data field to first jam bit      | t <sub>11</sub> |            | _   | -   | 5   | TXC cycles |

Note: (1) The 32 jam bits consists of all zeroes.

**ENDEC Combo**

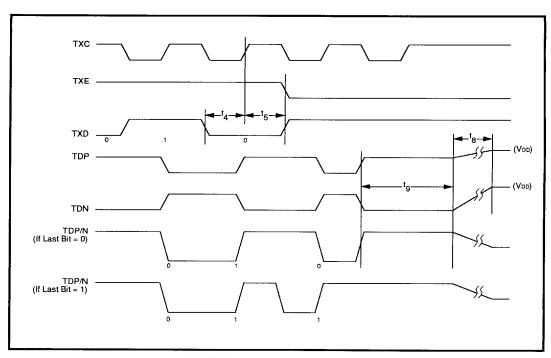

FIGURE 18: Transmit Start Timing

FIGURE 19: Transmit End Timing

TABLE 12: Transmit Start and End Timing: Figure 18-19 (for Encoder/Decoder Test mode)

| PARAMETER                     |                  | ETER CONDITIONS                          |       | NOM | MAX    | UNIT |

|-------------------------------|------------------|------------------------------------------|-------|-----|--------|------|

| TXC cycle time                | t,               |                                          | 99.99 | 100 | 100.01 | ns   |

| TXC high width                | t <sub>2</sub>   |                                          | 40    | 50  | 60     | ns   |

| TXC low width                 | t <sub>3</sub>   |                                          | 40    | 50  | 60     | ns   |

| TXD, TXE setup time to TXC    | ; t₄             |                                          | -     | 30  | -      | ns   |

| TXD, TXE hold time from TX    | C t <sub>5</sub> |                                          | -     | 20  | -      | ns   |

| TDP/N encode time             | t <sub>6</sub>   |                                          | -     | 90  | -      | ns   |

| TDP,N fall/rise time          | t <sub>7</sub>   | 20% to 80%, REXT = 20 kΩ,<br>$R_T = 78Ω$ | -     | 2   | -      | ns   |

| TDP/N line voltage transition | t <sub>8</sub>   |                                          | -     | -   | 8      | μs   |

| TDP/N end-of-packet delimiter | t <sub>9</sub>   |                                          | 200   | -   | -      | ns   |

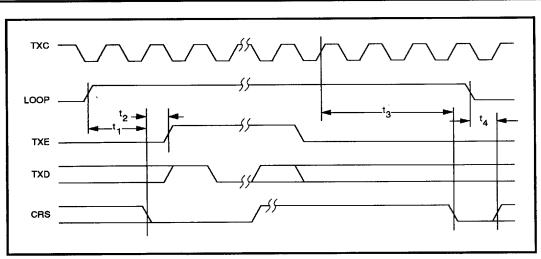

FIGURE 20: Loopback Timing

TABLE 13: Loopback Timing (for Encoder/Decoder test mode)

| PARAMETER                          | R CONDITIONS   |     | МОМ | MAX | UNIT |

|------------------------------------|----------------|-----|-----|-----|------|

| Loop receiving data purge time     | t,             | -   | 180 | -   | ns   |

| Wait time from CRS low to TXE high | t <sub>2</sub> | 9.6 | _   | •   | μs   |

| Data through time                  | t <sub>3</sub> | -   | 190 | •   | ns   |

| Loop receiving data accept time    | t <sub>4</sub> | -   | 30  | •   | ns   |

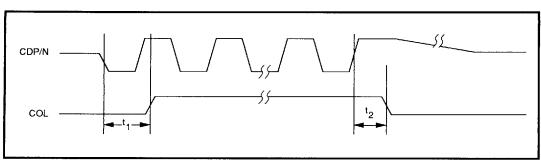

FIGURE 21: Collision Timing

TABLE 14: Collision Timing (for Encoder/Decoder Test mode)

| PARAMETER          |                | CONDITIONS | MIN | NOM | MAX | UNIT |

|--------------------|----------------|------------|-----|-----|-----|------|

| COL on delay time  | t,             |            | _   | 40  | 50  | ns   |

| COL off delay time | t <sub>2</sub> |            | -   | 270 | 300 | ns   |

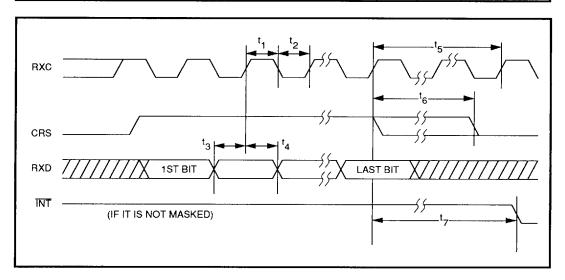

FIGURE 22: Receive Timing

Ethernet Controller/ ENDEC Combo

TABLE 15: Receive Timing (for external Encoder/Decoder mode)

| PARAMETER                                 |                 | CONDITIONS  | MIN | МОИ | MAX | UNIT       |

|-------------------------------------------|-----------------|-------------|-----|-----|-----|------------|

| Receive clock high width                  | t,              |             | 40  |     |     | ns         |

| Receive clock low width                   | t <sub>2</sub>  |             | 40  |     |     | ns         |

| Receive data and carrier sense setup      | .t <sub>3</sub> |             | 20  |     |     | ns         |

| Receive data and carrier sense hold       | t <sub>4</sub>  |             | 20  |     |     | ns         |

| Number of RXC cycles after last bit       | t <sub>5</sub>  |             | 1   |     |     | RXC cycles |

| Receive carrier sense drop after last bit | t <sub>6</sub>  |             |     |     | 7   | RXC cycles |

| Last bit of packet                        | t,              | Good packet |     |     | 8   | RXC cycles |

| received to interrupt                     | ,               | Bad packet  |     |     | 2   | RXC cycles |

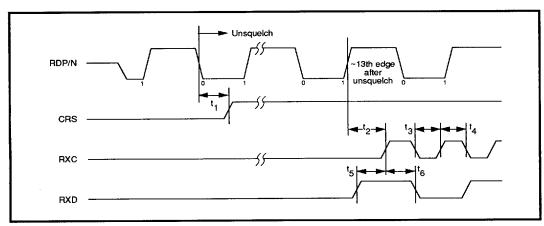

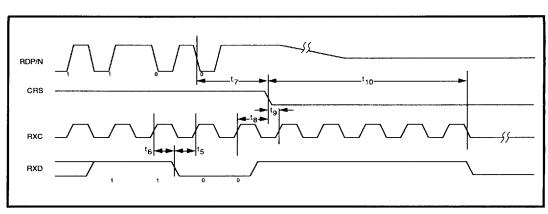

FIGURE 23: Receive Start Timing

FIGURE 24: Receive End Timing

TABLE 16: Receive Timing: Figure 23-24 (for Encoder/Decoder Test mode)

| PARAMETER                           |                 | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN | NOM | MAX | UNIT   |

|-------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| CRS on delay time                   | t,              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -   | 150 | 220 | ns     |