### SYNCHRONOUS ADDRESS MULTIPLEXER

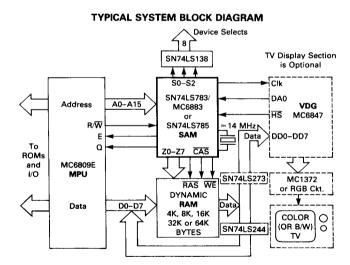

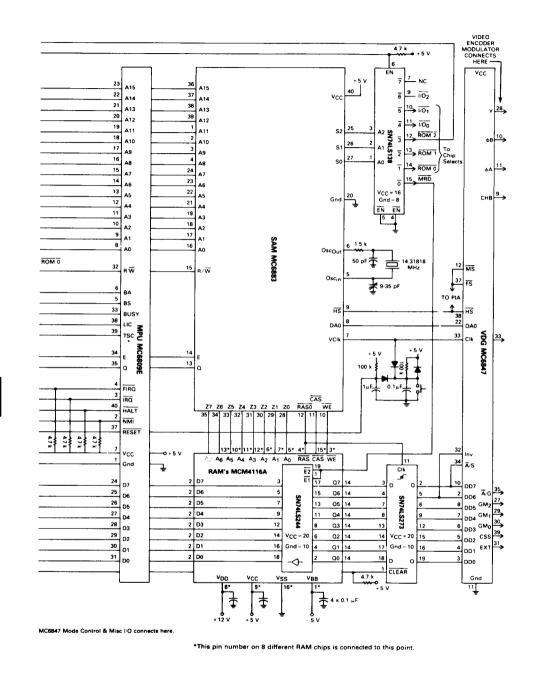

The SN74LS783/MC6883 and SN74LS785 bring together the MC6809E (MPU), the MC6847 (Color Video Display Generator) and dynamic RAM to form a highly effective, compact and cost effective computer and display system.

The SN74LS783/MC6883 is designed to support 4K x 1, 16K x 1 and 64K x 1 (128 column refresh) dynamic RAMs. The SN74LS785 has been modified to support the above listed products as well as 16K x 4 and 64K x 1 (256 column refresh) dynamic RAMs. A further enhancement allows the LS785 to support low power dynamic ROMs (such as MCM68364) without additional logic.

- MC6809E, MC6800, MC6801E, MC68000 and MC6847 (VDG) Compatible

- Transparent MPU/VDG/Refresh

- RAM size 4K, 8K, 16K, 32K or 64K Bytes (Dynamic or Static)

- Addressing Range 96K Bytes

- Single Crystal Provides All Timing

- Register Programmable:

- VDG Addressing Modes VDG Offset (0 to 64K) RAM Size Page Switch MPU Rate (Crystal ÷ 16 or ÷ 8) MPU Rate (Address Dependent or Independent)

- System "Device Selects" Decoded 'On Chip'

- Timing is Optimized for Standard Dynamic RAMs

- +5.0 V Only Operation

- Easy Synchronization of Multiple SAM Systems

- DMA Mode

# SN74LS783/ MC6883 SN74LS785

## SYNCHRONOUS ADDRESS MULTIPLEXER

#### LOW POWER SCHOTTKY

#### FAST AND LS TTL DATA

5-323

MAXIMUM RATINGS (T<sub>A</sub> = 25°C unless otherwise noted.)

| Rating                              | Symbol   | Value                   | Unit |

|-------------------------------------|----------|-------------------------|------|

| Power Supply Voltage                | Vcc      | -0.5 to +7.0            | Vdc  |

| Input Voltage (Except Oscin)        | VI       | -0.5 to 10              | Vdc  |

| Input Current (Except Oscin)        | <u> </u> | -30 to +5.0             | mA   |

| Output Voltage                      | Vo       | -0.5 to +7.0            | Vdc  |

| Operating Ambient Temperature Range | TA       | 0 to +70                | °C   |

| Storage Temperature Range           | Tstg     | -65 to +150             | °C   |

| Input Voltage Oscin                 | VIOscin  | -0.5 to V <sub>CC</sub> | Vdc  |

| Input Current Oscin                 | liOscin  | -0.5 to +5.0            | mA   |

#### **GUARANTEED OPERATING RANGES**

| Parameter                                  | Symbol          | Min  | Тур | Max   | Unit |

|--------------------------------------------|-----------------|------|-----|-------|------|

| Supply Voltage                             | Vcc             | 4.75 | 5.0 | 5.25  | v    |

| Operating Ambient Temperature Range        | TA              | 0    | 25  | 75    | °C   |

| Output Current High<br>RAS0, RAS1, CAS, WE | юн              | _    | _   | - 1.0 | mA   |

| All Other Outputs                          |                 | -    | -   | - 0.2 |      |

| Output Current Low<br>RASO, RAS1, CAS, WE  | <sup>I</sup> OL | _    | _   | 8.0   | mA   |

| VClk                                       |                 | _    |     | 0.8   | 1    |

| All Other Outputs                          | 1               | _    |     | 4.0   | 1    |

DC CHARACTERISTICS (Unless otherwise noted specifications apply over recommended power supply and temperature ranges.)

| Characterístic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Cum hal                           | Adda                                 | <b>T</b> |                           | 11-14- |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------|----------|---------------------------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Symbol                            | Min                                  | Тур      | Max                       | Units  |

| Input Voltage — High Logic State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Чн                                | 2.0                                  | -        | —                         | V      |

| Input Voltage — Low Logic State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | VIL                               |                                      | -        | 0.8                       | v      |

| Input Clamp Voltage<br>(V <sub>CC</sub> = Min, I <sub>in</sub> = -18 mA) All Inputs Except Osc <sub>In</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Viк                               | -                                    | -        | - 1.5                     | v      |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | i i                               |                                      | -        | 200<br>100<br>250<br>100  | μA     |

| Input Current High Logic State All Inputs Except VClk,   (V <sub>CC</sub> = Max, V <sub>in</sub> = 2.7 V) DA0 OscIn, OscOut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Чн                                | _                                    |          | 20                        | μΑ     |

| $eq:linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_linear_line$ | lι                                | -                                    |          | - 1.2<br>- 60<br>- 8<br>4 | mA     |

| Output Voltage — High Logic State<br>$(V_{CC} = Min,  _{OH} = -1.0 \text{ mA}) \overline{RAS0}, \overline{RAS1}, \overline{CAS}, \overline{WE}$<br>$(V_{CC} = Min,  _{OH} = -0.2 \text{ mA}) E, O$<br>$(V_{CC} = Min,  _{OH} = -0.2 \text{ mA}) All Other Outputs$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Voh(C)<br>Voh(E)<br>Voh           | 3.0<br>V <sub>CC</sub> - 0.75<br>2.7 |          |                           | v      |

| Output Voltage — Low Logic State<br>$(V_{CC} = Min, I_{OL} = 8.0 \text{ mA}) \overline{RAS0}, \overline{RAS1}, \overline{CAS}, \overline{WE}$<br>$(V_{CC} = Min, I_{OL} = 4.0 \text{ mA}) E, \Omega Outputs$<br>$(V_{CC} = Min, I_{OL} = 0.8 \text{ mA}) \text{ VClk Output}$<br>$(V_{CC} = Min, I_{OL} = 4.0 \text{ mA}) \text{ All Other Outputs}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VOL(C)<br>VOL(E)<br>VOL(V)<br>VOL |                                      |          | 0.5<br>0.5<br>0.6<br>0.5  | v      |

| Power Supply Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ICC                               | -                                    | 180      | 230                       | mA     |

| Output Short-Circuit Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | los                               | 30                                   | _        | 225                       | mA     |

## FAST AND LS TTL DATA

## 5-324

| Characteristic                                                                                                                         |                                                                            | Symbol                                           | Min    | Тур        | Max    | Units |

|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------|--------|------------|--------|-------|

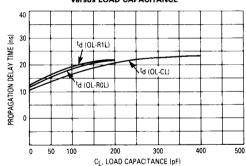

| Propagation Delay Times<br>. (See Circuit in Figure 9) Oscillator-In 🌂<br>Oscillator-In 🎜                                              | to Oscillator-Out<br>to Oscillator-Out                                     | td(OL-OH)<br>td(OH-OL)                           |        | 3.0<br>20  | _      | ns    |

| (C <sub>L</sub> = 195 pF) A0 thru A15 to Z0, Z1, Z<br>(C <sub>L</sub> = 30 pF) A0 thru A15, R/W to S0, S                               |                                                                            | <sup>t</sup> d(A-Z)<br><sup>t</sup> d(A-S)       | -      | 28<br>18   |        |       |

| (CL = 95 pF) Oscillator-Out  ⊂ to  RASO<br>(CL = 95 pF) Oscillator-Out   ⊂ to  RASO                                                    |                                                                            | td(OL-R0H)<br>td(OL-R0L)                         | _      | 20<br>18   | _<br>_ |       |

| (CL = 95 pF) Oscillator-Out  ◄_to  RAS1<br>(CL = 95 pF) Oscillator-Out  ◄_to  RAS1                                                     |                                                                            | <sup>t</sup> d(OL-R1H)<br><sup>t</sup> d(OL-R1L) |        | 22<br>20   | -      |       |

| (CL = 195 pF) Oscillator-Out $\rightarrow$ to $\overline{CAS}$<br>(CL = 195 pF) Oscillator-Out $\rightarrow$ to $\overline{CAS}$       |                                                                            | <sup>t</sup> d (OL-CH)<br><sup>t</sup> d(OL-CL)  | _      | 20<br>20   | _      |       |

| $(C_L = 195 \text{ pF}) \text{ Oscillator-Out } to \overline{WE}$<br>$(C_L = 195 \text{ pF}) \text{ Oscillator-Out } to \overline{WE}$ |                                                                            | <sup>t</sup> d(OL-WH)<br><sup>t</sup> d(OL-WL)   | _      | 22<br>40   | -      |       |

| (CL = 100 pF) Oscillator-Out  to E<br>(CL = 100 pF) Oscillator-Out  to E  to E  to E                                                   |                                                                            | <sup>t</sup> d(OL-EH)<br><sup>t</sup> d(OL-EL)   | _      | 55<br>25   |        |       |

| (CL = 100 pF) Oscillator-Out  to Q<br>(CL = 100 pF) Oscillator-Out  to Q<br>(CL = 100 pF) Oscillator-Out  to Q                         |                                                                            | td(OL-QH)<br>td(OL-QL)                           | _      | 55<br>25   |        |       |

| (CL = 30 pF) Oscillator-Out f to VClk<br>(CL = 30 pF) Oscillator-Out f to VClk                                                         |                                                                            | td(OH-VH)<br>td(OH-VL)                           | _      | 50<br>65   |        |       |

| (CL = 195 pF) Oscillator-Out  ◄ to Row<br>(CL = 195 pF) Oscillator-Out  ◄ to Coll                                                      |                                                                            | <sup>t</sup> d(OL-AR)<br><sup>t</sup> d(OL-AC)   | -      | 36<br>33   | —      |       |

| (C <sub>L</sub> = 15 pF) Oscillator-Out ◄ to DA0<br>(C <sub>L</sub> = 15 pF) Oscillator-Out ◄ to DA0                                   | JC Earliest(1)<br>JC Latest(1)                                             | td(OL-DH)<br>td(OL-DH)                           | _      | 15<br>+ 15 | _      |       |

| $(C_L = 95 \text{ pF on } \overline{RAS}, C_L = 195 \text{ pF on } \overline{CAS})$                                                    | ) CAS 🔍 to RAS 🖌                                                           | td(CL-RH)                                        | —      | 208        | —      |       |

| Setup Time for A0 thru A15, R/W                                                                                                        | $\begin{array}{rcl} Rate &=& \div \ 16 \\ Rate &=& \div \ \ 8 \end{array}$ | t <sub>su</sub> (A)                              | —<br>— | 28<br>28   | —      | ns    |

| Hold Time for A0 thru A15, R/W                                                                                                         | Rate = $\div$ 16<br>Rate = $\div$ 8                                        | <sup>t</sup> h(A)                                | _      | 30<br>30   | _      | ns    |

| Width of HS Low 2                                                                                                                      |                                                                            | twL(HS)                                          | 2.0    | 5.0        | 6.0    | μs    |

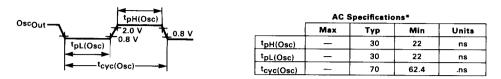

**AC CHARACTERISTICS** (4.75  $V \leq V_{CC} \leq 5.25$  V and  $0 \leq T_{\Delta} \leq 70^{\circ}$ C, unless otherwise noted).

Notes: 1. When using the SAM with an MC6847, the rising edge of DA0 is confined within the range shown in the timing diagrams (unless the synchronizing process is incomplete.) The synchronization process requires a maximum of 32 cycles of OscOut for completion.

2. tWL(HS) wider than 6.0 µs may yield more than 8 sequential refresh addresses.

#### FIGURE 1 --- PROPAGATION DELAY TIMES versus LOAD CAPACITANCE

## FAST AND LS TTL DATA

5-325

### PIN DESCRIPTION TABLE

|             |                         | Name        | No.      |                                                                                                                                                                                                                                                                                                                                  |

|-------------|-------------------------|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                         |             |          | Function                                                                                                                                                                                                                                                                                                                         |

|             | Power                   | VCC<br>Gnd  | 40<br>20 | Apply + 5 volts $\pm$ 5%. SAM draws less than 230 mA.<br>Return Ground for +5 volts.                                                                                                                                                                                                                                             |

|             |                         | A15         | 36       | Most Significant Bit.                                                                                                                                                                                                                                                                                                            |

|             |                         | A14         | 37       |                                                                                                                                                                                                                                                                                                                                  |

|             | _                       | A13         | 38       | MPU address bits A0-A15. These 16 signals come directly from the MPU and are used to                                                                                                                                                                                                                                             |

|             | 2                       | A12         | 39       | directly address up to 64K memory locations or to indirectly address up to 96K memory                                                                                                                                                                                                                                            |

|             | Ĕ                       | A11<br>A10  | 1        | locations. (See pages 17 and 18 for memory maps). Each input is approximately equivalent                                                                                                                                                                                                                                         |

|             | <u>ა</u>                | A10<br>A9   | 3        | to one low power Schottky load.                                                                                                                                                                                                                                                                                                  |

|             | 2                       | A8          | 4        |                                                                                                                                                                                                                                                                                                                                  |

|             | 8                       | A7          | 24       |                                                                                                                                                                                                                                                                                                                                  |

|             | 8                       | A6          | 23       |                                                                                                                                                                                                                                                                                                                                  |

| ŝ           | 후                       | A5          | 22       |                                                                                                                                                                                                                                                                                                                                  |

| Input Pins  | MPU Address and Control | A4          | 21       |                                                                                                                                                                                                                                                                                                                                  |

| a           | 2                       | A3          | 19       |                                                                                                                                                                                                                                                                                                                                  |

| 5           | Σ                       | A2<br>A1    | 18<br>17 |                                                                                                                                                                                                                                                                                                                                  |

|             |                         | A0          | 16       | Least Significant Bit.                                                                                                                                                                                                                                                                                                           |

|             | ł                       | R/W         |          |                                                                                                                                                                                                                                                                                                                                  |

|             |                         |             | 15       | MPU READ or WRITE. This signal comes directly from the MPU and is used to enable writing<br>to the SAM control register, dynamic RAM (via WE), and to enable device select #0.                                                                                                                                                   |

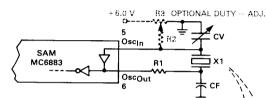

|             |                         | Oscin       | 5        | Apply 14.31818* MHz crystal and 2.5–30 pF trimmer to ground. See page 12.                                                                                                                                                                                                                                                        |

|             |                         | DA0         | 8        | Display Address DA0. The primary function of this pin is to input the least significant bit of a<br>16-bit video display address. The more significant 15-bits are outputs from an internal 15-bit<br>counter which is clocked by DA0. The secondary function of this pin is to indirectly input the                             |

| 507         | Control                 | ĦS          | 9        | logic level of the VDG "FS" (field synchronization pulse) for vertical video address updating.<br>Horizontal Synchronization. The primary function of this pin is to detect the falling edge of<br>VDG "HS" pulse in order to initiate eight dynamic RAM refresh cycles. The secondary function                                  |

|             |                         | VCIk        | 7        | is to reset up to 4 least significant bits of the internal video address counter.<br>VDG Clock. The primary function of this pin is to <b>output</b> a 3.579545 MHz square wave** to the<br>VDG "Clk" pin. The secondary function resets the SAM when this VClk pin is pulled to logic<br>"0" level, acting as an <b>input</b> . |

|             |                         | OscOut      | 6        | Apply 1.5 k $\Omega$ resistor to 14.31818* MHz crystal and 33 pF capacitor to ground. See page 12.                                                                                                                                                                                                                               |

| Javice      | Selects                 | S2<br>S1    | 25<br>26 | Most Significant Bit (Device Select Bits). The binary value of S2, S1, S0 selects one of eight<br>"chunks" of MPU address space (numbers 0 through 7). Varying in length, these "chunks"<br>provide efficient memory mapping for ROMs, RAMs, Input/Output devices, and MPU Vectors.<br>(Requires 74LS 138-type demultiplexer).   |

|             | - 0                     | S0          | 27       | Least Significant Bit.                                                                                                                                                                                                                                                                                                           |

| s III       | Clocks                  | E           | 14       | E (Enable Clock) "E" and "Q" are 90° out of phase and are both used as MPU clocks for the MC6809E. For the MC6800 and MC6801E, only "E" is used. "E" is also used for many MC6800 peripheral chips.                                                                                                                              |

| Output Pins | - 0                     | ٥           | 13       | Q (Quadrature Clock).                                                                                                                                                                                                                                                                                                            |

| ۲.          |                         | <b>Z7</b> † | 35       | Most Significant Bit                                                                                                                                                                                                                                                                                                             |

| 물           | _                       | Z6†         | 34       | First, the least significant address bits from the MPU or "VDG" are presented to Z0-Z5 (4K                                                                                                                                                                                                                                       |

| ō اج        | Address                 | Z5†         | 33       | x 1 RAMs) or Z0-Z6 (16K x 1 RAMs) or Z0-Z7 (64K x 1 RAMs). Next, the most significant                                                                                                                                                                                                                                            |

|             | ŝ                       | Z4†         | 32       | address bits from the MPU or "VDG" are presented to Z0 – Z5 (4K x 1 RAMs) or Z0 – Z6 (16K x 1 RAMs) or Z0 – Z6 (16K x 1 RAMs) or Z0 – Z7 (54K x 1 RAMs) Nets that for 4K x 1 red to K                                                                                                                                            |

| *           | - A                     | Z3†<br>Z2†  | 31<br>30 | (16K x 1 RAMs) or Z0 –Z7 (64K x 1 RAMs). Note that for 4K x 1 and 16K x 1 RAMs, Z7 (Pin<br>35) is not needed for address in <u>form</u> ation. Therefore, Pin 35 is used for a second row                                                                                                                                        |

|             |                         | Z1†         | 29       | address select which is labeled (RAS1).                                                                                                                                                                                                                                                                                          |

|             |                         | ZOT         | 28       | Least Significant Bit.                                                                                                                                                                                                                                                                                                           |

|             | _                       | RASIT       | 35       | Row Address Strobe One. This pulse strobes the least significant 6,7 or 8 address bits into<br>dynamic RAMs in Bank #1.                                                                                                                                                                                                          |

| Z           | 12 2                    | RAS0†       | 12       | Row Address Strobe Zero. This pulse strobes the least significant 6,7 or 8 address bits into                                                                                                                                                                                                                                     |

| MAM         | Control                 | CASt        | 11       | dynamic RAMs in Bank #0.<br>Column Address Strobe. This pulse strobes the most significant 6,7 or 8 address bits into<br>dynamic RAMs.                                                                                                                                                                                           |

|             |                         | WE†         | 10       | Write Enable. When low, this pulse enables the MPU to write into dynamic RAM.                                                                                                                                                                                                                                                    |

\*14.31818 MHz is 4 times 3.579545 MHz television color subcarrier. Other frequencies may be used. (See page 12.)

\*\*When VDG and SAM are not yet synchronized the "square wave" will stretch (see page 10.)

↑ Due to fast transitions, ferrite beads in series with these outputs may be necessary to avoid high frequency (≈ 60 MHz) resonances.

## FAST AND LS TTL DATA

5-326

FAST AND LS TTL DATA

5-327

Printed from www.freetradezone.com, a service of Partminer, Inc. This Material Copyrighted By Its Respective Manufacturer 5

5

## FAST AND LS TTL DATA

5-328

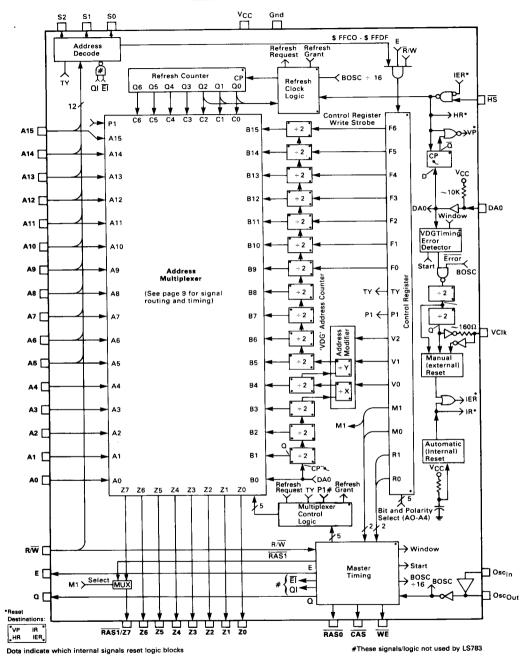

#### FIGURE 4 - SAM BLOCK DIAGRAM

FAST AND LS TTL DATA

5-329

#### SAM BLOCK DIAGRAM DESCRIPTION

#### MPU Addresses (A0-A15):

These 16 signals come directly from the MPU and are used to directly address up to 64K memory locations (K = 1024) or to indirectly address up to 96K memory locations, by using a paging bit "P" (see pages 17 and 18 for memory maps). Each input is approximately equivalent to one low power Schottky load.

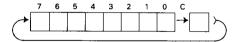

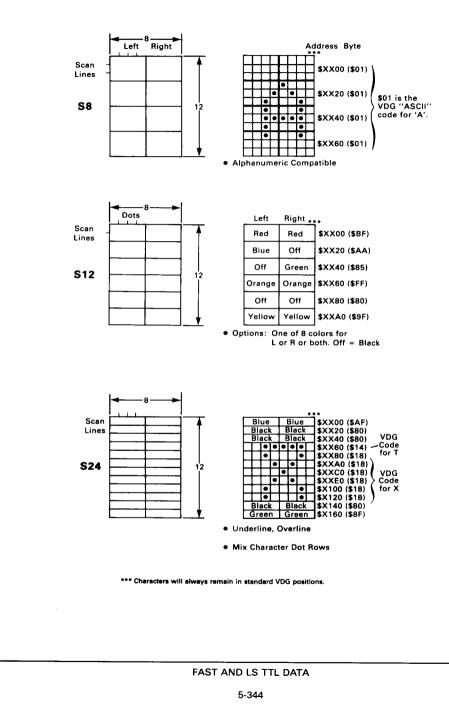

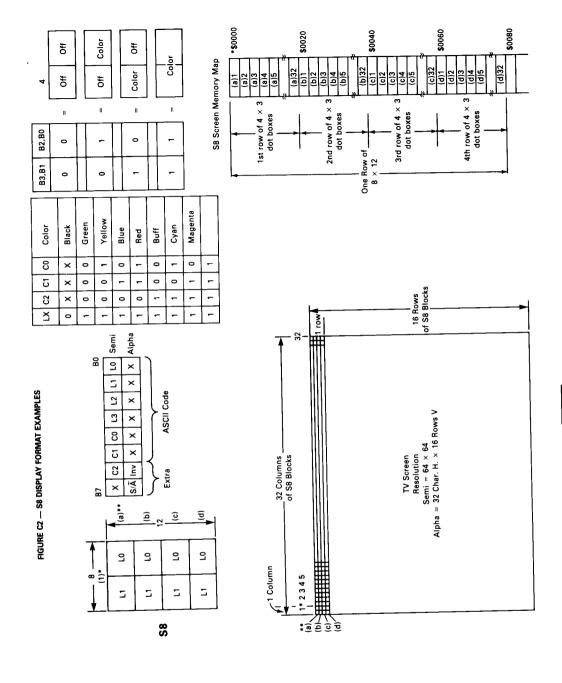

### VDG Address Counter (B0-B15):

These 16 signals are derived from one input (DA0) which is the least significant bit of the VDG address. Most of the counter is simply binary. However, to duplicate the various addressing modes of the MC6847 VDG, ADDRESS MODIFIER logic is used. Selected by three VDG mode bits (V2, V1, and V0) from the SAM CONTROL REGISTER, eight address modifications are obtained as shown in Figure 5.

Also, notice that bits B9–B15 may be loaded from bits F0–F6 from the CONTROL REGISTER. This allows the starting address of the VDG display to be offset (in 1/2K increments) from \$0000 to \$FFFFT. B9–B15 are loaded when a VERTICAL PRE-LOAD (VP) pulse is generated. VP goes active (high) when  $\overline{\rm HS}$  from the VDG rises if DA0 is high (or a high impedance). This condition should occur only while the TV electron beam is in vertical blanking and is simply implemented by connecting  $\overline{\rm FS}$  and  $\overline{\rm MS}$  together on the MC6847. The VP pulse also **clears** bits B1–B8.

Finally, a HORIZONTAL RESET (HR) pulse may also affect the counter by clearing bits B1-B3 or B1-B4 when HS from the VDG is LOW (see Figure 5). The HR pulse should occur only while the TV electron beam is in horizontal blanking. In summary, DA0 clocks the VDG ADDRESS COUNTER; HR initializes the horizontal portion and VF initializes the

#### vertical portion of the VDG ADDRESS COUNTER.

#### REFresh Address Counter (Q0-Q7):

A seven bit binary counter (the LS785 uses an 8-bit counter) supplies bursts of eight\* sequential addresses triggered by a HS high to low transition. Thus, while the TV electron beam is in horizontal blanking, eight sequential addresses are accessed. Likewise, the next eight addresses are accessed during the next horizontal blanking period, etc. In this manner, all 128 addresses are refreshed in less than 1.1 milliseconds.

#### Address Multiplexer:

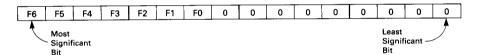

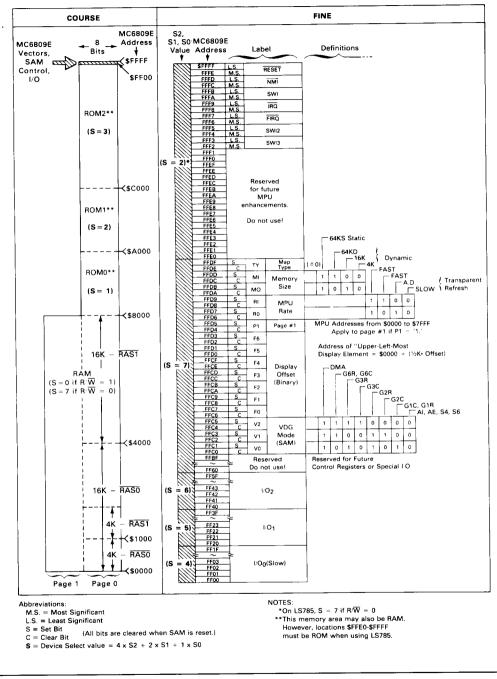

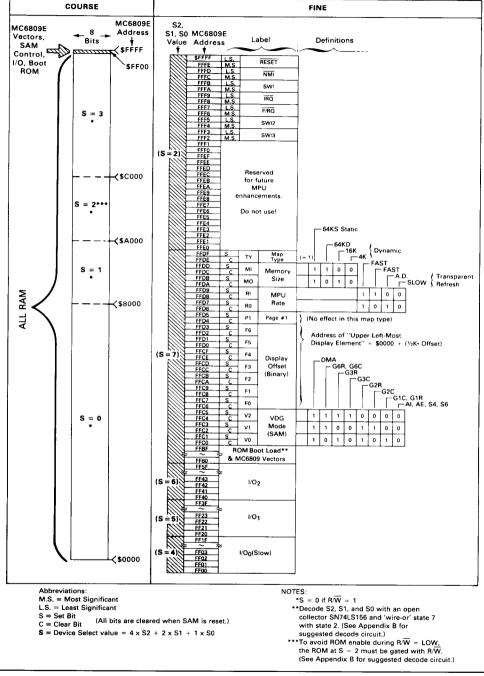

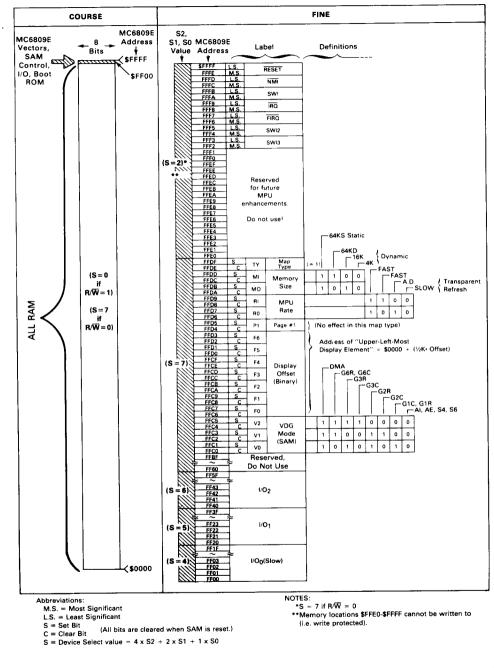

Occupying a large portion of the block diagram in Figure 4, is the address multiplexer which outputs bits Z0–Z7 (as addresses to dynamic RAM's). Inputs to the address multiplexer include the VDG address (B0–B15) the REFresh address (C0–C6) and the MPU address (A0–A15) or (A0–A14 plus one paging bit "P"). The paging bit "P" is one bit in the SAM CONTROL REGISTER that is used in place of A15 when memory map TYpe #0 is selected (via the SAM CONTROL REGISTER "TY" bit).

Figure 6 shows which inputs are routed to Z0–Z7 and when the routing occurs relative to one SAM machine cycle. Notice that Z7 and  $\overline{RAS1}$  share the same pin. Z7 is selected if "M1" in the SAM CONTROL REGISTER IS HIGH (Memory size = 64K).

#### Address Decode:

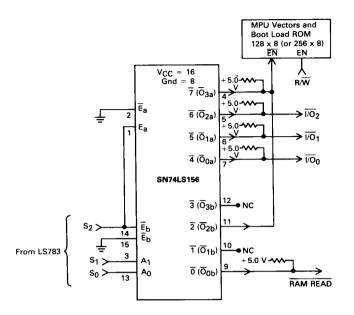

At the top left of Figure 4, is the Address Decode block. Outputs S2, S1, and S0 form a three bit encoded binary word(S). Thus S may be one of eight values (0 through 7) with each value representing a different range of MPU addresses. (To enable peripheral ROM's or I/O, decode the S2, S1, and S0 bits into eight separate signals by using a 74LS135 or 74LS156.)

On the LS783, the S2, S1 and S0 outputs are not gated with any timing signals. The LS785 forces the S outputs HIGH if accessing ROM (see Memory Map, Figures 14–16) when the E clock is LOW and the Q clock is HIGH (see Timing Diagram, Figures 2–3). This logic implementation allows the LS785 to easily interface with inexpensive "dynamic" ROMs such as MCM88364.

Along with the A5–A15 inputs is the MEMORY MAP TYpe bit (TY). This bit is soft-programmable (as are **all** 16 bits in the SAM CONTROL REGISTER), and selects one of two memory maps. Memory map #0 is intended to be used in systems that are primarily **ROM** based. Whereas, memory map #1 is intended for a primarily **RAM** based system with 64K contiguous **RAM** locations (minus 256 locations). The various meanings of S2, S1, S0 are tabulated in Figure 16 (page 19) and again on pages 17 and 18.

In addition to S2, S1, and S0 outputs is a decode of \$FFCO through \$FFDF which, when gated with E and  $\overline{R}/W$ , results in the write strobe for the SAM CONTROL REGISTER.

#### SAM Control Register

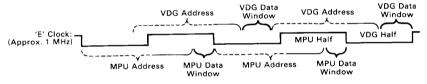

As shown in Figure 4, the CONTROL REGISTER has 16 "outputs":

| VDG Addressing Modes: | V2, V1, V0                 | MPU <u>R</u> ate:        | R1, R0 |

|-----------------------|----------------------------|--------------------------|--------|

| VDG Address OFFset:   | F6, F5, F4, F3, F2, F1, F0 | Memory Size (RAM):       | M1, M0 |

| 32K Page Switch:***   | Р                          | Memory Map <u>TY</u> pe: | ΤY     |

When the SAM is reset (see page 10), all 16 bits are cleared. To set any one of these 16 bits, the MPU simply writes to a unique\*\* odd address (within \$FFC1 through \$FFDF). To clear any one of these 16 bits, the MPU simply writes to a unique\*\* even address (within \$FFC0 through \$FFDE). Note that the data on the MPU data bus is irrevelant.

Inputs to the control register include A4, A3, A2, A1 (which are used to select **which one** of 16 bits is to be cleared or set), A0 (which determines the polarity . . . clear or set), and  $\overline{R}W$ , E and \$FFCO-\$FFDF) (which restrict the method, timing and addresses for changing one of the 16 bits). For more detailed descriptions of the purposes of the 16 control

\* If HS is held low longer than 8 μs, then the number of sequential addresses in one refresh "BURST" is proportional to the time interval during which HS is low.

\*\* See pages 17 or 18 for specific addresses.

\*\*\* The P bit is also used to select 16K x 4 bit dynamic RAM operation in the LS785. See the Page switch definition in the Programming Guide section. † In this document, the "\$" symbol always preceeds hexidecimal characters.

#### FAST AND LS TTL DATA

#### 5-330

bits, refer to related sections in the BLOCK DIAGRAM DESCRIPTION (pages 8 through 12) and the PROGRAMMING GUIDE (pages 14 through 18).

\*\* See pages 17 or 18 for specific addresses.

#### FIGURE 5 - VDG ADDRESS MODIFIER

|    | Mode |    | Division | Variables | Bits Cleared by HS (low) |

|----|------|----|----------|-----------|--------------------------|

| V2 | V1   | VO | x        | Y         |                          |

| 0  | 0    | 0  | 1        | 12        | B1-B4                    |

| 0  | 0    | 1  | 3        | 1         | B1-B3                    |

| 0  | 1    | 0  | 1        | 3         | B1-B4                    |

| 0  | 1    | 1  | 2        | 1         | B1–B3                    |

| 1  | 0    | 0  | 1        | 2         | B1-B4                    |

| 1  | 0    | 1  | 1        | 1         | B1-B3                    |

| 1  | 1    | 0  | 1        | 1         | B1-B4                    |

| 1  | 1    | 1  | 1        | 1         | None (DMA MODE)          |

## FIGURE 6 — SIGNAL ROUTING for ADDRESS MULTIPLEXER

| Memory Si      | ze | Signal | Row/Column |        |     | Signa | is Route | d to ZO- | -Z7 |     |     | Timing                |

|----------------|----|--------|------------|--------|-----|-------|----------|----------|-----|-----|-----|-----------------------|

| M1             | MO | Source |            | Z7     | Z6  | Z5    | Z4       | Z3       | Z2  | Z1  | Z0  | (Figure 2)            |

| 4K ① 0         | 0  | MPU    | ROW        | 0      | A6  | A5    | A4       | A3       | A2  | A1  | A0  | T7-TA                 |

| 4K U U         | v  |        | COL        | Ø      | LOW | A11   | A10      | A9       | A8  | A7  | A6  | TA-TF                 |

|                |    | VDG    | ROW        | 2      | B6  | B5    | 84       | B3       | B2  | B1  | BO  | TF-T2                 |

|                |    |        | COL        | Q      | LOW | B11   | B10      | B9       | 88  | B7  | B6  | T2-T7                 |

|                |    | REF    | ROW        | 2      | C6  | C5    | C4       | СЗ       | C2  | C1  | CO  | TF-T2                 |

|                |    |        | COL        | 0      | LOW | LOW   | LOW      | LOW      | LOW | LOW | LOW | T2-T7                 |

| 16K x 1 0      | 1  | MPU    | ROW        | 2      | A6  | A5    | A4       | A3       | A2  | A1  | A0  | T7-TA                 |

|                |    |        | COL        | 2      | A13 | A12   | A11      | A10      | A9  | A8  | A7  | TATF                  |

|                |    | VDG    | ROW        | ©      | B6  | 85    | B4       | B3       | B2  | B1  | BO  | TF-T2                 |

|                |    |        | COL        | 2      | B13 | B12   | B11      | B10      | B9  | B8  | B7  | T2-T7                 |

|                |    | REF    | ROW        | 2      | C6  | C5    | C4       | C3       | C2  | C1  | CO  | TF-T2                 |

|                |    |        | COL        | 2      | LOW | LOW   | LOW      | LOW      | LOW | LOW | LOW | T2-T7                 |

| 16K x 4 0      | 1  | MPU    | ROW        | A7     | A6  | A5    | A4       | A3       | A2  | A1  | A0  | T7-TA                 |

| (Page bit =    | 1) |        | COL        | 3      | A13 | A12   | A11      | A10      | A9  | A8  | A7  | TA-TF                 |

|                |    | VDG    | ROW        | B7     | B6  | 85    | B4       | B3       | B2  | B1  | BO  | TF-T2                 |

| This mode      |    |        | COL        | 3      | B13 | B12   | B11      | B10      | 89  | B8  | B7  | T2-T7                 |

| only available |    | REF    | ROW        | C7     | C6  | C5    | C4       | СЗ       | C2  | C1  | CO  | TFT2                  |

| with LS785     |    |        | COL        | LOW    | LOW | LOW   | LOW      | LOW      | LOW | LOW | LOW | T2-17                 |

| 64K (dynamic)  |    | MPU    | ROW        | A7     | A6  | A5    | A4       | A3       | A2  | A1  | A0  | <b>T7</b> –T <b>A</b> |

| 1              | 0  |        | COL        | P/A153 | A14 | A13   | A12      | A11      | A10 | A9  | A8  | TA-TF                 |

|                |    | VDG    | ROW        | B7     | B6  | B5    | B4       | B3       | B2  | B1  | BO  | TF-T2                 |

|                |    |        | COL        | B15    | B14 | B13   | B12      | B11      | B10 | B9  | B8  | T2T7                  |

|                |    | REF    | ROW        | C7@    | C6  | C5    | C4       | СЗ       | C2  | C1  | CO  | TF-72                 |

|                |    |        | COL        | LOW    | LOW | LOW   | LOW      | LOW      | LOW | LOW | LOW | T2-T2                 |

| 64K (static)   |    | MPU    | ROW        | A7     | A6  | A5    | A4       | A3       | A2  | A1  | A0  | T7-T9                 |

| 1              | 1  |        | COL        | P/A153 | A14 | A13   | A12      | A11      | A10 | A9  | A8  | T9-TF                 |

|                |    | VDG    | ROW        | B7     | B6  | B5    | B4       | B3       | B2  | B1  | B0  | TF-T1                 |

|                |    |        | COL        | B15    | B14 | B13   | B12      | B11      | B10 | B9  | B8  | т1-т7                 |

|                |    | REF    | ROW        | C7@    | C6  | C5    | C4       | C3       | C2  | C1  | C0  | TF-T1                 |

|                |    |        | COL        | LOW    | LOW | LOW   | LOW      | LOW      | LOW | LOW | LOW | T1-T7                 |

D When using 4K x 1 RAMs, two banks of eight IC's are allowed. This accounts for Addresses \$0000-1FFF. Also, this same RAM can be addressed at \$2000-\$3FFF, \$4000-\$5FFF and \$6000-\$7FFF. 27 functions as RAS1 and its level is address dependent. For example, when using two banks of 16K x 1 RAMs, RAS0 is active for addresses

\$0000 to \$3FFF and RAS1 is active for addresses \$4000 to \$7FFF.

If Map Type = 0, then page bit "P" is the output (otherwise A15). This is a "don't care" situation for 16K x 4 MOS RAM inputs. @ C7 = Low on LS783.

## FAST AND LS TTL DATA

## 5-331

### **Internal Reset**

By lowering V<sub>CC</sub> below 0.6 volts for at least one millisecond, a complete SAM reset is initiated and is completed within 500 nanoseconds after V<sub>CC</sub> rises above 4.25 volts.

NOTE: In some applications, (for example, multiple "VDG-RAM" systems controlled by a single MPU) multiple SAM ICs can be synchronized as follows:

- Drive all SAM's from one external oscillator.

- Stop external oscillator.

- Lower V<sub>CC</sub> below 0.6 volts for at least 1.0 millisecond.

- Raise V<sub>CC</sub> to 5.0 volts.

- Start external oscillator.

- Wait at least 500 nanoseconds.

Now, the "E" clocks from all SAM's should be in-phase.

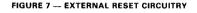

#### **External Reset**

When the VClk pin on SAM is forced below 0.8 volts for at least eight cycles of "oscillator-out", the <u>SAM</u> becomes partially reset. That is, all bits in the SAM control register are cleared. However, signals such as <u>RAS</u>, <u>CAS</u>, WE, E or Q are not stopped (as they are with an internal reset), since the SAM must maintain dynamic RAM refresh even during this external reset period.

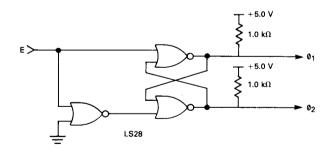

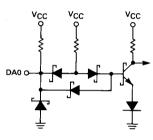

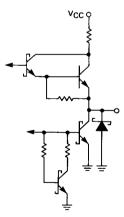

Figure 7 shows how VClk can be pulled low through diode D1 when node "A" is low.\* When node "A" is high, only the backbiased capacitance of diode D1 loads the 3.58 MHz on VClk. Diode D2 helps discharge C1 (Power-on-Reset capacitor) when power is turned off. Diode D3 allows the MPU reset time constant R2C2 to be greater than the SAM reset time constant. Thereby, ensuring **release** of the SAM reset **prior to** attempting to program the SAM control register.

#### **VDG Synchronization**

In order for the VDG and MPU to share the same dynamic RAM (see page 13,) the VDG clock must be stopped until the VDG data fetch and MPU data fetch are synchronized as shown in Figure 12. Once synchronized, the VDG clock resumes its 3.579545 MHz rate and is not stopped again unless an extreme temperature change (or SAM reset) occurs. When stopped, the VDG clock remains stopped for **no more than** 32 Osc<sub>Out</sub> cycles (approximately 2 microseconds.)

In the block diagram in Figure 4, DA0 enters a block labeled VDG Timing Error Detector. If DA0 rises **between** time reference points\*\*  $\tau_A$  and  $\tau_C$ , then Error is high and VClk is the result of dividing BOSC (Buffered Osc<sub>Out</sub>  $\approx$  14 MHz) by four. However, if DA0 rises **outside** the time Window  $\tau_A$  to  $\tau_C$ , then Error goes LOW and the VDG stops. A START pulse at time reference point  $\tau_B$  (center of Window) restarts the VDG . . . properly synchronized.

\*Use a diode with sufficiently low forward voltage drop to meet VIL requirement at VCIk.

\*\*See timing diagrams on page 5 and 6.

## FAST AND LS TTL DATA

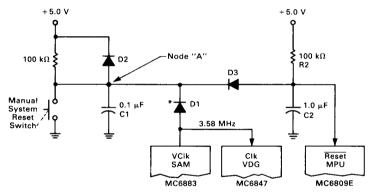

## Changing the MPU Rate (by changing SAM control register bits R0, R1).

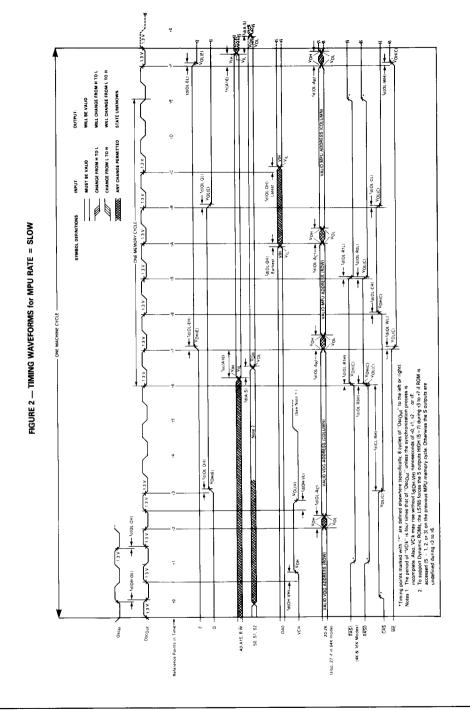

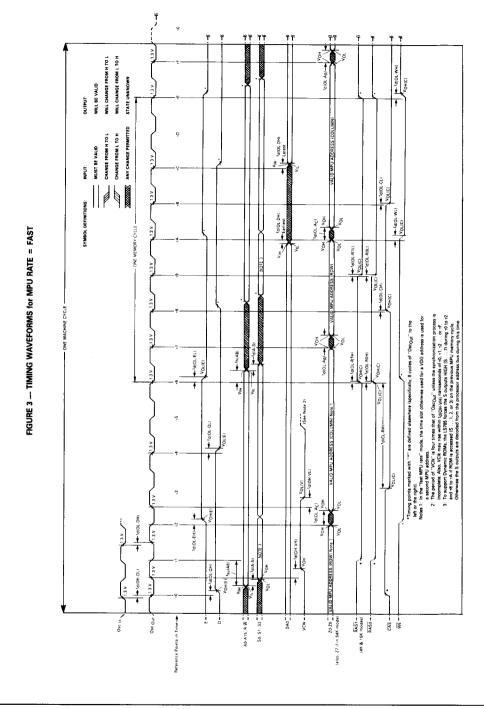

Two bits in the SAM control register determine the period of both "E" and "Q" MPU clocks. Three rate modes are implemented as follows:

| RATE MODE            | R1        | RO |                                                                                                                                                                                                                                                                                                                    |

|----------------------|-----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLOW                 | 0         | 0  | The frequency of "E" (and "Q") is f crystal $\div$ 16. This rate mode is automatically selected when the SAM is reset. Note that system timing is least critical in this "SLOW" rate mode.                                                                                                                         |

| A.D.<br>(Address Dep | 0<br>ende |    | The frequency of "E" (and "Q") is either f crystal $\div$ 16 or f crystal $\div$ 8, depending on the address the MPU is presenting.                                                                                                                                                                                |

| FAST                 | 1         | x  | The frequency of "E" (and "Q") is f crystal $\div$ 8. This is accomplished by stealing the time that is normally used for VDG/REFRESH, and using this time for the MPU. Note: Neither VDG display nor dynamic RAM refresh are available in the "FAST" rate mode. (Both are available in SLOW and A.D. rate modes). |

When changing between any two of the three rate modes, the following procedures must be followed to ensure that MPU timing specifications are met:

| RATE MODE |        |        |                                       |                         |

|-----------|--------|--------|---------------------------------------|-------------------------|

| SLOW      | Set R0 | Set R1 | · · · · · · · · · · · · · · · · · · · | This direct path is     |

| A.D.      |        |        | Sequence #1                           | not allowed except by   |

| FAST      |        |        | (See Below)                           | Set R1. hardware reset. |

|           |        |        | Set R0, then CLEAR R1                 |                         |

May be ANY address from \$0000 to \$7FFF.

SEQUENCE #1:

7D 00 00 TST #\$0000... Synchronizes STA instruction to write during T2-TG (See Figure #8).\* 21 00 BRN 00

B7 FF D6 STA #\$FFD6 ... Clears bit R0

\*Note: "TST" instruction affects MC6809E condition code register.

## Changing the MPU Rate (In Address Dependent Mode)

When the SAM control register bits "R1", and "R0" are programmed to "0" and "1", respectively, the Address Dependent Rate Mode is selected. In this mode, the  $\div$  16 MPU rate is automatically used when addressing within \$0000 to \$7FFF\* or \$FF00 to \$FF1F ranges. Otherwise the  $\div$  8 MPU rate is automatically used. (Refer to Figure 8 for sample "E" and "Q" waveforms yielding  $\div$  8 to  $\div$  16 and  $\div$  16 to  $\div$  8 rate changes). This mode often nearly doubles the MPU throughput while still providing transparent VDG and dynamic, RAM refresh functions. For example, since much of the MPU's time may be spent performing internal MPU functions (address = \$FFFF)\*, the faster f crystal  $\div$  8 MPU rate may be used much of the time.

Note: The VDG operates normally when using the SLOW or A.D. rate modes. However, in the FAST rate mode, the VDG is not allowed access to the dynamic RAM.

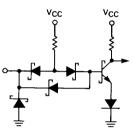

#### FIGURE 8 - RATE CHANGE E AND Q WAVEFORMS

\*When using Memory Map 0, addresses \$0000 to \$7FFF may access Dynamic RAM. \*\*The MC6809 outputs \$FFFF on A0-A15 when no other valid addresses are being presented.

## FAST AND LS TTL DATA

#### 5-333

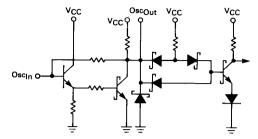

## Oscillator

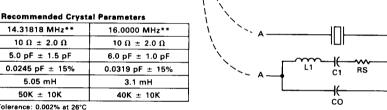

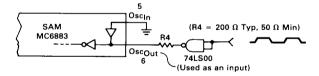

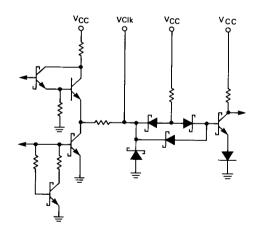

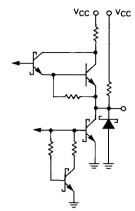

In Figure 4, an amplifier between Oscin and OscOut provides the gain for oscillation (using a crystal as shown in Figure 9.) Alternately, Pin 5 (OscIn) may be grounded while Pin 6 (OscOut) may be driven at low-power Schottky levels as shown in Figure 10. Also, see VIH, VIL on page 2.

#### FIGURE 9 - CRYSTAL OSCILLATOR

| Freq.<br>MHz | cv∗          | CF*      | R1*       | R2*    | R3* | X1 |

|--------------|--------------|----------|-----------|--------|-----|----|

| 14.31818     | 2.5–30<br>pF | 33<br>pF | 1.5<br>kΩ | ~ 100K | 10K | *  |

| 16.0000      | 2.5–30<br>pF | 33<br>pF | 1.5<br>kΩ | ~ 100К | 10K | *  |

nantad Common-A Values

R

R

Calibration Tolerance: 0.002% at 26°C Temperature Tolerance: 0.001% 0°C to 70°C

14.31818 MHz\*\*

$10 \Omega \pm 2.0 \Omega$

$5.0 \text{ pF} \pm 1.5 \text{ pF}$

0.0245 pF ± 15%

5.05 mH

50K ± 10K

RS

со

C1

L1

Q

#### FIGURE 10 - TTL CLOCK INPUT

Typical input capacitances are 3.0 pF for Pin 5 and 5.5 pF for Pin 6.

\*Optimum values depend on characteristics of the crystal (X1). For many applications, VClk must be 3.579545 MHz ± 50 Hz! Hence,

OscOut must be made similarly "drift resistant" (by balancing temperature coefficients of X1, CV, CF, R1, R2 and R3).

\*Specifically cut for the SAM are International Crystal Manufacturing, Inc. Crystals (#167568 for 14.31818 MHz or #167569 for 16.0 MHz). However, other crystals may be used.

## FAST AND LS TTL DATA

## 5-334

## THEORY OF OPERATION

### Video or No Video

Although the SAM may be used as a dynamic RAM controller **without** a video display\*, most applications are likely to include a MC6847 video display generator (VDG). Therefore, this document emphasizes use of the SAM with MC6847 systems.

#### Shared RAM (with interleaved DMA)

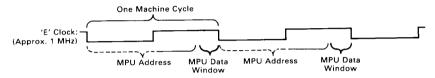

To minimize the number of RAM and interface chips, both the MPU and VDG share common dynamic RAM. Yet, the use of common RAM creates an apparent difficulty. That is, the MPU and VDG must both access the RAM without contention. This difficulty is overcome by taking advantage of the timing and architecture of Motorola MPU's (MC6800, MC6801E, MC68009E, MC68000). Specifically, **all** MPU accesses of external memory **always** occur in the **latter half** of the machine cycle, as shown below:

Similarly, the MC6847 (non-interlaced) VDG transfers a data byte in a half machine cycle (E or Φ2). Thus, when properly positioned, VDG and MPU RAM accesses interleave without contention as shown below:

This Interleaved Direct Memory Access (IDMA) is synchronized via the MC6883 by centering the VDG data window half-way between MPU data windows.\*\*

The result is a shared RAM system without MPU/VDG RAM access contention, with both MPU and VDG running uninterrupted at normal operating speed, each transparent to the other.

#### **RAM Refresh**

Dynamic RAM refresh is accomplished by accessing eight\*\*\* sequential row addresses every 64\*\*\* microseconds until all addresses have been accessed. To avoid RAM access contention between REFRESH and MPU, each of the refresh accesses occupies the "VDG half" of the interleaved DMA (IDMA). Furthermore, refresh accesses occur only during the television retrace period (at which time the VDG doesn't need to access RAM).

In summary, the VDG, MPU and SAM's Refresh Counter all transparently access the common dynamic RAM without contention or interruption.

#### Why IDMA?

Use of the interleaved direct memory access results in fast modification to variable portions of display RAM, by the MPU, without any distracting flashes on the screen (due to RAM access contention). In addition, the MPU is not slowed down nor stopped by the SAM; thereby, assuring accurate software timing loops without costly additional hardware timers. Furthermore, additional hardware and software to give "access permission" to the MPU is eliminated since the MPU may access RAM at **any** time.

FAST AND LS TTL DATA

<sup>\*</sup>Only 1 pin, (DA0) out of 40 pins is dedicated to the video display.

<sup>\*\*</sup>See VDG synchronization (page 10) for more detail.

<sup>\*\*\*</sup>When not using a MC6847, HS may be wired low for continuous transparent refresh.

#### "Systems On Silicon" Concept

#### **Total Timing**

For most applications, the SAM can supply complete system timing from its on-chip precision 14.31818 MHz oscillator. This includes buffered MPU clocks (E and Q), VDG clock, color subcarrier (3.58 MHz), row address select (RAS), column address select (CAS) and write enable (WE).

#### **Total Address Decode**

For most applications, the SAM plus a "1 of 8 decoder" chip completely decodes I/O, ROM and RAM chip selects without wasting memory address space and without needlessly chopping-up contiguous address space. Chip selects are positioned in address space to allow three types of memory (RAM, local ROM and cartridge ROM) independent room for growth. For example, RAM may grow from address \$0000-up, cartridge ROM may grow from address \$FEFF-down and local ROM may grow from \$FFF-down. Alternately, if the application requires minimum ROM and maximum contiguous RAM, a second choice of two memory maps places RAM from \$0000 to \$FEFF. (See Figures 14–16.)

In both memory maps all I/O, MPU vectors, SAM control registers, and some reserved address spaces are efficiently contained between addresses \$FF00 and \$FFFF.

#### **How Much RAM?**

Using nine SAM pins (Z0-Z7 and RAS0) the following combinations require no additional address logic.

#### FIGURE 13 - RAM CONFIGURATIONS

|     | Address: |

|-----|----------|

| MSB |          |

I SB

Chip Select:

| One or two banks | of 4K x 8 (like | MCM4027's) |

|------------------|-----------------|------------|

|------------------|-----------------|------------|

One or two banks of 16K x 8 (like MCM4116's)