# D 1M x 36 Pipelined NoBL™ SRAM Module

#### **Features**

- Operates at 133 MHz

- Uses 512K x 18 high-performance Pipelined NoBL<sup>™</sup> synchronous SRAMs

- 2.5V data inputs/outputs

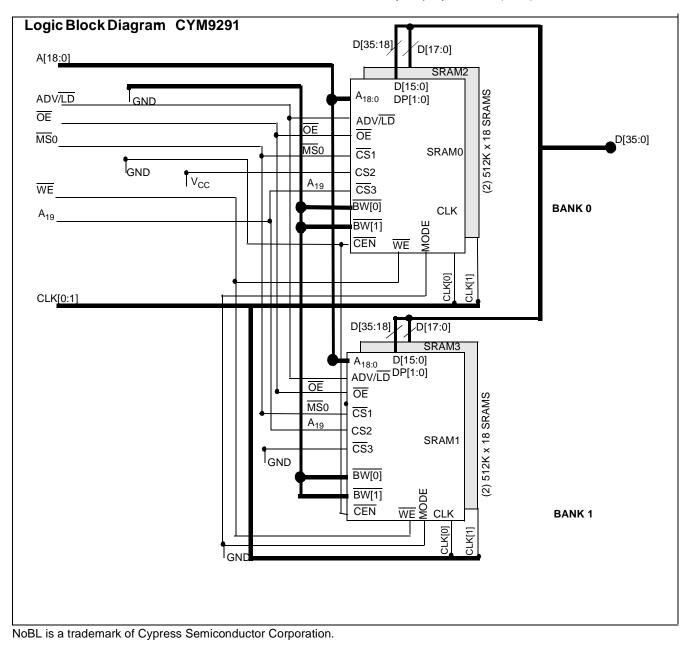

#### **Functional Description**

The CYM9291 is a high-performance synchronous pipelined NoBL memory module organized as 1M by 36 bits. These modules are constructed from 512K x 18 NoBL SRAMs in plastic surface mount packages on an epoxy laminate board with pins. The modules are designed to be incorporated into large memory arrays.

The module is configured as two banks, where each bank has separate chip select controls. Separate clocks are provided for every pair of SRAMs.

Multiple ground pins and on-board decoupling capacitors ensure high performance with maximum noise immunity.

All components on the modules are surface mounted on a multi-layer epoxy laminate (FR-4) substrate.

1

# **Selection Guide**

| NoBL | Pipelined | Module |

|------|-----------|--------|

|      |           | modulo |

| Part Number Cache Size |         | SRAM's Used          | System Clock (MHz) | Data t <sub>CDV</sub> |  |  |

|------------------------|---------|----------------------|--------------------|-----------------------|--|--|

| CYM9291PZ-133          | 1M x 36 | 4 of 512K x 18(TQFP) | 133                | 4.4 ns                |  |  |

| CYM9291PZ-117          | 1M x 36 | 4 of 512K x 18(TQFP) | 117                | 4.8ns                 |  |  |

# Pin Configuration

| Dual Read-Out<br>Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | t ZIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{c} \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{A}_{0} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{A}_{0} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{A}_{0} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{GND} & \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{I} & \textbf{I} & \textbf{I} \\ \textbf{I} \\ \textbf{SOO} & \textbf{O} & \textbf{I} & \textbf{I} \\ \textbf{I} & \textbf{I} \\ \textbf{I} \\ \textbf{SOO} & \textbf{I} & \textbf{I} \\ \textbf{I} \\ \textbf{I} \\ \textbf{SOO} & \textbf{I} \\ \textbf{I} \\ \textbf{I} \\ \textbf{I} \\ \textbf{SOO} & \textbf{I} \\ \textbf{I} $ | $ \begin{array}{c} A_{5} \\ A_{7} \\ GND \\ A_{6} \\ H \\ A_{11} \\ GND \\ A_{11} \\ Vcc2 \\ A_{13} \\ GND \\ A_{15} \\ A_{17} \\ GND \\ A_{15} \\ A_{17} \\ GND \\ H \\ A_{19} \\ H \\ WE \\ GND \\ H \\ A_{19} \\ H \\ WE \\ GND \\ H \\ B \\ GND \\ D_{1} \\ GND \\ D_{2} \\ GND \\ H \\ B \\ GND \\ H \\ $ |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $ \begin{array}{c} \square D_{23} \\ \square GND \\ \square D_{25} \\ \square V_{CC2} \\ \square D_{27} \\ \square GND \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## **Pin Definitions**

| Signal                           | Description                        |

|----------------------------------|------------------------------------|

| V <sub>CC2</sub>                 | 2.5V Supply                        |

| GND                              | Ground                             |

| A[19:0]                          | Addresses from processor           |

| ŌĒ                               | Output Enable                      |

| WE                               | Write Enable                       |

| MS[0]                            | Chip Select for the module         |

| PD <sub>0</sub> -PD <sub>1</sub> | Presence Detect output pins        |

| D[35:0]                          | Data lines from processor          |

| CLK[0:1]                         | Clock lines to the module          |

| ADV/LD                           | Advance Load Signal from processor |

| NC                               | Signal not connected on module     |

| NC(Pin 113)                      | Reserved for Depth expansion       |

| RSVD                             | Reserved                           |

# **Presence Detect Pins**

|                     | PD <sub>1</sub> | PD <sub>0</sub> |

|---------------------|-----------------|-----------------|

| CYM9291PZ - 1M x 36 | GND             | GND             |

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guide-lines, not tested.)

| Storage Temperature                              | –55°C to +125°C |

|--------------------------------------------------|-----------------|

| Ambient Temperature with Power Applied           | 0°C to +70°C    |

| Supply Voltage to Ground Potential               | 0.3V to +3.6V   |

| DC Voltage Applied to Outputs<br>in High Z State | –0.3V to +3.6V  |

#### Electrical Characteristics Over the Operating Range

DC Input Voltage ..... -0.5V to +3.6V

Output Current into Outputs (LOW) ...... 20 mA

#### **Operating Range**

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | $2.5V \pm 5\%$  |

| Parameter              | Description                              | Test Condition                                          | Min. | Max.                  | Unit |

|------------------------|------------------------------------------|---------------------------------------------------------|------|-----------------------|------|

| V <sub>IH</sub>        | Input HIGH Voltage                       |                                                         | 1.7  | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>        | Input LOW Voltage                        |                                                         | -0.3 | 0.7                   | V    |

| V <sub>OH</sub>        | Output HIGH Voltage                      | $V_{CC} = Min. I_{OH} = -1 mA$                          | 2.0  |                       | V    |

| V <sub>OL</sub>        | Output LOW Voltage                       | $V_{CC} = Min. I_{OL} = 1 mA$                           |      | 0.2                   | V    |

| I <sub>CC (9291)</sub> | V <sub>CC</sub> Operating Supply Current | $V_{CC} = Max., I_{OUT} = 0 mA, f = f_{MAX} = 1/t_{RC}$ |      | 1680                  | mA   |

#### Capacitance<sup>[1]</sup>

| Parameter        | Description               | Test Conditions                                                     | Max. | Unit |

|------------------|---------------------------|---------------------------------------------------------------------|------|------|

| C <sub>A</sub>   | Address Input Capacitance | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$<br>$V_{CC} = 2.5 \text{ V}$ | 24   | pF   |

| CI               | Control Input Capacitance | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$<br>$V_{CC} = 2.5 \text{ V}$ | 24   | pF   |

| C <sub>O</sub>   | Input/Output Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz}, V_{CC} = 2.5 \text{ V}$      | 16   | pF   |

| C <sub>CLK</sub> | Clock Capacitance         | $T_A = 25^{\circ}C, f = 1 \text{ MHz}, V_{CC} = 2.5 \text{ V}$      | 6    | pF   |

Note:

1. Tested initially and after any design or process changes that may affect these parameters.

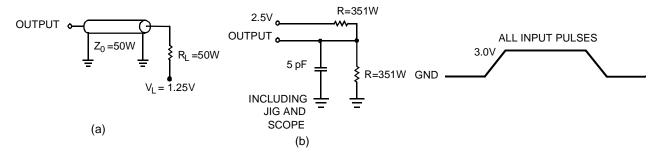

# AC Test Loads and Waveforms

## Switching Characteristics Over the Operating Range<sup>[2]</sup>

|                   |                                               | 1        | 33   | 1'   | 17   |      |

|-------------------|-----------------------------------------------|----------|------|------|------|------|

| Parameter         | Description                                   | Min.     | Max. | Min. | Max. | Unit |

| Clock             |                                               |          | 1    |      |      |      |

| t <sub>CYC</sub>  | Clock Cycle Time                              | 7.5      |      | 8.6  |      | ns   |

| F <sub>MAX</sub>  | Maximum Operating Frequency                   |          | 133  |      | 117  | MHz  |

| t <sub>CH</sub>   | Clock HIGH                                    | 2.5      |      | 3    |      | ns   |

| t <sub>CL</sub>   | Clock LOW                                     | 2.5      |      | 3    |      | ns   |

| Output Times      | · · · · · · · · · · · · · · · · · · ·         |          | 1    |      |      |      |

| t <sub>CDV</sub>  | Data Output Valid After CLK Rise              |          | 4.4  |      | 4.8  | ns   |

| t <sub>EOV</sub>  | OE LOW to Output Valid <sup>[3, 5]</sup>      |          | 4.4  |      | 4.8  | ns   |

| t <sub>DOH</sub>  | Data Output Hold After CLK Rise               | 2.3      |      | 2.3  |      | ns   |

| t <sub>CHZ</sub>  | Clock to High-Z <sup>[3, 4, 5]</sup>          |          | 3. 8 |      | 3.8  | ns   |

| t <sub>CLZ</sub>  | Clock to Low-Z <sup>[3, 4, 5]</sup>           | 2.3      |      | 2.3  |      | ns   |

| t <sub>EOHZ</sub> | OE HIGH to Output High-Z <sup>[3, 4, 5]</sup> |          | 3.8  |      | 3.8  | ns   |

| t <sub>EOLZ</sub> | OE LOW to Output Low-Z <sup>[3, 4, 5]</sup>   | 0        |      | 0    |      | ns   |

| Set-up Times      | -                                             | <b>I</b> | 1    |      |      |      |

| t <sub>AS</sub>   | Address Set-Up Before CLK Rise                | 1.5      |      | 1.5  |      | ns   |

| t <sub>DS</sub>   | Data Input Set-Up Before CLK Rise             | 1.5      |      | 1.5  |      | ns   |

| t <sub>WES</sub>  | WE Set-Up Before CLK Rise                     | 1.5      |      | 1.5  |      | ns   |

| t <sub>ALS</sub>  | ADV/LD Set-Up Before CLK Rise                 | 1.5      |      | 1.5  |      | ns   |

| t <sub>CES</sub>  | Chip Selects Set-Up                           | 1.5      |      | 1.5  |      | ns   |

| Hold Times        | ·                                             |          |      |      |      | •    |

| t <sub>AH</sub>   | Address Hold After CLK Rise                   | 0.5      |      | 0.5  |      | ns   |

| t <sub>DH</sub>   | Data Input Hold After CLK Rise                | 0.5      |      | 0.5  |      | ns   |

| t <sub>WEH</sub>  | WE Hold After CLK Rise                        | 0.5      |      | 0.5  |      | ns   |

| t <sub>ALH</sub>  | ADV/LD Hold after CLK Rise                    | 0.5      |      | 0.5  |      | ns   |

| t <sub>CEH</sub>  | Chip Selects Hold After CLK Rise              | 0.5      |      | 0.5  |      | ns   |

Notes:

2. A/C test conditions assume signal transition time of 2 ns or less, timing reference levels, input pulse levels and output loading shown in AC Test Load for 2.5V

t<sub>CHZ</sub>, t<sub>CLZ</sub>, t<sub>CLZ</sub>, t<sub>CLZ</sub>, and t<sub>EOHZ</sub> are specified with AC test conditions shown in part (a) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage. 3.

At any given voltage and temperature, t<sub>EOHZ</sub> is less than t<sub>EOLZ</sub> and t<sub>CHZ</sub> is less than t<sub>CLZ</sub> to eliminate bus contention between SRAMs when sharing the same data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed to achieve High-Z prior to Low-Z under the same system conditions. This parameter is sampled and not 100% tested. 4.

5.

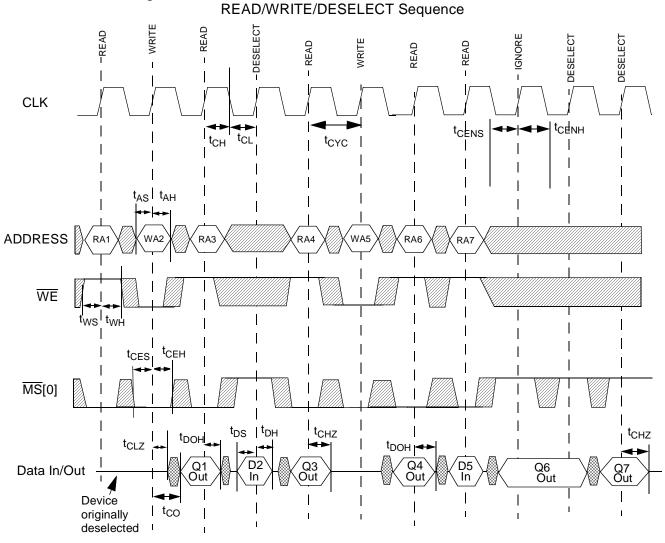

Switching Waveforms

All chip enables need to be active in order to select the device. Any chip enable can deselect the device. RAx stands for Read Address X, WAx stands for Write Address X, Dx stands for Data-in for location X, Qx stands for Data-out for location X. ADV/LD held LOW. OE held LOW.

= DON'T CARE = UNDEFINED

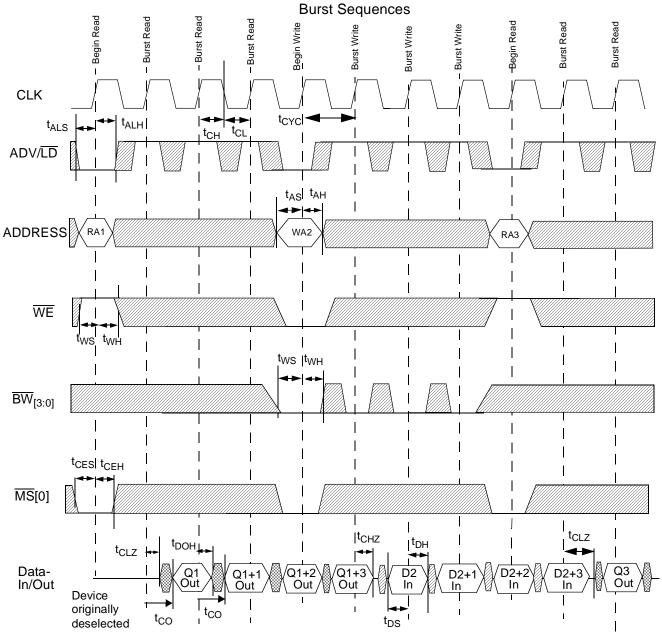

#### Switching Waveforms (continued)

**Burst Timing**

All chip enables need to be active in order to select the device. Any chip enable can deselect the device. RAx stands for Read Address X, WA stands for Write Address X, Dx stands for Data-in for location X, Qx stands for Data-out for location X. CEN held LOW. During burst writes, byte writes can be conducted by asserting the appropriate  $\overline{BW}_{[3:0]}$  input signals. Burst order determined by the state of the Mode input.  $\overline{OE}$  held LOW.

= DON'T CARE 🔤 = UNDEFINED

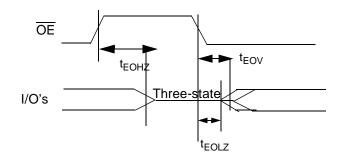

# Switching Waveforms (continued)

# OE Timing

# **Ordering Information**

| Speed (MHz) | Ordering Code  | Package Name | Package Type | Description            | Operating Range |

|-------------|----------------|--------------|--------------|------------------------|-----------------|

| 133         | CYM9291PZ-133C | PZxx         | 120-Pin ZIP  | Pipelined NoBL 1M x 36 | Commercial      |

| 117         | CYM9291PZ-117C | PZxx         | 120-Pin ZIP  | Pipelined NoBL 1M x 36 |                 |

Document #: 38-01012-\*\*

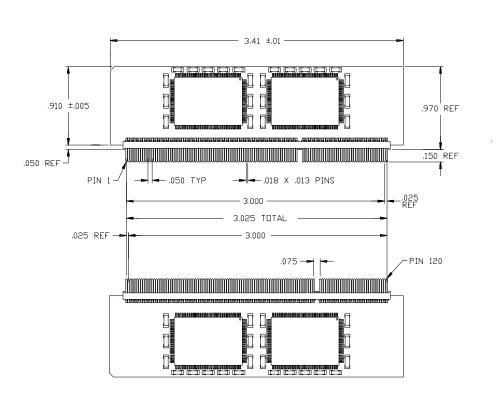

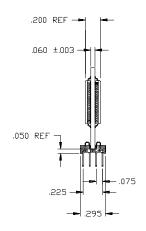

## Package Diagrams

PZ13: 120 Pin Dual Sided ZIP Module

© Cypress Semiconductor Corporation, 2000. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges.