# 37kHz SAMPLING, 12-BIT A/D CONVERTER

### **FEATURES**

- Complete 12-bit A/D converter with reference, clock and three state outputs

- Internal sample-and-hold amplifier

- Internal hold capacitor

- Pin compatible with industry standard 574

- 37kHz throughout

- Low power: 390mW

# **DESCRIPTION**

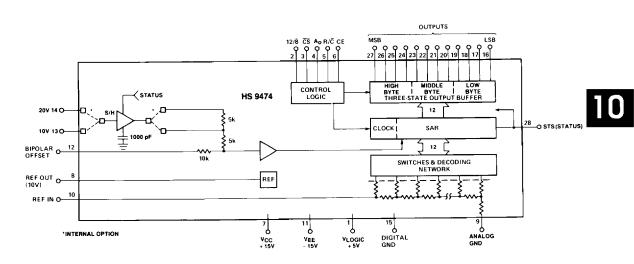

The HS9474 is a complete HS574 A/D converter with internal sample-hold amplifier. Requiring no external sample-hold connections, the HS9474 is pin for pin compatible with the industry standard 574. It is specifically designed for systems applications where the sample-hold is an integral part of the conversion process. Incorporation of the sample-hold into the same circuit with the A/D converter reduces real estate, parts count, design time, and component interaction errors.

The sample-hold has a  $7\mu$ sec acquisition time to 0.01% for a full 10V input change. A 1000 pF hold

capacitor is included in the circuit. Input voltage ranges available are  $\pm 5V$  or 0 to  $\pm 40V$  for the -1 model and  $\pm 10V$  for the -2 model.

The HS9474 is offered in a hermetically-sealed ceramic package for use over a wide temperature range and for MIL-STD-883 Rev. C requirements.

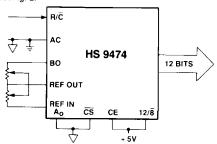

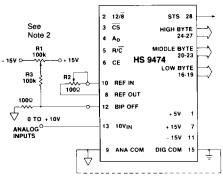

# **FUNCTIONAL DIAGRAM**

# **SPECIFICATIONS**

(Typical @ +25°C with  $V_{CC}$  = +15V,  $V_{EE}$  = -15V,  $V_{LOGIC}$  = +5V unless otherwise specified)

| MODEL HS 9474J                                                   |                                                                       | HS 9474K      | HS 9474S                                         | HS 9474T |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------|---------------|--------------------------------------------------|----------|--|

| ESOLUTION (max) 12 Bits                                          |                                                                       | *             | *                                                | *        |  |

| TYPE                                                             | Successive Approximation                                              | *             |                                                  | •        |  |

| ANALOG INPUTS                                                    |                                                                       |               |                                                  |          |  |

| Input Ranges                                                     |                                                                       |               |                                                  |          |  |

| -1***<br>-2                                                      | ±5V, 0 to +10V<br>±10V                                                | :             | •                                                | •        |  |

| Input Impedance                                                  | ± 10V<br>10¹º Q                                                       | -             | ,                                                | -        |  |

| DIGITAL INPUTS                                                   |                                                                       |               |                                                  |          |  |

| Logic Inputs                                                     |                                                                       |               |                                                  |          |  |

| CE, CS, R/C, A <sub>o</sub> , 12/8                               |                                                                       |               |                                                  |          |  |

| Logic 1                                                          | +2.4V min, +5.5V max                                                  |               |                                                  | *        |  |

| Logic 0                                                          | -0.5V min, +0.8V max                                                  | •             |                                                  | *        |  |

| Current<br>Capacitance                                           | ±5 µ A max                                                            | :             | •                                                | •        |  |

| Minimum Start Pulse                                              | 5pF                                                                   | -             | ·                                                | •        |  |

| CE-Positive                                                      | 50nsec                                                                | •             | •                                                | •        |  |

| CS-Negative                                                      | 50nsec                                                                |               |                                                  | •        |  |

| R/C-Negative  DIGITAL OUTPUTS                                    | 50nsec                                                                | •             |                                                  | *        |  |

|                                                                  |                                                                       | <del></del> - | · · · · · · · · · · · · · · · · · · ·            |          |  |

| Logic Outputs<br>DB <sub>11</sub> -DB <sub>0</sub> , STS         |                                                                       |               |                                                  |          |  |

| Logic 0                                                          | + 0.4V max, I <sub>SINK</sub> ≤1.6mA                                  |               | •                                                |          |  |

| Logic 1                                                          | + 2.4V min, I <sub>SOURCE</sub> ≤500 µA                               |               | *                                                | •        |  |

| Leakage (High Z State)                                           | ±5 μA max (Data Bits Only)                                            | •             | *                                                | *        |  |

| Capacitance<br>Parallel Data                                     | 5pF                                                                   | •             | •                                                | •        |  |

| Output Codes                                                     |                                                                       |               |                                                  |          |  |

| Unipolar                                                         | Positive True Binary                                                  | *             | *                                                | •        |  |

| Bipolar<br>REFERENCE                                             | Positive True Offset Binary                                           | •             | •                                                | •        |  |

|                                                                  |                                                                       |               |                                                  |          |  |

| Internal Output Current                                          | 10.00 ±0.1 Volts max<br>1.5mA****                                     |               | *                                                | :        |  |

| CONVERSION TIME                                                  | 18 µ sec (25 µ sec max)                                               |               | •                                                |          |  |

| ACQUISITION TIME                                                 | 7 μ sec (10 μ sec max)                                                | •             |                                                  | *        |  |

| ACCURACY                                                         | 7 μ sec (10 μ sec max)                                                |               |                                                  |          |  |

|                                                                  | <del></del>                                                           |               | 1                                                |          |  |

| Linearity (% of F.S.R. max) Monotonicity (Bits) <sup>2</sup>     | ± 0.025                                                               | ±0.012        | ± 0.025                                          | ± 0.012  |  |

| No Missing Codes                                                 | 11                                                                    | 12            | 11                                               | 12       |  |

| Offset <sup>3</sup>                                              |                                                                       | ,-            |                                                  |          |  |

| Unipolar (% of F.S.R. max)                                       | ±0.05                                                                 | •             |                                                  | •        |  |

| Bipolar (% of F.S.R. max) Gain <sup>3, 4</sup> (% fo F.S.R. max) | ± 0.25<br>± 0.3                                                       | ± 0.1         | ± 0.25                                           | ± 0.1    |  |

| STABILITY                                                        | 10.0                                                                  |               |                                                  |          |  |

|                                                                  |                                                                       |               | <del>                                     </del> |          |  |

| Linearity (ppm/°C max)<br>0°C to +70°C                           | ± 0.5                                                                 | •             | ± 0.5                                            |          |  |

| ~55°C to +125°C                                                  | 10.0                                                                  |               | ± 0.5                                            | **       |  |

| Unipolar Offset (ppm/°C max)<br>0°C to +70°C                     | 40                                                                    | . •           |                                                  |          |  |

| -55°C to +125°C                                                  | ± 10                                                                  | ± 5           | ± 10                                             | ± 5      |  |

| Bipolar Offset (ppm/°C max)                                      |                                                                       |               | 110                                              | Ξ3       |  |

| 0°C to +70°C                                                     | ±15                                                                   | ± 10          |                                                  |          |  |

| ~55°C to +125°C<br>Gain (Scale Factor)(ppm/°C max)               |                                                                       |               | ± 15                                             | ± 10     |  |

| 0°C to +70°C                                                     | ± 50                                                                  | ± 27          |                                                  |          |  |

| -55°C to +125°C                                                  | 2                                                                     | ±=-           | ±50                                              | ± 25     |  |

| POWER SUPPLY                                                     |                                                                       |               |                                                  |          |  |

| VLOGIC                                                           | +4.5 to +5.5 Volts @ 3mA max                                          | •             |                                                  | •        |  |

| VCC                                                              | + 13.5 to + 16.5 Volts @ 12.5mA typ, 17mA max                         | *             | •                                                | •        |  |

| V <sub>EE</sub><br>Power Dissipation                             | <ul> <li>13.5 to - 16.5 Volts @ 8mA max</li> <li>390mW max</li> </ul> | •             | •                                                | :        |  |

| Rejection <sup>5</sup>                                           | SSOMITY INDA                                                          |               |                                                  |          |  |

| V <sub>LOGIC</sub>                                               | ± 0.002%/%                                                            | •             | •                                                | •        |  |

| V <sub>CC</sub> . V <sub>EE</sub>                                | ± 0.005%/%                                                            | *             | •                                                | •        |  |

| FEMPERATURE RANGE                                                |                                                                       |               | <del></del>                                      |          |  |

| Operating<br>Storage                                             | 0°C to +70°C                                                          | •             | -55°C to +125°C                                  |          |  |

| Storage                                                          | -25°C to +85°C                                                        | •             | -65°C to +150°C                                  |          |  |

### NOTES:

<sup>1.</sup> Conversion time shown for a complete 12 bit conversion. 2. T<sub>min</sub> to T<sub>max</sub>. 3. Externally adjustable to zero. See application information. 4. Connect 509 between REF OUT and REF IN initial gain and offset adjustable to zero. 5. Maximum change over rated supply range.

<sup>\*</sup>Specifications same as HS 9474J. \*\*\*Specifications same as HS 9474S.

<sup>&</sup>quot;"Input range selected at factory ""Recommend buffer for external use.

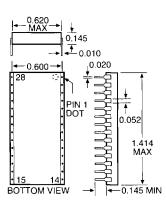

### PIN ASSIGNMENTS

|     |                        |     | 1                      |

|-----|------------------------|-----|------------------------|

| PIN | FUNCTION               | PIN | FUNCTION               |

| 1   | V <sub>LOGIC</sub>     | 28  | STS                    |

| 2   | 12/8                   | 27  | DB <sub>11</sub> (MSB) |

| 3   | CS                     | 26  | DB <sub>10</sub>       |

| 4   | A <sub>o</sub>         | 25  | DB <sub>9</sub>        |

| 5   | R/C                    | 24  | DB <sub>8</sub>        |

| 6   | CE                     | 23  | DB <sub>7</sub>        |

| 7   | V <sub>CC</sub>        | 22  | DB <sub>6</sub>        |

| 8   | REF OUT                | 21  | DB <sub>5</sub>        |

| 9   | ANA GND(AC)            | 20  | DB <sub>4</sub>        |

| 10  | REF IN                 | 19  | DB <sub>3</sub>        |

| 11  | V <sub>EE</sub>        | 18  | DB <sub>2</sub>        |

| 12  | BIP OFF                | 17  | DB <sub>1</sub>        |

| 13* | 10V <sub>IN</sub> (-1) | 16  | DB <sub>0</sub> (LSB)  |

| 14* | 20V <sub>IN</sub> (-2) | 15  | DIGITAL GND            |

<sup>\*</sup>Input not selected at factory will not be connected.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to Digital Common                                     | 0 to + 16.5V                                            |

|-----------------------------------------------------------------------|---------------------------------------------------------|

| V <sub>EE</sub> to Digital Common                                     |                                                         |

| V <sub>LOGIC</sub> to Digital Common                                  |                                                         |

| Analog Common to Digital Common                                       | ± 1V                                                    |

| Control Inputs (CE, CS, A <sub>o</sub> , 12/8, R/C) to Digital Common | 0.5V to V <sub>LOGIC</sub> + 0.5V                       |

| Analog Inputs (REF IN, BIP OFF, V <sub>IN</sub> ) to<br>Analog Common | <u>±</u> 16.5V                                          |

| REF OUT Indef                                                         | inite short to common omentary short to V <sub>CC</sub> |

| Power Dissipation                                                     | 1000mW                                                  |

| Lead Temperature, Soldering                                           | 300°C, 10sec                                            |

# **CONTROL FUNCTIONS**

The HS 9474 contains all control functions necessary to provide for complete microprocessor interface and also 'stand alone' operation including continuous conversions. All control functions are defined in Table 1 and Table 2.

| Function         | Definition    | Function                                                                                                                                                                                                                                                 |

|------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE               | Chip Enable   | <ol> <li>Typically used as clock<br/>synchronization with μP.</li> <li>Must be high (1) for a conversion<br/>to start.</li> <li>Must be high (1) to read data on<br/>the output.</li> <li>Irransition may be used to<br/>initiate conversion.</li> </ol> |

| <u>CS</u>        | Chip Select   | 1. Typically the address pin when used with μP. 2. Must be low (0) for a conversion to start or read data at the output. 3. Liransition may be used to initiate conversion.                                                                              |

| R/C              | Read/Convert  | Initiate conversion     Initiate read                                                                                                                                                                                                                    |

| A <sub>o</sub>   | Address       | 1. Selects conversion mode. 12 Bits if low (0), 8 Bits if high (1) 2. In read mode A <sub>0</sub> selects the output format. If low (0) then 8 MSB's (high and middle byte) or if high (1) then only low byte and trailing zeros.                        |

| 12/ <del>8</del> | Output Format | Must be hard wired.     Normal 12 Bit format if high (1).     8-Bit format as set by A <sub>0</sub> if low (0).                                                                                                                                          |

Table 1. Defining the Control Functions

|    | (00 | NTROL IN | HS 9474 OPERATION |    |                                         |

|----|-----|----------|-------------------|----|-----------------------------------------|

| CE | ČŠ  | R/Ĉ      | 12/8              | Ao |                                         |

| 0  | Х   | Х        | Х                 | Х  | No Operation                            |

| ×  | 1   | X        | х                 | Х  | No Operation                            |

| 1  | 0   | 7        | Х                 | 0  | Initiates 12-Bit Conversion             |

| 1  | 0   | الما     | X                 | 1  | Initiates 8-Bit Conversion              |

|    | 0   | 0        | х                 | 0  | Initiates 12-Bit Conversion             |

| 7  | 0   | 0        | Х                 | 1  | Initiates 8-Bit Conversion              |

| 1  | ٦   | 0        | X                 | 0  | Initiates 12-Bit Conversion             |

| 1  | 7   | 0        | X                 | 1  | Initiates 8-Bit Conversion              |

| 1  | 0   | F        | Pin 1             | Х  | Enables 12-Bit Parallel<br>Output       |

| 1  | 0   |          | Pin 15            | 0  | Enables 8 MSB's                         |

| 1  | 0   |          | Pin 15            | 1  | Enables 4 LSB's and<br>4 Trailing Zeros |

NOTES: 1. 1 indicates logic HIGH.

2. 0 indicates logic LOW.

3. X indicates don't care.

4. \_\_\_\_\_ indicates operation

- indicates operation commences on low to high transition.

5. MSB → XXXX XXXX ← LSB xxxxHigh Middle Byte Byte

<sup>6.</sup> Not a common use of this function.7. When using the HS 9474 in the 8-bit bus mode with 12-bit resolution, the high byte must be externally hard wired to the low byte.

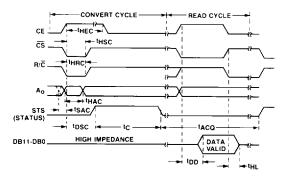

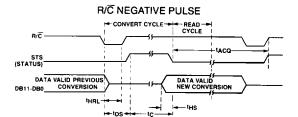

#### TIMING

The timing diagrams are shown in Fig. 1. Note that to start a conversion CS, CE, and R/C must have an overlap time of 50ns minimum. CS and R/C may be advanced or delayed if needed (by the application) but no specifications are given for this — only the coincidence of 50ns must be met. Typically R/C is used to initiate a conversion — however other lines may be used. See truth table (Table 2).

In the READ mode note the access time  $t_{DD}$  is 75ns typ, 150ns max. This means that an entire conversion can be completed and read in 20  $\mu$ s typ, 25  $\mu$ s max including setup, conversion time and access time.

### CONVERT CYCLE

| PARAMETER                              |                                                                                                                                                                                                                                                         |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acquisition Time                       | 7 μs typ, 10 min                                                                                                                                                                                                                                        |

| CE Pulse Width                         | 50ns min                                                                                                                                                                                                                                                |

| CS LOW during<br>CE high               | 50ns min                                                                                                                                                                                                                                                |

| R/C LOW during<br>CE high              | 50ns min                                                                                                                                                                                                                                                |

| A <sub>o</sub> valid during<br>CE high | 50ns min                                                                                                                                                                                                                                                |

| Maximum A <sub>o</sub>                 | Ons max                                                                                                                                                                                                                                                 |

|                                        |                                                                                                                                                                                                                                                         |

|                                        |                                                                                                                                                                                                                                                         |

| CE) not needed                         |                                                                                                                                                                                                                                                         |

| STS delay from CE                      | 200ns max                                                                                                                                                                                                                                               |

| 8 Bit cycle<br>12 Bit cycle            | 13 µs typ, 19 µs max<br>20 µs typ, 25 µs max                                                                                                                                                                                                            |

|                                        | Acquisition Time CE Pulse Width CS LOW during CE high R/C LOW during CE high A <sub>0</sub> valid during CE high Maximum A <sub>0</sub> delay from CE. Set up as shown (negative time wrt *CE) not needed STS delay from CE Conversion time 8 Bit cycle |

### **CONVERSION START**

A conversion may be initiated by a logic transition on any of the three inputs: CE, CS, R/C, as shown in Table 1. The last of the three to reach the correct state starts the conversion, so one, two or all three may be dynamically controlled. The nominal delay from each is the same and all three may change state simultaneously. In order to assure that a particular input controls the start of conversion, the other two should be setup at least 50ns earlier. Refer to the convert mode timing specifications. The Convert Start timing diagram is illustrated in Figure 1.

The output signal STS is the status flag and goes high only when a conversion is in progress. While STS is high, the output buffers remain in a high impedance state so that data can not be read. Also, when STS is high, an additional Start Convert will not reset the converter or reinitiate a conversion. Note, if  $A_0$  changes state after a conversion begins, an additional Start Convert command will latch the new state of  $A_0$  and possibly cause a wrong cycle length for that conversion (8 versus 12-bits).

### READ CYCLE

| $t_{\rm DD}$    | Access time<br>from CE high | 75ns typ, 150ns max |

|-----------------|-----------------------------|---------------------|

| t <sub>HL</sub> | Output Float<br>Delay       | 150ns max           |

<sup>&</sup>quot;wrt = With Respect To.

#### STAND-ALONE OPERATION

The HS 9474 can be used in a 'stand alone' mode in systems having dedicated input ports. Connections and timing for this mode are shown in Fig. 2.

NOTE: HS 9474 wired for 12-Bit conversion

### **CONVERT CYCLE**

| SYMBOL           | PARAMETER                |           |

|------------------|--------------------------|-----------|

| <sup>I</sup> HRL | Low R/C Pulse Width      | 50ns min  |

| t <sub>DS</sub>  | STS Delay from R/C       | 200ns max |

| tc               | Conversion Time          | 25 µs max |

| tHS              | Data valid after STS low | 70ns max  |

| <sup>t</sup> ACQ | Acquisition Time         | 7 µs typ  |

|                  |                          | 10us may  |

## READ CYCLE

- Data always in 'read' mode except during a conversion in which data lines revert to high impedance.

- 2. Output always valid after conversion is complete

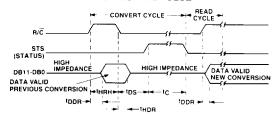

# R/C POSITIVE PULSE

# CONVERT CYCLE

| SYMBOL           | PARAMETER                                         |           |

|------------------|---------------------------------------------------|-----------|

| <sup>t</sup> HDR | Valid Data (Previous Conversion)<br>after R/ℂ low | 25ns min  |

| thBH             | High R/C  Pulse Width                             | 150ns min |

| tDS              | STS Delay from R/C                                | 200ns max |

| <sup>t</sup> DDR | Data Access Time                                  | 150ns max |

| t <sub>C</sub>   | Conversion Time                                   | 25 us max |

#### READ CYCLE

Converter output remains in high impedance state after conversion (STS goes low) until R/C goes high (to 'read' data).

Figure 2. HS 9474 Stand-Alone Operation Top: Using negative R/C pulse Bottom: Using positive R/C pulse

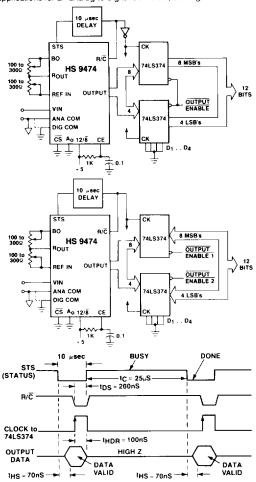

### **CONTINUOUS CONVERSION**

Requirements for self triggered-continuous conversions are popular applications for an analog to digital converter, see Fig. 3.

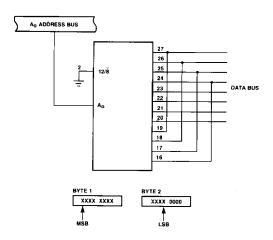

Figure 3. Continuous Conversion Top: DATA BUS 12 Bits or greater Bottom: DATA BUS 8 Bits

CS and A<sub>a</sub> are tied low (0) while 12/8 is tied high (1) to select the converter and enable a 12-Bit conversion. Note A<sub>a</sub> is 'don't care' in the truth table

CE is connected to a 1KΩ and 0.1 μF integrator as shown, this ensures an initial conversion on power up.  $\overrightarrow{CE}$  will see a rising edge which will initiate a conversion  $(\overrightarrow{CS} = 0, R/\overrightarrow{C} = 0)$ . The RC network will then integrate the initial 1 at the output of the first inverter causing a delay in the R/C command. After the first conversion, continuous conversions are caused by delaying the STATUS (STS) into R/C After the conversion is complete the output data lines come out of tri-state approximately 70ns after STS goes low (DONE). Data will remain valid (from previous conversion) 100ns after the new R/C 1 command which allows for the positive edge → triggered data to be loaded into the external buffer (75LS374 or equivalent).

Using the R-C network as shown, 1.5 µs is allowed between conversions. Shorter times can be used but a longer time will cause long rise and fall of the R/C line and the clock input to the buffer. The setup time for the latch shown is 20ns and the hold time is 0ns.

The user may access the octal latches asynchronously by means of the OUTPUT ENABLE (CONTROL OUTPUT) line. The data will always be valid, for a 12-bit conversion. Using this method, data will always be current and the STATUS bit need not be tested for valid data

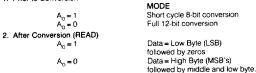

### USING THE Ao LINE

The state of the A<sub>a</sub> line at the start of a conversion places the HS 9474 in either a full 12-bit conversion or in an 8-bit 'short cycle' mode. During a READ at the end of a conversion the An line is used to the format of the data as follows:

#### 1. Prior to Conversion

In a  $\mu P$  application the  $A_o$  line can be considered a pair of  $\overline{W}R$ locations as follows:

### 1. Prior to Conversion (WRITE)

$\overline{W}R = 0$  in low address  $(A_0 = 0)$  $\overline{W}R = 0$  in high address  $(\tilde{A}_0 = 1)$

2. Atter Conversion (READ)  $\overline{W}R = 1$  in either address  $(A_0 = X)$  $\overline{W}R = 1$  in high address  $(A_0 = 1)$  $\overline{W}R = 1$  in low address  $(A_0 = 0)$

### MODE

Full 12-bit conversion Short cycle 8-bit conversion

Full 12-bit word with 12/8 = 1LSB's & zeros when  $12\overline{8} = 0$ 8 MSB's only when 12/8 = 0

## INTERFACING THE HS 9474 WITH 8-BIT MICROPROCESSORS

The HS 9474 which has 12-bit data can be used directly with popular 8-bit microprocessors. The data however, must be multiplexed by setting the output mode select 12/8 pin to GND.

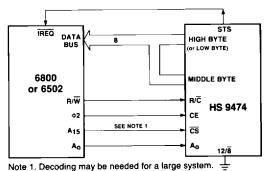

In the first case, a 6800 (or 6502) is used. See Figure 4

Figure 4. Interfacing the HS 9474 and a 6800 µP

The STATUS (STS) is tied directly to IREQ which is the interrupt line. When STS goes to 0 (at the end of a conversion) the 6800 may either service the interrupt or be timed for 25 \( \mu \) (since this IREQ is software maskable) the time required for a conversion

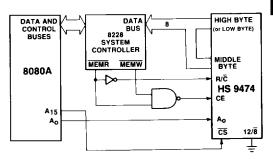

Figure 5 shows the 8080A  $\,\mu\text{P}$  as interfaced with the HS 9474. In this case, a 8228 controller is shown with gates to generate needed signals.

Figure 5. Interfacing the HS 9474 and 8080A μP

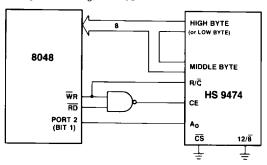

Figure 6 shows the HS 9474 connected with a 8048  $\,\mu\text{P}.$  A single NAND gate is used to generate CE.

Figure 6. Interfacing the HS 9474 and a 8048  $\mu P$

A summary of  $\mu P$  types and connections is in Table 3.

| MICRO-<br>PROCESSOR                               | HS 9474 CONTROL INPUTS |        |                                                                   |                         |

|---------------------------------------------------|------------------------|--------|-------------------------------------------------------------------|-------------------------|

|                                                   | CE                     | R/C    | CS                                                                | A <sub>O</sub>          |

| 8080<br>MEMORY MAPPED<br>I/O<br>PROGRAMMED<br>I/O | (MEMW • MEMR)          | (MEMR) | DECODED<br>ADDRESS                                                | A <sub>o</sub>          |

| 6800                                              | <b>\$</b> 2            | R/₩    | DECODED<br>ADDRESS                                                | Ao                      |

| 6502                                              | <b>†</b> 2             | A/₩    | DECODED<br>ADDRESS                                                | A <sub>o</sub>          |

| Z80<br>MEMORY MAPPED<br>I/O<br>PROGRAMMED<br>I/O  | (RD • WR)              |        | DECODED<br>ADDRESS<br>WITH MREQ<br>DECODED<br>ADDRESS<br>WITH IOR | A <sub>O</sub>          |

| 8048                                              | (RD • WR)              | (RD)   | PORT 2 <sub>0-3</sub> *                                           | PORT 2 <sub>0-3</sub> * |

<sup>\*</sup>Port 2. Lines 0-3 can be used as a 4-Bit address bus. System address decoding requirements vary from no hardware to a fully latched 12-Bit address, depending on system complexity.

Table 3. Summary of HS 9474 Control Inputs with Various Microprocessors

# **ENABLING DATA IN 8-BIT MODE**

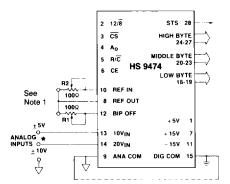

To operate the HS 9474 in a 12-bit conversion mode with an 8-bit data bus, use the basic configuration shown in Figure 7. The  $A_{\rm O}$  control can be connected to the least significant bit of the data bus in order to store the output data into two consecutive memory locations. When  $A_{\rm O}$  is pulled low, only the 8 MSB's are enabled. When  $A_{\rm O}$  is high, the 4 MSB's are disabled, bits 4 through 7 are forced to a zero and the 4 LSB's are enabled. The two byte format is ''left justified data'' as shown above and can be considered to have a decimal point or binary to the left of byte 1.  $A_{\rm O}$  may be toggled without damage to the converter at any time. Break-before-make action is guaranteed between two data bytes. This assures that the outputs which are strapped together in Figure 7 will never be enabled at the same time.

# **ZERO AND GAIN CONNECTIONS**

The HS 9474 is normally used with external zero and gain calibration potentiometers. However, if maximum accuracy is not required, they may be omitted. If no trims are used, the gain calibration will be within approximately ±2LSB zero offset error, and ±12LSB maximum full scale error. See Figure 8 for connection with no trims. If gain and zero adjustment potentiometers are used, they should be connected as shown in Figure 9. The zero control has a range of about ±20LSB, and the gain control has a range of about ±3LSB. Proper gain and zero calibration requires great care and the use of extremely sensitive and accurate instruments. The voltage source used as a signal input must be very stable. It also should be capable of being set to within 1/10LSB at both ends of its range.

The HS 9474's zero and gain adjustments are independent of each other if the zero (or offset) adjustment is made first.

Figure 7. Enabling Data in 8-Bit Mode

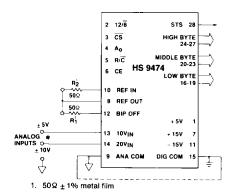

Figure 8a. No Trim Biplor Input Connections

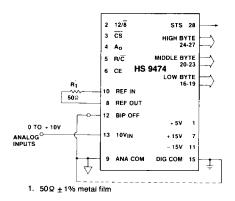

Figure 8b. No Trim Unipolar Input Connections

- 1. To increase adjustment range:

- a) Change R1 and R2 to 300

- b) Add series resistor  $100\Omega$  to  $\pm 5V$  input and  $200\Omega$  to  $\pm 10V$  input.

- \*Selected at factory

- \*\*May be changed to 300Ω for greater adjustment capability.

Figure 9a. Bipolar Input Connections with Trim Adjustment

- 2. To increase adjustment range:

- a) Change R3 to 33kΩ, and R2 to 300

- b) Add series resistor 100 Ω to ±5V input and 200 Ω to ± 10V input.

Figure 9b. Unipolar Input Connections with Trim Adjustment

### ZERO ADJUSTMENT PROCEDURE

- 1. For unipolar ranges:

- a) Set input voltage precisely to + 1/2LSB.

- Adjust zero control until converter is switching from 000000000000 to 00000000001.

- 2. For bipolar ranges:

- a) Set input voltage precisely to ½LSB above F.S.

- b) Adjust zero control until converter is switching from 000000000000 to 00000000001

### **GAIN ADJUSTMENT PROCEDURE**

- Set input voltage precisely to ½LSB less than 'all bits on' value. Note that this is 1½LSB less than nominal full scale.

- 2. Adjust gain control until converter is switching from 11111111110 to 111111111111.

Table 4 summarizes the zero and gain adjustment procedure, and shows the proper input test voltages used in calibrating the HS 9474.

Table 4. Calibration Data

| Input<br>Voltage<br>Range | Adjust-<br>ment | Input<br>Voltage | Adjust input to point<br>where converter is<br>just on the verge of<br>switching between<br>the two codes shown.1 |

|---------------------------|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| - 1 Model                 | ZERO            | 1.22mV           | 0000 0000 0000                                                                                                    |

| 0 to + 10V                | GAIN            | 9.9963V          | 1111 1111 1110                                                                                                    |

| - 1 Model                 | ZERO            | - 4.9988V        | 0000 0000 0000                                                                                                    |

| ± 5V                      | GAIN            | 4.9963V          | 1111 1111 1110                                                                                                    |

| - 2 Model                 | ZERO            | - 9.9976V        | 0000 0000 0000                                                                                                    |

| ± 10V                     | GAIN            | 9.9927V          | 1111 1111 1110                                                                                                    |

<sup>1</sup>Codes shown are natural binary for unipolar input ranges and offset binary for bipolar ranges.

0 = a transition between logic "1" and logic "0".

### POWER SUPPLY CONSIDERATION

Power supplies used for the HS 9474 should be selected for low noise operation. In particular they should be free of high frequency noise. Unstable output codes may result with noisy power sources. It is important to remember that 2.44mV is 1LSB for a 10 volt input.

Decoupling capacitors are recommended on all power supply pins located as close to the converter as possible. Suitable decoupling capacitors are 10  $\mu F$  tantalum type in parallel with 0.1  $\mu F$  disc ceramic type.

#### **GROUNDING CONSIDERATIONS**

The analog common at pin 9 is the ground reference point for the internal reference and is thus the high quality ground for the HS 9474; it should be connected directly to the analog reference point of the system. In order to achieve all of the high accuracy performance available from the HS 9474 in an environment of high digital noise content, it is recommended that the analog and digital commons be connected together at the package. In some situations, the digital common at pin 15 can be connected to the most convenient ground reference point; analog power return is preferred. If digital common contains high frequency noise beyond 200mV, this noise may feed through the converter, so that some caution will be required.

It is also important in the layout, to carefully consider the placement of digital lines. It is recommended that digital lines not be run directly under the 9474. For optimum system performance, if space permits, a ground plane is advised under the 9474. This should be connected to a digital ground. Finally, in packaging the assembled 9474, the designer should also try to minimize any capacitive coupling that might occur at the top to the device.

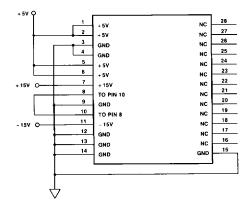

Figure 10. Burn-In Schematic

# **ORDERING INFORMATION**

| MODEL        | RESOLUTION   | INPUT          | TEMPERATURE     | SCREENING           |

|--------------|--------------|----------------|-----------------|---------------------|

| NUMBER       | MONOTONICITY | RANGE(S)       | RANGE           |                     |

| HS 9474J-1   | 11 Bits      | ±5V, 0 to +10V | 0° to +70°C     |                     |

| HS 9474J-2   | 11 Bits      | ±10V           | 0° to +70°C     |                     |

| HS 9474K-1   | 12 Bits      | ±5V, 0 to +10V | 0° to +70°C     |                     |

| HS 9474K-2   | 12 Bits      | ±10V           | 0° to +70°C     |                     |

| HS 9474S/B-1 | 11 Bits      | ±5V, 0 to +10V | -55°C to +125°C | 883 Rev. C, Level B |

| HS 9474S/B-2 | 11 Bits      | ±10V           | -55°C to +125°C | 883 Rev. C, Level B |

| HS 9474T/B-1 | 12 Bits      | ±5V, 0 to +10V | -55°C to +125°C | 883 Rev. C, Level B |

| HS 9474T/B-2 | 12 Bits      | ±10            | -55°C to +125°C | 883 Rev. C, Level B |

Specifications subject to change without notice.