## INTEGRATING LIGHT-VOLTAGE CONVERTER

## **FEATURES**

- Two photosensors with integrating amplifiers

- Integration time can be set externally

- Internal shift register for chain connection

- Detection of low supply voltage

- TTL/CMOS-compatible logic inputs and outputs

- 5V supply voltage

- Low power consumption

- -198 CARIN Photosensors with 1mm pitch; active area ca. 0.97mm x 0.55mm (0.4mm<sup>2</sup>)

## **APPLICATIONS**

- Optical row sensors

- As substitutes for CCDs

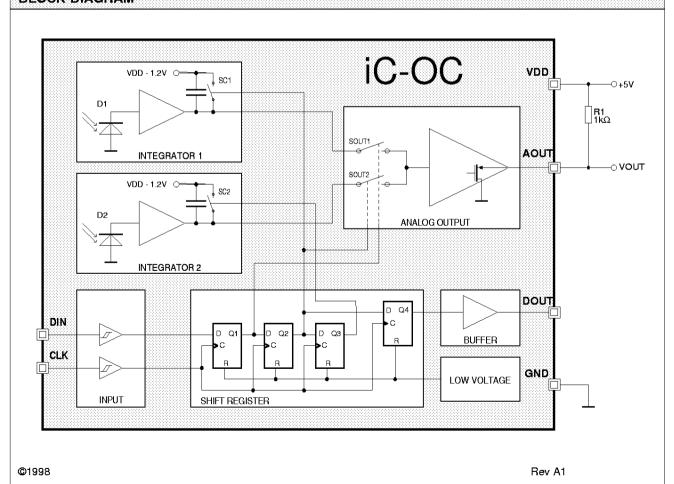

#### **BLOCK DIAGRAM**

iC-Haus GmbH Integrated Circuits Am Kuemmerling 18, D-55294 Bodenheim Tel +49-6135-9292-0 Fax +49-6135-9292-192 http://www.ichaus.com

## INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 2/7

#### DESCRIPTION

iC-OC is an optical sensor with two photodiodes, two integrating amplifiers and a control logic which enables several iC-OCs to be connected in a chain.

Furthermore, the control logic, consisting of a two-stage shift register, determines when the integration time starts and ends and switches the integrators in sequence to the analog output. The analog output is a source follower and in its deactivated state has a high impedance and can thus be used in buses.

The control logic output supplies a CMOS-compatible signal and in chain connection it can be directly linked to the digital input of the next device. Logic inputs are configured as Schmitt triggers and are TTL/CMOS-compatible.

All the registers in the device are reset with low voltage (power-down reset). All pins are protected against ESD.

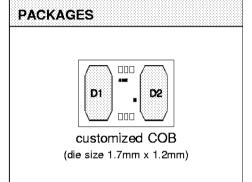

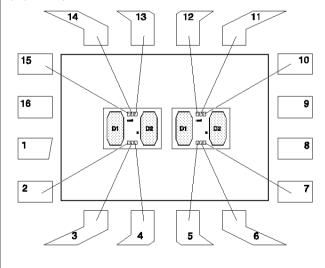

## PACKAGES CDIP16 (for samples only)

#### **PIN CONFIGURATION**

(top view)

#### **PIN FUNCTIONS**

| PIN FUNCTIONS                                                  |                                                                                       |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Name                                                           | Function                                                                              |  |  |  |  |

| n.c.<br>DIN1<br>CLK1<br>DOUT1<br>VDD1<br>AOUT1<br>GND1<br>n.c. | Input 1 Clock 1 Digital Output 1 +5V Supply Voltage Analog Output 1 Ground            |  |  |  |  |

| DIN2<br>CLK2<br>DOUT2<br>n.c.<br>n.c.<br>VDD2<br>AOUT2<br>GND2 | Input 2 Clock 2 Digital Output 2 +5V Supply Voltage Analog Output 2 Ground            |  |  |  |  |

|                                                                | Name  n.c. DIN1 CLK1 DOUT1 VDD1 AOUT1 GND1 n.c.  DIN2 CLK2 DOUT2 n.c. n.c. VDD2 AOUT2 |  |  |  |  |

# INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 3/7

## **ABSOLUTE MAXIMUM RATINGS**

Values beyond which damage may occur; device operation is not guaranteed.

| Item | Symbol | Parameter                                        | Conditions                                                   | Fig. |      |      | Unit |

|------|--------|--------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

|      |        |                                                  |                                                              |      | Min. | Max. |      |

| G001 | VDD    | Supply Voltage                                   |                                                              |      | -0.3 | 6.5  | V    |

| G002 | lc()   | Schutzdiodenstrom in DIN, CLK, DOUT, AOUT        |                                                              |      | -20  | 20   | mA   |

| G003 | 1()    | Current in DOUT                                  |                                                              |      | -10  | 10   | mA   |

| G004 | llu()  | Pulse Current in all Pins<br>(Latch-up strength) | pulse width ≤ 10μs                                           |      | -100 | 100  | mA   |

| E001 | Vd()   | ESD-Susceptibility, at all Pins                  | MIL-STD-883, Method 3015, HBM 100pF discharged through 1.5kΩ |      |      | 2    | kV   |

| TG1  | Tj     | Junction-Temperatur                              |                                                              |      | -40  | 150  | °C   |

| TG2  | Ts     | Storage-Temperatur                               |                                                              |      | -40  | 150  | °C   |

#### THERMAL DATA

Operating Conditions: VDD= 5V  $\pm 10\%$

| Item | Symbol | Parameter                              | Conditions | Fig. |      |      |      | Unit |

|------|--------|----------------------------------------|------------|------|------|------|------|------|

|      |        |                                        |            |      | Min. | Тур. | Max. |      |

| T1   | Та     | Operating Ambient Temperature<br>Range |            |      | 0    |      | 70   | °C   |

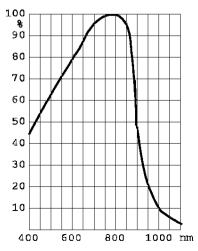

## **ELECTRICAL CHARACTERISTICS: Diagramms**

Relative spectral sensitivity

# INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 4/7

## **ELECTRICAL CHARACTERISTICS**

Operating Conditions:

VDD=5V ±10%, RL(VDD/AOUT)= 1kΩ, Tj= 0..85°C unless otherwise noted

| ltem   | Symbol      | Parameter                                                 | Conditions                                          | Tj | Fig. |      |      |      | Unit      |

|--------|-------------|-----------------------------------------------------------|-----------------------------------------------------|----|------|------|------|------|-----------|

|        |             |                                                           |                                                     | °C |      | Min. | Тур. | Max. |           |

| Total  | Device      |                                                           |                                                     |    |      |      |      |      |           |

| 001    | VDD         | Permissible Supply Voltage<br>Range                       |                                                     |    |      | 4.5  |      | 5.5  | ٧         |

| 002    | I(VDD)      | Supply Current in VDD                                     |                                                     |    |      | 100  |      | 700  | μA        |

| 003    | Vc()hi      | Clamp Voltage hi at<br>DIN, CLK, DOUT, AOUT               | Vc()hi= V() -VDD, I()= 10mA<br>other Pins open      |    |      | 0.3  |      | 1.5  | ٧         |

| 004    | Vc()lo      | Clamp Voltage Io at<br>DIN, CLK, DOUT, AOUT               | I()= -10mA, other Pins open                         |    |      | -1.5 |      | -0.3 | ٧         |

| Analo  | og Output   | AOUT                                                      |                                                     |    |      |      |      |      |           |

| 201    | V0()        | Output Voltage at no illuminance                          | V0()= VDD -V(AOUT)max,<br>AOUT active (* see below) |    |      | 0.8  |      | 1.5  | ٧         |

| 202    | ΔV0()       | Variation of Output Voltage at no illuminance             | ΔV0()= V(AOUT)t1 -V(AOUT)t2,<br>Δt= t2 -t1= 1ms     |    |      |      |      | 50   | mV        |

| 203    | Vlin()      | Range of Linearity for Output<br>Voltage                  | Vlin()= VDD -V0() -V(AOUT)                          |    |      | 1.6  |      |      | ٧         |

| 204    | К           | Transfer Factor Output voltage -<br>Light Power           |                                                     |    |      |      | 0.4  |      | V/<br>pWs |

| 205    | ΔKlin       | Transfer Factor Deviation within Linearity Range          |                                                     |    |      |      |      | 5    | %         |

| 206    | 1()         | Leakage Current                                           | V(AOUT)= 0VDD, AOUT high impedance (* see below)    |    |      | -5   |      | 5    | μА        |

| Shift- | Register li | nputs DIN, CLK                                            |                                                     |    |      |      |      |      |           |

| 301    | Vt()hi      | Threshold Voltage hi at DIN, CLK                          |                                                     |    |      | 1.4  |      | 2.2  | ٧         |

| 302    | Vt()lo      | Threshold Voltage Io at DIN, CLK                          |                                                     |    |      | 0.8  |      | 1.3  | ٧         |

| 303    | Vt()hys     | Hysteresis at DIN, CLK                                    | Vt()hys= Vt()hi -Vt()lo                             |    |      | 300  |      | 1300 | m۷        |

| 304    | li()        | Input Current in DIN, CLK                                 | V()= 0VDD                                           |    |      | -1   |      | 1    | μA        |

| 305    | f()         | Permissible Frequency at CLK                              |                                                     |    |      |      |      | 10   | MHz       |

| 306    | tw()hi      | Permis. Pulse Width hi at CLK                             |                                                     |    |      | 20   |      |      | ns        |

| 307    | tw()lo      | Permis. Pulse Width lo at CLK                             |                                                     |    |      | 20   |      |      | ns        |

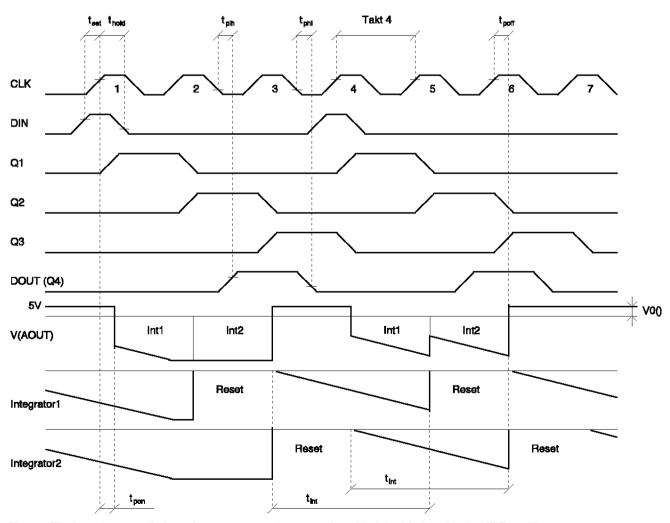

| 308    | tplh        | Propagation Delay:<br>CLK hi→lo until DOUT lo→hi          | CL(DOUT)= 50pF                                      |    | 2    |      |      | 40   | ns        |

| 309    | tphl        | Propagation Delay:<br>CLK hi→lo until DOUT hi→lo          | CL(DOUT)= 50pF                                      |    | 2    |      |      | 40   | ns        |

| 310    | tpon        | Propagation Delay:<br>CLK lo→hi until AOUT active         | CL(VDD/AOUT)= 1nF                                   |    | 2    |      |      | 800  | ns        |

| 311    | tpoff       | Propagation Delay: CLK lo→hi<br>until AOUT high impedance | CL(VDD/AOUT)= 1nF                                   |    | 2    |      |      | 100  | ns        |

| Buffe  | r DOUT      |                                                           |                                                     |    |      |      |      |      |           |

| 312    | Vs()hi      | Saturation Voltage hi                                     | Vs()hi= VDD -V(), I()= -1mA                         |    |      |      |      | 0.4  | ٧         |

| 314    | Vs()lo      | Saturation Voltage lo                                     | I()= 1mA                                            |    |      |      |      | 0.4  | ٧         |

| Low    | Voltage De  | etection                                                  | •                                                   |    |      |      |      |      |           |

| 401    | VDDon       | Turn-on Threshold VDD                                     | increasing voltage at VDD                           |    |      | 2.3  |      | 3.8  | ٧         |

| 402    | VDDoff      | Undervoltage Threshold VDD                                | decreasing voltage at VDD                           |    |      | 1.2  |      | 1.9  | ٧         |

| 403    | VDDhys      | Hysteresis                                                | VDDhys= VDDon -VDDoff                               |    |      | 0.8  |      | 2    | V         |

<sup>(\*)</sup> AOUT active: SOUT1 or SOUT2 closed; AOUT high impedance: SOUT1 and SOUT2 open.

## INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 5/7

## **OPERATING REQUIREMENTS: Logic**

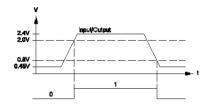

Operating Conditions: VDD= 5V  $\pm$ 10%, Ta= 0..70°C, input levels lo= 0..0.45V, hi= 2.4V..VDD, see Fig. 1 for reference levels

| Item | Symbol | Parameter                                  | Conditions | Fig. |      |      | Unit |

|------|--------|--------------------------------------------|------------|------|------|------|------|

|      |        |                                            |            |      | Min. | Max. |      |

| 11   | tset   | Setup time:<br>DIN stable before CLK lo→hi |            | 2    | 10   |      | ns   |

| 12   | thold  | Hold time:<br>DIN stable after CLK lo→hi   |            | 2    | 5    |      | ns   |

Fig. 1: Reference levels

Fig. 2: Timing characteristics after power on (assumption: V0()1= V0()2= V0(), VDD= 5V)

## INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 6/7

#### DESCRIPTION OF FUNCTIONS

iC-OC is an integrating light-voltage converter with two separate photodiodes and two integrators. The integration time starts when the supply voltage is applied. To obtain a specified integration time a hi pulse must first be available at the digital input DIN and clocked by the device. This process sequentially resets the integrators to their initial value and restarts the integration time with the next clock pulse.

Flip-flops Q1 to Q3 sequentially accept the signal at DIN with the positive CLK edge. Flip-flop Q4, which controls the DOUT output signal, reacts to the negative CLK edge. The switching states in the IC always remain for the duration of a clock cycle. The process depicted in Fig. 2 is initiated when a hi pulse is applied to DIN.

During the first clock cycle integrator 1 is switched to the analog output AOUT (switch SOUT1 closes). AOUT initially supplies a voltage value which cannot be reproduced as the integration time is unknown. The second clock cycle switches the analog output from integrator 1 to integrator 2 (SOUT1 opens, SOUT2 closes). A non-reproducible voltage value is again present at AOUT (see above). At the same time the integration capacity of integrator 1 is short-circuited by switch SC1 (reset).

Flip-flop Q4 is set in the second clock cycle with the negative clock edge (DOUT1) and thus the DIN signal for the next device in the chain is produced.

During the third clock cycle integrator 2 is disconnected from AOUT (SOUT2 opens) and reset (SC2 closes). Simultaneously, the integration time for integrator 1 starts anew (SC1 opens). If several iC-OCs are connected in a chain, then the hi signal from DOUT is shifted into the first flip-flop of the next device with the third clock cycle.

During the fourth clock cycle switch SC2 opens and starts the integration time for integrator 2.

## APPLICATIONS INFORMATION

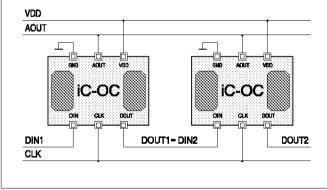

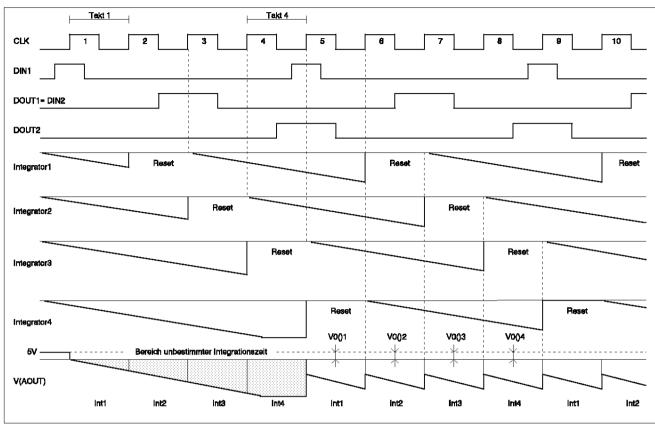

Fig. 3: Example of a chain connection for two devices

Only when the DOUT2 output has a hi level can the next hi signal be applied to DIN1. The first hi signal clocked by the device implements a sequential reset of the integrators, followed by the integration time starting in sequence.

The second hi signal shifted through the register determines the end of the integration time and restarts the integration time after a reset. The integrators can be read out with the aid of a sample and hold circuit, as the device itself has no hold mode.

Besides the clock a periodic signal at DIN is also necessary for the continuous operation of the device.

## INTEGRATING LIGHT-VOLTAGE CONVERTER

Rev A1, Page 7/7

Fig. 4: Time sequence for the chain connection in Fig. 3 after the device has been switched on

With operation of the device at low level illumination the output voltage V(AOUT) decreases by V0(AOUT). When calibrating, this drop in voltage must be determined for each of the photosensors.

#### ORDERING INFORMATION

| Туре                   | Package | Order designation             |

|------------------------|---------|-------------------------------|

| iC-OC<br>OC Demo-Board |         | iC-OC-CDIP16<br>OC Demo-Board |

For information about prices, terms of delivery, options for other case types, etc., please contact:

iC-Haus GmbH Am Kuemmerling 18 D-55294 Bodenheim GERMANY Tel +49-6135-9292-0 Fax +49-6135-9292-192 http://www.ichaus.com

This specification is for a newly developed product. iC-Haus therefore reserves the right to modify data without further notice. Please contact us to ascertain the current data. The data specified is intended solely for the purpose of product description and is not to be deemed guaranteed in a legal sense. Any claims for damage against us - regardless of the legal basis - are excluded unless we are guilty of premeditation or gross negligence.

We do not assume any guarantee that the specified circuits or procedures are free of copyrights of third parties. Copying - even as an excerpt - is only permitted with the approval of the publisher and precise reference to source.