## HITACHI SEMICONDUCTOR TECHNICAL UPDATE

| Classification<br>of Production | Memory                                            |          |                                  | No                                                                                                                                                     | TN-M62-112A/E | Rev            | 1 |

|---------------------------------|---------------------------------------------------|----------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|---|

| THEME                           | SRAM: Notes on Usage Classification o Information |          | Classification of<br>Information | <ol> <li>Spec change</li> <li>Supplement of Documents</li> <li>Limitation of Use</li> <li>Change of Mask</li> <li>Change of Production Line</li> </ol> |               |                |   |

| PRODUCT<br>NAME                 | All 4-Mbit fast<br>SRAM C-mask<br>products        | Lot No.  |                                  | Liteshi IC memory datashasta                                                                                                                           |               | Effective Date |   |

|                                 |                                                   | All Lots | Reference<br>Documents           | Hitachi IC memory datasheets<br>ADE-203-1196B(Z)/1198B(Z)/1199B(Z)/<br>1200C(Z)/1294D(Z)/1202C(Z)/1263A(Z)<br>/1283A(Z)/1304A(Z)/1305A(Z)              |               | Permanent      |   |

As the operating speeds of SRAM products rise, securing the various design margins is becoming more difficult. Accordingly, there is an increasing possibility of noise from the input-signal or power-supply lines acting as an obstacle to the normal operation of SRAM products. To prevent malfunctions in 4-Mbit fast SRAM (C-mask) products, please note the following points.

1. Announcement

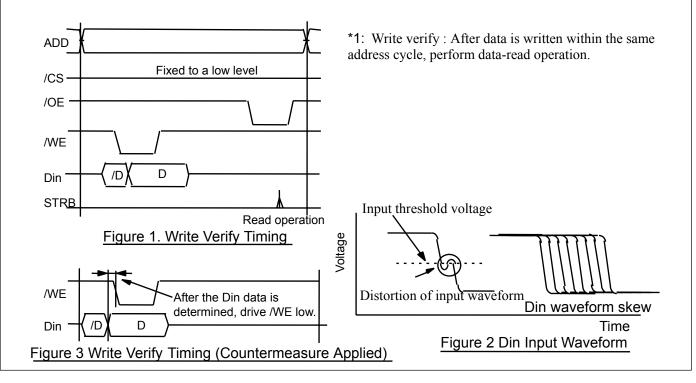

In executing a write-with-verify operations with a 4-Mbit fast SRAM (C-mask) product, incorrect data may be read because of noise, etc., even when the data has been written correctly (see figure 1 and note 1). This problem does not arise with a further read operation. If you are having problems of the type described or your project may be subject to such problems, refer to the points below for the appropriate countermeasures.

2. Countermeasures

Please apply countermeasures (1) and (2) below according to your situation.

- (1) Avoid executing the read for verification in the same cycle as the write operation it follows. Verify the written data after inputting an address or switching the /CS signal.

- (2) Please ensure that your design is not subject to adverse effects because of distortion or skewing of the Din input waveform (figure 2). Drive /WE low (write) after determining the data on Din (see figure 3).