## **BUSSED RESISTOR NETWORK**

California Micro Devices' resistor arrays are the hybrid equivalent to the bussed resistor networks available in surface-mount packages. The resistors are spaced on ten mil centers resulting in reduced real estate. These chips are manufactured using advanced thin film processing techniques and are 100% electrically tested and visually inspected.

| ELECTRICAL SPECIFICATIONS                       |                                        |                        |      |  |  |  |  |

|-------------------------------------------------|----------------------------------------|------------------------|------|--|--|--|--|

| Parameter                                       | Test Conditions                        |                        |      |  |  |  |  |

| TCR                                             | −55°C to 125°C                         | ±100ppm/C              | Max  |  |  |  |  |

| Operating Voltage                               | –55°C to 125°C                         | 50Vdc                  | Max  |  |  |  |  |

| Power Rating (per resistor)                     | @ 70°C (Derate linearly to 0@150°C)    | 50mw                   | Max  |  |  |  |  |

| Thermal Shock                                   | Method 107 MIL-STD-202F                | ±0.25%@∆R              | Max  |  |  |  |  |

| igh Temperature Exposure 100Hrs @ 150°C Ambient |                                        | ±0.25%∆R               | Max  |  |  |  |  |

| Moisture                                        | Method 106 MIL-STD-202F                |                        | Max  |  |  |  |  |

| Life                                            | Method 108 MIL-STD-202F (125°C/1000hr) |                        | Max  |  |  |  |  |

| Noise                                           | Method 308 MIL-STD-202F                | -35dB                  | Max  |  |  |  |  |

|                                                 | ≥250kΩ                                 | -30dB                  | Max  |  |  |  |  |

| Short Time Overload                             | Overload MIL-R-83401                   |                        | Max  |  |  |  |  |

| Insulation Resistance                           | @25°C                                  | 1 x 10 <sub>12</sub> Ω | Min. |  |  |  |  |

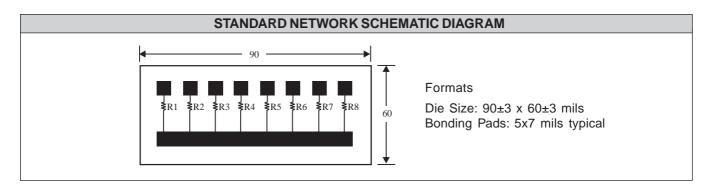

| MECHANICAL SPECIFICATIONS |                                                     |  |  |  |

|---------------------------|-----------------------------------------------------|--|--|--|

| Substrate                 | Silicon 10 ±2 mils thick                            |  |  |  |

| Isolation Layer           | Si02 10,000Å thick, min                             |  |  |  |

| Backing                   | Lapped (gold optional)                              |  |  |  |

| Metalization              | Aluminum 10,000Å thick, min (15,000Å gold optional) |  |  |  |

| Passivation               | Silicon Nitride                                     |  |  |  |

| VALUES                                                  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|

| 8 resistors from 100 $\Omega$ to 500K $\Omega$          |  |  |  |  |

| PACKAGING                                               |  |  |  |  |

| Two inch square trays of 196 chips maximum is standard. |  |  |  |  |

| NOTES                                                   |  |  |  |  |

| Resistor pattern may vary from one value to another.    |  |  |  |  |

| PART NUMBER DESIGNATION |                    |                 |                     |                      |                    |                    |  |  |  |

|-------------------------|--------------------|-----------------|---------------------|----------------------|--------------------|--------------------|--|--|--|

| NCC                     | 5003               | F               | Α                   | G                    | W                  | Р                  |  |  |  |

| Series                  | Value              | Tolerance       | TCR                 | Bond Pads            | Backing            | Ratio<br>Tolerance |  |  |  |

|                         | First 3 digits are | $D = \pm 0.5\%$ | No Letter = ±100ppm | G = Gold             | W = Gold           | No Letter = 1%     |  |  |  |

|                         | significant value. | F = ±1%         | $A = \pm 50$ ppm    | No Letter = Aluminum | L = Lapped         | P = 0.5%           |  |  |  |

|                         | Last digit repres- | G = ±2%         | $B = \pm 25ppm$     |                      | No Letter = Either |                    |  |  |  |

|                         | sents number of    | J = ±5%         |                     |                      |                    |                    |  |  |  |

|                         | zeros. R indicates | K = ±10%        |                     |                      |                    |                    |  |  |  |

|                         | decimal point.     | M = ±20%        |                     |                      |                    |                    |  |  |  |

© 2000 California Micro Devices Corp. All rights reserved.

C0970500