RA0256B Solid State Image Sensor Array

### Introduction

The EG&G Reticon RA0256B is a two-dimensional self-scanned optical sensor array with perfected characteristics. 65,536 discrete photodiodes are geometrically arranged into 256 x 256 matrix. In contrast to comparable CCD devices, the discrete photodiode sensors require no surface electrode so there is no interference pattern or light loss and the full inherent sensitivity is obtainable.

The scanning method permits pixel rates up to 5 MHz. Each line of pixel information is parallel-loaded into a high-speed bucket-brigade analog shift register and sequentially shifted out. All 256 lines may be sequentially accessed to give a 256-line frame, or alternate odd or even lines may be selected to produce 128 lines per field in an odd and even field pattern. The integration time is nominally one frame period, giving maximum sensitivity.

### **Features**

- 65,536 light-sensitive elements in a high-resolution 256 x 256 matrix

- 40 µm center-to-center element spacing in both X and Y directions

- Frame storage—each diode integrates photocurrent for the entire frame

- Self-scanned in both X and Y directions by high-speed on-chip circuitry to provide either single frame or interlaced odd/even field multiplexed serial video output

- Nonburning sensors

- Solid-state reliability

- · Low power dissipation

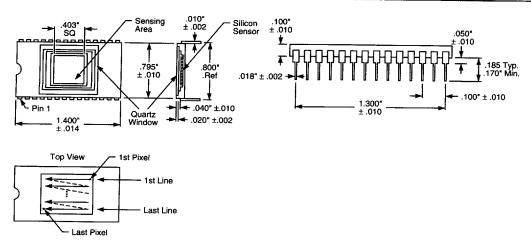

- 28-pin dual-inline package with scratch-resistant quartz window

## **General Description**

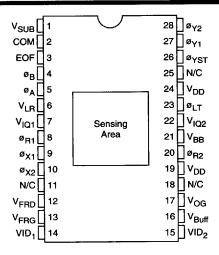

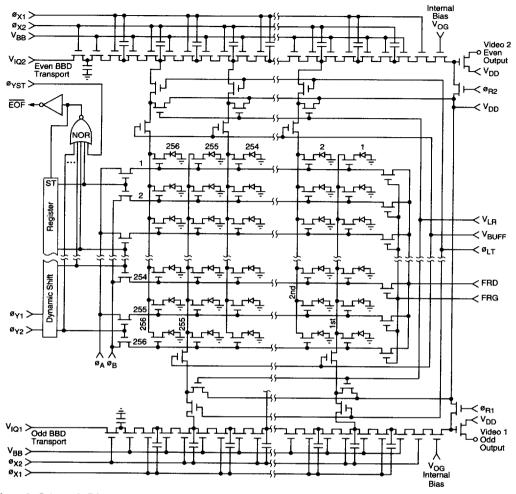

The RA0256B is packaged in a 28-pin dual-inline pin package with a ground and polished window covering the mask-defined active area. Figure 1 is the device's pinout configuration. The device, fabricated on a monolithic silicon chip, contains the matrix diode array with access and reset switches in addition to both the X and Y readout shift registers. Figure 2 is a schematic representation.

A MOS dynamic shift register sequentially selects the diode rows while two bucket brigades connect to each column. Each position of the shift register selects two diode rows through two multiplexing gates,  $\emptyset_A$  and  $\emptyset_B$ , one for the odd and the other for the even, providing the user the choice of selecting the odd or even fields.

Together the shift register and the bucket brigade process the signal in the following sequence: The shift register selects two rows, one of which is selected by the ØA or ØB clock. The transfer gates parallel-transfer the selected diode in each column into the bucket brigade.

Figure 1. Pinout Configuration

One bucket brigade obtains information from odd and the other from even diode columns and each then shifts that information sequentially to the output. On the output side, there are three extra buckets on the even video transport and two extra buckets on the odd video. Therefore, the even video is delayed an extra 1/2 cycle of the shift frequency,  $\mathfrak{g}_{X1}$ , to obtain the desired time sequence. The alternating odd and even signals are then transferred to corresponding output ports, VID<sub>1</sub> and VID<sub>2</sub>.

The integration times are determined by the time interval between accesses for a given diode. This interval can be controlled through the special frame reset clock or through the normal sequential readout. The difference between the two reset processes lies in the integration time for each diode. Frame reset initializes all diodes simultaneously and hence allows each diode to increase the integration time monotonically as the diodes are sequentially read-out—while in the array's normal scanning mode, each diode is accessed periodically with a constant time interval. Hence, in this mode each diode has the same integration time.

# Input/Output Definitions and Functional Description

The area array has functional elements which serve to control the timing sequences for diode access, to transport the pixel information to the output, to control integration time, to control the odd and even fields, to provide for interlace, and to buffer each video output. The external circuit provides the timing and the bias to these functional elements as well as clocks to control ØA, ØB, LT, VBUFF, ØYST, EOF, FRD, ØR1, ØR2, VIO1,VIO2.

345 POTBERO AVENUE SUNNYVALE, CALIFORNIA 94086-4197 (408) 738-4266 FAX: (408) 738-6979

**3**030738 0004741 420 🖿

Figure 2. Schematic RA0256B

1. The Odd and Even Bucket Brigade Transports and Their Clocks,  $\emptyset \chi_1$ - $\emptyset \chi_2$ .

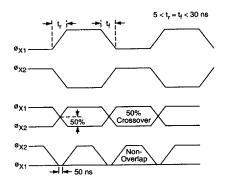

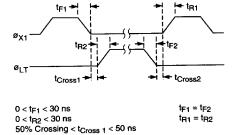

Figure 2 shows two bucket brigade analog shift registers located on each side of the device. These are the odd and even transport registers which accept the pixel information in parallel from their respective odd and even video diode columns and shift the pixel information sequentially to the output amplifier. Each bucket brigade must be provided with a two-phase clock as shown in Figure 3. Note: To ensure high transfer efficiency, it is important that the clock waveforms cross at or below the 50% level. The two limits on clock crossing are shown in Figure 3. Normally these clocks swing from a low of 0.4V to a high of 15V.

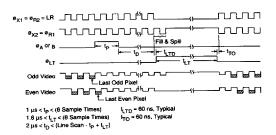

As evident from Figures 2 and 4, the transfer into both shift

registers takes place simultaneously while the  $\emptyset_{X2}$  is held high. However, the odd bucket brigade produces a pixel first, since it reads out on the second low-going  $\emptyset_{X2}$  clock after the transfer period. The second pixel is produced by the even shift register. This pixel must transfer through an extra half-stage which is controlled by the  $\emptyset_{X1}$  clock; thus, even pixels are produced 1/2 cycle out of phase with the odd pixels to provide an easily multiplexed signal by means of a simple adder amplifier.

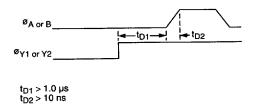

The multiplexing increases the pixel rate to 2 times the transport clock frequency. See Figure 4 for the clock timing diagram. Figure 5 shows the detailed relationship between  $\alpha_{X1}$  and  $\alpha_{LT}$ , the line transfer clock. Figure 6 shows the detailed relationship between  $\alpha_{A}$ , and  $\alpha_{B}$ , the vertical multiplexing clocks, and  $\alpha_{Y}$ , the shift register clock.

Figure 3. Illustration of  $\emptyset_{X1}$  and  $\emptyset_{X2}$  Clock Crossover and Time Tolerance

Figure 4. Overall Relationship

tCross 1 = tCross 2

Figure 5. Detailed Timing Between  $\emptyset_{X1}$  and  $\emptyset_{LT}$

Figure 6. Detailed Timing Between ØA or ØB, ØY1 or ØY2

### 2. The Y Dynamic Shift Register

This shift register is shown in Figure 2 as a block with 128 outputs, each connected to two multiplexing gates plus one extra stage at each end. The gates are connected to two rows of photodiodes and select those rows in accordance to the multiplex clocks, øA and øB. If øA and øB are atternately clocked, the rows will be sequentially accessed, each selected diode connected to its respective column's video line. Then the photodiode information on each column line is transferred to the bucket brigade. Tied to each stage of the shift register are inputs to a NOR gate which provides for the self-loading feature. When there is a "1" in any of the 130 stages the NOR gate keeps the shift register from loading. Once the bit has been clocked out of the last stage, the NOR gate's output goes high and the shift register loads with the falling edge of øy1. Note that øysT is connected to the NOR gate. It can be used to inhibit the register from loading by pulling øyst to VDD. The register requires a two-phase clock which typically swings from a low of 0.4V to VDD.

Note there are two extra stages, one in the first and another in the last position. The purpose of the stages is to minimize the interference caused by the starting and terminating process of the shift register.

### Line Select Controls, ØA and ØB

As evident from the schematic diagram, Figure 2, the  $\emptyset_A$  input terminal controls the gates that switch all of the odd-numbered rows from the Y shift register, and the  $\emptyset_B$  terminal controls the gates that switch the even-numbered rows. These gates,  $\emptyset_A$  and  $\emptyset_B$ , select the rows of diodes as discussed under Section 2. The time relationship is shown in Figure 6.

### 4. Line Reset, LR

The LR maintains the potential of the column video line between line transfers by bleeding off the excess charges collected under excess illumination. It will require adjustment when the frame reset function is used. This adjustment is discussed under Optimum Relation Between Clocks and Bias.

### 5. Line Transfer, LT, and Line Buffer, VBUFF

The LT pulse input controls the period during which the row of diode information is transferred into the bucket-brigade transport registers. This pulse must occur while LR is off (low). Normally this LT input is clocked as seen in Figures 4 and 5 with rise and fall as shown. The line buffer control, VBUFF, is normally held at approximately 0.8 VDD and adjusted to optimize blooming control.

### 6. Y Shift Register Start, Øyst

The  $\emptyset_{YST}$  input provides access to one of the inputs to the Y shift register's NOR gate (Figure 2). When this input is held high, the output of the NOR gate is held low and inhibits loading of the shift register; however, when the  $\emptyset_{YST}$  input is pulled low, the NOR output rises and a bit is loaded into the register with the falling edge of  $\emptyset_{Y1}$  clock. The first two rows are then accessed on the next  $\emptyset_{Y1}$  rising edge.

### 7. End of Frame, EOF

As discussed under  $\emptyset_{YST}$ , the Y shift register has a NOR gate which provides control for the self-starting feature. The NOR gate output is connected to an external pin through an open-drain inverter. This output is normally tied to  $V_{DD}$  through an 8.6 K $\Omega$  resistor; therefore, when there is a bit in any row, or if  $\emptyset_{YST}$  is active, EOF will remain high. It goes immediately low on the rising edge of  $\emptyset_{YZ}$ , when the bit leaves the last stage of the shift register. This point will sink a maximum of 1.5 ma.

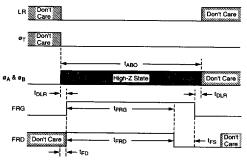

### Frame Reset, FRG

This input controls access switches to every diode in the matrix and provides simultaneous resetting of all diodes. Since the diodes in each line are automatically reset when the line is accessed, the frame reset control is not normally used, and, as such, is held low. However, when a particular exposure is desired, this control may be used to clear the diodes to start a fresh integration cycle.

The minimum timing requirements for the frame operation are shown in Figure 7.  $\varnothing_A$  and  $\varnothing_B$  are held in a high-impedance state during the entire procedure. FRG and FRD are pulsed as shown to connect all photodiodes to their respective video lines. During this connection, the array is taken through at least three line-transfer-and-readout sequences. This resets the video lines and photodiodes through the BBD output registers (the LR function could be used, too, at the expense of

|                  | Min    | Тур | Max    | Remark                                 |                                                                         |

|------------------|--------|-----|--------|----------------------------------------|-------------------------------------------------------------------------|

| t <sub>DLR</sub> | 200 ns |     |        |                                        | Note: Clock rise and fall<br>times are not critical.                    |

| †ABO             |        |     |        | To be consistant with t <sub>FRG</sub> | However it is recommended not to                                        |

| t <sub>FRG</sub> | 2.5 ms |     | 3.5 ms |                                        | exceed 0.5 μs. While<br>frame reset is active,<br>the reset takes place |

| terd             | 2.5 ms |     |        |                                        | by performing at least<br>3 line scans using the                        |

| t <sub>FS</sub>  | 4.0 µs |     |        |                                        | BBD registers. If no bi                                                 |

| tFD              | 0.2 µs |     |        |                                        | between frames), ø <sub>A</sub><br>and ø <sub>B</sub> need not be       |

|                  |        |     |        |                                        | taken to a high-Z state<br>during frame reset.                          |

Figure 7. Timing Sequence for Frame Reset. This is only performed before or after a line transfer sequence.

more fixed-pattern-noise (FPN). This FPN can be reduced by going through one line readout sequence after the line reset is done). After the reset is finished, FRD is taken low to turn off the multiplex switches. It is important to wait the indicated time,  $t_{\rm FS}$ , to make sure the multiplex switches are not left with their gates floating "on."

For best performance, the frame reset drain input may require adjustment. The adjustment procedure is described under Optimum Relation Between Clocks and Bias.

## Reset Clocks for the Gated-Charge Amplifiers, Ø<sub>R1</sub> and Ø<sub>R2</sub>

These terminals provide reset voltages for the gated-charge amplifiers which are shown in the schematic diagram, Figure 2, at the outputs of both bucket brigades. On the even side, the signal appears at the gate of the output source follower when  $\varnothing_{X1}$  drops to a low potential. While  $\varnothing_{X1}$  is high, before the next sample appears, this node is cleared by charging it to a reset voltage. Thus, reset is accomplished when this terminal is clocked synchronously with  $\varnothing_{X1}$ . The complementary situation applies to the odd output, with signal appearing while  $\varnothing_{X2}$  is low and reset while  $\varnothing_{X2}$  is high. The extra half-stage in the even side allows the alternating sequence desired. Normally, the synchronous relationship is obtained by direct connection of  $\varnothing_{X1}$  to  $\varnothing_{R2}$ , and direct connection of  $\varnothing_{X2}$  to  $\varnothing_{R1}$ . The timing sequence for the output signal is shown in Figure 4 relative to the transfer pulse time.

### 10. Video Output Terminals, VID1 and VID2

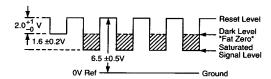

The video output is that of a source follower. Normally, the output of each source follower is connected to  $1 \mathrm{K}\Omega$  which is referenced to ground. This configuration provides the proper bias current for the source follower. Figure 8 shows the output voltage across such a load resistor, showing the relationship of the video pixel information relative to the superimposed reset clock amplitude.

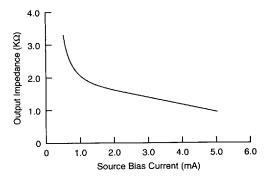

Figure 9 shows the output impedance of the source follower as a function of the bias current. This graph can be used to design a desired interface circuit with suitable DC bias translation (e.g., an emitter-coupled transistor with the base biased up near the video output line potential).

### 11. Input Bias, VIO1 and VIO2

Bias voltages are connected to the inputs of both bucketbrigade transports:  $V_{IQ1}$  to the odd and  $V_{IQ2}$  to the even. These inputs control the bias level in the dark. Nominally, these terminals are biased to approximately 10V.

Figure 8. Typical Video Signal Across a 1  $K\Omega$  Output Load

Figure 9. Output Impedance vs. Output Source Current

Figure 10a. Scope Output

An example of worst case adjustment. Single frame scan of video output after frame reset. Horizontal 0.5V/div, Vertical 0.002 sec/div.

Figure 10b. Scope Output

An example of properly biased output. Single frame scan of video output after frame reset. Horizontal 0.5V/div, Vertical 0.002 sec/div.

## Adjustment of VIQ1 and VIQ2

Since  $V_{IQ1}$  and  $V_{IQ2}$  bias the internal operating levels of the bucket brigade, they affect the output signal level. Since there are two bucket brigade outputs, when the two are summed together, an odd and even imbalance may be experienced. One easy method to balance out the odd and even patterns in the summed video is to make one of the  $V_{IQ}$  inputs adjustable.

Typically these voltages are set to 10V and they will produce an output bias condition as seen in Figure 8 where the difference between the "fat zero" (or the dark level) and the reset level will maintain a magnitude of approximately 2V. However, when  $V_{BB}$  is reduced, the "fat zero" level reduces proportionally. In this case,  $V_{IQ1}$  and  $V_{IQ2}$  may be reduced to maintain the "fat zero" level. In any case, both  $V_{IQ}$  voltages and  $V_{BB}$  must be limited according to  $7 < V_{IQ} < 10V$  and  $8.5 < V_{BR} < V_{DD} - 0.5$ .

## **Optimum Relation Between Clocks and Bias**

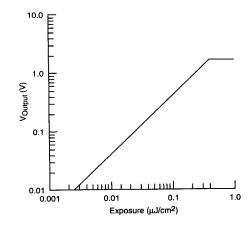

Greatest performance from the device is normally obtained with the  $\emptyset_{\chi_2}$  and LT clocks interleaved as shown in Figure 4. In this mode of operation the optical to electrical transfer function is given in Figure 11. The dynamic range is in excess of 100:1 with an rms noise-equivalent exposure of less than .5 x 10-3  $\mu$ J/cm<sup>2</sup>.

The important relationships that must be observed are timing of the clock transitions of  $\emptyset_{X1}$ ,  $\emptyset_{X2}$ ,  $\emptyset_{Y1}$  and  $\emptyset_{Y2}$ ; the zero level of LT; and the relative timing relationship between LT and  $\emptyset_{X2}$  (this creates a fill-and-spill phenomenon to improve transfer efficiency). Furthermore, when FR is employed, both the LR and FR voltage level will require adjustment (see Frame Reset Adjustment).

Figure 11. Exposure Chart

$\sigma_{X1}$  and  $\sigma_{X2}$  are complementary clocks with crossover of the transition edge taking place at or below 50% of the clock amplitude. Rise and fall times preferably are on the order of 20 nanoseconds. If an MH0026 or equivalent is employed, place a 50 $\Omega$  resistor in series between the driver output and the clock input pins. This edge control is required to obtain the optimum efficiency from the bucket-brigade transport (refer to Figure 3 for  $\sigma_X$  clock shapes).

$\emptyset_{Y1}$  and  $\emptyset_{Y2}$  also are complementary and should cross approximately at the 50% level at the transition edges and should have rise and fall times the same as the  $\emptyset_X$  clocks. The transition-edge spacing of the interleaving clocks  $\emptyset_{LT}$  and  $\emptyset_{X2}$  should be kept as shown in the detailed timing diagram of Figure 4.

## Frame Reset Adjustment

When FR is employed, FRD and V<sub>LR</sub> voltages may require adjustment. With the application of the voltage as given in the specification table, the array will provide operation suitable for most applications. However, to obtain the best balance between low noise, high sensitivity, and antiblooming control, the following adjustment procedure is recommended.

With the array operating with the voltages as specified in the specification table, make the following adjustment: Apply a uniform light across the array surface to provide an output which is approximately 1/4 of the total saturated output. Apply the frame reset clock as specified in Figure 7 and the specification table. Operate the array atapproximately 2 MHz sampling rate. With the Frame Reset pulse synchronized to the scope, the frame scan as shown in Figure 10A will be seen. Lower LR amplitude to approximately 12V then lower FRD voltage towards 10V until a linear output as seen in Figure 10B is achieved.

### Transfer Function and Spectral Response

Figure 11 is a transfer function graph which shows a linear optical-to-electrical relationship with dynamic range exceeding 100:1. This linear relationship depends on the proper electrode potentials, especially those for V<sub>BUFF</sub> and the line reset level, LR. Improper potentials can cause substantial nonlinearity.

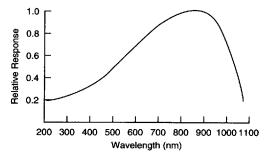

The array spectral response is shown in Figure 12.

Figure 12. Photodiode Response

**Table 1. Array Mechanical Characteristics**

|                                                                                               |                                                       | Units   |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|

| Number of diodes Diode X, Y center-to-center spacing Diode sensing area Package size (28-pin) | 65,536<br>40/1.57<br>912 μm <sup>2</sup><br>0.8 x 1.4 | μm/mils |

Table 2. Terminal Input Capacitance

| Pin | Sym               | Capacitance (pF)  |  |

|-----|-------------------|-------------------|--|

|     |                   | - тарионано (р. ) |  |

| 3   | End of frame      | 5                 |  |

| 4   | ØΒ                | 21                |  |

| 5   | Ø <sub>A</sub>    | 21                |  |

| 6   | VLR               | 48                |  |

| 7   | V <sub>IQ1</sub>  | 5                 |  |

| 8   | V <sub>R1</sub>   | 6                 |  |

| 9   | ØX1               | 150               |  |

| 10  | ø <sub>X2</sub>   | 150               |  |

| 12  | ØFRD              | 50                |  |

| 13  | ØFRG              | 29                |  |

| 14  | VID <sub>1</sub>  | 6                 |  |

| 15  | VID <sub>2</sub>  | 6                 |  |

| 16  | V <sub>BUFF</sub> | 64                |  |

| 17  | Vog               | 6                 |  |

| 20  | V <sub>R2</sub>   | 4                 |  |

| 21  | V <sub>BB</sub>   | 101               |  |

| 22  | V <sub>IQ2</sub>  | 5                 |  |

| 23  | ØLT               | 43                |  |

| 26  | ØYST              | 4                 |  |

| 27  | ØY1               | 28                |  |

| 28  | ø <sub>Y2</sub>   | 28                |  |

Table 3. Array Performance Characteristics (T<sub>A</sub> = 23°C)

| Sym                                                                     | Parameter                                                                                                                                                                                                                    | Тур                                                            | Max           | Units                                                                                           |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------|

| DR<br>ENE<br>ESat<br>R<br>PRNU<br>VDark<br>VSat<br>RO<br>f <sub>s</sub> | Dynamic range (P-P) 1 Peak-to-peak noise equivalent exposure 2 Saturation exposure 2 Responsivity 2 Photoresponse nonuniformity 1,2 Average dark signal 3 Saturation output voltage 4 Output impedance 5 Video sample rate 6 | 100:1<br>2.5 x 10 <sup>-3</sup><br>0.4<br>4<br>±10<br>1<br>1.6 | ±15<br>2<br>2 | —<br>μJ/cm <sup>2</sup><br>μJ/cm <sup>2</sup><br>V/(μJ/cm <sup>2</sup> )<br>%<br>V<br>ΚΩ<br>MHz |

## Notes:

- Ignoring lines 1, 2 and 256 as well as the first and last two diodes of each line

- 2870°K tungsten lamp with a Fish Schurman HA-11 visible spectrum filter was used as the source

- 3 Integration time 20 ms. Dark signal changes by a factor of 2 every 7°C

- 4 Voltage measured across  $1.5 \text{K}\Omega$  load resistor

- 5 See Figure 9

- 6 Odd and even video outputs combined

**Table 4. Electrical Specifications**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Parameter                                                                           |                                                                                              |                                                                            |                                                                                                      |                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------|

| Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Sym                                                                                 | Min                                                                                          | Тур                                                                        | Max <sup>3</sup>                                                                                     | Dimension                             |

| X-register clock amplitudes <sup>2</sup> Y-register clock amplitudes <sup>2</sup> Y shift register reset amplitude Line transfer amplitude Line reset amplitude Line reset amplitude X-register input bias odd X-register input bias even Video reset 1 (odd) Video reset 2 (even) Frame reset gate <sup>1</sup> Frame reset drain <sup>1</sup> Isolation gate DC supply DC current X-register tetrode gate bias Multiplex clock amplitude Multiplex clock amplitude Substrate bias | ØX1 ØX2 ØY1 ØY2 ØYST ØLT VLR VIQ1 VIQ2 VR1 VR2 FRG FRD VBuff VDD IDD VBB ØA ØB VSub | 11.5<br>11.5<br>11.5<br>11.5<br>11.5<br>11.5<br>9<br>11.8<br>6<br>8<br>11.5<br>11.5<br>-2.95 | 14 14 14 14 14 12 10 VDD-0.5 VDD-0.5 VDD-0.5 10 12.75 15 8 12.5 14 14 -3.3 | VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>VDD<br>13<br>16<br>10<br>VDD-55V<br>VDD<br>VDD-3.65 | > > > > > > > > > > > > > > > > > > > |

## Notes:

- See text

- All voltages measured with reference to common (ground). See text

- 3 For optimum performance use typical value. Other in-spec voltages will operate the array but with reduction in performance

Figure 13. Package Dimensions and Scanning Sequence

## **Ordering Information**

| Part Number                      | Evaluation Circuit (Current Amplifier) | Adjacent Defects<br>Forming a Group |

|----------------------------------|----------------------------------------|-------------------------------------|

| RA0256BAQ-011<br>(1-12 defects)  | RC0503ANC-011                          | up to 2                             |

| RA0256BAQ-020<br>(13-50 defects) | RC0503ANC-011                          | up to 4                             |

055-0081 March 1992

© 1992 EG&G RETICON. Contents may not be reproduced in whole or in part without the written consent of EG&G RETICON. Specifications are subject to change without notice. Printed in U.S.A. Information furnished herein is believed to be accurate and reliable. However, no responsibility is assumed by EG&G RETICON for its use, nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of EG&G RETICON.