# HD44105

# (Dot Matrix Liquid Crystal Graphic Display Common Driver)

### Description

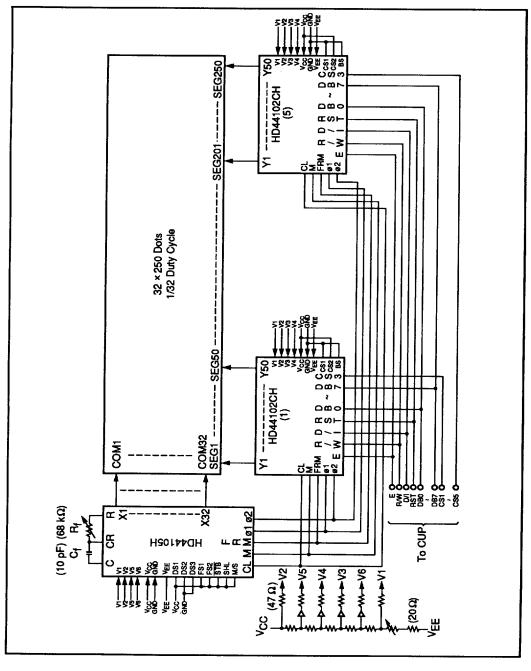

The HD44105H is a common signal driver for LCD dot matrix graphic display systems. It generates the timing signals required for display with its internal oscillator and supplies them to the column driver (HD44102H) to control display, also automatically scanning the common signals of the liquid crystal according to the display duty cycle. It can select 7 types of display duty cycle 1/8, 1/12, 1/16, 1/24,1/32, 1/48, and 1/64. It provides 32 driver output lines and the impedance is low (1 k $\Omega$  max) enough to drive a large screen.

#### **Features**

- Dot matrix graphic display common driver including the timing generation circuit

- Internal oscillator (Oscillation frequency is selectable by attaching an oscillation resistor and an oscillation capacitor)

- · Generates display timing signals

- 32-bit bidirectional shift register for generating common signals

- 32 liquid crystal driver circuits with low impedance

- Selectable display duty ratio: 1/8, 1/12, 1/16, 1/24, 1/32, 1/48, 1/64

- Low power dissipation

- Power supplies:

$V_{CC} = +5 V \pm 10\%$

$V_{EE} = 0 \text{ to } -5.5 \text{ V}$

CMOS process

### **Ordering Information**

| Type No. | Package                   |  |  |  |  |

|----------|---------------------------|--|--|--|--|

| HD44105H | 60-pin plastic QFP(FP-60) |  |  |  |  |

| HD44105D | Chip                      |  |  |  |  |

|          |                           |  |  |  |  |

# Absolute Maximum Rating (Ta =25°C)

| Item                  | Symbol          | Ratings                                       | Unit | Note                                  |

|-----------------------|-----------------|-----------------------------------------------|------|---------------------------------------|

| Supply voltage (1)    | V <sub>cc</sub> | -0.3 to +7.0                                  | V    | 1                                     |

| Supply voltage (2)    | V <sub>EE</sub> | V <sub>CC</sub> -13.5 to V <sub>CC</sub> +0.3 | V    | · · · · · · · · · · · · · · · · · · · |

| Terminal voltage (1)  | V <sub>T1</sub> | -0.3 to V <sub>CC</sub> +0.3                  | V    | 1, 2                                  |

| Terminal voltage (2)  | V <sub>T2</sub> | V <sub>EE</sub> -0.3 to V <sub>CC</sub> +0.3  | V    | 3                                     |

| Operating temperature | Topr            | -20 to +75                                    | °C   |                                       |

| Storage temperature   | Tstg            | -55 to +125                                   | °C   |                                       |

Notes: 1. Referred to GND = 0 V.

2. Applied to input terminals (except for V1, V2, V5, and V6) and I/O common terminals.

3. Applied to terminals V1, V2, V5, and V6. Connect a protection resistor of 47  $\Omega$  ± 10% to each terminal in series.

#### HITACHI

4496204 **00463**15 **7**99 ■

519

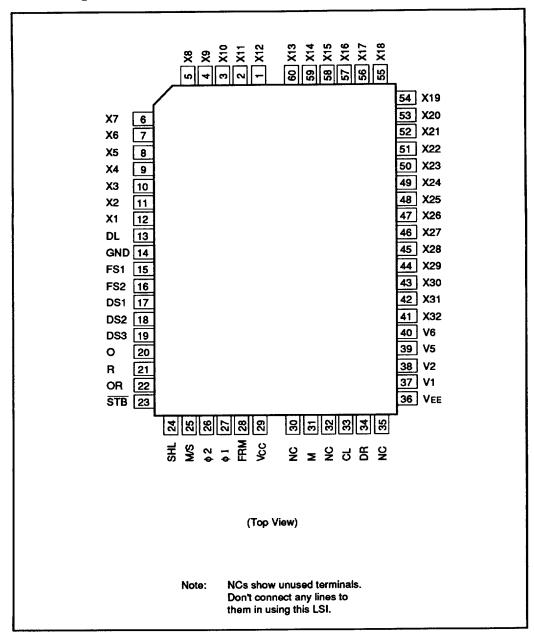

### Pin Arrangement

**HITACHI**

• 4496204 0046316 625 **=**

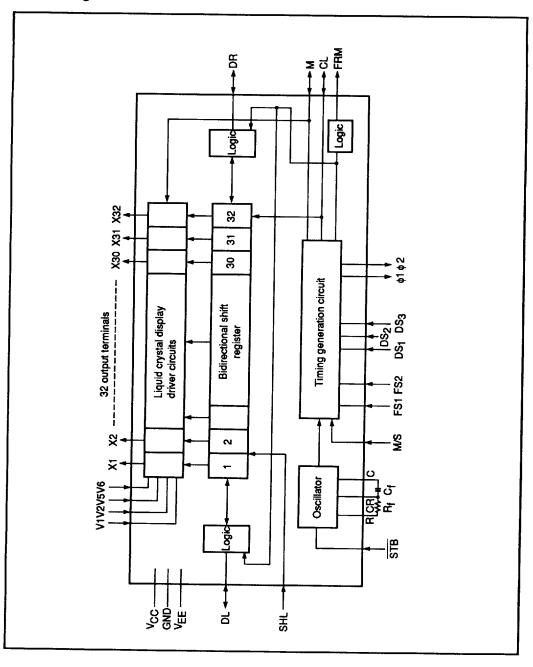

# **Block Diagram**

HITACHI

4496204 0046317 561 **=**

521

#### HD44105

# Electrical Characteristics (Note 4) $(V_{CC}=+5~V\pm10\%,~GND=0~V,~V_{EE}=0~to~-5.5~V,~Ta=-20~to~+75^{\circ}C)$

| item                               | Symbol           | Min                   | Тур | Max                   | Unit | Test Condition                                          | Note |

|------------------------------------|------------------|-----------------------|-----|-----------------------|------|---------------------------------------------------------|------|

| Input high voltage                 | VIH              | 0.7 × V <sub>CC</sub> | _   | V <sub>CC</sub>       | ٧    |                                                         | 5    |

| Input low voltage                  | V <sub>IL</sub>  | 0                     | _   | 0.3 × V <sub>CC</sub> | ٧    |                                                         | 5    |

| Output high voltage                | V <sub>OH</sub>  | V <sub>CC</sub> -0.4  | _   | _                     | ٧    | i <sub>OH</sub> = -400 μA                               | 6    |

| Output low voltage                 | Val              | _                     | _   | 0.4                   | ٧    | l <sub>OL</sub> = 400 μA                                | 6    |

| Vi-Xj On resistance                | Ron              | _                     |     | 1000                  | Ω    | V <sub>EE</sub> = -5 V ± 10%,<br>Load current<br>±15 μA |      |

| Input leakage current (1)          | I <sub>IL1</sub> | -1                    |     | 1                     | μА   | V <sub>IN</sub> = V <sub>CC</sub> to GND                | 7    |

| Input leakage current (2)          | l <sub>IL2</sub> | <b>-</b> 5            | _   | 5                     | μΑ   | VIN = VCC to VEE                                        | 8    |

| Shift frequency                    | F <sub>SFT</sub> |                       |     | 50                    | kHz  | în slave mode                                           | 9    |

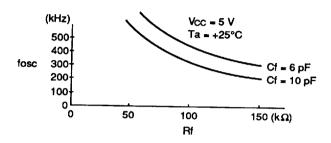

| Oscillation frequency              | fosc             | 300                   | 430 | 560                   | kHz  | Rf = 68 k $\Omega \pm 2\%$ ,<br>Cf = 10 pF ± 5%         | 10   |

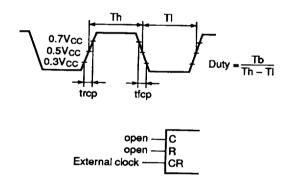

| External clock operating frequency | fcP              | 50                    | _   | 560                   | kHz  |                                                         | 11   |

| External clock duty cycle          | Duty             | 45                    | 50  | 55                    | %    |                                                         | 11   |

| External clock rise time           | trce             |                       |     | 50                    | ns   |                                                         | 11   |

| External clock fall time           | tfCP             |                       |     | 50                    | ns   |                                                         | 11   |

| Dissipation power (Master)         | P <sub>W1</sub>  |                       |     | 4.4                   | mW   | CR oscillation,<br>430 kHz                              | 12   |

| Dissipation power (Slave)          | P <sub>W2</sub>  | _                     | _   | 1.1                   | mW   | Frame 70 kHz                                            | 13   |

Notes: 4. Specified within this range unless otherwise noted.

- 5. Applied to CR, FS1, FS2, DS1 to DS3, M, SHL, M/S, CL, DR, DL, and STB.

- 6. Applied to DL, DR, M, FRM, CL, φ1, and φ2.

- Applied to input terminals CR, FS1, FS2, DS1 to DS3, SHL, M/S, and STB and I/O common terminals DL, DR, M, and CL at high impedance.

- 8. Applied to V1, V2, V5, and V6.

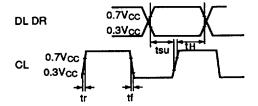

- 9. Shift operation timing.

|     | Min | Тур | Max | Unit |

|-----|-----|-----|-----|------|

| tsu | 5   | -   | -   | µs   |

| tH  | 5   | _   | -   | μs   |

| tr  | _   | _   | 100 | ns   |

| tf  | _   | _   | 100 | ns   |

**HITACHI**

522

M 4436504 0046378 418

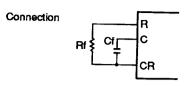

# Notes: 10. Relation between oscillation frequency and Rf, Cf.

The values of Rf and Cf are typical values. The oscillation frequency varies with the mounting condition. Adjust oscillation frequency to a required value.

11.

- 12. Measured by Vcc terminal at output non-load of Rf = 68 k $\Omega$  ± 2% and Cf = 10 pF ± 5%, and 1/32 duty cycle in the master mode. Input terminals are connected to Vcc or GND.

- Measured by Vcc terminal at output non-load, 1/32 duty cycle, and frame frequency of 70 Hz in the slave mode. Input terminals are connected to Vcc or GND.

**HITACHI**

523

4496204 0046319 334 **=**

# HD44105

# Pin Description

| Pin Name                                                                                             | Pin Number | 1/0 | Function                       |          |                   |                  |                 |          |                     |             |      |

|------------------------------------------------------------------------------------------------------|------------|-----|--------------------------------|----------|-------------------|------------------|-----------------|----------|---------------------|-------------|------|

| X1-X32                                                                                               | 32         | 0   | Liquid crystal<br>Relation amo | display  | driver out level, | utput.<br>M, and | data (D         | ) in s   | hift regi           | ster.       |      |

|                                                                                                      |            |     |                                | М        |                   | 1                |                 |          | 0                   |             |      |

|                                                                                                      |            |     |                                | D        | 1                 | $\neg$           | 。 Г             | 1        | $\neg$              | ь           |      |

|                                                                                                      |            |     |                                |          |                   |                  |                 |          | 1 1                 | <del></del> |      |

|                                                                                                      |            |     | Outpu                          | t level  | V2                | <del>- - '</del> | <del>/6</del> → | <u> </u> | + <u>'</u>          | 5           |      |

| CR, R, C                                                                                             | 3          |     | P.                             | cr<br>CR | c                 | R Oscill         | _               |          |                     |             |      |

| М                                                                                                    | 1          | 1/0 | Signal for cor                 | verting  | liquid c          | rystal di        | splay d         | river    | signal i            | nto AC.     |      |

|                                                                                                      |            |     | Master:<br>Slave:              |          | ut termina        |                  |                 |          |                     |             |      |

| CL.                                                                                                  | 1          | 1/0 | Shift register                 | shift cl | ock.              |                  |                 |          |                     |             |      |

|                                                                                                      |            |     | Master:                        |          | ut termi          |                  |                 |          |                     |             |      |

|                                                                                                      |            |     | Slave:                         |          | t termina         |                  |                 |          |                     |             |      |

| FRM                                                                                                  | 1          | 0   | Frame signal                   |          |                   | ronous           | signal.         |          |                     |             |      |

| DS1-DS3                                                                                              | 3          | ١   | Display duty                   |          | elect.            |                  |                 |          |                     |             |      |

|                                                                                                      |            |     | Display Duty<br>Ratio          | 1/8      | 1/16              | 1/32             | 1/64            | _        | 1/12                | 1/24        | 1/48 |

|                                                                                                      |            |     | DS1                            | L        | L                 | Н                | Н               | L        | L                   | Н           | Н    |

|                                                                                                      |            |     | DS2                            | L        | Н                 | L                | Н               | L        | <u>H</u>            | L           | Н    |

|                                                                                                      |            |     | DS3                            | L_       | <u>L</u>          | L                | <u> </u>        | <u>H</u> | Н                   | <u>H</u>    | Н    |

| FS1-FS2                                                                                              | 2          | 1   | Selects frequency              | -        |                   |                  |                 |          |                     |             |      |

| The relation between the frame frequency fram and the osci frequency fosc is as follows:             |            |     |                                |          |                   | oscillati        | on              |          |                     |             |      |

|                                                                                                      |            |     | FS1 FS2                        | fo       | sc(kHz)           | fF               | RM(Hz)          |          | f <sub>M</sub> (Hz) | fcp(        | kHz) |

|                                                                                                      |            |     | L L                            | 10       | 7.5               | 70               | )               |          | 35                  | 53.8        | 3    |

|                                                                                                      |            |     | H L                            | 10       | 7.5               | 70               | )               |          | 35                  | 53.8        | 3    |

|                                                                                                      |            |     | L H                            | 21       | 5.0               | 70               | )               |          | 35                  | 107         | .5   |

|                                                                                                      |            |     | н н                            | 43       | 0.0               | 70               | )               |          | 35                  | 215         | .0   |

| fosc: Oscillation frequency fram: Frame frequency fm: M signal frequency fcp: Frequencies of \$1 and |            |     |                                |          |                   | ·                |                 |          |                     |             |      |

HITACHI

4496204 0046320 OS6 **==**

# Pin Description (cont)

| Pin Nam               | e Pin Nur | nber I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------------|-----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| STB                   | 1         | ī        | Input terminal for testing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|                       |           |          | Connect this terminal to Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| DL, DR                | 2         | 1/0      | Data I/O terminals of bidirectional shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| SHL                   | 1         | 1        | Selects shift direction of bidirectional shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                       |           |          | SHL Shift Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                       |           |          | H DL→DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                       | ·         |          | L DL←DR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| M/S                   | 1         | 1        | Selects Master/Slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                       |           |          | M/S = High: Master mode<br>The oscillator and timing generation circuit operate to supply<br>display timing signals to the display system. Each of I/O common<br>terminals, DL, DR, M, and CL is in the output state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                       |           |          | M/S = Low: Slave mode  The timing generation circuit stop operating. The oscillator is not required. Connect terminal CR to Vcc. Open terminals C and R. One (determined by SHL) of DL and DR, and terminals M and CL are in the input state. Connect M, CL and one of DL and DR of the master to the respective terminals. Connect FS1, FS2, DS1, DS2, DS3, STB to Vcc. When display duty ratio is 1/8, 1/12, 1/16, 1/24, 1/32, one HD44105H is required. Use it in the master mode. When display duty ratio is 1/48, 1/64, two HD44105Hs are required. Use one in the master mode to drive common signals 1 to 32, and another in the slave mode to drive common signals 33 to 48(64). |  |  |  |  |  |

| φ1, φ2                | 2         | 0        | Operating clock output terminals for HD44102CH. The frequencies of ¢1 and ¢2 are half of oscillation frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| V1, V2,               | 4         |          | Liquid crystal display driver level power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| V5, V6                |           |          | V1 and V2: Selected level V5 and V6: Non-selected level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| V <sub>CC</sub> , GND | 3         | -        | Power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| V <sub>EE</sub>       |           |          | Vcc – GND: Power supply for internal logic Vcc – VEE: Power supply for driver circuit logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

HITACHI

#### **Block Functions**

#### Oscillator

A CR oscillator attached to an oscillation resistor Rf and an oscillation capacitor Cf. The oscillation frequency v aries with the values of Rf and Cf and the mounting conditions. Refer to electrical characteristics (note 10) to make proper adjustment.

#### **Timing Generation Circuit**

This circuit divides the signals from the oscillator and generates display timing signals (M, CL, and FRM) and operating clock ( $\phi$ 1 and  $\phi$ 2) for HD44102CH according to the display duty ratio set by DS1 to DS3. In the slave mode, this block stops operating. It is meaningless to set FS1, FS2 and DS1 to DS3. However, connect them to  $V_{CC}$  to prevent floating current.

#### Bidirectional Shift Register

A 32-bit bidirectional shift register. The shift direction is determined by the SHL. The data input from DL or DR performs a shift operation at the rise of shift clock CL.

#### Liquid Crystal Display Driver Circuit

Each of 32 driver circuits is a multiplex circuit composed of four CMOS switches. The combination of the data from the shift register with the M signal allows one of the four liquid crystal display driver levels V1, V2, V5, and V6 to be transferred to the output terminals.

HITACHI

526

4496204 0046322 929

# Connection between HD44105H and HD44102CH

**HITACHI**

527

4496204 0046323 **8**65 **...**