# UV ERASABLE 8192-BIT READ ONLY MEMORY

September 1978

5-32

ORIG

002500

T-2500

FUT

# OBSOLTE

# MOS 8192-BIT UV ERASABLE AND ELECTRICALLY PROGRAMMABLE READ ONLY MEMORY

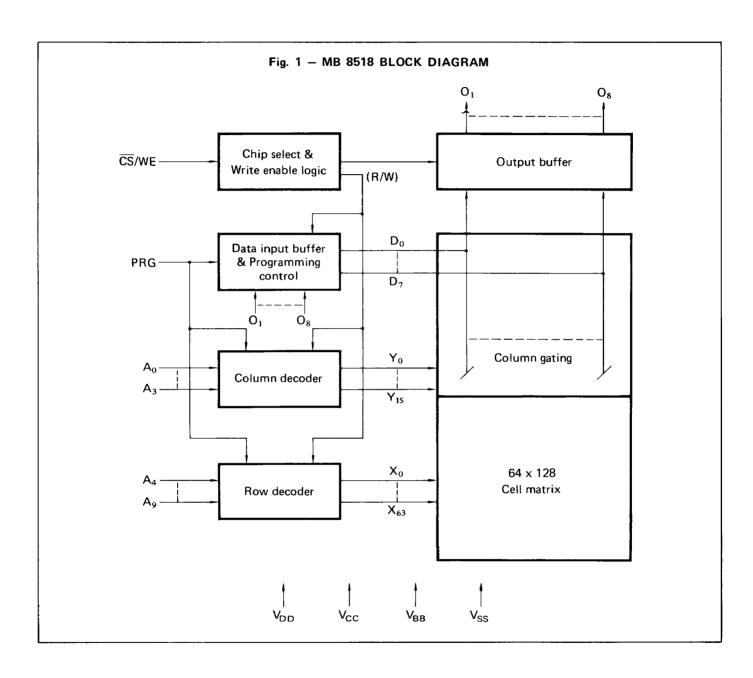

The Fujitsu MB 8518 is a high speed 8192-bit static N-channel MOS erasable and electrically programmable read only memory (EPROM). It is especially well suited for applications where rapid turn-around and/or bit pattern experimentation are important.

A 24-pin dual-in-line package with a transparent lid is used to package the MB 8518. The transparent lid allows the user to expose the device to ultraviolet light in order to erase the memory bit pattern previously programmed. At the completion of erasure, a new pattern can then be written into the memory.

The MB 8518 is fabricated using N-channel double polysilicon gate

technology with single transistor stacked gate cells. A pin-for-pin equivalent mask programmed ROM, the Fujitsu MB 8308, is available for large volume requirements.

- 1024 words by 8 bits organization, fully decoded

- Fast programming (typ. 100 sec. for all 8192 bits)

- Low power requirement (only one high-level pulse required)

- No clocks required (fully static operation)

- TTL compatible inputs and outputs

- Three-state outputs with OR-tie capability

- Chip Select (CS) lead for simplified memory expansion

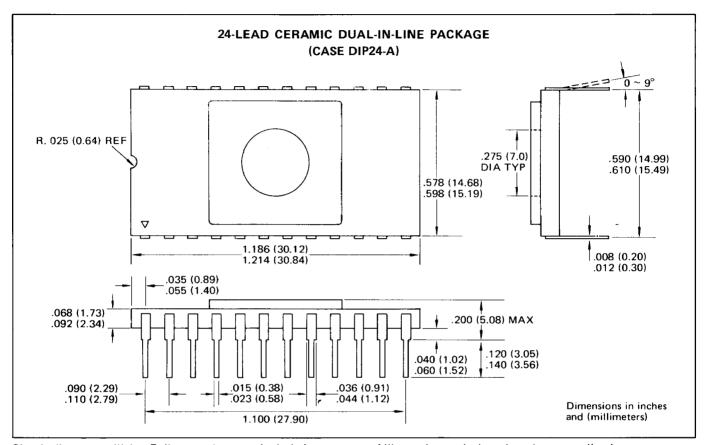

CASE DIP24-A

CERAMIC PACKAGE

- Standard (+12V and ±5V) power supplies

- Standard 24-pin DIP package

- Interchangeable with Intel 2708

#### **ABSOLUTE MAXIMUM RATINGS (See Note)**

| Rating                                                              | Symbol                             | Value       | Unit |

|---------------------------------------------------------------------|------------------------------------|-------------|------|

| Temperature Under Bias                                              | TA                                 | -25 to + 85 | °c   |

| Storage Temperature                                                 | T <sub>stg</sub>                   | -65 to +125 | °c   |

| Inputs/Outputs (Except PRG and CS/WE) with Respect to VBB           | V <sub>IN1</sub> ,V <sub>OUT</sub> | -0.3 to +15 | V    |

| Program Input with Respect to V <sub>BB</sub>                       | V <sub>P</sub>                     | -0.3 to +35 | V    |

| CS/WE with Respect to V <sub>BB</sub>                               | V <sub>IN2</sub>                   | -0.3 to +20 | V    |

| V <sub>CC</sub> and V <sub>SS</sub> with Respect to V <sub>BB</sub> | V <sub>CC</sub> ,V <sub>SS</sub>   | -0.3 to +15 | ٧    |

| V <sub>DD</sub> with Respect to V <sub>BB</sub>                     | v <sub>DD</sub>                    | -0.3 to +20 | ٧    |

| Power Dissipation                                                   | PD                                 | 1.5         | w    |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet.

#### PIN ASSIGNMENT

| A <sub>7</sub> ☐ 1  | 0 | 24 □ V <sub>CC</sub> |

|---------------------|---|----------------------|

| A <sub>6</sub> 🗖 2  |   | 23 🗖 A <sub>8</sub>  |

| $A_5 \square 3$     |   | 22 🗖 A9              |

| A4 ☐ 4              |   | 21 V <sub>BB</sub>   |

| A₃ <b>□</b> 5       |   | 20 CS/WE             |

| A2 <b>□</b> 6       |   | 19 \ \v_DD           |

| A <sub>1</sub> 7    |   | 18 PRG               |

| A₀ <b></b>          |   | 17 🗖 🔾 8             |

| 0₁៨9                |   | 16 🗖 O <sub>7</sub>  |

| O <sub>2</sub> 10   |   | 15 <b>0</b> 6        |

| 03 🗖 11             |   | 14 □0₅               |

| V <sub>SS</sub> □12 |   | 13 🗖 04              |

|                     |   |                      |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this highimpedance circuit.

# **FUNCTIONS AND PIN CONNECTIONS**

| Function<br>(Pin No.)<br>Mode |                 | Data I/O<br>(9~11,13~17) | V <sub>SS</sub><br>(GND)<br>(12) | PRG<br>(Program)<br>(18) | V <sub>DD</sub><br>Supply<br>(19) | CS/WE<br>(20)    | V <sub>BB</sub><br>Supply<br>(21) | V <sub>CC</sub><br>Supply<br>(24) |

|-------------------------------|-----------------|--------------------------|----------------------------------|--------------------------|-----------------------------------|------------------|-----------------------------------|-----------------------------------|

| Read                          | A <sub>IN</sub> | D <sub>out</sub>         | GND                              | GND                      | +12V                              | VIL              | -5V                               | +5V                               |

| Deselect                      | DON'T CARE      | HIGH Z                   | GND                              | GND                      | +12V                              | V <sub>IH</sub>  | -5V                               | +5V                               |

| Program                       | A <sub>IN</sub> | D <sub>IN</sub>          | GND                              | PULSED<br>+26V           | +12V                              | V <sub>IHW</sub> | -5V                               | +5V                               |

### RECOMMENDED OPERATING CONDITIONS (Referenced to $V_{SS}$ )

| Parameter          | Symbol          | Min             | Тур   | Max                | Unit | Operating<br>Temperature |

|--------------------|-----------------|-----------------|-------|--------------------|------|--------------------------|

| Supply Voltage     | V <sub>DD</sub> | 11.4            | 12    | 12.6               | ٧    | <del></del>              |

| Supply Voltage     | v <sub>cc</sub> | 4.75            | 5.0   | 5.25               | ٧    |                          |

| Supply Voltage     | V <sub>SS</sub> | _               | 0.0   |                    | V    | 0°C to +70°C             |

| Supply Voltage     | V <sub>BB</sub> | - 4.75          | - 5.0 | - 5.25             | ٧    |                          |

| Input High Voltage | V <sub>IH</sub> | 3.0             | _     | V <sub>CC</sub> +1 | ٧    |                          |

| Input Low Voltage  | V <sub>IL</sub> | V <sub>SS</sub> | _     | 0.65               | V    |                          |

STATIC CHARACTERISTICS (Recommended operating conditions unless otherwise noted, and pin 18 PRG must be tied to V<sub>SS</sub> during read operation.)

| Parameter                                                                                          | Symbol            | Min         | Тур | Max  | Unit |

|----------------------------------------------------------------------------------------------------|-------------------|-------------|-----|------|------|

| Address and Chip Select Input Load Current (V <sub>IN</sub> =5.25V)                                | I <sub>L1</sub>   |             |     | 10   | μΑ   |

| Output Leakage Current (V <sub>OUT</sub> =5.25V, CS/WE=5V)                                         | I <sub>LO</sub>   |             |     | 10   | μΑ   |

| V <sub>DD</sub> Supply Current (All Inputs=V <sub>IH</sub> , $\overline{\text{CS}}$ /WE=5V)        | I <sub>DD</sub> * | <del></del> | 50  | 65   | mA   |

| V <sub>CC</sub> Supply Current (All Inputs=V <sub>IL</sub> , $\overline{CS}$ /WE=5V)               | Icc*              |             | 7   | 10   | mA   |

| V <sub>BB</sub> Supply Current (All Inputs=V <sub>IH</sub> , $\overline{\text{CS}}/\text{WE=5V}$ ) | I <sub>BB</sub> * |             | 30  | 45   | mA   |

| Output Low Voltage (I <sub>OL</sub> =1.6mA)                                                        | V <sub>OL</sub>   |             |     | 0.45 | ٧    |

| Output High Voltage (I <sub>OH</sub> =-100μA)                                                      | V <sub>OH1</sub>  | 3.7         |     |      | ٧    |

| Output High Voltage (I <sub>OH</sub> =-1mA)                                                        | V <sub>OH2</sub>  | 2.4         |     |      | ٧    |

| Power Dissipation (T <sub>A</sub> =70°C)                                                           | P <sub>D</sub>    | _           |     | 800  | mW   |

<sup>\*</sup>Note: Typical values are measured at nominal voltage and  $T_A = 25^{\circ}C$ ; max. values at  $T_A = 0^{\circ}C$ .

# **CAPACITANCE** (T<sub>A</sub>=25°C; f=1MHz)

| Parameter                                 | Symbol           | Min | Тур | Max | Unit |

|-------------------------------------------|------------------|-----|-----|-----|------|

| Input Capacitance (V <sub>IN</sub> =0V)   | C <sub>IN</sub>  | _   | 4   | 6   | pF   |

| Output Capacitance (V <sub>OUT</sub> =0V) | C <sub>OUT</sub> | -   | 8   | 12  | pF   |

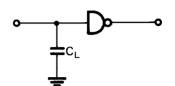

Fig. 2 - DYNAMIC TEST CONDITIONS

Input Pulse Levels:

0.65V to 3.0V

Input Rise and Fall Time:

**≦**20ns

Timing Measurement Reference Levels: 0.8V and 2.8V for inputs

0.8V and 2.4V for outputs

Output Load:

1 TTL gate and C<sub>L</sub>=100pF

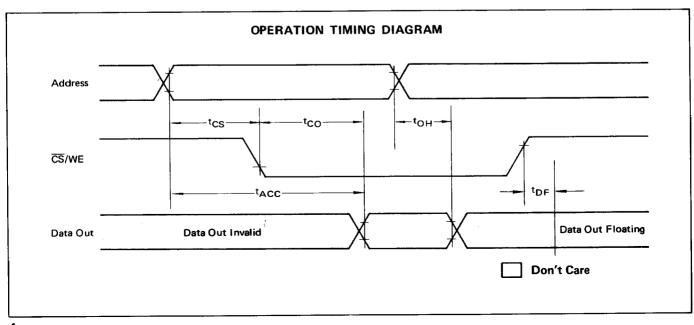

### **DYNAMIC CHARACTERISTICS**

(Recommended operating conditions unless otherwise noted

| Parameter                     | Symbol            | Min | Тур | Max | Unit |

|-------------------------------|-------------------|-----|-----|-----|------|

| Address to Output Delay       | <sup>t</sup> ACC  | _   | _   | 450 | ns   |

| Chip Select to Output Delay   | t <sub>CO</sub>   | -   | _   | 120 | ns   |

| Chip Deselect to Output Float | t <sub>DF</sub>   | 0   |     | 120 | ns   |

| Address to Output Hold        | <sup>t</sup> OH   | 0   | _   | _   | ns   |

| Chip Select Delay             | t <sub>CS</sub> * | _   | _   | 330 | ns   |

<sup>\*</sup>Note:  $t_{ACC}$ = $t_{CS}$  +  $t_{CO}$  at  $t_{CS}$  > 330ns, and  $t_{ACC}$ =450ns (max.) at  $t_{CS}$   $\leqq$  330ns.

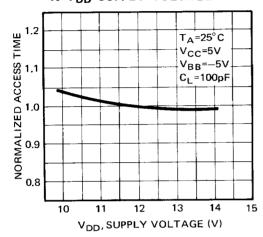

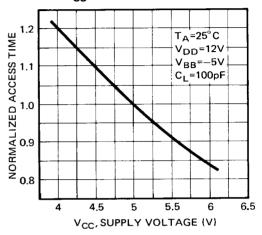

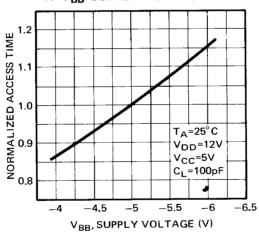

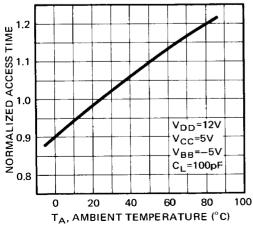

### TYPICAL CHARACTERISTICS CURVES

Fig. 3 - NORMALIZED ACCESS TIME vs V<sub>DD</sub> SUPPLY VOLTAGE

Fig. 4 — NORMALIZED ACCESS TIME vs  $V_{CC}$  SUPPLY VOLTAGE

Fig. 5 - NORMALIZED ACCESS TIME vs  $V_{BB}$  SUPPLY VOLTAGE

Fig. 6 — NORMALIZED ACCESS TIME vs AMBIENT TEMPERATURE

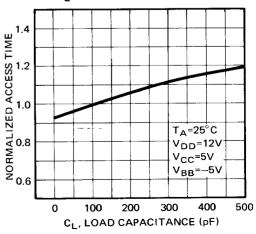

Fig. 7 — NORMALIZED ACCESS TIME vs  $C_L$  LOAD CAPACITANCE

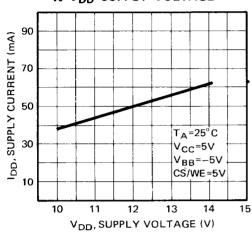

Fig. 8 - I<sub>DD</sub> SUPPLY CURRENT vs V<sub>DD</sub> SUPPLY VOLTAGE

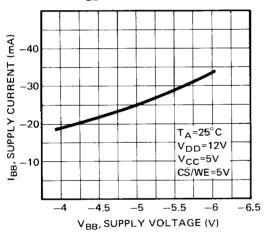

Fig. 10 - I<sub>BB</sub> SUPPLY CURRENT vs V<sub>BB</sub> SUPPLY VOLTAGE

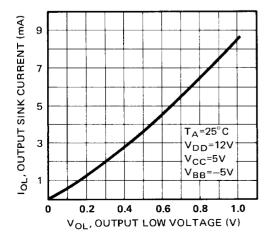

Fig. 12  $-I_{OL}$  OUTPUT SINK CURRENT vs  $V_{OL}$  OUTPUT LOW VOLTAGE

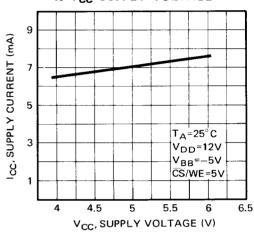

Fig. 9 - I<sub>CC</sub> SUPPLY CURRENT vs V<sub>CC</sub> SUPPLY VOLTAGE

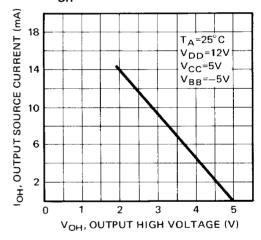

Fig. 11 — I<sub>OH</sub> OUTPUT SOURCE CURRENT vs V<sub>OH</sub> OUTPUT HIGH VOLTAGE

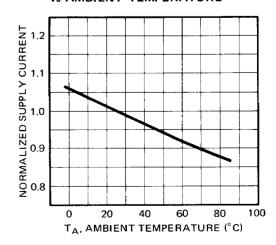

Fig. 13 — NORMALIZED SUPPLY CURRENT VS AMBIENT TEMPERATURE

### PROGRAMMING/ERASING INFORMATION

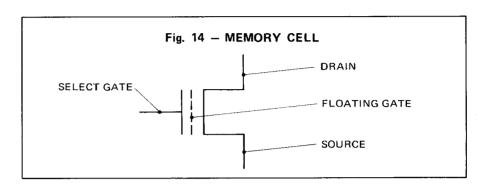

#### MEMORY CELL DESCRIPTION

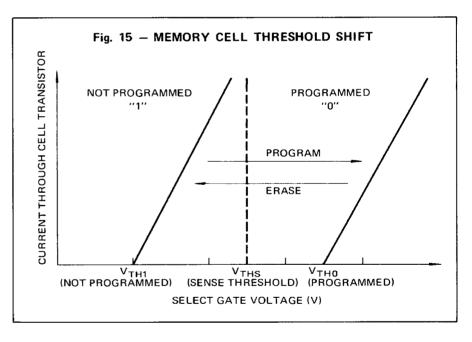

The MB 8518 is fabricated using a single-transistor stacked gate cell construction, implemented via doublelayer polysilicon technology. The individual cells consist of a bottom floating gate and a top select gate (see Fig. 14). The top gate is connected to the row decoder, while the floating gate is used for charge storage. The cell is programmed by the injection of high energy electrons through the oxide and onto the floating gate. The presence of the charge on the floating gate causes a shift in the cell threshold (refer to Fig. 15). In the initial state, the cell has a low threshold (V<sub>TH1</sub>) which will enable the transistor to be turned on when the cell is selected (via the top select gate). Programming shifts the threshold to a higher level (V<sub>THO</sub>), thus preventing the cell transistor from turning on when selected. The status of the cell (i.e., whether programmed or not) can be determined by examining its state at the sense threshold (V<sub>THS</sub>), as indicated by the dotted line in Fig. 15.

#### **PROGRAMMING**

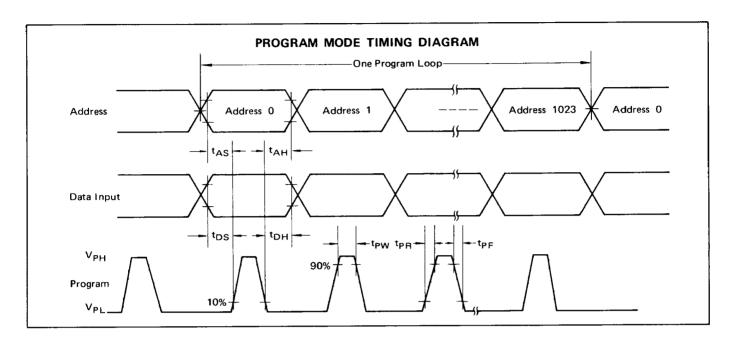

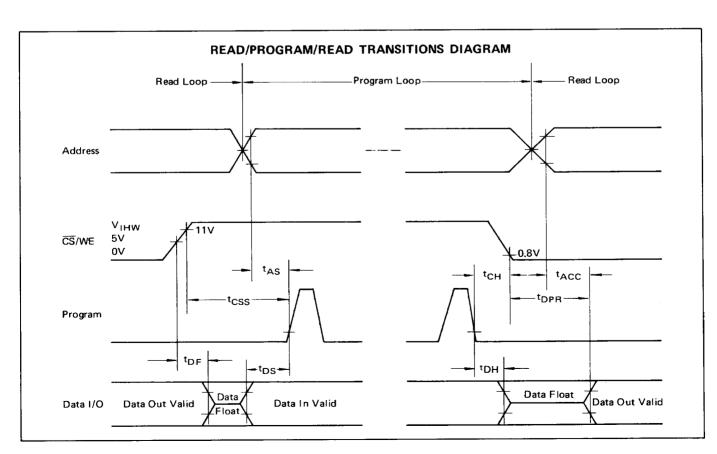

Initially, and after each erasure, all bits are in the "1" (output high) state. Information is stored by programming a "0" into each desired bit location. Address and supply voltage (VDD, V<sub>CC</sub>, V<sub>BB</sub> and V<sub>SS</sub>) input levels used in the read mode of operation are also applicable in the programming mode. For programming operation, the circuit is set up by applying +12V to the CS/WE lead (pin 20). The word address is then selected in the same manner as in the read mode, with data to be programmed applied 8 bits in parallel to the data lines  $(O_1 \sim O_8)$ . After address and data set up, one program pulse (VP) per address is applied to the Program input (pin 18). One pass through all addresses to be programmed is defined as a program loop. The number of loops required (N) is a function of the program pulse

width  $(t_{PW})$  according to the formula N x  $t_{PW} \ge 100$  msec. For programming verification, program loops and read loops may be alternated as shown in "Read/Program/Read Transitions Diagram."

During programming, the selected row and column lines are pulsed to approximately 22 volts, and the floating gate is charged (as described previously). It is the presence of these 22V pulses on the interconnected gates that leads to the requirement that all addresses must be programmed sequentially; programming of single words or small blocks of words is not allowed, as transients

may be generated that could partially alter the charge state of cells not being programmed.

#### **ERASING**

The MB 8518 can be erased by exposure to high-intensity, shortwave ultraviolet light at a wavelength of 2537Å. The recommended integrated dosage (UV intensity x exposure time) is 10Wsec./cm². Normally, commercial ultraviolet lamps should be used without shortwave filters, with the device to be erased placed one inch (2 to 3cm) away from the lamp tube. It is suggested that a guard band of 3~4 times the (cont.)

# PROGRAMMING/ERASING INFORMATION (continued)

minimum required period for erasure be used, the minimum period being the time which appears to erase all bits. The guard band will ensure erasure at temperature and voltage extremes. Typical guard band erase times for various UV source power ratings are: typically 10 minutes for  $12,000\mu W/cm^2$ ; typically 30 minutes for  $6,000\mu W/cm^2$ .

#### SUPPLEMENTARY INFORMATION

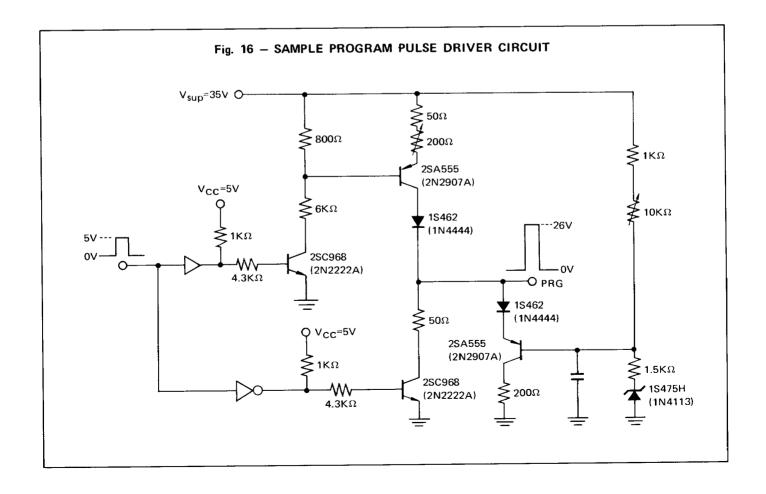

Programming can be performed in accordance with the procedure described in "Programming." A recommended circuit for programming pulse generation is shown in Fig. 16. The program pulse high voltage (V<sub>PH</sub>) source must sink more than 20mA, and the program

pulse low voltage (V<sub>PL</sub>) source should drive more than 8mA.

The width of the program pulse can vary anywhere from 0.1 to 1.0 msec. The number of loops (N) can vary from a minimum of 100 ( $t_{PW}$ =1.0 msec.) to a maximum of more than 1,000 ( $t_{PW}$ =0.1 msec.), depending on the value selected for  $t_{PW}$ . Remember, however, there must be "N" successive loops through all 1024 addresses. It is incorrect to apply "N" program pulses to one address, change to the next address, and again apply "N" program pulses.

With reference to the timing diagram, optimum or more efficient program-

ming is achieved when:

$t_{CSS}^- = t_{AS} = t_{DS} = 10 \ \mu sec.$

$t_{PW} = 1.0$  msec.

$t_{AH} = t_{DH} = 1.0 \mu sec.$

$t_{PR} = t_{PF} = 0.5 \mu sec.$

Thus the time for one address is:

$t_{AS} + t_{PR} + t_{PW} + t_{PF} + t_{AH} =$ 1.012 msec.

For 100 loops and 1024 addresses, the total time to program an entire device will be:

1.012 msec./address x 100 loops x 1024 addresses = 103.6 sec.

Note that the program pulse duty cycle is approximately 99%. Regardless of the length of the program pulse, the requirement for making successive passes through all addresses cannot be eliminated.

## STATIC SPECIFICATIONS (T<sub>A</sub> =25 $^{\circ}$ C, V<sub>DD</sub>=12V±5%, V<sub>CC</sub>=5V±5%, V<sub>SS</sub>=0V, V<sub>BB</sub>=-5V±5%)

| Parameter                                                                                                               | Symbol                              | Min             | Тур | Max                | Unit |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|-----|--------------------|------|

| Input High Voltage for Address and Data                                                                                 | V <sub>IH</sub>                     | 3.0             |     | V <sub>CC</sub> +1 | V    |

| Input Low Voltage for Address and Data                                                                                  | VIL                                 | V <sub>SS</sub> |     | 0.65               | V    |

| Address and Data Input Load Current (V <sub>IN</sub> =5.25V, CS/WE=11.4V)                                               | I <sub>LIA</sub> , I <sub>LID</sub> |                 |     | 10                 | μΑ   |

| CS/WE Input Load Current (CS/WE=12.6V)                                                                                  | ILIW                                |                 |     | 10                 | μΑ   |

| CS/WE Input High Voltage                                                                                                | V <sub>IHW</sub>                    | 11.4            |     | 12.6               | ٧    |

| V <sub>DD</sub> Supply Current<br>(All Inputs=V <sub>IH</sub> , PRG=V <sub>PL</sub> , $\overline{\text{CS}}$ /WE=11.4V) | I <sub>DDW</sub>                    |                 |     | 78                 | mA   |

| V <sub>CC</sub> Supply Current (All Inputs=V <sub>IL</sub> , $\overline{\text{CS}}/\text{WE}=11.4\text{V}$ )            | Iccw                                |                 |     | 12                 | mA   |

| V <sub>BB</sub> Supply Current (All Inputs=V <sub>IH</sub> , $\overline{\text{CS}}/\text{WE}=11.4\text{V}$ )            | I <sub>BBW</sub>                    |                 |     | 50                 | mA   |

| Program Pulse Source Current                                                                                            | I <sub>PL</sub>                     |                 | _   | 8                  | mA   |

| Program Pulse Sink Current                                                                                              | I <sub>PH</sub>                     |                 |     | 20                 | mA   |

| Program Pulse Low Voltage                                                                                               | V <sub>PL</sub>                     | V <sub>SS</sub> |     | 1                  | ٧    |

| Program Pulse High Voltage                                                                                              | V <sub>PH</sub>                     |                 |     | 27                 | ٧    |

| Program Pulse Height                                                                                                    |                                     | 25              |     | 27                 | V    |

# DYNAMIC SPECIFICATIONS ( $T_A=25^{\circ}C$ )

| Parameter                           | Symbol           | Min | Тур | Max | Unit |

|-------------------------------------|------------------|-----|-----|-----|------|

| Address Set Up Time                 | t <sub>AS</sub>  | 10  | _   |     | μς   |

| CS/WE Set Up Time                   | t <sub>css</sub> | 10  |     |     | μs   |

| Data Set Up Time                    | t <sub>DS</sub>  | 10  |     |     | μs   |

| Address Hold Time                   | t <sub>AH</sub>  |     |     | -   | μs   |

| CS/WE Hold Time                     | t <sub>сн</sub>  | 0.5 |     |     | μς   |

| Data Hold Time                      | t <sub>DH</sub>  | 1   |     |     | μs   |

| Chip Deselect to Output Float Delay | t <sub>DF</sub>  | 0   |     | 120 | ns   |

| Program to Read Delay               | t <sub>DPR</sub> |     |     | 10  | μs   |

| Program Pulse Width                 | t <sub>PW</sub>  | 0.1 |     | 1.0 | ms   |

| Program Pulse Rise Time             | t <sub>PR</sub>  | 0.5 | _   | 2.0 | μs   |

| Program Pulse Fall Time             | tpf              | 0.5 |     | 2.0 | μs   |

## PROGRAMMING/ERASING INFORMATION (continued)

#### PACKAGE DIMENSIONS

Circuit diagrams utilizing Fujitsu products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information herein has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described herein any license under the patent rights of Fujitsu Limited or others. Fujitsu Limited reserves the right to change device specifications.