# TOSHIBA

# **TLCS-90 Series**

## **CMOS 8–Bit Microcontrollers**

#### TMP90PH48F

#### 1. Outline and Characteristics

The TMP90PM48 is a system evalution LSI having a built in One-Time PROM for TMP90C848.

A programming and verification for the internal PROM is achieved by using a general EPROM programmer with an adapter socket.

The function of this device is exactly same as the

TMP90C848 by programming to the internal PROM. The differences between TMP90PH48 and TMP90C848

are the memory size (ROM).

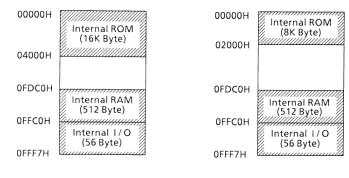

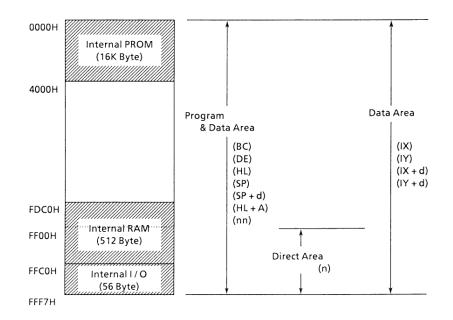

The following are the memory map of TMP90PH48 and TMP90C848.

TMP90PH48F Memory Map

TMP90C848F Memory Map

| Parts No.  | ROM              | RAM        | Package | Adapter Socket No. |

|------------|------------------|------------|---------|--------------------|

| TMP90PH48N | OTP 16384 x 8bit | 512 x 8bit | 80-FP   | BM1153             |

The information contained here is subject to change without notice.

The information contained herein is presented only as guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. These TOSHIBA products are intended for usage in general electronic equipments (office equipment, communication equipment, admestic electrification, etc.) Please make sure that you consult with us before you use these TOSHIBA products in equipments which require high quality and/or reliability, and in equipments which could have major impact to the welfare of human life (atomic energy control, spaceship, traffic signal, combustion control, all types of safety devices, etc.). TOSHIBA cannot accept liability to any damage which may occur in case these TOSHIBA products were used in the mentioned equipments whout prior consultation with TOSHIBA.

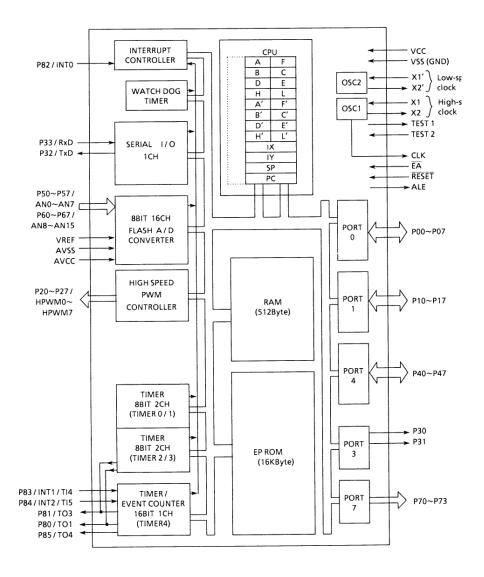

Figure 1. TMP90PH48F Block Diagram

# 2. Pin Assignment and Functions

The assignment of input/output pins, their names and functions are described below.

#### 2.1 Pin Assignment

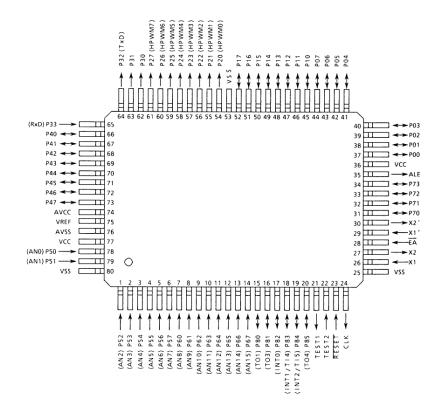

Figure 2.1 shows pin assignment of the TMP90PH48.

Figure 2.1 Pin Assignment (80-FP)

#### 2.2 Pin Names and Functions

The TMP90PH48 has MCU mode and PROM mode.

(1) MCU mode (The TMP90C848 and TMP90PH48 are pin compatible)

# Table 2.2 (1/2)

| Pin Name      | No. of pins | I/O or tristates | Function                                                                                                         |

|---------------|-------------|------------------|------------------------------------------------------------------------------------------------------------------|

| P00 ~ P07     | 8           | I/O              | Port 0: 8-bit I/O port. Each bit can be set for input or output.                                                 |

| P10 ~ P17     | 8           | I/O              | Port 1: An 8-bit I/O port.Each bit can be set for input or output Pull-up resistance included.                   |

| P20 ~ P27     | 8           | I/O              | Port 2: 8-bit output port.                                                                                       |

| P30           | 1           | Output           | Port 30: 1-bit output port.                                                                                      |

| P31           | 1           | Output           | Port 31: 1-bit output port.                                                                                      |

| P32           | 1           | Output           | Port 32: 1-bit output port.                                                                                      |

| /TxD          | I           | Output           | Used to transmit serial data.                                                                                    |

| P32           | 1           | Input            | Port 33: 1-bit output port.                                                                                      |

| /RxD          | I           | Input            | Used to receive serial data.                                                                                     |

| P40 ~ P47     | 8           | I/O              | Port 4: 8-bit I/O port. Each bit can be set for input or output (P40 - P43 O.D. 4mA sink, P44 - 47 10mA source). |

| P50 ~ P57     | 0           | Input            | Port 5: 8-bit input port.                                                                                        |

| /AN0 ~ AN7    | 8           | Input            | Analog input: 8-bit analog input to the A/D converter.                                                           |

| P60 ~ 67      | 8           | Input            | Port 6: 8-bit input port.                                                                                        |

| /AN8 ~ AN15   | 0           | Input            | Analog input: 8-bit analog input the A/D converter                                                               |

| P70 ~ P73     | 4           | I/O              | Port 7: 4-bit I/O port. Each bit can be set for input or output. Programmable pull-up resistance included.       |

| P80           |             | I/O              | Port 80: 1-bit I/O port.                                                                                         |

| /T01          | 1           | Output           | Timer output 1: Used for timer 0 or timer 1 output.                                                              |

| P81           | 1           | I/O              | Port 81: 1-bit I/O port.                                                                                         |

| /T03          | 1           | Output           | Timer output 3: Used for timer 2 or timer 3 output.                                                              |

| P82           | 1           | I/O              | Port 82: 1-bit I/O port.                                                                                         |

| /INT0         | 1           | Input            | Interrupt request pin 0: Level/rising edge programmable interrupt request pin.                                   |

| P83           |             | I/O              | Port 83: 1-bit I/O port.                                                                                         |

| /INT1<br>/TI4 | 1           | Input            | Interrupt request pin 1: Rising/falling edge programmable interrupt request pin.                                 |

| 7117          |             | Input            | Timer input 4: Count input/capture trigger signal for timer 4.                                                   |

| Pin name        | No. of pins | I/O or tristate | Function                                                                                                                                     |

|-----------------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| P84             |             | I/0             | Port 84: 1-bit I/O port.                                                                                                                     |

| /INT2           | 1           | Input           | Interrupt request pin 2: Rising edge programmable interrupt request pin.                                                                     |

| /TI5            |             | Input           | Timer input 5: Count input/capture trigger signal for timer 5.                                                                               |

| P85             | 4           | I/O             | Port 85: 1-bit I/O port.                                                                                                                     |

| /T04            |             | Output          | Timer output 4: used as the timer 4 output.                                                                                                  |

| ALE             | 1           | Output          | Address latch enable signal: The falling edge of this signal used as the timing to latch AD0 ~ AD7 addresses when accessing external memory. |

| CLK             | 1           | Output          | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation.<br>Pulled up during resetting.                                    |

| ĒĀ              | 1           | Input           | External access: Connected to the $V_{CC}$ pin when using the TMP90C848F with built-in ROM.                                                  |

| RESET           | 1           | Input           | Reset: Initializes the TMP90C848F.                                                                                                           |

| X1/X2           | 2           | I/0             | High-speed crystal oscillator connection pin.                                                                                                |

| X1'/X2'         | 2           | I/0             | Low-speed crystal oscillator connection pin.                                                                                                 |

| TEST1/TEST2     | 2           | I/0             | Testing pins Connects directly TEST1 and TEST2 at a normal state operation.                                                                  |

| AVCC            | 1           | -               | Comparator power supply for the A/D converter.                                                                                               |

| VREF            | 1           | -               | A/D converter reference voltage input.                                                                                                       |

| AVSS            | 1           | -               | Analog GND pin (0V)                                                                                                                          |

| V <sub>CC</sub> | 2           | -               | Power supply (+5V±10%)                                                                                                                       |

| V <sub>SS</sub> | 3           | -               | GND pin                                                                                                                                      |

#### Table 2.2 (2/2)

## TMP90PH48

#### (2) PROM Mode

| Pin Function<br>Name   | No. of<br>pins | I/O           | Function                           | Pin Name<br>(MCU mode) |

|------------------------|----------------|---------------|------------------------------------|------------------------|

| A7 ~ A0                | 8              | Input         | Address inputs                     | P27 ~ P20              |

| A15 ~ A8               | 8              | Input         |                                    | P15 ~ P10              |

| D7 ~ D0                | 8              | I/0           | Data Input/Output                  | P07 ~ P00              |

| ŌĒ                     | 1              | Input         | Output Enable Input                | P30                    |

| CE                     | 1              | Input         | Chip Enable Signal Input           | P31                    |

| VPP                    | 1              | Power Supply  | 12.5V/5V(Programming Power Supply) | ĒĀ                     |

| VCC                    | 1              | Power Supply  | 5V                                 | VCC                    |

| VSS                    | 1              | Power Supply  | 0V                                 | VSS                    |

| Pin Names              | No. of pins    | I/O           | Pin Setting                        |                        |

| P16, P17               | 2              | Output        | Be fixed to "L" level (Note).      |                        |

| P32, P33               | 2              | Output, Input | Be fixed to "H" level.             |                        |

| P40 ~ P47              | 8              | I/0           | Be fixed to "H" level.             |                        |

| P50 ~ P57<br>P60 ~ P67 | 8 8            | Input         | Be fixed to "L" level.             |                        |

| P70 ~ P73              | 4              | I/0           | Be fixed to "H" level.             |                        |

| P80 ~ P85              | 6              | I/0           | Be fixed to "L" level.             |                        |

| VREF/<br>AVss/AVcc     | 3              |               | Be fixed to "L" level.             |                        |

| RESET                  | 1              | Input         |                                    |                        |

| CLK                    | 1              | Output        | Refer to Figure 3.2                |                        |

| X1                     | 1              | Input         |                                    |                        |

| X2                     | 1              | Output        | Resonator connection pin           |                        |

| X1'                    | 1              | Input         |                                    |                        |

| X2'                    | 1              | Output        |                                    |                        |

# 3. Operation

The TMP90PH48 is the OTP version of the TMP90CC848 that is replaced an internal ROM from Mask ROM to EPROM.

The function of TMP90PH48 is exactly same as that of TMP90CC848 except the internal ROM size.

Refer to the TMP90C848 except the functions which are not described this section.

The following is an explanation of the hardware configuration and operation in relation to the TMP90CH48.

The TMP90PH48 has an MCU mode and a PROM mode.

#### 3.1 MCU Mode

(1) Mode Setting and Function

The MCU mode is set by opening the CLK pin (Output status).

In the MCU mode, the operation is same as that of TMP90C848.

(2) Memory Map

Figure 3.1 shows the memory map TMP90PH48, and the accessing area by the respective addressing mode.

Figure 3.1. TMP90PH48F Memory Map

#### 3.2 PROM Mode

(1) Mode Setting and Function

PROM mode is set by setting the  $\overline{\mbox{RESET}}$  and CLK pins to the "L" level.

The programming and verification for the internal

PROM is achieved by using a general EPROM programmer with the adapter socket. The device slection (ROM type) should be "27256" with following conditions.

Size = 256Kbit (32Kx 8bit) TPW = 1ms, VPP = 12.5V)

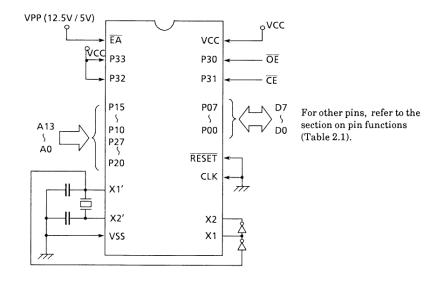

Figure 3.2 shows the setting of pins in PROM mode

Figure 3.2. PROM Mode Pin Setting

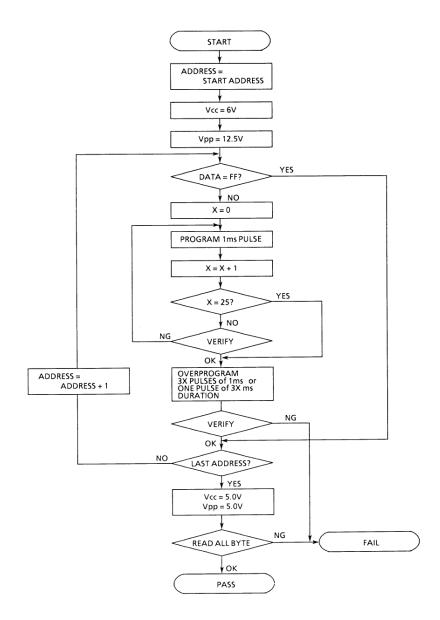

(2) Programming Flow Chart

The programming mode is set by applying 12.5V (programming voltage) to the VPP pin when the following pins are set as follows,

(Vcc : 6.0V) \*These conditions can be

(RESET : "L" level) obtained by using adaptor

(CLK : "L" level) socket.

After the address and data have been fixed, a data on the Data Bus is programmed when the  $\overline{CE}$  pin is set to "Low" (1ms plus is required).

General programming procedure of an EPROM programmer is as follows,

- Write a data to a specified address for 1ms.

- Verify the data. If the read-out data does not match the expected data, another writing is performed until the correct data is written (Max. 25 times).

After the correct data is written, an additional writing is performed by using three times longer programming pulse width (1ms x programming times), or using three times more programming pulse number. Then, verify the data and increment the address.

The verification for all data is done under the condition of Vpp = Vcc = 5V after all data were written. Figure 3.3 shows the programming flow chart.

8/14

Figure 3.3. Flow Chart

#### (3) The Security Bit

The TMP90PH48 has the Security Bit in PROM cell. If the Security Bit is programmed to "0", the content of the PROM is disable to read in PROM mode. How to program the Security Bit.

- 1) Connect A15 pins to Vcc. [Otherwise connect them GND to program PROM, (address 0000H ~ 3FFFH)

- 2) Set programming address to 0000H.

- 3) To program the Security Bit, Do to "0"

- 4) Set D2 ~ D7 to "1", respectively.

#### Table 3.1 Data to Program

| Bit to PROGRAM       | D0 ~ D7 | A0 ~ A12 | A15     |

|----------------------|---------|----------|---------|

| The Security Bit     | FEH     | all "O"  | all "1" |

| PROM (0000H ~ 1FFFH) | _       | -        | all "0" |

# 4. Electrical Characteristics

TMP90PH48

#### 4.1 Absolute Maximum Ratings

| Symbol              | Item                          | Rating                       | Unit |

|---------------------|-------------------------------|------------------------------|------|

| V <sub>CC</sub>     | Power supply voltage          | -0.5 ~ + 7                   | V    |

| V <sub>IN</sub>     | Input voltage                 | -0.5 ~ V <sub>CC</sub> + 0.5 | V    |

| PD                  | Power dissipation (Ta = 70°C) | 500                          | mW   |

| T <sub>SOLDER</sub> | Soldering temperature (10s)   | 260                          | О°   |

| T <sub>STG</sub>    | Storage temperature           | -65 ~ 150                    | С°   |

| T <sub>OPR</sub>    | Operating temperature         | -20 ~ 70                     | С°   |

#### 4.2 DC Characteristics

# $V_{CC}=5V{\pm}10\%\ TA=-20\ \sim\ 70^\circ C$ High-speed clock: 16 ~ 20MHz, Low-speed clock: 0.5 ~ 1MHz Typical values are for TA = 25°C and Vcc = 5V

| Symbol                                                                      | Parameter                                           | Min                                                     | Max                   | Unit                | Condition                                                                                                 |

|-----------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------|-----------------------|---------------------|-----------------------------------------------------------------------------------------------------------|

| VIL                                                                         | Input Low Voltage (P0)                              | -0.3                                                    | 0.8                   | V                   | -                                                                                                         |

| V <sub>IL1</sub>                                                            | P1, P3, P4, P5, P6, P7, P8                          | -0.3                                                    | 0.3V <sub>CC</sub>    | V                   | -                                                                                                         |

| V <sub>IL2</sub>                                                            | RESET, P82 (INTO)                                   | -0.3                                                    | 0.25V <sub>CC</sub>   | V                   | -                                                                                                         |

| V <sub>IL3</sub>                                                            | ĒĀ                                                  | -0.3                                                    | 0.3                   | V                   | -                                                                                                         |

| $V_{IL4}$                                                                   | X1, X1'                                             | -0.3                                                    | 0.2V <sub>CC</sub>    | V                   | -                                                                                                         |

| V <sub>IH</sub>                                                             | Input High Voltage (P0)                             | 2.2                                                     | V <sub>CC</sub> + 0.3 | V                   | -                                                                                                         |

| V <sub>IH1</sub>                                                            | P1, P3, P4, P5, P6, P7, P8                          | 0.7V <sub>CC</sub>                                      | V <sub>CC</sub> + 0.3 | V                   | -                                                                                                         |

| V <sub>IH2</sub>                                                            | RESET, P82 (INTO)                                   | 0.75V <sub>CC</sub>                                     | V <sub>CC</sub> + 0.3 | V                   | -                                                                                                         |

| V <sub>IH3</sub>                                                            | ĒĀ                                                  | V <sub>CC</sub> -0.3                                    | V <sub>CC</sub> + 0.3 | V                   | -                                                                                                         |

| V <sub>IH4</sub>                                                            | X1, X1'                                             | 0.8V <sub>CC</sub>                                      | V <sub>CC</sub> + 0.3 | V                   | -                                                                                                         |

| V <sub>OL</sub><br>V <sub>OL1</sub>                                         | Output Low Voltage<br>(OPEN DRAIN Sink)             |                                                         | 0.45<br>0.45          | V<br>0.45           | $I_{OL} = 1.6 \text{mA}$<br>$I_{OL} = 4 \text{mA}$                                                        |

| V <sub>OH</sub><br>V <sub>OH1</sub><br>V <sub>OH2</sub><br>V <sub>OH3</sub> | Output High Voltage<br>P44 ~ 47 (OPEN DRAIN Source) | 2.4<br>0.75V <sub>CC</sub><br>0.9V <sub>CC</sub><br>2.4 |                       | V<br>V<br>V<br>0.45 | I <sub>OH</sub> = -400μA<br>I <sub>OH</sub> = -100μA<br>I <sub>OH</sub> = -20μA<br>I <sub>OH</sub> = 10μA |

| ILI                                                                         | Input Leakage Current                               | 0.02 (Typ)                                              | 步                     | μA                  | 0.0≤ Vin ≤V <sub>CC</sub>                                                                                 |

| ILO                                                                         | Output Leakage Current                              | 0.05 (Typ)                                              | ±10                   | μA                  | 0.2≤ Vin ≤V <sub>CC</sub> - 0.2                                                                           |

| I <sub>CC</sub>                                                             | Operating Current (RUN)<br>Idle 1                   | 15 (Тур)<br>1.5 (Тур)                                   | 30<br>5               | mA<br>mA            | High-speed clock: 20MHz<br>Low-speed clock: 1MHz                                                          |

| (Vcc - Vss)                                                                 | STOP (TA = -20 ~ 7°C)<br>STOP (TA = 0 ~ 50°C)       | 0.2 (Typ)                                               | 40<br>10              | μΑ<br>μΑ            | $0.2 \le Vin \le V_{CC} - 0.2$                                                                            |

| Alcc<br>AVcc - AVss)                                                        | Operating Current                                   | 7 (Typ)                                                 | 15                    | mA                  | fosc = 10MHz<br>AVcc = 5V ± 10%                                                                           |

| V <sub>STOP</sub>                                                           | Power Down Voltage (@STOP)<br>RAM BACK UP           | 2.0                                                     | 6.0                   | V                   | $\label{eq:VIL2} \begin{array}{l} V_{IL2} = 0.2 V_{CC}, \\ V_{IH2} = 0.8 V_{CC} \end{array}$              |

| R <sub>RST</sub>                                                            | RESET, P1, P7, Pull Up Register                     | 30                                                      | 130                   | KΩ                  | -                                                                                                         |

| CIO                                                                         | Pin Capacitance                                     | -                                                       | 10                    | pF                  | testfreq = 1MHz                                                                                           |

| V <sub>TH</sub>                                                             | Schmitt width (RESET, P82)                          | 0.4                                                     | 1.0 (Typ)             | V                   | -                                                                                                         |

## 4.3 A/D Converter Characteristics

| V <sub>CC</sub> = 5V±10% TA = -20 ~ 70°C                  |  |

|-----------------------------------------------------------|--|

| High-speed clock: 16 ~ 20MHz, Low-speed clock: 0.5 ~ 1MHz |  |

| Symbol             | Parameter                                   | Condition              | Min | Тур | Max | Unit |

|--------------------|---------------------------------------------|------------------------|-----|-----|-----|------|

| V <sub>REF</sub>   | Analog reference voltage                    | -                      | 3.5 | Vcc | Vcc | V    |

| $\Delta V_{REF}$   | Analog reference voltage range              | V <sub>REF</sub> - Vss | 3.5 | Vcc | Vcc |      |

| AVss               | Analog power supply voltage                 | -                      | Vss | Vss | Vss |      |

| V <sub>AIN</sub>   | Analog input voltage range                  | -                      | Vss | -   | Vcc |      |

| I <sub>REFAD</sub> | Supply current for analog reference voltage | -                      | -   | 0.8 | 2   | mA   |

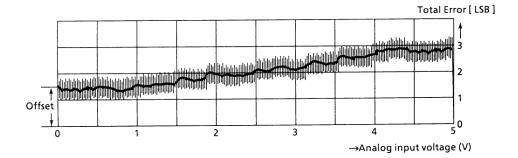

This A/D Converter is guaranteed only monotonicity because it has an offset value (when VAIN = 0V), but the 8-bit resolution is gotten except an offset value.

The A/D converted data is recommended to be processed relatively.

Figure 4.3 (1). A/D Converter Typical Conversion Characterics ( $V_{REF} = 5V$ , Vss = 0V)

#### 4.4 Zero-Cross Characteristics

|                              | $V_{CC} = 5V \pm 10\%$ TA = -20 ~ 70°C |

|------------------------------|----------------------------------------|

| High-speed clock: 16 ~ 20MHz | , Low-speed clock: 0.5 ~ 1MHz          |

| Symbol          | Item                                 | Condition               | Min  | Max | Unit    |

|-----------------|--------------------------------------|-------------------------|------|-----|---------|

| V <sub>ZX</sub> | Zero-cross detection input           | For AC, $C = 0.1 \mu F$ | 1    | 1.8 | VAC P-P |

| A <sub>ZX</sub> | Zero-cross accuracy                  | 50/60Hz sine wave       | -    | 135 | mV      |

| F <sub>ZX</sub> | Zero-cross detection input frequency | -                       | 0.04 | 1   | kHz     |

#### 4.5 Timer/Counter Input Clock (TI0, TI2, and TI4)

|                               | $V_{CC} = 5V \pm 10\% TA = -20 \sim 70^{\circ}C$ |

|-------------------------------|--------------------------------------------------|

| High-speed clock: 16 ~ 20MHz, | Low-speed clock: 0.5 ~ 1MHz                      |

| Symbol            | Parameter              | Variable |     | 10MHz Clock |     | Unit |

|-------------------|------------------------|----------|-----|-------------|-----|------|

|                   |                        | Min      | Max | Min         | Max | Unit |

| t <sub>VCK</sub>  | Clock cycle            | 8x + 100 | -   | 900         | -   | ns   |

| t <sub>VCKL</sub> | Low clock pulse width  | 4x + 40  | -   | 440         | -   | ns   |

| t <sub>VCKH</sub> | High clock pulse width | 4x + 40  | _   | 440         | _   | ns   |

#### 4.6 Interrupt Operation

# $V_{CC}$ = 5V±10%TA = -20 ~ 70°C High-speed clock: 16 ~ 20MHz, Low-speed clock: 0.5 ~ 1MHz

| Cumbal             | Item                              | Variable |     | 10MHz Clock |     | 11   |

|--------------------|-----------------------------------|----------|-----|-------------|-----|------|

| Symbol             |                                   | Min      | Max | Min         | Max | Unit |

| t <sub>INTAL</sub> | NMI, INTO Low level pulse width   | 4x       | _   | 400         | _   | ns   |

| t <sub>INTAH</sub> | NMI, INTO High level pulse width  | 4x       | -   | 400         | -   | ns   |

| t <sub>INTBL</sub> | INT1, INT2 Low level pulse width  | 8x + 100 | -   | 900         | -   | ns   |

| t <sub>INTBH</sub> | INT1, INT2 High level pulse width | 8x + 100 | -   | 900         | _   | ns   |

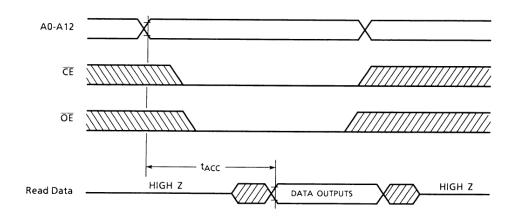

#### 4.7 Read Operation (PROM Mode)

#### DC Characteristic, AC Characteristic

#### $TA = -40 \sim 85^{\circ}C Vcc = 5V \pm 10\%$

| Symbol                                                  | Parameter                                                                                                    | Condition      | Min                                  | Max                                       | Unit        |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------|-------------------------------------------|-------------|

| V <sub>PP</sub><br>V <sub>IH1</sub><br>V <sub>IL1</sub> | V <sub>PP</sub> read voltage<br>Input high voltage (A0 ~ A15, CE, OE)<br>Input low voltage (A ~ A15, CE, OE) |                | 4.5<br>0.7 x V <sub>CC</sub><br>-0.3 | 5.5<br>Vcc + 0.3<br>0.3 x V <sub>CC</sub> | V<br>V<br>V |

| t <sub>ACC</sub>                                        | Address to output delay                                                                                      | $C_L = 50_P F$ | -                                    | 2.25TCYC + α                              | ns          |

TCYC = 400ns (10MHz Clock)  $\alpha$  = 200ns

#### 4.8 Programming Operation (PROM Mode)

#### DC Characteristic, AC Characteristic

#### $TA = 25 \pm 5^{\circ}C Vcc = 6V \pm 0.25V$

| Symbol           | Parameter                             | Condition                | Min                      | Тур   | Max                                               | Unit |

|------------------|---------------------------------------|--------------------------|--------------------------|-------|---------------------------------------------------|------|

| V <sub>PP</sub>  | Programming voltage                   | -                        | 12.25                    | 12.50 | 12.75                                             | V    |

| V <sub>IH</sub>  | Input high voltage (D0 ~ D7)          | -                        | 0.2V <sub>CC</sub> + 1.1 |       | V <sub>CC</sub> + 0.3                             | V    |

| VIL              | Input low voltage (D0 ~ D7)           | -                        | -0.3                     |       | V <sub>CC</sub> + 0.3<br>0.2V <sub>CC</sub> - 0.1 | V    |

| V <sub>IH1</sub> | Input high voltage (A0 ~ A15, CE, OE) | -                        | 0.7V <sub>CC</sub>       |       | V <sub>CC</sub> + 0.3                             | V    |

| V <sub>IL1</sub> | Input low voltage (A0 ~ A15, CE, OE)  | -                        | -0.3                     |       | 0.3V <sub>CC</sub>                                | V    |

| I <sub>CC</sub>  | V <sub>CC</sub> supply current        | t <sub>OSC</sub> = 10MHz | -                        |       | 50                                                | mA   |

| I <sub>PP</sub>  | V <sub>PP</sub> supply current        | V <sub>PP</sub> = 13.00V | -                        |       | 50                                                | mA   |

| t <sub>PW</sub>  | CE Program pulse width                | $C_L = 50_P F$           | 0.95                     | 1.00  | 1.05                                              | ms   |

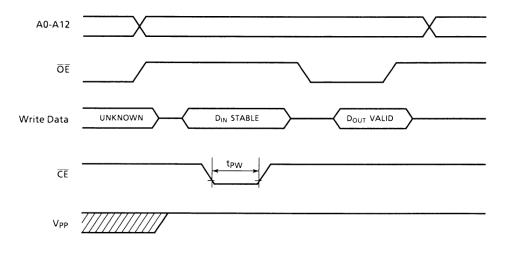

# 4.9 Read Operation Timing Chart (PROM Mode)

# 4.10 Programming Operation Timing Chart (PROM Mode)