# PaceMips™ R2010A FPA 32-BIT RISC CO-PROCESSOR (FLOATING POINT ACCELERATOR)

### **FEATURES**

- 32-BIT RISC Co-Processor:

- Contains sixteen 64-bit registers to support single-précision or double-precision arithmetic

- Fully conforms to the requirements of ANSI/IEEE Standard 754-1985, "IEEE Standard for Binary Floating Point Arithmetic"

- Up to three PaceMips R2010A Co-Processors can be used with the PR2000A Processor

- Compatible with the MIPS R3010 RISC Co-Processor

- Comprehensive System Development Support

- Produced with PACE II Technology™

- Tightly-coupled interface with the PaceMips R2000A increases system performance:

- 5 MFLOPS for single precision and 3 MFLOPS for double precision arithmetic when used with the PaceMips R2000A RISC Processor (Floating Point Operations for LINPACK Benchmark)

- Available Package:

- 84 Pin Quad J-Lead CerPak

- Military Temperature and MIL-STD-883C, Class B devices

#### DESCRIPTION

The PaceMips R2010A Co-Processor is a floating point accelerator that operates in conjunction with the PaceMips R2000A Processor and fully supports the requirements of ANSI/IEEE Standard 754-1985, "IEEE Standard for Binary Floating Point Arithmetic".

Like the PaceMips R2000A, the PR2010A uses a LOAD/ STORE architecture to increase system performance. In a LOAD/STORE architecture all operations are carried out on operands contained in the processor registers, and only the load and store instructions can access the main memory system. Included in the PR2010A there are sixteen 64-bit registers that can be used to store both single and double-precision values. All IEEE-Standard exception handling requirements are supported by a 32bit status/control register. The PR2010A is functionally compatible with the PR3010 25MHz Floating Point Accelerator.

The PaceMips R2010A Co-Processor is manufactured using PACE II Technology™ which is Performance Advanced CMOS Engineered to use 0.7 micron effective channel lengths resulting in 400 picoseconds loaded⁺ internal gate delays. PACE Technology includes two-level metal and epitaxial substrates. In addition to very high performance and very high density, the technology features latch-up protection and single event upset protection, and is supported by a Class 1 environment volume production facility.

The PaceMips R3010 Co-Processor is available in a 84 Pin Quad J-Lead CerPak.

\* For a fan-in/fan-out of 4 at 85°C junction temperature and 5.0 V supply.

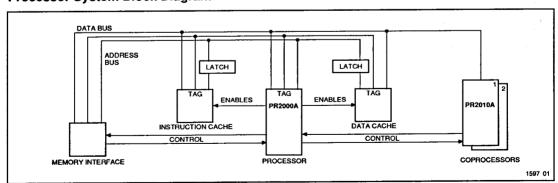

# Processor System Block Diagram

Means Quality, Service and Speed

©1989 Performance Semiconductor Corporation

PliOn:

**FpPresent:**

Clk2xSvs:

Clk2xSmp:

Clk2xRd:

### 1. SIGNAL DESCRIPTIONS

(I/O) A multiplexed 32-bit bus used for instruction and data transfers on phase 1 and phase 2, Data (31:0): respectively.

(O) A 4-bit bus containing even parity over the data bus. Parity is generated by the FPC on DataP(3:0):

(I) Input to the FPC which indicates whether the processor-coprocessor system is in the run or Run: stall state.

(I) Input to the FPC which indicates exception related status information. Exception:

(O) Signal to the CPU indicating a request for a coprocessor busy stall. FpBusy:

(O) Signal to the CPU indicating the result of the last comparison operation. FpCond:

(O) Signal to the CPU indicating that a floating-point exception has occured for the current FPC Fpint: instruction.

(I) Synchronous initialization input used to distinguish the processor-FPC synchronization period Reset: from the execution period. Reset must be synchronized by the leading edge of SysOut from the CPU.

> (I) Input which during the reset period determines whether the phase lock mechanism is enabled and during the execution period determines the output timing model.

(O) Output which is pulled to ground through an impedance of approximately 0.5k ohms. By providing an external pullup on this line an indication of the presence or absence of the FPC can be obtained.

(I) A double frequency clock input used for generating FpSysOut.

(I) A double frequency clock input used to determine the sample point for data coming into the FPC.

(I) A double frequency clock input used to determine the disable point for the data drivers.

(I) A double frequency clock input used to determine the position of the internal phases, phase 1 Clk2xPhl: and phase 2.

(O) Synchronization clock from the FPC. FpSysOut: (I) Input used to receive the synchronization clock from the FPC.

FpSysin: FpSync:

(I) Input used to receive the synchronization clock from the CPU.

## 2. ELECTRICAL SPECIFICATIONS

#### 2.1 MAXIMUM RATINGS

| Symbol           | Parameter             | Conditions | Min. | Max. | Units |

|------------------|-----------------------|------------|------|------|-------|

| V <sub>cc</sub>  | Supply Voltage        |            | 5    | +7.0 | V     |

| V <sub>IN</sub>  | Input Voltage (1)     |            | 5    | +7.0 | ٧     |

| T <sub>stg</sub> | Storage Temperature   |            | -65  | +150 | °C    |

| T <sub>A</sub>   | Operating Temperature |            | 0    | +70  | °C    |

Notes:

1597 Tbl 01

1.  $V_{\rm in}$  Min. = -3.0V for pulse width less than 15ns. 2. Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

#### 2.2 RECOMMENDED OPERATING CONDITIONS

| Grade      | Ambient<br>Temperature | GND | V <sub>cc</sub> |  |

|------------|------------------------|-----|-----------------|--|

| Commercial | 0°C to +70°C           | 0V  | 5.0V ± 5%       |  |

1597 Tbl 02

#### 2.3 CAPACITIVE LOAD DERATING FACTOR

| O               | Danamatan   | Conditions | 16MHz |     | Unit    |

|-----------------|-------------|------------|-------|-----|---------|

| Symbol          | Parameter   |            | Min   | Max | Oill    |

| C <sub>LD</sub> | Load Derate |            | .5    | 2   | ns/25pF |

1597 Tbl 03

### 2.4 DC ELECTRICAL CHARACTERISTICS

| Symbol                         | Parameter           | Conditions                                      | 16MHz |                      | 11-14 |

|--------------------------------|---------------------|-------------------------------------------------|-------|----------------------|-------|

|                                |                     |                                                 | Min   | Max                  | Unit  |

| V <sub>OH</sub>                | Output HIGH Voltage | V <sub>cc</sub> = Min<br>I <sub>OH</sub> = -4mA | 3.5   |                      | ٧     |

| V <sub>OL</sub>                | Output LOW Voltage  | V <sub>cc</sub> = Min.<br>I <sub>oL</sub> = 4mA |       | .4                   | ٧     |

| V <sub>IH</sub>                | Input HIGH Voltage  |                                                 | 2     | V <sub>cc</sub> + .5 | ٧     |

| V <sub>IL</sub> <sup>(1)</sup> | Input LOW Voltage   |                                                 | 5     | .8                   | ٧     |

| VIHS                           | Input HIGH Voltage  |                                                 | 3     | V <sub>cc</sub> + .5 | ٧     |

| V <sub>ILS</sub>               | Input LOW Voltage   |                                                 | 5     | .4                   | ٧     |

| V <sub>IHC</sub>               | Input HIGH Voltage  |                                                 | 4.0   | V <sub>cc</sub> + .5 | ٧     |

| V <sub>ILC</sub>               | Input LOW Voltage   |                                                 | 5     | .4                   | ٧     |

| C <sub>IN</sub>                | Input Capacitance   |                                                 |       | 10                   | рF    |

| C <sub>out</sub>               | Output Capacitance  |                                                 |       | 10                   | pF    |

| I <sub>cc</sub>                | Operating Current   | V <sub>cc</sub> = 5.5V                          |       | 550                  | mA    |

| C <sub>Ld</sub>                | Load Capacitance    |                                                 |       | 100                  | pF    |

Notes:

1597 Tbl 04

- 1. V<sub>IL</sub> Min. = -3.0V for pulse width less than 15ns.

2. V<sub>HB</sub> and V<sub>ILS</sub> apply to Clk2xSys, Clk2xSmp, Clk2xRd, Clk2Phi, FpSysIn, FpSync and Reset.

3. V<sub>HB</sub> and V<sub>ILC</sub> apply to Run and Exception.

4. Operation above the C<sub>Le</sub> maximum may impair the useful life of the device.

# 2.5 AC ELECTRICAL CHARACTERISTICS

| Symbol              | Parameter            | Conditions       | 16MHz |                    | Unit     |

|---------------------|----------------------|------------------|-------|--------------------|----------|

|                     |                      |                  | Min   | Max                | Onn      |

| T <sub>CkHigh</sub> | Input Clock High     | Transition ≤ 5ns | 12    |                    | ns       |

| T <sub>CkLow</sub>  | Input Clock Low      | Transition ≤ 5ns | 12    |                    | ns       |

| CKLOW               | Input Clock Period   |                  | 30    | 1000               | ns       |

| T <sub>CkP</sub>    | Clk2xSys to Clk2xSmp |                  | 0     | t <sub>Cyd/4</sub> | ns       |

| CKP                 | Clk2xSmp to Clk2xRd  |                  | 0     | t <sub>Cyo/4</sub> | ns       |

|                     | Clk2xSmp to Clk2xPhi |                  | 9     | t <sub>Cyc/4</sub> | ns       |

| T <sub>DEn</sub>    | Data Enable          |                  | -1    | -2                 | ns       |

| T <sub>DDis</sub>   | Data Disable         |                  | 0     | -1                 | ns       |

| T <sub>DVal</sub>   | Data Valid           |                  | 2     | 3                  | ns       |

| T <sub>DS</sub>     | Data Setup           |                  | 9     |                    | ns       |

| T <sub>DH</sub>     | Data Hold            |                  | -2.5  |                    | ns       |

| T <sub>FpCond</sub> | Fp Condition         |                  | 0     | 35                 | ns       |

| T <sub>FpBusy</sub> | Fp Busy              |                  | 0     | 15                 | ns       |

| T <sub>Fpint</sub>  | Fp Interrupt         |                  | 0     | 40                 | ns       |

| T <sub>FpMov</sub>  | Fp Move To           |                  | 0     | 35                 | ns       |

| T <sub>ExS</sub>    | Exception Setup      |                  | 10    |                    | ns       |

| T <sub>ExH</sub>    | Exception Hold       |                  | 0     |                    | ns       |

| TRunS               | Run Setup            |                  | 10    |                    | ns       |

| T <sub>RunH</sub>   | Run Hold             |                  | -2    |                    | ns       |

| Notes:              |                      | 1                |       |                    | 1597 Tbl |

Notes:

1. All output timings are given assuming 25pF of capacitive load.

2. All timings referenced to 1.5V.

3. The clock parameters apply to all four 2xClocks.

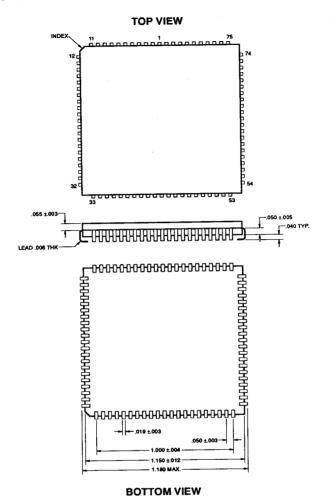

### 3. MECHANICAL DATA

## 3.1 PIN ASSINGMENT AND PACKAGE DIMENSIONS

### 3.1.1 84 Pin Quad J-Lead CerPak

Table 3.1 Pinout—84 Pin Quad J-Lead CerPak

| Pin Name   | Pin Number | Pin Name  | Pin Number |

|------------|------------|-----------|------------|

| Data(0)    | 33         | FpSync    | 23         |

| Data(1)    | 34         | Reset     | 22         |

| Data(2)    | 35         | PIIOn     | 28         |

| Data(3)    | 36         | Run       | 66         |

| Data(4)    | 39         | Exception | 67         |

| Data(5)    | 40         | Fp!nt     | 68         |

| Data(6)    | 41         | FpBusy    | 69         |

| Data(7)    | 42         | FpCond    | 70         |

| Data(8)    | 44         | VCC0      | 7          |

| Data(9)    | 45         | VCC1      | 15         |

| Data(10)   | 46         | VCC2      | 24         |

| Data(11)   | 47         | VCC3      | 26         |

| Data(12)   | 50         | VCC4      | 29         |

| Data(13)   | 51         | VCC5      | 31         |

| Data(14)   | 52         | VCC6      | 38         |

| Data(15)   | 53         | VCC7      | 49         |

| Data(16)   | 76         | VCC8      | 55         |

| Data(17)   | 77         | VCC9      | 57         |

| Data(18)   | 78         | VCC10     | 61         |

| Data(19)   | 79         | VCC11     | 63         |

| Data(20)   | 82         | VCC12     | 72         |

| Data(21)   | 83         | VCC13     | 75         |

| Data(22)   | 84         | VCC14     | 81         |

| Data(23)   | 1          | Gnd0      | 6          |

| Data(24)   | 3          | Gnd1      | 16         |

| Data(25)   | 4          | Gnd2      | 25         |

| Data(26)   | 5          | Gnd3      | 27         |

| Data(27)   | 8          | Gnd4      | 30         |

| Data(28)   | 9          | Gnd5      | 32         |

| Data(29)   | 10         | Gnd6      | 37         |

| Data(30)   | 11         | Gnd7      | 48         |

| Data(31)   | 14         | Gnd8      | 54         |

| DataP(0)   | 43         | Gnd9      | 56         |

| DataP(1)   | 73         | Gnd10     | 60         |

| DataP(2)   | 2          | Gnd11     | 62         |

| DataP(3)   | 17         | Gnd12     | 71         |

| Clk2xSys   | 19         | Gnd13     | 74         |

| Clk2xSmp   | 20         | Gnd14     | 80         |

| Clk2xRd    | 12         | Resvd0    | 58         |

| Clk2xPhi   | 21         | Resvd1    | 64         |

| FpSysIn    | 13         | Resvd2    | 65         |

| FpSysOut P | 18         | FpPresent | 59         |

1597 Tbl 06

Figure 3.1 Dimensions—84 Pin Quad J-Lead CerPak

1597 02

#### 3.2 MOUNTING

A variety of sockets allow low insertion force or zero insertion force mountings, and a choice of terminals such as soldertail, surface mounts or wire wrap. Several sock-

ets are available from the following sample list of socket manufacturers. Contact the manufacturer directly for the latest socket specifications.

- AMP Incorporated P.O. Box 3608 Harrisburg, PA 17105-3608 (800) 522-6752

- Burndy Corporation Richards Avenue Norwalk, CT 06856 (203) 838-4444

- Yamaichi Electronics Inc. 1425 Koll Circle, Suite 106 San Jose, CA 95112 (408) 452-0797

- Textool/3M Test and Interconnect Products Department 3M Austin Center

P.O. Box 2963

Austin, TX 78769-2963

(800) 225-5373

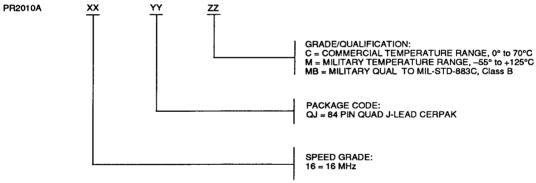

### 4. ORDERING INFORMATION

1597 03