# /VI/XI/VI

# CMOS Dual 12-Bit **Double-Buffered uP-Compatible DAC**

## **General Description**

Maxim's MX7549 is a dual, 12-bit, four-quadrant multiplying, current-output D/A converter (DAC) with 1% DAC-to-DAC matching. Thin-film resistors, laser-trimmed at the wafer level, maintain full accuracy over the operating temperature range. Other features include ±1/2LSB maximum integral nonlinearity, ±3LSB full-scale error, and ±5ppm/°C gain temperature coefficient.

Three address lines controlled by standard CHIP SELECT (CS) and WRITE (WR) signals simplify microprocessor  $(\mu P)$  interfacing. Each DAC is loaded in three 4-bit nibbles. The UPDATE (UPD) input updates the output of both DACs simultaneously.

All digital inputs are TTL, 74HC, and +5V CMOS compatible. The MX7549 operates from a single +5V to +15V supply and is pin-compatible with the AD7549.

## **Applications**

Automatic Test Equipment (ATE) Microprocessor-Based Process Control Programmable Power Supplies Programmable Filters

Synchro Applications

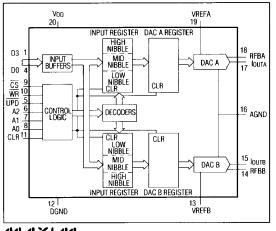

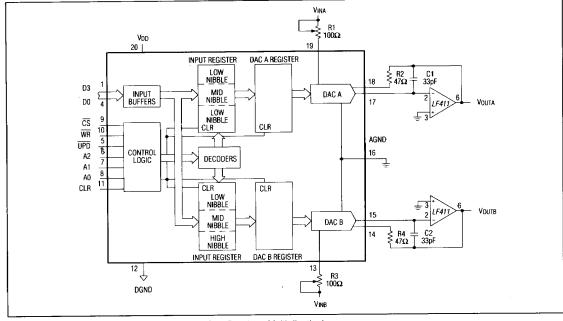

# Functional Diagram

### Features

- Two 12-Bit, Double-Buffered DACs in One Package

- ◆ 4-Bit Microprocessor Interface

- ◆ Four-Quadrant Multiplication

- ♦ 1% DAC-to-DAC Matching

- ♦ ±1/2LSB Max Integral Nonlinearity

- ◆ ±3LSB Max Full-Scale Error

- ◆ ±5ppm/°C Max Gain Tempco

- ◆ Operates with a Single +5V to +15V Supply

- ◆ Pin-Compatible with the AD7549

## **Ordering Information**

| PART       | TEMP. RANGE     | PIN-PACKAGE    | ERROR<br>(LSBs) |

|------------|-----------------|----------------|-----------------|

| MX7549JN   | 0°C to +70°C    | 20 Plastic DIP | ±1              |

| MX7549KN   | 0°C to +70°C    | 20 Plastic DIP | ±1/2            |

| MX7549JCWP | 0°C to +70°C    | 20 Wide SO     | ±1              |

| MX7549KCWP | 0°C to +70°C    | 20 Wide SO     | ±1/2            |

| MX7549JP   | 0°C to +70°C    | 20 PLCC        | ±1              |

| MX7549KP   | 0°C to +70°C    | 20 PLCC        | ±1/2            |

| MX7549JC/D | 0°C to +70°C    | Dice*          | ±1              |

| MX7549AQ   | -40°C to +85°C  | 20 CERDIP      | ±1              |

| MX7549BQ   | -40°C to +85°C  | 20 CERDIP      | ±1/2            |

| MX7549SE   | -55°C to +125°C | 20 LCC**       | ±1              |

| MX7549TE   | -55°C to +125°C | 20 LCC**       | ±1/2            |

| MX7549SQ   | -55°C to +125°C | 20 CERDIP**    | ±1              |

| MX7549TQ   | -55°C to +125°C | 20 CERDIP**    | ±1/2            |

\*Contact factory for dice specifications.

\*\*Contact factory for availability and processing to MIL-STD-883.

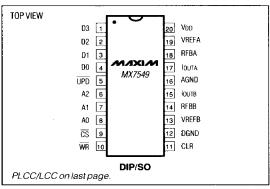

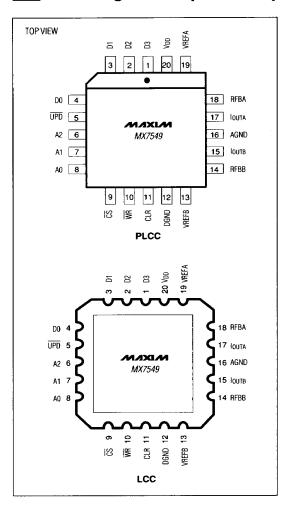

# Pin Configurations

NINXIN

Maxim Integrated Products 1

/ I / I X I / VI is a registered trademark of Maxim Integrated Products.

#### **ARSOLUTE MAXIMUM RATINGS**

| ADJOEO I E IIIAAIIII OIII IIAAIII OO                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD to DGND         -0.3V to +17V           VREFA to AGND         ±25V           VREFB to AGND         ±25V           VRFBA to AGND         ±25V           VRFBB to AGND         ±25V           AGND to DGND         -0.3V to Vpo+0.3V           Digital Input Voltage to DGND         -0.3V to Vpo+0.3V           Analog Outputs to DGND         -9.3V to Vpo+0.3V | Power Dissipation to +75°C (any package) Derate above +75°C by Operating Temperature Ranges: MX7549J_/K_ MX7549AQ/BQ MX7549S_/T_ Storage Temperature Lead Temperature (Soldering, 10 sec.) |

|                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

......550mW .....10mW/°C ....0°C to +70°C .-40°C to +85°C -55°C to +125°C -65°C to +150°C .....+300°C

## **ELECTRICAL CHARACTERISTICS**

(VDD = +15V ±5%; VREFA = VREFB = +10V; IOUTA = IOUTB = AGND = DGND = 0V; All Grades; TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMÉTER                                   | SYMBOL          | <u>_</u>                                                                                      | CONDITIONS                                                    |         |    |     | MAX  | UNITS  |  |

|---------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------|----|-----|------|--------|--|

| ACCURACY                                    |                 |                                                                                               |                                                               |         |    |     |      |        |  |

| Resolution                                  | N               |                                                                                               |                                                               |         | 12 |     |      | Bits   |  |

|                                             |                 |                                                                                               |                                                               | J/A/S   |    |     | ±1   | LSB    |  |

| Integral Nonlinearity                       | INL             |                                                                                               | K/B/T                                                         |         |    |     | ±1/2 |        |  |

| Differential Nonlinearity                   | DNL             | Guaranteed monoton                                                                            | ic over temperature                                           |         |    |     | ±1   | LSB    |  |

|                                             |                 |                                                                                               |                                                               | J/A/S   |    |     | ±6   | LSB    |  |

| Full-Scale Error                            | 1               |                                                                                               |                                                               | K/B/T   |    |     | ±3   |        |  |

| Gain Temperature Coefficient (Note 2)       | ΔGain/<br>ΔTemp |                                                                                               |                                                               |         |    | ±1  | ±5   | ppm/°C |  |

|                                             |                 |                                                                                               | T <sub>A</sub> = +25°C                                        |         |    |     | 20   |        |  |

| Output Leakage Current                      | lout            | DAC_Register loaded with all 0's                                                              | T. T 44 T                                                     | J/K/A/B |    |     | 150  | nA     |  |

|                                             |                 | loaded William of                                                                             | TA = TMIN to TMAX                                             | S/T     |    |     | 250  | )      |  |

| Reference Input Resistance                  |                 |                                                                                               |                                                               |         | 7  | 11  | 18   | kΩ     |  |

| VREFA, VREFB Input                          | VREF            |                                                                                               |                                                               | J/A/S   |    | ±1  | ±3   | %      |  |

| Resistance Match                            | VHEF            |                                                                                               |                                                               | K/B/T   |    | ±1  | ±2   |        |  |

| DYNAMIC PERFORMANCE (No                     | ote 3)          |                                                                                               |                                                               |         |    |     |      |        |  |

| Output-Current Settling Time (Note 4)       | ts              |                                                                                               | T <sub>A</sub> = +25°C                                        |         |    | 0.8 | 1.5  | μs     |  |

| AC Feedthrough VREF_ to                     |                 |                                                                                               | T <sub>A</sub> = +25°C                                        |         |    |     | -70  | dB     |  |

| IOUT_ (Note 5)                              |                 |                                                                                               | TA = TMIN to TMAX                                             |         |    |     | -65  |        |  |

| Digital-to-Analog Glitch Impulse            | Q               | Note 6                                                                                        | T <sub>A</sub> = +25°C                                        |         |    | 10  |      | (nV)(s |  |

| 0.1.10                                      | Cour            | DAC_loaded with a                                                                             | l 0's                                                         |         |    | 40  | 80   | pF     |  |

| Output Capacitance                          | Соит            | DAC_loaded with all 1's                                                                       |                                                               |         |    | 100 | 160  | ļ.,    |  |

| Channel-to-Channel Isolation VREF_ to IOUT_ |                 | VREFA = 20Vp-p 100kHz sine wave, VREFB = 0V or<br>VREFB = 20Vp-p 100kHz sine wave, VREFA = 0V |                                                               |         |    | -62 |      | dB     |  |

| Digital Crosstalk                           |                 | For code transitions from all 0's to all 1's                                                  |                                                               |         |    | 10  |      | (nV)(s |  |

| Output-Noise Voltage Density                |                 | From RFBA to IOUTA<br>10Hz to 100kHz.                                                         | From RFBA to IOUTA and from RFBB to IOUTB.<br>10Hz to 100kHz. |         |    | 15  |      | nV∠√H  |  |

| Harmonic Distortion                         | THD             | V <sub>IN</sub> = 6Vrms 1kHz                                                                  |                                                               |         |    | -90 |      | dB     |  |

|   |  | 44 43/1 44 |

|---|--|------------|

| 2 |  | MIXIM      |

3

# **CMOS Dual 12-Bit Double-Buffered µP-Compatible DAC**

**ELECTRICAL CHARACTERISTICS (continued)**

(VDD = +15V ±5%; VREFA = VREFB = +10V; IOUTA = IOUTB = AGND = DGND = 0V; All Grades; TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                  | SYMBOL        | C                            | CONDITIONS                        |     | TYP     | MAX    | UNITS |

|----------------------------|---------------|------------------------------|-----------------------------------|-----|---------|--------|-------|

| DIGITAL INPUTS             |               |                              |                                   |     |         |        |       |

|                            |               |                              | T <sub>A</sub> = +25°C            |     |         | ±1     |       |

| Input Current              | IN            | VIN = VDD                    | TA = TMIN to TMAX                 |     |         | ±10    | μA    |

| Input Low Voltage          | VIL           |                              |                                   |     |         | 0.8    | V     |

| Input High Voltage         | ViH           |                              |                                   | 2.4 |         |        |       |

| Input Capacitance (Note 3) | Cin           |                              |                                   |     |         | 7      | pF    |

| POWER REQUIREMENTS         |               |                              |                                   |     |         |        |       |

| Power Supply               | IDD           | All digital inputs           | at V <sub>1H</sub>                |     |         | 3      | mA    |

| Power-Supply Rejection     | ∆Gain<br>∆Vpp | V <sub>DD</sub> = 10.8V to 1 | V <sub>DD</sub> = 10.8V to 15.75V |     | ±0.0005 | ±0.002 | %/%   |

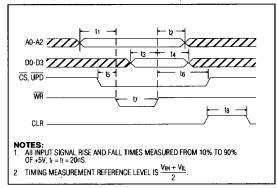

### TIMING CHARACTERISTICS

(VDD = +15V, VREFA = VREFB = +10V; IOUTA = IOUTB = AGND = DGND = 0V; All Grades; TA = TMIN to TMAX, unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL           | CONDITIONS                               |     | MIN TYP | MAX | UNITS |  |    |

|-------------------------------------------|------------------|------------------------------------------|-----|---------|-----|-------|--|----|

|                                           |                  | T <sub>A</sub> = +25°C                   |     | 50      |     |       |  |    |

| Address Valid to<br>Write Setup Time      | t <sub>1</sub>   | T. T. W. An T                            | J/A | 75      |     | ns    |  |    |

| write Setup Time                          |                  | TA = TMIN to TMAX                        | S/T | 90      |     |       |  |    |

| Address Valid to<br>Write Hold Time       | t2               |                                          |     | 0       |     | ns    |  |    |

|                                           |                  | T <sub>A</sub> = +25°C                   |     | 70      |     |       |  |    |

| Data Setup Time                           | t3               | T. T | J/A | 95      |     | ns    |  |    |

| ·                                         |                  | TA = TMIN to TMAX                        |     | 120     |     |       |  |    |

| Data Hold Time                            | t4               |                                          |     | 0       |     | ns    |  |    |

| Chip Select or Update to Write Setup Time | t5               |                                          |     | 0       |     | ns    |  |    |

| Chip Select or Update to Write Hold Time  | t <sub>6</sub>   |                                          |     | 0       |     | ns    |  |    |

|                                           |                  | T <sub>A</sub> = +25°C                   |     | 50      |     |       |  |    |

| Write Pulse Width                         | e Pulse Width t7 |                                          |     | t7 J/A  | J/A | 75    |  | ns |

|                                           |                  | $T_A = T_{MIN}$ to $T_{MAX}$             | S/T | 90      |     |       |  |    |

|                                           |                  | T <sub>A</sub> = +25°C                   |     | 50      |     |       |  |    |

| Clear Pulse Width                         | t <sub>8</sub>   | T T T                                    | J/A | 75      |     | ns    |  |    |

|                                           |                  | TA = TMIN to TMAX                        | S/T | 90      |     | 1     |  |    |

| Note 1: | At VDD = +5V, the device is functional with degraded performance. | Performance at power-supply tolerance limits is |

|---------|-------------------------------------------------------------------|-------------------------------------------------|

|         | guaranteed by Power-Supply Rejection test                         |                                                 |

Note 2: Ğuaranteed by design.

These characteristics are for design guidance only and are not subject to test. Note 3:

Note 4: Measured to 0.01% of full-scale range. IOUT Load =  $100\Omega$ . CEXT = 13pF. DAC output measured from falling edge of  $\overline{WR}$ . Note 5: VREF\_ = 20Vp-p 10kHz sine wave. DAC register is loaded with all zeros.

Note 6: Measured with VREFA = VREFB = 0V. IOUTA, IOUTB load = 1000, CEXT = 13pF. DAC registers alternately loaded with all 0's and 1's.

| 444 41 37 1 444 |  |  |  |

|-----------------|--|--|--|

### Pin Description

| PIN | NAME  | FUNCTION                                                                                   |

|-----|-------|--------------------------------------------------------------------------------------------|

| 1   | D3    | Data Bit 3, 7, or 11 (MSBs)                                                                |

| 2   | D2    | Data Bit 2, 6, or 10                                                                       |

| 3   | D1    | Data Bit 1, 5, or 9                                                                        |

| 4   | D0    | Data Bit 0, 4, or 8 (LSBs)                                                                 |

| 5   | UPD   | UPDATE Input - active low. Updates both DAC registers simultaneously from input registers. |

| 6-8 | A2-A0 | Address Lines 2 - 0                                                                        |

| 9   | CS    | CHIP SELECT Input - active low                                                             |

| 10  | WR    | WRITE Input - active low                                                                   |

| 11  | CLR   | CLEAR Input - active high. Clears all registers.                                           |

| 12  | DGND  | Digital Ground                                                                             |

| 13  | VREFB | Voltage Reference Input to DAC B                                                           |

| 14  | RFBB  | Feedback Resistor for DAC B                                                                |

| 15  | Іоитв | DAC B Output                                                                               |

| 16  | AGND  | Analog Ground                                                                              |

| 17  | IOUTA | DAC A Output                                                                               |

| 18  | RFBA  | Feedback Resistor for DAC A                                                                |

| 19  | VREFA | Voltage Reference Input to DAC A                                                           |

| 20  | VDD   | Supply Voltage Input                                                                       |

### **Detailed Description**

The nibble input registers of both DACs share a common 4-bit input buffer. Address inputs A2 - A0 select which DAC will receive a 4-bit nibble from the input data bus. With  $\overline{CS}$ , the address lines, and  $\overline{WR}$  low, the low-nibble (4 least significant bits (LSBs)) from the input buffer transfers to the DAC A low-nibble register (Table 1). The mid- and high-nibbles (4 mid and most significant bits (MSBs)) are then transferred in two additional WRITE cycles, reflecting the subsequent 3-bit address codes. The 4th WRITE cycle transfers the 12-bit data from the DAC A nibble input registers to the DAC A register. The DAC B register is loaded in a similar manner. With  $\overline{CS}$  high,  $\overline{UPD}$  low, and after all nibble input registers are loaded, strobing  $\overline{WR}$

updates DAC A and DAC B registers simultaneously, eliminating one WRITE cycle. All digital inputs incorporate standard protection circuitry and are TTL, 74HC, and +5V CMOS compatible.

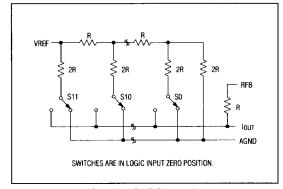

#### **D/A Converter**

The basic MX7549 circuit includes two identical DACs with laser-trimmed, thin-film (R-2R) arrays with NMOS current-steering switches (Figure 1). Binary-weighted currents switch between AGND and the output, depending on the status of each input data bit.

Figure 1. MX7549 Simplified DAC Schematic

The current output can be converted to a voltage by adding an external output amplifier (Figures 3, 4). The VREF input accepts a wide range of signals, including fixed and time-varying voltage or current inputs. Consider the temperature coefficient of R1 (R3) and R2 (R4) to minimize gain variation with temperature. The internal feedback resistor is compensated with an NMOS switch that matches the NMOS switches used in the R-2R array. This yields excellent supply rejection and gain temperature coefficients.

The output capacitance, C<sub>OUT</sub>, is code dependent and is typically 40pF with DAC loaded with all zeros, or 100pF with all ones.

#### **Digital Circuit**

Logic inputs are TTL, 74HC, and +5V CMOS compatible (0.8V and 2.4V) at  $V_{\rm DD} = +12V$  to +15V. DAC supply current can be reduced below specified levels by keeping digital input voltages as close to the logic supply and ground as possible (as with CMOS logic levels).

Table 1. MX7549 Truth Table

| CLR | UPD | CS | WR | A2 | <b>A</b> 1 | A0 | FUNCTION                                                  |

|-----|-----|----|----|----|------------|----|-----------------------------------------------------------|

| 0   | Х   | X  | 1  | Х  | Х          | Х  | No data transfer                                          |

| 0   | 1   | 1  | X  | Х  | Х          | Х  | No data transfer                                          |

| 1   | х   | ×  | ×  | х  | ×          | ×  | All registers cleared                                     |

| 0   | 1   | 0  | T  | 0  | 0          | 0  | DAC A low-<br>nibble register<br>loaded from<br>data bus  |

| 0   | 1   | 0  | T  | 0  | 0          | 1  | DAC A mid-<br>nibble register<br>loaded from<br>data bus  |

| 0   | 1   | 0  | v  | 0  | 1          | 0  | DAC A high-<br>nibble register<br>loaded from<br>data bus |

| 0   | 1   | 0  | T  | 0  | 1          | 1  | DAC A register<br>loaded from<br>nibble registers         |

| 0   | 1   | 0  | T  | 1  | 0          | 0  | DAC B low-<br>nibble register<br>loaded from<br>data bus  |

| 0   | 1   | 0  | v  | 1  | 0          | 1  | DAC B mid-<br>nibble register<br>loaded from<br>data bus  |

| 0   | 1   | 0  | T  | 1  | 1          | 0  | DAC B high-<br>nibble register<br>loaded from<br>data bus |

| 0   | 1   | 0  | 7. | 1  | 1          | 1  | DAC B register<br>loaded from<br>nibble registers         |

| 0   | 0   | 1  | T  | x  | x          | ×  | DAC A and B registers updated simultaneously              |

Note: X = Don't care

#### Interface

Figure 2 shows the timing diagram for the MX7549. A2. A1, and A0 select the nibble (low, mid, or high) input registers for DAC A or DAC B (Table 1). Data is transferred on the falling edge of WR with CS and CLEAR (CLR) low. When loading the high-nibble register, D11 is the MSB of the 4-bit data input. Similarly, D7 is the MSB for the mid nibble, and D3 is the MSB for the low nibble. Once the nibble input registers are loaded, the appropriate DAC register is selected and the data transferred. When UPD and CLR are low and CS high, the DAC registers are updated simultaneously when WR goes active (low).

Figure 2. Timing Diagram for MX7549

# \_\_\_ Applications Unipolar Operation

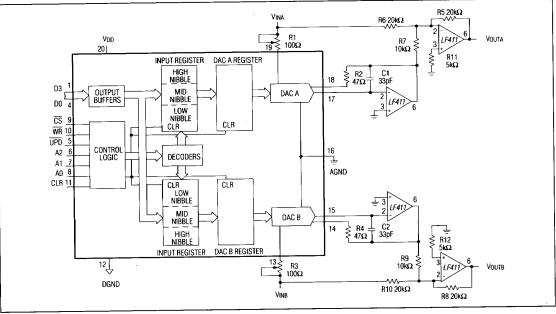

Figure 3 shows the most common configuration for the MX7549 that is used for unipolar binary operation or two-quadrant multiplication when VIN\_ is an AC signal. For full-scale adjustment, load 1's into the DAC A register, and trim R1 until VOUT\_ = -VIN(4095/4096). Alternatively, R1-R4 can be omitted, and the reference voltage can be adjusted to compensate for full-scale error. DAC B full-scale errors are trimmed in the same manner.

Capacitors C1 and C2 provide phase compensation. They also reduce overshoot and ringing when fast amplifiers are used at the DAC output. Single or dual op amps can be used in this application.

Figure 3. Dual DAC Unipolar Binary Operation (Two-Quadrant Multiplication)

Table 2. Unipolar Binary Code Table for MX7549

| - 1  | DIGITAL INPUT | ANALOG OUTPUT                            |

|------|---------------|------------------------------------------|

| 1111 | 1111 1111     | $-V_{IN} \frac{4095}{4096}$              |

| 1000 | 0000 0000     | $-V_{1N}\frac{2048}{4096} = -1/2 V_{1N}$ |

| 0000 | 0000 0001     | -V <sub>IN</sub> 1/4096                  |

| 0000 | 0000 0000     | OV                                       |

Note 1: Use R1, R2, R3, and R4 only if gain adjustment is required.

**Note 2:** C1 and C2 capacitors prevent oscillations when using high-speed amplifiers.

#### **Bipolar Operation**

Figure 4 shows bipolar operation (four-quadrant multiplication) using offset-binary code. Adjust zero error as follows: with the appropriate DAC register loaded to 1000

0000 0000, adjust R1 (R3) so VOUTA (VOUTB) = 0V. Alternatively, omit R1 and R2 (R3, R4), and vary R6 and R7 (R9, R10) ratios for VOUTA = 0V. For full-scale trimming, adjust the VIN amplitude, or vary the R5 (R8) value. Select resistors R5, R6, and R7 (R8, R9, R10) so all ratios match to 0.01% and have low-temperature coefficients (e.g. RN-type metal film).

Table 3. Bipolar Binary Code Table for MX7549

| DIGITAL INPUT  | ANALOG OUTPUT                        |

|----------------|--------------------------------------|

| 1111 1111 1111 | +V <sub>IN</sub> 2047<br>2048        |

| 1000 0000 0001 | +V <sub>IN</sub> 1/2048              |

| 1000 0000 0000 | OV                                   |

| 0111 1111 1111 | $-V_{1N} \frac{1}{2048}$             |

| 0000 0000 0000 | $-V_{IN}\frac{2048}{2048} = -V_{IN}$ |

Figure 4. Dual DAC Bipolar Offset Binary Operation (Four-Quadrant Multiplication)

# \_\_\_ Application Hints Temperature Coefficients

The MX7549 has a maximum gain temperature coefficient (TC) of ±5ppm/°C. If the trim resistors in Figures 3 or 4 are used to adjust full-scale gain error, consider their TC as part of total gain error over the temperature range. Select resistors R5, R6, and R7 (R8, R10, R9) so all ratios match to 0.01% and have low-temperature coefficients (e.g. RN-type metal film).

## Digital Feedthrough

The digital inputs to the MX7549 are normally connected directly to the  $\mu P$  bus. Even when the device is not selected, these inputs will be constantly changing. The

high-frequency logic activity on the bus can feed through the DAC package capacitance to show up as noise on the DAC output. Care should be taken in routing the PC board layout and selecting decoupling components to minimize noise.

## **Output Amplifier**

7

The output amplifier's offset voltage (Vos) adds to the DAC's nonlinearity. To minimize the effect of Vos and maintain monotonicity, Vos should be less than (25 x 10-6)(VREF) over the operating temperature range. The LF430 has a maximum Vos of 5µV over temperature and is ideal for low-bandwidth applications. The LF411 has a 15V/sec slew rate with a wide bandwidth and is recommended for multiplying applications.

/V/XI/VI \_\_\_\_\_

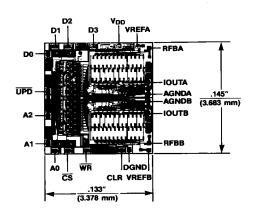

## PIn Configurations (continued)

# Chip Topography

024748 V \_ R

SEP 2 5 1991

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

©1991 Maxim Integrated Products

Printed USA

19-3799

3/91