#### **FEATURES**

- On chip Phase Locked Loop for clock synchronization

- Synchronizes frequencies up to 120 MHz (output)

- ±1ns skew (max) between input and output clocks

- Can recover poor duty cycle clocks

- CLK1 and CLK2 skew controlled to within ±1ns

- Single 5 volt power supply

- · Low power CMOS technology

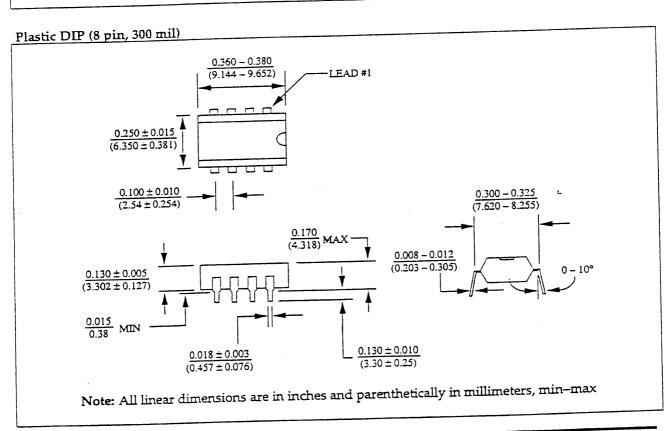

- Small 8 pin DIP or SOIC package

- · On chip loop filter

- w42C70-01, -04 for output clocks 10-120

- w42C70-02, -05 for output clocks 2.5-30 MHz

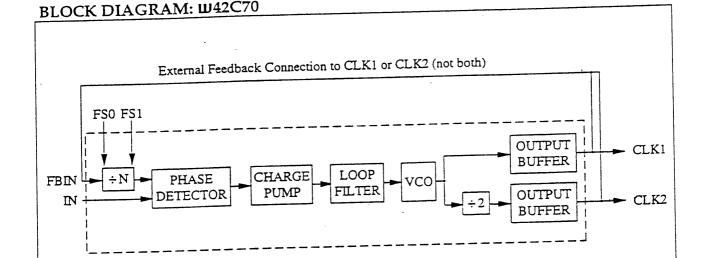

#### DESCRIPTION

The w42C70 generates an output clock which is synchronized to a given continuous input clock with zero delay (±1ns). Using IC WORKS' proprietary phase locked loop (PLL) analog CMOS technology, the w42C70 is useful for regenerating clocks in high speed systems where skew is a major concern. By the use of the two select pins, multiples or divisions of the input clock can be generated with zero delay (see Tables 2 and 3). The standard versions produce two outputs, where CLK2 is always a divide by two version of CLK1.

The  $\pm 42$ C70 is also useful to recover poor duty cycle clocks. A 50 MHz signal with a 20/80% duty cycle, for example, can be regenerated to the 48/52% typical of the part.

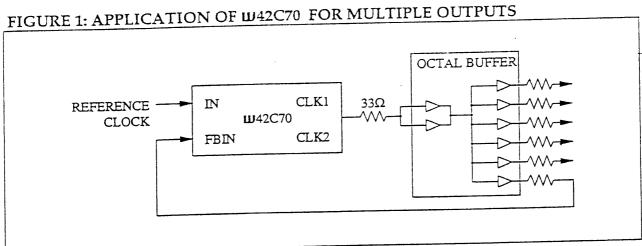

The w42C70 allows the user to control the PLL feedback, making it possible, with an additional 74F240 octal buffer (or other such device that offers controlled skew outputs), to synchronize up to 8 output clocks with zero delay compared to the input (see Figure 1).

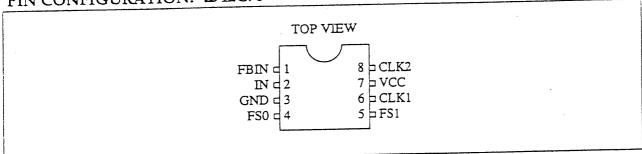

#### PIN DESCRIPTIONS

| INVEST   |      |        |                                                      |

|----------|------|--------|------------------------------------------------------|

| Pin Name | Pin# | Type   | Description                                          |

| FBIN     | 1    | Input  | FEEDBACK INPUT                                       |

| IN       | 2    | Input  | INPUT for reference clock                            |

| GND      | 3    | -      | GROUND                                               |

| FS0      | 4    | Input  | FREQUENCY SELECT 0                                   |

| PS1      | 5    | Input  | FREQUENCY SELECT 1                                   |

| CLK1     | 6    | Output | CLOCK output 1 (See Tables 1, 2, 3, 6, 7 for values) |

| VCC      | 7    | -      | Power Supply (+5V)                                   |

| CLK2     | 8    | Output | CLOCK output 2 (See Tables 1, 2, 3, 6, 7 for values) |

# PIN CONFIGURATION: W42C70

TABLE 1

| FS1 | FS0 | f <sub>FBIN</sub> (-01,-02)                | f <sub>FBIN</sub> (-04,-05)                                       |  |  |

|-----|-----|--------------------------------------------|-------------------------------------------------------------------|--|--|

| 0 0 | 0 1 | 2 · f <sub>IN</sub><br>4 · f <sub>IN</sub> | 3 · f <sub>IN</sub><br>5 · f <sub>IN</sub><br>6 · f <sub>IN</sub> |  |  |

| 1 1 | 0 1 | #N<br>8 · f <sub>IN</sub>                  | 10 · f <sub>IN</sub>                                              |  |  |

#### USING THE W42C70

The  $\mathbf{w}42$ C70 has the following characteristics:

- Rising edges at IN and FBIN are lined up. Falling edges are not synchronized.

- 2 The relationship between the frequencies at FBIN and IN is shown in Table 1.

- 3. The frequency of CLK2 is half the CLK1 frequency.

4. The CLK1 frequency ranges are:

$$$\omega 42C70-01, 04$$$

10 < fCLK1 < 120MHz  $$\omega 42C70-02, -05$$  2.5 < fCLK1 < 30MHz

The  $\mathbf{w}$ 42C70 will only operate correctly within these frequency ranges.

# ELIMINATE HIGH SPEED CLOCK ROUTING PROBLEMS

The  $\mathbf{w}42C70$  makes it possible to route lower speed clocks over long distances on the PC board, and to place a  $\mathbf{w}42C70$  next to the device requiring a higher speed clock. The multiplied output can then be used to produce a phase locked, higher speed output clock.

# COMPENSATE FOR PROPAGATION **DELAYS**

Including  $\mathbf{w}42$ C70 in a timing loop allows the use of PALs, gate arrays, etc., with loose timing specifications. The w42C70 compensates for the delay through the PAL and synchronizes the output to the input reference clock.

# OPERATING FREQUENCY RANGE

The  $\pm 42$ C70 is offered in versions optimized for operation in two frequency ranges. The -01 and -04 cover high frequencies, 10 to 120 MHz. The -02 and -05 operate from 2.5 to 30 MHz. The  $\upmu42$ C70 can be supplied with custom multiplication factors and operating ranges. Consult IC WORKS for details.

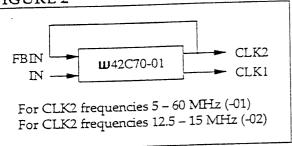

# USING CLK2 FEEDBACK

Connecting CLK2 to FBIN as shown in Figure 2 will cause all of the rising edges to be aligned (Fig. 3).

#### FIGURE 2

TABLE 2: DECODING TABLE FOR W42C70-01, 2 WITH CLK2 FEEDBACK

| Darcio o | -/ - |       |      |

|----------|------|-------|------|

| FS1      | FS0  | CLK1  | CLK2 |

| 0        | 0    | INx4  | INx2 |

| 0        | 1    | INx8  | INx4 |

| 1        | 0    | INx2  | IN   |

| 1        | 1    | INx16 | INx8 |

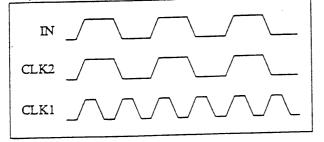

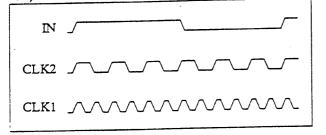

# FIGURE 3: INPUT AND OUTPUT CLOCK WAVEFORMS FOR w42C70-01, 2 WITH CLK2 FEEDBACK

# USING CLK1 FEEDBACK

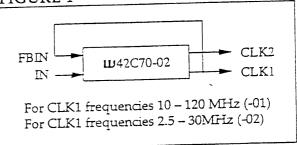

With CLK1 connected to FBIN as shown in Figure 4, the input and CLK1 output will be aligned on the rising edge, but CLK2 can be either rising or falling (Fig. 5).

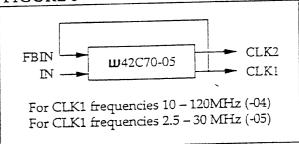

#### FIGURE 4

TABLE 3: DECODING TABLE FOR UJ42C70-01, 2 WITH CLK1 FEEDBACK

| marcio | · - / |      |      |

|--------|-------|------|------|

| FS1    | FS0   | CLK1 | CLK2 |

| 0      | 0     | INx2 | IN   |

| 0      | 1     | INx4 | INx2 |

| 1      | 0     | IN   | IN÷2 |

| 1      | 1     | INx8 | INx4 |

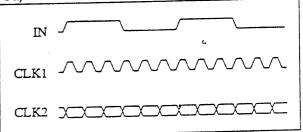

FIGURE 5: INPUT AND OUTPUT CLOCK WAVEFORMS FOR **ш**42C70-01, 2 WITH CLK1 FEEDBACK

#### USING CLK2 FEEDBACK

Connecting CLK2 to FBIN as shown in Figure 6 will cause all of the rising edges to be aligned (Fig. 7).

#### FIGURE 6

# TABLE 4: DECODING TABLE FOR w42C70-04, 5 WITH CLK2 FEEDBACK

| FS1 | FS0 | CLK1  | CLK2  |

|-----|-----|-------|-------|

| 0   | 0   | INx6  | INx3  |

| 0   | 1   | INx10 | INx5  |

| 1   | 0   | INx12 | INx6  |

| 1   | 1   | INx20 | INx10 |

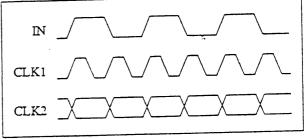

### FIGURE 7: INPUT AND OUTPUT CLOCK WAVEFORMS FOR **w**41C70-04, 5 WITH CLK2 FEEDBACK

#### USING CLK1 FEEDBACK

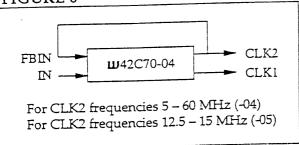

With CLK1 connected to FBIN as shown in Figure 8, the input and CLK1 output will be aligned on the rising edge, but CLK2 can be either rising or falling (Fig. 9).

#### FIGURE 8

TABLE 5: DECODING TABLE FOR W42C70-04, 5 WITH CLK1 FEEDBACK

| FS1 FS0 |   | CLK1  | CLK2   |

|---------|---|-------|--------|

| 0       | 0 | INx3  | INx1.5 |

| 0       | 1 | INx5  | INx2.5 |

| 1       | 0 | INx6  | INx3   |

| 1       | 1 | IN×10 | INx5   |

### FIGURE 9: INPUT AND OUTPUT CLOCK WAVEFORMS FOR **II** 42C70-04, 5 WITH CLK1 FEEDBACK

ABSOLUTE MAXIMUM RATINGS (Note 1)

| ABSOLUTE MANAMENTAL                      |        | D - L'       | Unit  |

|------------------------------------------|--------|--------------|-------|

| Parameter                                | Symbol | Rating       | Ultit |

|                                          |        | 7            | V     |

| VCC referenced to GND                    |        | 0 to +70     |       |

| Operating Temperature Under Bias         | _      |              | ·c    |

| Storage Temperature                      | TSTG   | -65 to +150  |       |

|                                          |        | -0.5 to +0.5 | V     |

| Voltage on I/O Pins Referenced to Ground |        | 0.5          | Watts |

| Power Dissipation                        |        | 1 32         | 1     |

Note 1: Stresses greater than those listed in this table may cause permanent damage to the device. These represent a stress rating only. Operation of the device at these or any other conditions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.

# ELECTRICAL CHARACTERISTICS DC CHARACTERISTICS (VCC = 5V ± 10%,TA=0°C to 70°C unless otherwise stated)

| Parameter Parameter           | Symbol          | Test Conditions                                 | Min           | Тур | Max | Unit    |

|-------------------------------|-----------------|-------------------------------------------------|---------------|-----|-----|---------|

|                               |                 | V <sub>C</sub> C = 5V                           | _             | -   | 0.8 | V       |

| Input Low Voltage             | V <sub>IL</sub> | VCC = 5V                                        | 2.0           |     | -   | V       |

| Input High Voltage            | VIH             | VIN = 0V                                        | -30 (1)       | -   | 5   | μА      |

| Input Low Current (FS0, FS1)  | III             | VIN = VCC                                       | -50 (1)<br>-5 | -   | 5   | μА      |

| Input High Current (FS0, FS1) | IH              |                                                 | -5<br>-5      | _   | 5   | μА      |

| Input Low Current (IN, FBIN)  | III             | $V_{IN} = 0V$                                   | -5<br>-5      | _   | 5   | μА      |

| Input High Current (IN, FBIN) |                 | $V_{IN} = V_{CC}$                               | -5            | _   | 0.4 | v       |

| Output Low Voltage            | VOL             | $I_{OL} = 12 \text{ mA}$                        | -<br>Vac 4V   | _   | -   | v       |

| Output High Voltage           | VOH             | $I_{OH} = -1 \text{ mA}, V_{DD} = 5.0V$         | VCC4V         |     | _   | v       |

| Output High Voltage           | VOH             | $I_{OH} = -4 \text{ mA}, V_{DD} = 5.0 \text{V}$ | VCC8V         | _   |     | v       |

| Output High Voltage           | VOH             | $I_{OH} = -12 \text{ mA}$                       | 2.4           | 20  | 50  | mA      |

| Supply Current                | ICC             | Unloaded, 100MHz                                | -             | 20  | 30  | 1 111/2 |

Note 1: Pins FS0, FS1 include an internal pull-up resistor.

#### **ARACTERISTICS**

| Parameter                     | Symbol            | Test Conditions       | Min          | Тур   | Max | Unit         |

|-------------------------------|-------------------|-----------------------|--------------|-------|-----|--------------|

| lock Rise Time. Note 1        | ICLK <sub>r</sub> |                       | <del> </del> | 1 31  | 10  | <del> </del> |

| lock Fall Time. Note 1        | ICLKf             |                       |              | -     | i   | ns           |

| Rise time, 0.8 to 2.0V        | tr                | 15 pf load            | -            | -     | 10  | ns           |

| e, 20% to 80% VCC             | tr                | 15 pf load            | -            | 1     | 2   | ns           |

| Fall time, 2.0 to 0.8V        | tf                | 15 pf load            | -            | 2     | 4   | ns           |

| , 80% to 20% V <sub>CC</sub>  |                   | , .                   | -            | 1     | 2   | ns           |

| Duty cycle, <b>w</b> 42C70-01 | tf                | 15 pf load            | -            | 2     | 4   | ns           |

| Juty cycle, <b>w</b> 42C70-02 | dt                | 15 pf load. Note 2, 3 | 40           | 48/52 | 60  | %            |

|                               | dt                | 15 pf load. Note 2, 3 | 45           | 49/51 | 55  | %            |

| gma                           | $T_{1s}$          |                       | -500         | ±120  | 300 | ps           |

| olute                         | Tabs              | For CLK1 > 10MHz      | -2%          | ±250  | 500 | ps           |

| olute                         | Tabs              | For CLK1 < 10MHz      |              |       | 2   | %            |

| quency. Note 4                | f                 |                       | 1            |       | 120 | MHz          |

| requency CLK1. Note 5         | fo                | ш42С70-01, -04        | 10           |       | 120 | i            |

| requency CLK1. Note 5         | fo                | ш42С70-02, -05        | 2.5          |       |     | MHz          |

| V skew                        | tskew1            | Note 2, 6. Input rise | -1           | 0.4   | 30  | MHz          |

|                               | SREWI             | time <5ns             | -1           | 0.4   | 1   | ns           |

| 1 skew                        | tskew1            | Note 2, 6. Input rise |              | 0.4   | _   |              |

|                               | SKEWI             | time <10ns            | -2           | 0.6   | 2   | ns           |

| LK2 skew                      |                   |                       | 1            | 1     |     |              |

| car input rice and 6-11 ti    | tskew2            | Note 2, 4             | -1           | 0.4   | 1   | ns           |

ger input rise and fall time will degrade skew and jitter performance.

a.c. specifications are measured with a  $50\Omega$  transmission line, load terminated with  $50\Omega$  to 1.4V

y Cycle is measured at 1.4 V.

it frequency is limited by output frequency range and input to output frequency multiplication factor ch is determined by circuit configuration).

ay be possible to operate the w42C70 outside of these ranges. Consult IC WORKS for your specific ication.

$<sup>\</sup>prime$  measured at 1.4V on rising edges.

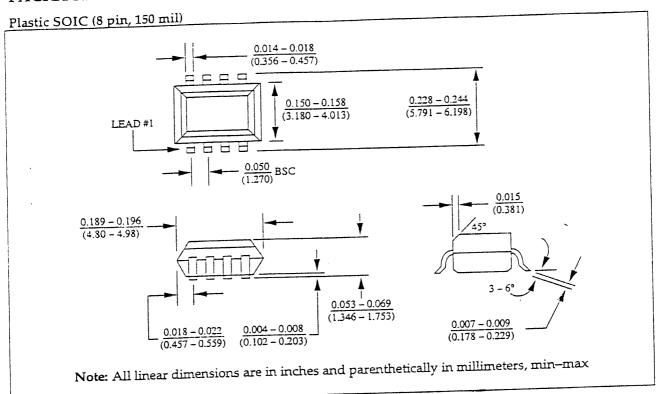

# PACKAGING INFORMATION

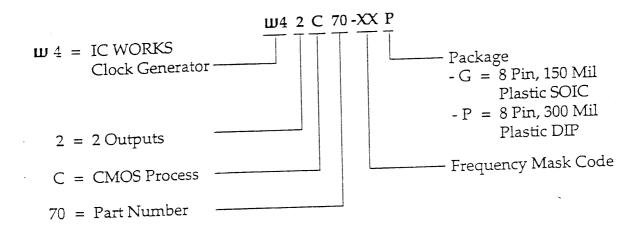

# ORDERING INFORMATION

# VALID PART NUMBERS

**W**42C70-01G **W**42C70-01P

11142C70-02G ш42С70-02Р

ш42C70-03G ш42C70-03P

ш42C70-04G ш42С70-04Р

**w**42C70-05G ш42C70-05P

IC WORKS, Inc. 3725 N. First Street San Jose, CA 95134-1700 Tel: (408) 922-0202

Fax: (408) 922-0833

IC WORKS, Inc. reserves the right to amend or discontinue this product without notice. Circuit and timing diagrams used to describe IC WORKS product operations and applications are included as a means of illustrating a typical product application. Complete information for design purposes is not necessarily given. This information has been carefully checked and is believed to be entirely reliable. IC WORKS, however, will not assume any responsibility for inaccuracies.

#### LIFE SUPPORT APPLICATIONS:

IC WORKS products are not designed for use in life support applications, devices, or systems where malfunctions of the IC WORKS product can reasonably be expected to result in personal injury. IC WORKS customers using or selling IC WORKS products for use in such applications do so at their own risk and agree to fully indemnify IC WORKS for any damages resulting in such improper use or sale.

Document No. 42C70/00/0195