|                                                                                                 |                                                                            |                                        |                  |                              |                                      |                                |                   | F                | REVIS           | IONS             |                    |                      |                          |                               |                                                  |                                          |                                                |                              |                             |     |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------|------------------|------------------------------|--------------------------------------|--------------------------------|-------------------|------------------|-----------------|------------------|--------------------|----------------------|--------------------------|-------------------------------|--------------------------------------------------|------------------------------------------|------------------------------------------------|------------------------------|-----------------------------|-----|

| LTR                                                                                             | _                                                                          | DESCRIPTION                            |                  |                              |                                      |                                |                   | D                | ATE (           | YR-MO-           | DA)                |                      | APP                      | ROVE                          | )                                                |                                          |                                                |                              |                             |     |

| Α                                                                                               | Cha                                                                        | ed dev<br>nges to<br>orial ch          | o table          | : III, an                    | d char                               | 4. Ted<br>ges to               | chnicia<br>reflec | l chan<br>t MIL- | ges to<br>H-385 | 1.3 ar<br>34 pro | nd table<br>cessin | e I.<br>g.           | 90-10-10                 |                               | 0 G. Lude                                        |                                          |                                                |                              |                             |     |

| В                                                                                               | Mad<br>Edite                                                               | e corre                                | ection<br>anges  | to the<br>throu              | lead le<br>ghout.                    | ngth c                         | n figu            | re 2 fo          | r case          | outline          | e Y.               |                      |                          | 91-1                          | 11-25                                            |                                          |                                                | G.                           | Lude                        |     |

| С                                                                                               | dime                                                                       | case o<br>ensions<br>rminal            | s for ca         | ase ou                       | tlines 2                             | ( and                          | Y. Ma             | ke tec           | hnical          | chang            | nge<br>es to f     | igure                |                          | 93-0                          | 03-10                                            |                                          |                                                | K. Co                        | ottongir                    | n   |

| D                                                                                               | Add<br>char                                                                | case on ges to .?                      | outline<br>table | T. Ma                        | ake cha                              | anges<br>packa                 | to par<br>ge hei  | agrapl           | 1.4.<br>case    | Make<br>outline  | X from             | n .25                |                          | 93-0                          | )7-27                                            |                                          |                                                | K. Co                        | ottongir                    | n   |

| E                                                                                               | Cha                                                                        | nges ir                                | n acco           | rdance                       | e with I                             | NOR 5                          | 962-F             | 1077-9           | 4.              |                  |                    | 1.                   |                          | 93-1                          | 2-22                                             |                                          |                                                | K. Cc                        | ottongir                    | n   |

| F                                                                                               |                                                                            | nges ir                                |                  |                              |                                      |                                |                   |                  |                 |                  |                    |                      |                          |                               | 1-16                                             |                                          |                                                |                              | ottongir                    |     |

| G                                                                                               | Cha                                                                        | nges ir                                | n acco           | rdance                       | with I                               | NOR 5                          | 962-F             | 119-9            | 5               |                  |                    |                      |                          |                               | )4-27                                            |                                          |                                                |                              | ottongir                    |     |

| Н                                                                                               | Corr                                                                       | ect ca                                 | se out           | line T p                     | oackaç                               | je heig                        | ght dim           | ensior           | 1 from          | .150 iı          | nches              | to                   |                          | 97-0                          | )3-04                                            |                                          |                                                |                              | ottong                      |     |

|                                                                                                 |                                                                            | 1                                      | 1                |                              |                                      |                                | <b>T</b>          | -                |                 | ···              |                    |                      |                          |                               |                                                  |                                          |                                                |                              |                             |     |

| REV<br>SHEET                                                                                    |                                                                            |                                        |                  |                              |                                      |                                |                   |                  |                 |                  |                    |                      |                          |                               |                                                  |                                          |                                                |                              |                             |     |

|                                                                                                 | Н                                                                          | Н                                      | н                | Н                            | Н                                    | Н                              | н                 | Н                | Н               | Н                | Н                  | Н                    | Н                        | Н                             | Н                                                | Н                                        | H                                              | H                            | Н                           |     |

| SHEET                                                                                           | H 15                                                                       | H<br>16                                | H<br>17          | H 18                         | H<br>19                              | H<br>20                        | H<br>21           | H 22             | H<br>23         | H 24             | H<br>25            | H 26                 | H 27                     | H<br>28                       | H<br>29                                          | H<br>30                                  | H<br>31                                        | H<br>32                      | H<br>33                     |     |

| SHEET REV SHEET REV STATE                                                                       | 15<br>JS                                                                   | <del></del>                            |                  |                              | 19                                   |                                |                   | <del></del>      |                 | <u> </u>         |                    | $\vdash$             |                          | <u> </u>                      | <del>                                     </del> | 1                                        | <del></del>                                    | -                            |                             | ŀ   |

| SHEET<br>REV<br>SHEET                                                                           | 15<br>JS                                                                   | <del></del>                            |                  | 18<br>REV                    | 19                                   |                                | 21                | 22               | 23              | 24               | 25                 | 26                   | 27                       | 28                            | 29                                               | 30                                       | 31                                             | 32                           | 33                          | F 1 |

| SHEET REV SHEET REV STATE                                                                       | 15<br>JS                                                                   | <del></del>                            |                  | 18 REV SHE                   | 19<br>/                              | 20<br>BY                       | 21<br>H           | 22<br>H          | 23<br>H         | 24<br>H          | 25<br>H<br>5       | 26<br>H<br>6         | 27<br>H<br>7             | 28<br>H<br>8                  | 29<br>H<br>9                                     | 30<br>H<br>10<br>NTER                    | 31<br>H<br>11                                  | 32<br>H<br>12<br>JMBU        | 33<br>H<br>13               |     |

| SHEET REV SHEET REV STATI OF SHEET: PMIC N/A STA                                                | JS<br>S<br>NDA<br>OCIR                                                     | RD<br>CUI                              | 17               | 18 REV SHE PREI Stev         | 19<br>V<br>EET                       | 20<br>BY<br>ncan               | 21<br>H           | 22<br>H          | 23<br>H         | 24<br>H          | 25<br>H<br>5       | 26<br>H<br>6         | 27<br>H<br>7             | 28<br>H<br>8                  | 29<br>H<br>9                                     | 30<br>H<br>10                            | 31<br>H<br>11                                  | 32<br>H<br>12<br>JMBU        | 33<br>H<br>13               |     |

| SHEET REV SHEET REV STATE OF SHEET PMIC N/A STA MICRO DR THIS DRAW FOR                          | JS<br>S<br>NDA<br>OCIR<br>AWIN<br>ING IS A<br>USE BY                       | RD<br>CUITIG                           | 17<br><b>Г</b>   | 18 RE\ SHE PREI Stev CHE Mic | 19 V EET PAREC e L. Du               | BY ncan BY Jones               | 21<br>H           | 22<br>H          | 23<br>H         | 24<br>H<br>4     | 25<br>H<br>5       | 26<br>H<br>6<br>DEFE | 27 H 7 NSE S             | 28<br>H<br>8<br>SUPPL<br>MBUS | 29 H 9                                           | 30<br>H<br>10<br>NTER<br>2 432           | 31<br>H<br>11<br>COLU<br>16-50                 | 32<br>H<br>12<br>JMBU        | 33<br>H<br>13               |     |

| SHEET REV SHEET REV STATE OF SHEET PMIC N/A STA MICRE DR THIS DRAW FOR                          | JS<br>S<br>NDA<br>OCIR<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES ( | RD<br>CUITION IN ALLAIR ALL ITS OF THE | 17  F  BLE       | 18 REN SHE PREI Stev CHE Mic | 19 V EET PARED e L. Du CKED chael C. | BY Jones BY Lude               | 21<br>H           | 22<br>H<br>2     | 23<br>H         | 24<br>H<br>4     | 25<br>H<br>5       | 26<br>H<br>6<br>DEFE | 27 H 7 NSE S             | 28 H 8 SUPPL MBUS             | 29 H 9                                           | 30<br>H<br>10<br>NTER<br>O 4322<br>IEAR, | 31<br>H<br>11<br>COLU<br>16-50<br>MIL-<br>INAL | 32<br>H<br>12<br>JMBU:<br>00 | 33<br>H<br>13<br>S<br>1553, |     |

| SHEET REV SHEET REV STATE OF SHEET  PMIC N/A  STA MICRE DR  THIS DRAW FOR DEP, AND AGE DEPARTME | JS<br>S<br>NDA<br>OCIR<br>AWIN<br>ING IS A<br>USE BY<br>ARTMEN<br>ENCIES ( | RD<br>CUITION IN ALLAIR ALL ITS OF THE | 17  F  BLE       | 18 REN SHE Stev CHE Mic      | 19 V EET PARED e L. Du CKED chael C. | BY ncan BY Jones BY Lude APPRO | 21<br>H<br>1      | 22<br>H<br>2     | 23<br>H         | H 4 MIC BC/      | 25<br>H<br>5       | 26 H 6 DEFE          | H 7  NSE S COLUIT  T, HY | 28 H 8 SUPPL MBUS             | 29 H 9                                           | 30<br>H<br>10<br>NTER<br>O 4322<br>IEAR, | 31<br>H<br>11<br>COLU<br>16-50<br>MIL-<br>INAL | 32<br>H<br>12<br>JMBU        | 33<br>H<br>13<br>S<br>1553, |     |

DESC FORM 193

JUL 94

<u>DISTRIBUTION STATEMENT A</u>. Approved for public release; distribution is unlimited.

5962-E064-97

#### 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for class H hybrid microcircuits to be processed in accordance with MIL-PRF-38534 and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN).

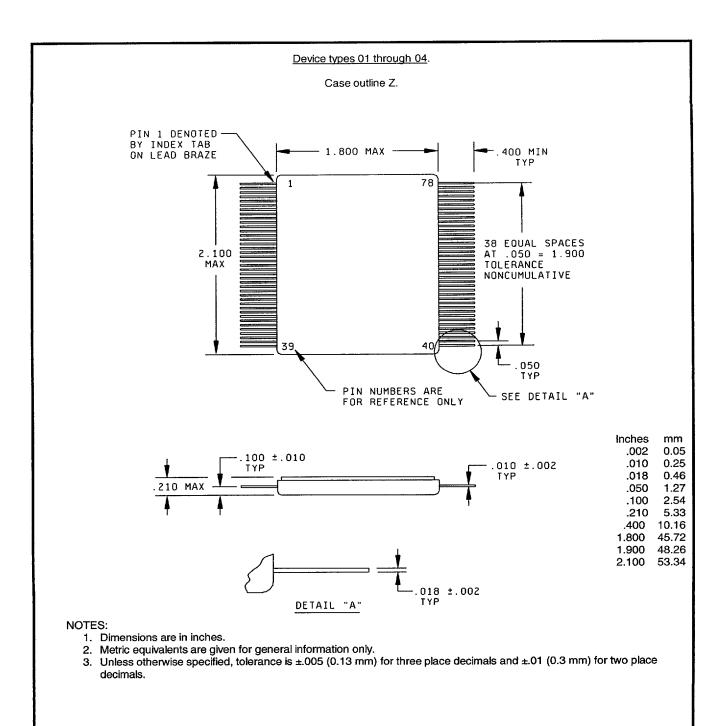

- 1.2 PIN. The PIN shall be as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number     | Circuit function                                              |

|-------------|--------------------|---------------------------------------------------------------|

| 01          | BUS61553, BUS61563 | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal     |

| 02          | BUS61554, BUS61564 | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal     |

| 03          | BUS61555, BUS61565 | MIL-STD-1553, BC/RTU/MT, transceiver multiplexed terminal     |

| 04          | BUS61556           | MIL-STD-1553, BC/RTU/MT, transceiverless multiplexed terminal |

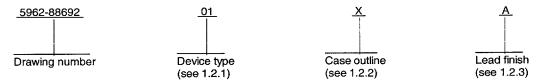

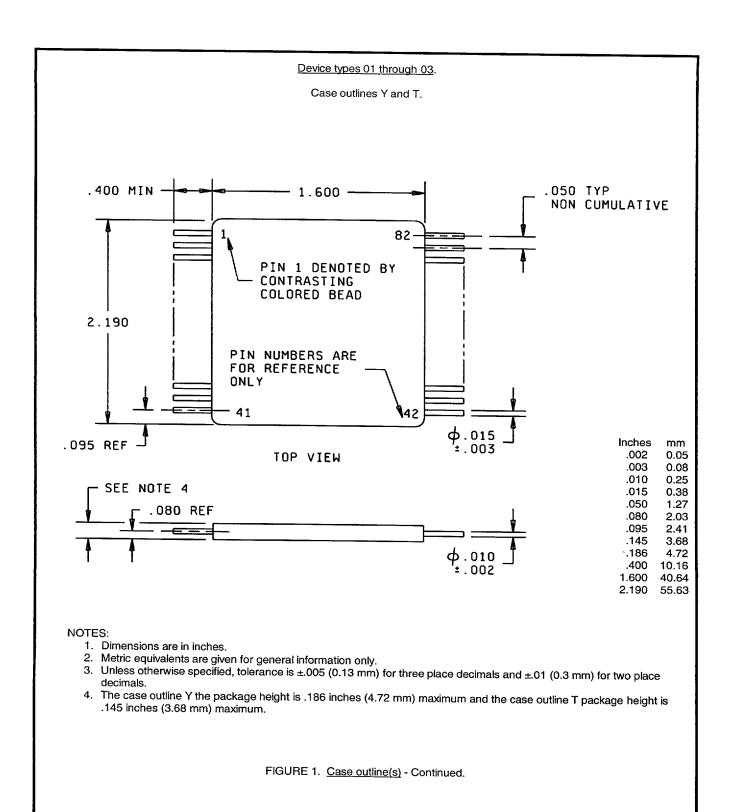

1.2.2 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style |

|----------------|------------------------|------------------|---------------|

| Т              | See figure 1           | 82               | Flat pack     |

| X              | See figure 1           | 78               | Dual-in-line  |

| Υ              | See figure 1           | 82               | Flat pack     |

| Z              | See figure 1           | 78               | Flat pack     |

- 1.2.3 Lead finish. The lead finish shall be as specified in MIL-PRF-38534.

- 1.3 Absolute maximum ratings. 1/

| Supply voltage range:  V <sub>CC</sub> (device types 01 through 03)  V <sub>EE</sub> (device types 01 and 02)  Logic input voltage range (V <sub>DD</sub> ) | -0.5 V dc to +7.0 V dc<br>+0.3 V dc to -18 V dc<br>-0.5 V dc to +7.0 V dc |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Power dissipation (P <sub>D</sub> ): 2/3/<br>Devices type 01 and 02                                                                                         | 810 mW                                                                    |

| Device type 03                                                                                                                                              | 120 mW                                                                    |

| Device type 04                                                                                                                                              | 100 mW<br>-65°C to +150°C                                                 |

| Storage temperature range                                                                                                                                   | +300°C                                                                    |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ ): 3/                                                                                                  |                                                                           |

| Devices types 01 and 02                                                                                                                                     | 5.7°C/W                                                                   |

| Device type 03                                                                                                                                              | 112°C/W                                                                   |

| Device type 04                                                                                                                                              | 11.6°C/W                                                                  |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

2/ Applies up to  $T_C = +125^{\circ}C$ .

3/ Hottest die.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br><b>A</b> |                     | 5962-88692 |

|-------------------------------------------------------------|------------------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>H | SHEET 2    |

#### 1.4 Recommended operating conditions.

Supply voltage range:

VCC (device types 01 and 02)

+4.5 V dc to +5.5 V dc

VCC (device type 03)

+4.75 V dc to +5.5 V dc

VEE (device type 01)

-14.25 V dc to -15.75 V dc

VEE (device type 02)

-11.40 V dc to -12.60 V dc

Logic input voltage range:

VDD (device types 01, 02, and 04)

+4.5 V dc to +5.5 V dc

VDD (device type 03)

+4.75 V dc to +5.5 V dc

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbook.</u> The following specification, standards, and handbook form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those listed in the issue of the Department of Defense Index of Specifications and Standards (DoDISS) and supplement thereto, cited in the solitation.

#### **SPECIFICATION**

#### DEPARTMENT OF DEFENSE

MIL-PRF-38534 - Hybrid Microcircuits, General Specification for.

#### **STANDARDS**

## DEPARTMENT OF DEFENSE

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-973 - Configuration Management. MIL-STD-1835 - Microcircuit Case Outlines.

#### **HANDBOOK**

# DEPARTMENT OF DEFENSE

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Unless otherwise indicated, copies of the specification, standards, and handbook are available from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000

| SIZE<br><b>A</b> |                     | 5962-88692 |

|------------------|---------------------|------------|

| :                | REVISION LEVEL<br>H | SHEET<br>3 |

DESC FORM 193A JUL 94

9004708 0030295 86%

#### 3. REQUIREMENTS

- 3.1 Item requirements. The individual item performance requirements for device classes D, E, G, H, and K shall be in accordance with MIL-PRF-38534. Compliance with MIL-PRF-38534 may include the performance of all tests herein or as designated in the device manufacturer's Quality Management (QM) plan or as designated for the applicable device class. Therefore, the tests and inspections herein may not be performed for the applicable device class (see MIL-PRF-38534). Futhermore, the manufacturers may take exceptions or use alternate methods to the tests and inspections herein and not perform them. However, the performance requirements as defined in MIL-PRF-38534 shall be met for the applicable device class.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38534 and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein and figure 1.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 2.

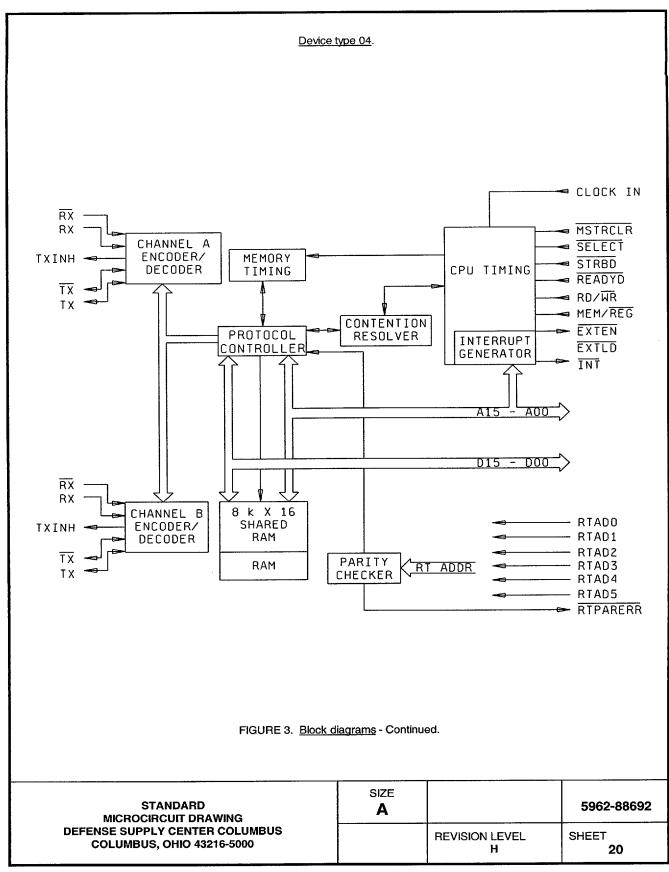

- 3.2.3 Block diagram(s). The block diagram(s) shall be as specified on figure 3.

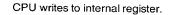

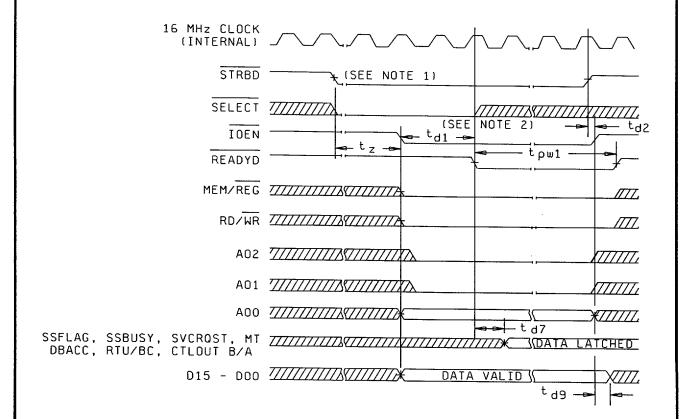

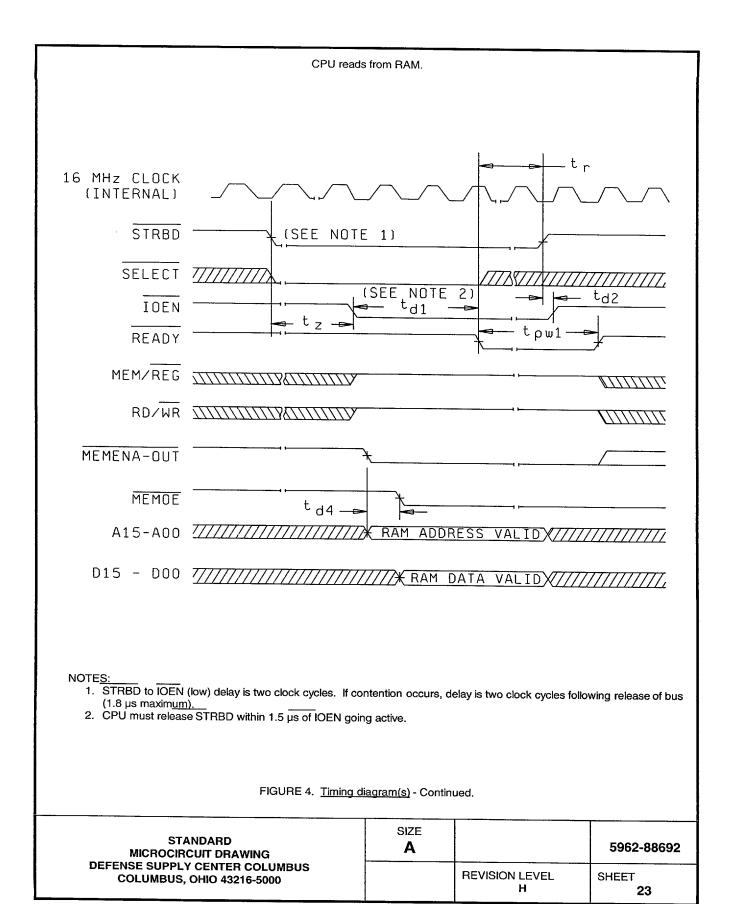

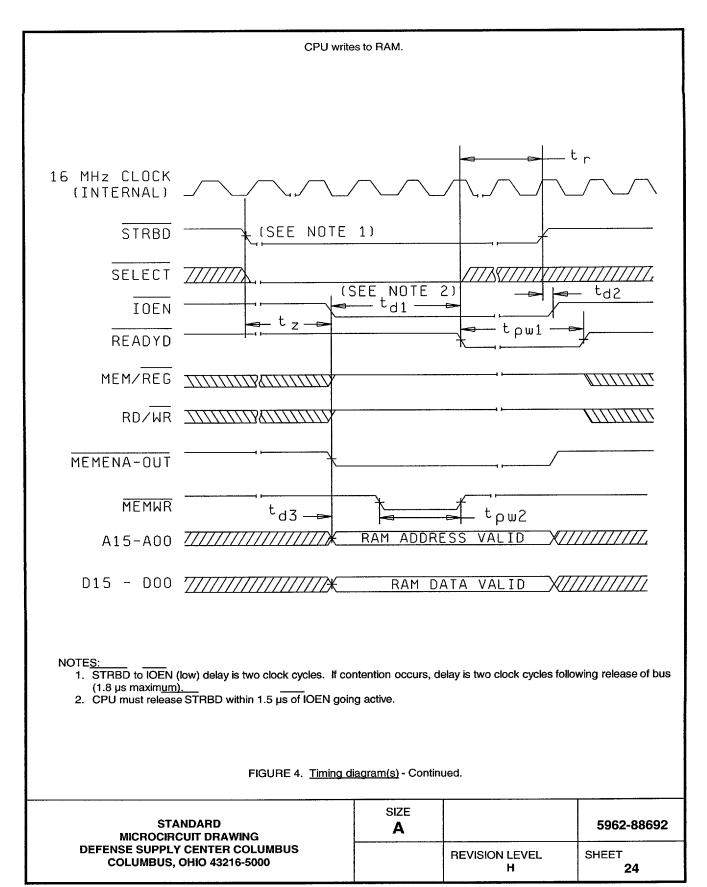

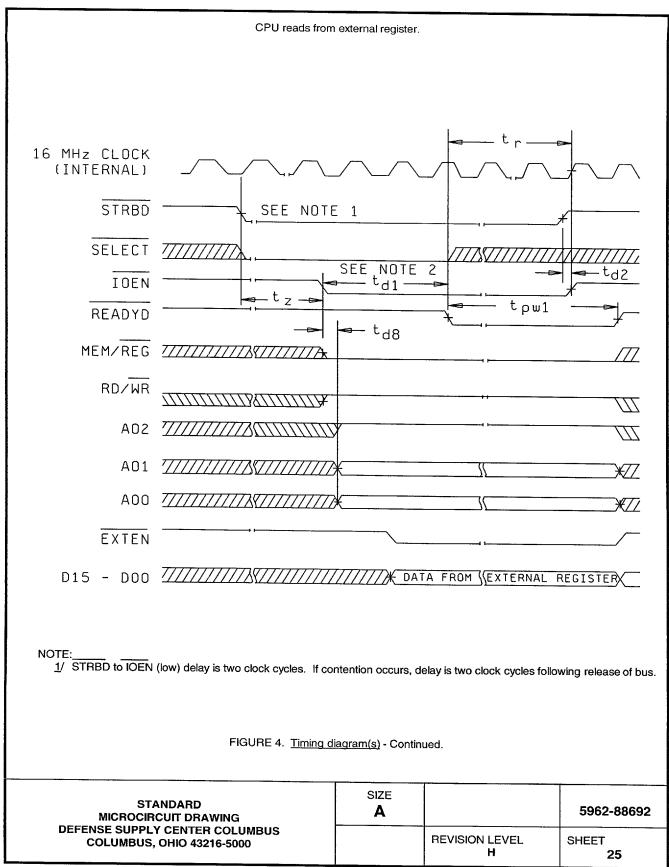

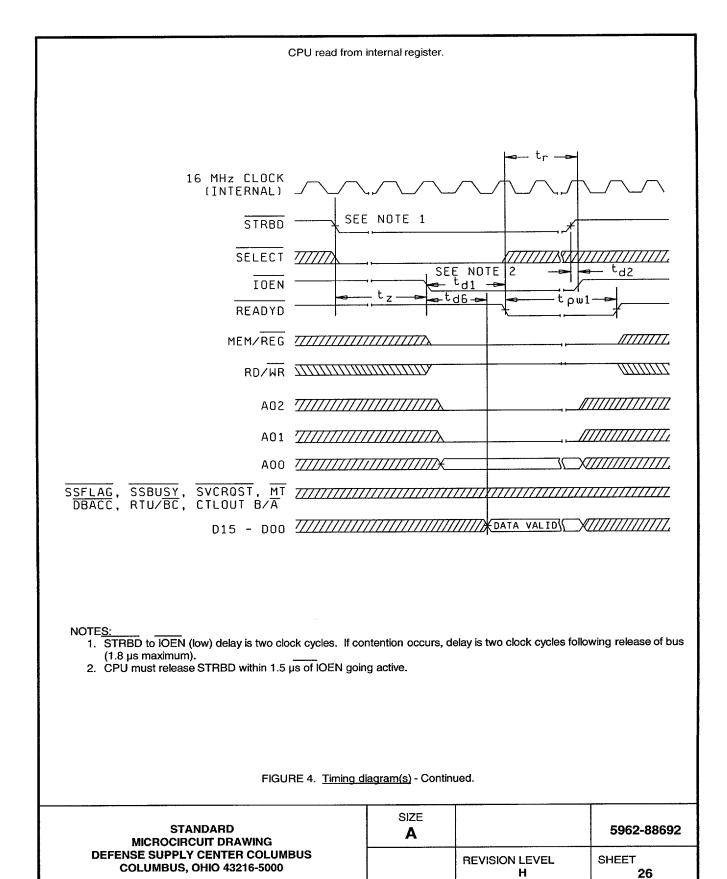

- 3.2.4 Timing diagram(s). The timing diagram(s) shall be as specified on figure 4.

- 3.3 Electrical performance characteristics. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full specified operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 Marking of Device(s). Marking of device(s) shall be in accordance with MIL-PRF-38534. The device shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's vendor similar PIN may also be marked as listed in QML-38534.

- 3.6 <u>Data</u>. In addition to the general performance requirements of MIL-PRF-38534, the manufacturer of the device described herein shall maintain the electrical test data (variables format) from the initial quality conformance inspection group A lot sample, for each device type listed herein. Also, the data should include a summary of all parameters manually tested, and for those which, if any, are guaranteed. This data shall be maintained under document revision level control by the manufacturer and be made available to the preparing activity (DSCC-VA) upon request.

- 3.7 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to supply to this drawing. The certificate of compliance (original copy) submitted to DSCC-VA shall affirm that the manufacturer's product meets the performance requirements of MIL-PRF-38534 and herein.

- 3.8 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-PRF-38534 shall be provided with each lot of microcircuits delivered to this drawing.

### 4. QUALITY ASSURANCE PROVISIONS

4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-PRF-38534 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

STANDARD

MICROCIRCUIT DRAWING

DEFENSE SUPPLY CENTER COLUMBUS

COLUMBUS, OHIO 43216-5000

| SIZE<br><b>A</b> |                     | 5962-88692 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>H | SHEET<br>4 |

DESC FORM 193A JUL 94

9004708 0030296 7T8 **==**

| Test                                                                            | Symbol           | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                                                                                     | Group A subgroups | Device<br>type | Limits |       | Unit    |

|---------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|-------|---------|

|                                                                                 |                  | unless otherwise specified                                                                                                                                                                                   |                   |                | Min    | Max   |         |

| Logic supply current, idle 2/                                                   | I <sub>DD</sub>  | V <sub>CC</sub> = 5.5 V, V <sub>DD</sub> = 5.5 V                                                                                                                                                             | 1,2,3             | 01,02          | 5.0    | 170   | _ mA    |

| idle <u>2</u> /                                                                 |                  | VEE = -15 V for device<br>type 01 and -12 V for                                                                                                                                                              |                   | 03             | 50.0   | 170   |         |

|                                                                                 | <u></u>          | device type 02,<br>loL <sub>1</sub> = 3.6 mA,                                                                                                                                                                |                   | 04             | 5.0    | 60    |         |

| Positive supply current, idle 3/                                                | lCC1             | $ OH1  = -400 \mu\text{A},$<br> OL2  = 2.0 mA,<br> OL3  = 4.0 mA,                                                                                                                                            |                   | 01,02          | 5.0    | 170   | mA<br>- |

|                                                                                 |                  | f <sub>IN</sub> = 16 MHz                                                                                                                                                                                     |                   | 03             | 50.0   | 170   |         |

| Negative supply current, idle 4/                                                | l <sub>EE1</sub> |                                                                                                                                                                                                              |                   | 01,02          | -5.0   | -80   | mA      |

| Positive supply current, channel A = 25                                         | lCC2             |                                                                                                                                                                                                              |                   | 01,02          | 5.0    | 170   | mA      |

| percent duty cycle,<br>channel B = idle 3/                                      |                  |                                                                                                                                                                                                              |                   | 03             | 50.0   | 170   |         |

| Positive supply current, channel B = 25                                         | Іссз             |                                                                                                                                                                                                              |                   | 01,02          | 5.0    | 170   | mA      |

| percent duty cycle,<br>channel A = idle 3/                                      |                  | _                                                                                                                                                                                                            |                   | 03             | 50.0   | 170   |         |

| Negative supply current, channel A = 25 percent duty cycle, channel B = idle 4/ | I <sub>EE2</sub> |                                                                                                                                                                                                              |                   | 01,02          | -25    | -130  | mA      |

| Negative supply current, channel B = 25 percent duty cycle, channel A = idle 4/ | I <sub>EE3</sub> |                                                                                                                                                                                                              |                   | 01,02          | -25    | -130  | mA      |

| High level output voltage <u>5</u> /                                            | VOH              | $V_{CC} = 4.5 \text{ V}, V_{DD} = 4.5 \text{ V}$ $V_{IH} = 2.7 \text{ V}, V_{IL} = 0.4 \text{ V},$ $V_{EE} = -15 \text{ V}$ for device type 01 and -12 V for device type 02, $I_{OH} = -400  \mu\text{A}$ 6/ | /,                | All            | 2      |       | V       |

|                                                                                 | STANDAR          |                                                                                                                                                                                                              | SIZE<br><b>A</b>  | 10-10-         |        | 596   | 62-8869 |

| DEFENSE SUF                                                                     |                  | ER COLUMBUS                                                                                                                                                                                                  | 7.                | REVISION L     | FVFI   | SHEE  |         |

| COLUMB                                                                          | US, OHIO         | 13216-5000                                                                                                                                                                                                   |                   | HEVIOIONE      |        | 0,166 | ์ 5     |

**■ 9004708 0030297 634 ■**

| Test                                    | Symbol                   | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                 |                            | Group A<br>subgroups | Device<br>type | Limits |       | Unit   |

|-----------------------------------------|--------------------------|------------------------------------------------------------------------------------------|----------------------------|----------------------|----------------|--------|-------|--------|

|                                         |                          | unless otherw                                                                            | ise specified              | Jacgioapo            | ,,,po          | Min    | Max   |        |

| Low level output voltage 7/             | V <sub>OL1</sub>         | V <sub>CC</sub> = 4.5 V,<br>V <sub>DD</sub> = 4.5 V,<br>V <sub>IH</sub> = 2.7 V,         |                            | 1,2,3                | All            |        | 0.4   | V      |

| Low level output voltage 8/             | V <sub>OL2</sub>         | VIL = 0.4 V, VEE = -15 V for device type 01 and -12 V for device type 02 6/              | I <sub>OL2</sub> = 2.0 m/s |                      |                |        | 0.4   | V      |

| Low level output voltage <u>9</u> /     | V <sub>OL3</sub>         |                                                                                          | I <sub>OL3</sub> = 4.0 m/  |                      |                |        | 0.4   | V      |

| High level input<br>current <u>10</u> / | liH1                     | V <sub>CC</sub> = 5.5 V, V<br>V <sub>IN</sub> = 2.7 V, V <sub>I</sub><br>for device type | <sub>EE</sub> = -15 V      |                      |                | -30    | -220  | μА     |

| High level input<br>current <u>11</u> / | liH2                     | -12 V for devi                                                                           |                            |                      |                | -20    | -630  | μА     |

| High level input current 12/            | Інз                      | -                                                                                        |                            |                      |                | -50    | -200  | μА     |

| High level input current 13/            | liH4                     |                                                                                          |                            |                      |                | -10    | 10    | μА     |

| High level input current 14/            | I <sub>IH5</sub>         |                                                                                          |                            |                      |                | -20    | 20    | μА     |

| High level input<br>current <u>15</u> / | lіН6                     |                                                                                          |                            |                      |                | -40    | -220  | μA     |

| Low level input current 7/              | lıL1                     | V <sub>CC</sub> = 5.5 V, V<br>V <sub>IN</sub> = 0.4 V, V <sub>I</sub><br>for device type | <sub>EE</sub> = -15 V      |                      |                | -100   | -400  | μА     |

| Low level input current 11/             | l <sub>IL2</sub>         | -12 V for device                                                                         | ce type 02                 |                      |                | -35    | -700  | μА     |

| Low level input<br>current <u>12</u> /  | IIL3                     |                                                                                          |                            |                      |                | -100   | -400  | μА     |

| See footnotes at end o                  | of table.                |                                                                                          |                            | 1                    | ,              | •      |       | •      |

| MICE                                    | STANDARI<br>ROCIRCUIT DI |                                                                                          |                            | SIZE<br><b>A</b>     |                |        | 5962  | 2-8869 |

| DEFENSE S                               |                          | ER COLUMBUS                                                                              | •                          |                      | REVISION L     |        | SHEET | 6      |

| Test                                             | Symbol                          | Conditions <u>1</u> /<br>-55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                                                               | Group A<br>subgroups | Device<br>type | Limits              |     | Unit          |

|--------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------------------|-----|---------------|

|                                                  |                                 | unless otherwise specified                                                                                                                                                             |                      |                | Min                 | Max |               |

| Low level input<br>current <u>13</u> /           | l <sub>IL4</sub>                | V <sub>CC</sub> = 5.5 V, V <sub>DD</sub> = 5.5 V,<br>V <sub>IN</sub> = 0.4 V V <sub>EE</sub> = -15 V<br>for device type 01 and                                                         | 1,2,3                | All            | -10                 | 10  | μΑ            |

| Low level input<br>current <u>14</u> /           | I <sub>IL5</sub>                | -12 V for device type 02                                                                                                                                                               |                      |                | -20                 | 20  | μΑ            |

| Receiver differential input impedance 16/17/     | Z <sub>IN</sub>                 | DC to 1.0 MHz                                                                                                                                                                          | 4,5,6                | 01,02,03       | 5.0                 |     | kΩ            |

| Receiver input threshold voltage                 | V <sub>TH</sub>                 | Transformer coupled                                                                                                                                                                    |                      |                | 650                 | 860 | mV p-p        |

| Receiver differential input voltage 16/17/       | V <sub>IN</sub>                 | DC to 1.0 MHz                                                                                                                                                                          |                      |                |                     | 40  | V p-p         |

| Receiver common mode rejection 17/ratio          | CMRR                            | DC to 2.0 MHz                                                                                                                                                                          |                      |                | 40                  |     | dB            |

| Transmitter<br>differential output<br>voltage    | vo                              | Transformer coupled, measured across the stub                                                                                                                                          |                      |                | 18                  | 27  | V p-p         |

| Transmitter sinusoidal output rise and fall time | t <sub>r</sub> , t <sub>f</sub> |                                                                                                                                                                                        |                      |                | 100                 | 300 | ns            |

| Output offset 17/voltage                         | v <sub>OS</sub>                 |                                                                                                                                                                                        |                      |                | -250                | 250 | mV            |

| Transmitter overshoot                            | VOVRSHT                         |                                                                                                                                                                                        |                      |                | -900                | 900 | mV            |

| Functional test                                  |                                 | V <sub>CC</sub> = 4.5 V, V <sub>DD</sub> = 4.5 V,<br>V <sub>IH</sub> = 2.7 V, V <sub>IL</sub> = 0.4 V<br>V <sub>EE</sub> = -15 V for 01 and<br>-12 V for device type 02,<br><u>6</u> / | 7,8                  | All            |                     |     | pass/fail     |

| See footnotes at end of                          | f table.                        |                                                                                                                                                                                        |                      | -              | <del> </del>        |     |               |

| MICR                                             | STANDAR<br>OCIRCUIT D           | RAWING                                                                                                                                                                                 | SIZE<br><b>A</b>     |                |                     |     | 5962-8869     |

| DEFENSE S                                        | JPPLY CENT<br>IBUS, OHIO        | ER COLUMBUS                                                                                                                                                                            |                      | REVISIO        | N LEVEL<br><b>H</b> | s   | HEET <b>7</b> |

| Test                                           | Symbol           | Conditions 1/<br>-55°C ≤ T <sub>C</sub> ≤ +125°C<br>unless otherwise specified                                                      | Group A subgroups | Device<br>type | Limits       |      | Unit      |  |

|------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------------|------|-----------|--|

|                                                |                  |                                                                                                                                     | j                 |                | Min          | Max  |           |  |

| Delay timing                                   |                  |                                                                                                                                     |                   | 1              | T            |      |           |  |

| READYD low delay<br>(CPU handshake) 17/        | <sup>t</sup> d1  | V <sub>CC</sub> = 4.5 V, V <sub>DD</sub> = 4.5 V <sub>IH</sub> = 2.7 V, V <sub>IL</sub> = 0.4 V, V <sub>FF</sub> = -15 V for device | V, 9,10,11        | All            |              | 150  | ns        |  |

| IOEN high delay<br>(CPU handshake) <u>17</u> / | t <sub>d2</sub>  | type 01 and -12 V for<br>device type 02,<br>IOH = -400 µA,<br>IOL1 = 2.6 mA,                                                        |                   |                |              | 20   | ns        |  |

| CPU MEMWR low <u>17</u> /<br>delay             | t <sub>d3</sub>  | IOL1 = 2.0 IIIA,<br>IOL2 = 2.0 mA,<br>IOL3 = 4.0 mA,<br>see figure 4 6/18/                                                          |                   |                |              | 100  | ns        |  |

| CPU MEMOE low 17/<br>delay                     | t <sub>d4</sub>  |                                                                                                                                     |                   |                |              | 100  | ns        |  |

| EXTLD low delay 17/                            | <sup>t</sup> d5  |                                                                                                                                     |                   |                | 50           |      | ns        |  |

| Internal register 17/<br>delay (read)          | <sup>t</sup> d6  |                                                                                                                                     |                   |                |              | 60   | ns        |  |

| Internal register <u>17</u> /<br>delay (write) | <sup>t</sup> d7  |                                                                                                                                     |                   |                |              | 60   | ns        |  |

| Register data/address 17/<br>setup time        | t <sub>d8</sub>  |                                                                                                                                     |                   |                |              | 30   | ns        |  |

| Register data/address 17/<br>hold time         | t <sub>d9</sub>  |                                                                                                                                     |                   |                |              | 0    | ns        |  |

| Other timing                                   | 1                |                                                                                                                                     | I                 |                | 1            |      |           |  |

| READYD pulse width (CPU handshake)             | t <sub>pw1</sub> | $V_{CC} = 4.5 \text{ V}, V_{DD} = 4.5$<br>$V_{IH} = 2.7 \text{ V}, V_{IL} = 0.4 \text{ V},$<br>$V_{FF} = -15 \text{ V}$ for device  | V, 9,10,11        | All            | 50           |      | ns        |  |

| CPU MEMWR low pulse width                      | t <sub>pw2</sub> | type 01 and -12 V for<br>device type 02,<br>IOH = -400 µA,                                                                          |                   |                | 50           |      | ns        |  |

| EXTLD low pulse width                          | t <sub>pw3</sub> | $I_{OL1} = 2.6 \text{ mA},$<br>$I_{OL2} = 2.0 \text{ mA},$                                                                          |                   |                | 50           |      | ns        |  |

| READYD to STRBD release time                   | t <sub>r</sub>   | I <sub>OL3</sub> = 4.0 mA,<br>see figure 4 <u>6</u> / <u>18</u> /                                                                   |                   |                |              | 1.37 | ns        |  |

| (SELECT X STRBD) to IOEN 17/                   | t <sub>Z</sub>   |                                                                                                                                     |                   |                |              | 1.80 | ns        |  |

| See footnotes at end of table                  | e.               |                                                                                                                                     |                   |                | .1           | Lam  |           |  |

| Si                                             | TANDARD          |                                                                                                                                     | SIZE<br><b>A</b>  |                |              |      | 5962-8869 |  |

| MICROCI<br>DEFENSE SUPPI<br>COLUMBUS           |                  | R COLUMBUS                                                                                                                          |                   | REVISIO        | N LEVEL<br>H | s    | HEET      |  |

■ 9004708 0030300 T59 ■

# TABLE I. <u>Electrical performance characteristics</u> - Continued.

1/ All group A subgroup testing of the same temperature may be performed concurrently.

## 2/ Measured at the following pins:

Device types 01 through 04: Pin 14.

Case Y and T:

Device types 01 through 03: Pin 28.

Case Z:

Device types 01 through 03: Pin 27.

#### 3/ Measured at the following pins:

Case X:

Device types 01 and 03: Pins 58 and 77.

Case Y and T:

Device types 01 through 03: Pins 37 and 46.

Case Z:

Device types 01 through 03: Pins 36 and 43.

#### 4/ Measured at the following pins:

Case X:

Device types 01 and 02: Pins 18 and 39.

Case Y and T:

Device types 01 and 02: Pins 36 and 45.

Case Z:

Device types 01 through 03: Pins 35 and 42.

#### 5/ Measured at the following pins:

Case X:

Device types 01 through 03: Pins 1 through 8, 13, 15 through 17, 22 through 31, 35, 37, 41 through 48,

52 through 57, 60 through 68, 70, 72, 73, 75, and 76.

Device type 04: Pins 1 through 8, 13, 15 through 19, 22 through 31, 35, 37 through 39, 41 through 48,

52 through 58, 60 through 68, 70, 72, 73, and 77.

Device types 01 through 03: Pins 2 through 17, 25 through 27, 29 through 35, 48 through 50, 53, 54, 56, 60, 61, 63 through 80.

Case 7:

Device types 01 through 03: Pins 1 through 16, 24 through 26, 28 through 34, 45 through 47, 50, 51, 53, 57, 58, 60 through 77.

$\underline{6}$ / For device type 03,  $V_{CC} = 4.75 \text{ V}$  and  $V_{DD} = 4.75 \text{ V}$ .

#### 7/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 1 through 8, 22 through 29, 41 through 48, and 60 through 67.

Case Y and T:

Device types 01 through 03: Pins 2 through 17 and 65 through 80.

Device types 01 through 03: Pins 1 through 16, and 62 through 77.

**STANDARD** MICROCIRCUIT DRAWING **DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000**

| SIZE<br><b>A</b> |                     | 5962-88692 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>H | SHEET<br>9 |

DESC FORM 193A **JUL 94**

9004708 0030301 995

### TABLE I. <u>Electrical performance characteristics</u> - Continued.

### 8/ Measured at the following pins:

Case X:

Device types 01 through 03: Pins 13, 15 through 17, 52 through 57, and 70.

Device type 04: Pins 13, 15 through 17, 52 through 58, 70, and 77.

Case Y and T:

Device types 01 through 03: Pins 25 through 27, 29 through 35, and 60.

Case Z:

Device types 01 through 03: Pins 24 through 26, 28 through 34, and 57.

### 9/ Measured at the following pins:

Case X:

Device types 01 through 03: Pins 30, 31, 35, 37, 68, 72, 73, 75, and 76. Device type 04: Pins 18, 19, 30, 31, 35, 38, 39, 68, 72, 73, 75, and 76.

Case Y and T:

Device types 01 through 03: Pins 48 through 50, 53, 54, 56, 61, 63, and 64.

Case Z:

Device types 01 through 03: Pins 45 through 47, 50, 51, 53, 58, 60, and 61.

#### 10/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 1 through 8 and 41 through 48.

Case Y and T:

Device types 01 through 03: Pins 2 through 17.

Case Z:

Device types 01 through 03: Pins 1 through 16.

#### 11/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 33, 34, 36, 71, and 74.

Case Y and T:

Device types 01 through 03: Pins 51, 52, 55, 57, and 58.

Case Z:

Device types 01 through 03: Pins 48, 49, 52, 54, and 55.

### 12/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 9 through 11 and 49 through 51.

Case Y and T:

Device types 01 through 03: Pins 18 through 23.

Case Z:

Device types 01 through 03: Pins 17 through 22.

# 13/ Measured at the following pins:

Case X:

Device types 01 through 03: Pin 12.

Device type 04: Pins 12, 20, 40, 59, and 78.

Case Y and T:

Device types 01 through 03: Pin 24.

Case Z:

Device types 01 through 03: Pin 23.

| STANDARD                       |

|--------------------------------|

| MICROCIRCUIT DRAWING           |

| DEFENSE SUPPLY CENTER COLUMBUS |

| COLUMBUS, OHIO 43216-5000      |

| SIZE<br><b>A</b> |                     | 5962-88692  |

|------------------|---------------------|-------------|

|                  | REVISION LEVEL<br>H | SHEET<br>10 |

DESC FORM 193A JUL 94

■ 9004708 0030302 821 **■**

TABLE I. <u>Electrical performance characteristics</u> - Continued.

14/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 32 and 69.

Case Y and T:

Device types 01 through 03: Pins 59 and 62.

Case Z:

Device types 01 through 03: Pins 56 and 59.

15/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 22 through 29 and 60 through 67.

Case Y and T:

Device types 01 through 03: Pins 65 through 80.

Case Z:

Device types 01 through 03: Pins 62 through 77.

16/ Measured at the following pins:

Case X:

Device types 01 through 04: Pins 20, 40, 59, and 78.

Case Y and T:

Device types 01 through 03: Pins 39, 40, 43, and 44.

Case Z:

Device types 01 through 03: Pins 38 through 41.

17/ Parameter shall be tested as part of the initial characterization of this device and after design and process changes. Parameter shall be guaranteed to limits specified in table I for all lots not specifically tested.

18/ All timing parameters are measured at the 50 percent level of the waveform.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | 11         |

DESC FORM 193A JUL 94

9004708 0030303 768

#### Device types 01 through 04. Case outline X. .075 TYP .25 MAX .075 φ.018 PIN 1.500 78 PLS 1.800 MAX 20 59 Inches mm .018 0.45 2.100 1.27 .050 MAX.075 1.91 2.54 1.900 .100 100 .25 6.4 TYP 1.800 1.500 38.10 1.650 41.91 1.800 45.72 1.900 48.26 2.100 53.34 . 100 PIN NUMBERS ARE BOTTOM VIEW .050 -FOR REFERENCE

### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- Unless otherwise specified, tolerance is ±.005 (0.13 mm) for three place decimals and ±.01 (0.3 mm) for two place decimals.

FIGURE 1. Case outline(s).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | 12         |

DESC FORM 193A JUL 94

9004708 0030304 6T4 **=**

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-88692  |

|-------------------------------------------------------------------------------------------------|------------------|---------------------|-------------|

|                                                                                                 |                  | REVISION LEVEL<br>H | SHEET<br>13 |

**3004708 0030305 530**

FIGURE 1. Case outline(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | <b>14</b>  |

**■ 9004708 0030306 477 ■**

| Device<br>types  | 01 throu                             | igh 03        | Device<br>types    | 01 thro                              | ugh 03                               |

|------------------|--------------------------------------|---------------|--------------------|--------------------------------------|--------------------------------------|

| Case<br>outlines | X                                    | Y and T       | Case<br>outlines   | X                                    | Y and T                              |

| Terminal number  | Terminal                             | symbol        | Terminal<br>number | Terminal symbol                      |                                      |

| 1                | D00                                  | No connection | 22                 | A01                                  | RTAD4                                |

| 2                | D02                                  | D00           | 23                 | A03                                  | RTADP                                |

| 3                | D04                                  | D01           | 24                 | A05                                  | ILLCMD                               |

| 4                | D06                                  | D02           | 25                 | A07                                  | SA/MC-2                              |

| 5                | D08                                  | D03           | 26                 | A09                                  | SA/MC-0                              |

| 6                | D10                                  | D04           | 27                 | A11                                  | SA/MC-4                              |

| 7                | D12                                  | D05           | 28                 | A13                                  | V <sub>DD</sub>                      |

| 8                | D14                                  | D06           | 29                 | A15                                  | SA/MC-3                              |

| 9                | RTAD1                                | D07           | 30                 | МЕМОЕ                                | SA/MC-1                              |

| 10               | RTAD0                                | D08           | 31                 | MEMENA-OUT                           | THIS-RT                              |

| 11               | RTAD4                                | D09           | 32                 | CLOCK IN                             | BCSTRCV                              |

| 12               | ILLCMD                               | D10           | 33                 | MEM/REG                              | RTPARRER                             |

| 13               | SA/MC-0                              | D11           | 34                 | STRBD                                | LMC                                  |

| 14               | V <sub>DD</sub>                      | D12           | 35                 | EXTEN                                | T/R                                  |

| 15               | SA/MC-1                              | D13           | 36                 | RD/WR                                | V <sub>EE</sub> (CH B)<br>(SEE NOTE) |

| 16               | BCSTRCV                              | D14           | 37                 | EXTLD                                | V <sub>CC</sub> (CH B)               |

| 17               | LMC                                  | D15           | 38                 | GNDA                                 | GNDB                                 |

| 18               | V <sub>EE</sub> (CH B)<br>(SEE NOTE) | RTAD1         | 39                 | V <sub>EE</sub> (CH A)<br>(SEE NOTE) | TX/RX-В                              |

| 19               | GNDB                                 | RTAD3         | 40                 | TX/RX-A                              | TX/RX-B                              |

| 20               | TX/RX-B                              | RTAD0         | 41                 | D01                                  | No connection                        |

| 21               | LOGIC GND                            | RTAD2         | 42                 | D03                                  | No connection                        |

NOTE: For device type 03, no connection.

FIGURE 2. Terminal connections.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43216-5000 | SIZE<br><b>A</b> |                     | 5962-88692         |

|-------------------------------------------------------------------------------------------------|------------------|---------------------|--------------------|

|                                                                                                 |                  | REVISION LEVEL<br>H | SHEET<br><b>15</b> |

DESC FORM 193A JUL 94

**9**004708 0030307 303 **3**

| Device<br>types    |                        |                                      | Device<br>types  | 01 throu               | ugh 03        |

|--------------------|------------------------|--------------------------------------|------------------|------------------------|---------------|

| Case<br>outlines   | ×                      | Y and T                              | Case<br>outlines | x                      | Y and T       |

| Terminal<br>number | Termir                 | nal symbol                           | Terminal number  | Terminal symbol        |               |

| 43                 | DO5                    | TX/RX-A                              | 63               | A06                    | MEMOE         |

| 44                 | DO7                    | TX/RX-A                              | 64               | A08                    | MEMWR         |

| 45                 | DO9                    | V <sub>EE</sub> (CH A)               | 65               | A10                    | A15           |

| 46                 | D11                    | (SEE NOTE)<br>V <sub>CC</sub> (CH A) | 66               | A12                    | A14           |

| 47                 | D13                    | GNDA                                 | 67               | A14                    | A13           |

| 48                 | D15                    | TAGEN                                | 68               | MEMWR                  | A12           |

| 49                 | RTAD3                  | EXTLD                                | 69               | MEMENA-IN              | A11           |

| 50                 | RTAD2                  | READYD                               | 70               | INCMD                  | A10           |

| 51                 | RTADP                  | RD/WR                                | 71               | MSTRCLR                | A09           |

| 52                 | SA/MC-2                | SELECT                               | 72               | INT                    | A08           |

| 53                 | SA/MC-4                | EXTEN                                | 73               | IOEN                   | A07           |

| 54                 | SA/MC-3                | IOEN                                 | 74               | SELECT                 | A06           |

| 55                 | THIS-RT                | STRBD                                | 75               | READYD                 | A05           |

| 56                 | RTPARERR               | INT                                  | 76               | TAGEN                  | A04           |

| 57                 | T/R                    | MEM/REG                              | 77               | V <sub>CC</sub> (CH A) | A03           |

| 58                 | V <sub>CC</sub> (CH B) | MSTRCLR                              | 78               | TX/RX-A                | A02           |

| 59                 | TX/RX-B                | CLOCK IN                             | 79               |                        | A01           |

| 60                 | AO0                    | INCMD                                | 80               |                        | A00           |

| 61                 | AO2                    | MEMENA-OUT                           | 81               |                        | LOGIC GND     |

| 62                 | AO4                    | MEMENA-IN                            | 82               |                        | No connection |

NOTE: For ddevice type 03, no connection.

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | <b>16</b>  |

DESC FORM 193A JUL 94

■ 7004708 0030308 24T **■**

| Device type                     |                 |                 | 04              |                 |                 |

|---------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Case outline<br>Terminal number | Termibal symbol | Terminal number | X               | 1               | 1               |

|                                 |                 | reminal number  | Terminal symbol | Terminal number | Terminal symbol |

| 1                               | D00             | 27              | A11             | 53              | SA/MC-4         |

| 2                               | D02             | 28              | A13             | 54              | SA/MC-3         |

| 3                               | D04             | 29              | A15             | 55              | THIS-RT         |

| 4                               | D06             | 30              | мемое           | 56              | RTPARERR        |

| 5                               | D08             | 31              | MEMENA-OUT      | 57              | T/R             |

| 6                               | D10             | 32              | CLOCK IN        | 58              | TXINH-B         |

| 7                               | D12             | 33              | MEM/REG         | 59              | RX-B            |

| 8                               | D14             | 34              | STRBD           | 60              | A00             |

| 9                               | RTAD1           | 35              | EXTEN           | 61              | A02             |

| 10                              | RTAD0           | 36              | RD/WR           | 62              | A04             |

| 11                              | RTAD4           | 37              | EXTLD           | 63              | A06             |

| 12                              | ILLCMD          | 38              | TX-A            | 64              | A08             |

| 13                              | SA/MC-0         | 39              | TX-A            | 65              | A10             |

| 14                              | V <sub>DD</sub> | 40              | RX-A            | 66              | A12             |

| 15                              | SA/MC-1         | 41              | D01             | 67              | A14             |

| 16                              | BSCTRCV         | 42              | D03             | 68              | MEMWR           |

| 17                              | LMC             | 43              | D05             | 69              | MEMENA-IN       |

| 18                              | ТХ-В            | 44              | D07             | 70              | INCMD           |

| 19                              | TX-B            | 45              | D09             | 71              | MSTRCLR         |

| 20                              | RX-B            | 46              | D11             | 72              | INT             |

| 21                              | LOGIC GND       | 47              | D13             | 73              | IOEN            |

| 22                              | A01             | 48              | D15             | 74              | SELECT          |

| 23                              | A03             | 49              | RTAD3           | 75              | READYD          |

| 24                              | A05             | 50              | RTAD2           | 76              | TAGEN           |

| 25                              | A07             | 51              | RTADP           | 77              | TXINH-A         |

| 26                              | A09             | 52              | SA/MC-2         | 78              | RX-A            |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | <b>17</b>  |

| Device type                     |                 | 01, 02, 3       |                        |                 |                 |

|---------------------------------|-----------------|-----------------|------------------------|-----------------|-----------------|

| Case outline<br>Terminal number | Terminal symbol | Terminal number | Z<br> Terminal symbol  | Terminal number | Terminal symbol |

| 1                               | D00             | 27              | V <sub>DD</sub>        | 53              | INT             |

| 2                               | D01             | 28              | SA/MC-3                | 54              | MEM/REG         |

| 3                               | D02             | 29              | SA/MC-1                | 55              | MSTRCLR         |

| 4                               | D03             | 30              | THIS-RT                | 56              | CLOCK-IN        |

| 5                               | D04             | 31              | BCSTRCV                | 57              | INCMD           |

| 6                               | D05             | 32              | RTPARERR               | 58              | MEMENA-OUT      |

| 7                               | D06             | 33              | LMC                    | 59              | MEMENA-IN       |

| 8                               | D07             | 34              | T/R                    | 60              | MEMOE           |

| 9                               | D08             | 35              | V <sub>EE</sub> (CH B) | 61              | MEMWR           |

| 10                              | D09             | 36              | V <sub>CC</sub> (CH B) | . 62            | A15             |

| 11                              | D10             | 37              | GNDB                   | 63              | A14             |

| 12                              | D11             | 38              | TX/RX-B                | 64              | A13             |

| 13                              | D12             | 39              | TX/RX-B                | 65              | A12             |

| 14                              | D13             | 40              | TX/RX-A                | 66              | A11             |

| 15                              | D14             | 41              | TX/RX-A                | 67              | A10             |

| 16                              | D15             | 42              | V <sub>EE</sub> (CH A) | 68              | A09             |

| 17                              | RTAD1           | 43              | V <sub>CC</sub> (CH A) | 69              | A08             |

| 18                              | RTAD3           | 44              | GNDA                   | 70              | A07             |

| 19                              | RTAD0           | 45              | TAGEN                  | 71              | A06             |

| 20                              | RTAD2           | 46              | EXTLD                  | 72              | A05             |

| 21                              | RTAD4           | 47              | READYD                 | 73              | A04             |

| 22                              | RTADP           | 48              | RD/WR                  | 74              | A03             |

| 23                              | ILLCMD          | 49              | SELECT                 | 75              | A02             |

| 24                              | SA/MC-2         | 50              | EXTEN                  | 76              | A01             |

| 25                              | SA/MC-0         | 51              | IOEN                   | 77              | A00             |

| 26                              | SA/MC-4         | 52              | STRBD                  | 78              | GND             |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | 18         |

■ 9004708 0030311 834 ■

# NOTES:

- STRBD to IOEN (low) delay is two clock cycles. If contention occurs, delay is two clock cycles following release of bus (1.8 μs maxim<u>um).</u>

- 2. CPU must release STRBD within 1.5 µs of IOEN going active.

FIGURE 4. Timing diagram(s).

| STANDARD<br>MICROCIRCUIT DRAWING                         | SIZE<br><b>A</b> |                     | 5962-88692         |

|----------------------------------------------------------|------------------|---------------------|--------------------|

| DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43216-5000 |                  | REVISION LEVEL<br>H | SHEET<br><b>21</b> |

DESC FORM 193A JUL 94

# **9004708 0030313 607**

NOTES:

FIGURE 4. Timing diagram(s) - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-88692 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43216-5000        |                  | H              | 22         |

DESC FORM 193A JUL 94

9004708 0030314 543

<sup>1.</sup> STRBD to IOEN (low) delay is two clock cycles. If contention occurs, delay is two clock cycles following release of bus (1.8 µs maximum).

<sup>2.</sup> CPU must release STRBD within 1.5 μs of IOEN going active.

### ■ 9004708 0030315 48T ■

**9004708 0030316 316**

# 9004708 0030318 199 📟

# TABLE II. Electrical test requirements.

| MIL-PRF-38534 test requirements                                            | Subgroups<br>(in accordance with<br>MIL-PRF-38534, group<br>A test table) |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------|