nRF2401 Single Chip 2.4 GHz Radio Transceiver

# Single chip 2.4 GHz Transceiver

True single chip GFSK transceiver in a small

# APPLICATIONS

• Wireless mouse, keyboard, joystick

nRF2401

- Keyless entry

- Wireless data communication

- Alarm and security systems

- Home automation

- Home automation

- Surveillance

- Automotive

- Telemetry

- Intelligent sports equipment

- Industrial sensors

- Toys

125 channelsChannel switching time <200us.</li>

Multi channel operation

Only 2 external components

Data rate 0 to1Mbps

**FEATURES**

•

•

• Support frequency hopping

24-pin package (QFN24 5x5mm)

- Data slicer / clock recovery of data

- Address and CRC computation

- DuoCeiver<sup>™</sup> for simultaneous dual receiver topology

- ShockBurst<sup>™</sup> mode for ultra-low power operation and relaxed MCU performance

- Power supply range: 1.9 to 3.6 V

- Low supply current (TX), typical 10.5mA peak @ -5dBm output power

- Low supply current (RX), typical 18mA peak in receive mode

- 100% RF tested

- No need for external SAW filter

- World wide use

# **GENERAL DESCRIPTION**

nRF2401 is a single-chip radio transceiver for the world wide 2.4 - 2.5 GHz ISM band. The transceiver consists of a fully integrated frequency synthesizer, a power amplifier, a crystal oscillator and a modulator. Output power and frequency channels are easily programmable by use of the 3-wire serial interface. Current consumption is very low, only 10.5mA at an output power of -5dBm and 18mA in receive mode. Built-in Power Down modes makes power saving easily realizable.

# **QUICK REFERENCE DATA**

| Parameter                                       | Value      | Unit |

|-------------------------------------------------|------------|------|

| Minimum supply voltage                          | 1.9        | V    |

| Maximum output power                            | 0          | dBm  |

| Maximum data rate                               | 1000       | kbps |

| Supply current in transmit @ -5dBm output power | 10.5       | mA   |

| Supply current in receive mode                  | 18         | mA   |

| Temperature range                               | -40 to +85 | °C   |

| Sensitivity                                     | -90        | dBm  |

| Supply current in Power Down mode               | 1          | μΑ   |

### Table 1 nRF2401 quick reference data

### nRF2401 Single Chip 2.4 GHz Radio Transceiver

| Type Number   | Description                                          | Version |

|---------------|------------------------------------------------------|---------|

| NRF2401 IC    | 24 pin QFN 5x5                                       | А       |

| NRF2401-EVKIT | Evaluation kit (2 test PCB, 2 configuration PCB, SW) | 1.0     |

| Table 2 nRF2401 | ordering | infor | mation |

|-----------------|----------|-------|--------|

|-----------------|----------|-------|--------|

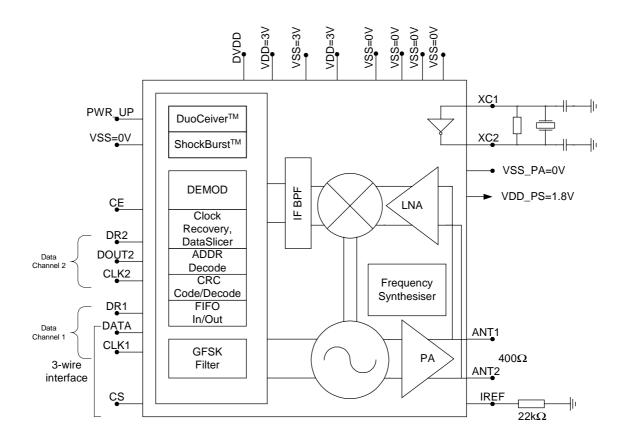

# **BLOCK DIAGRAM**

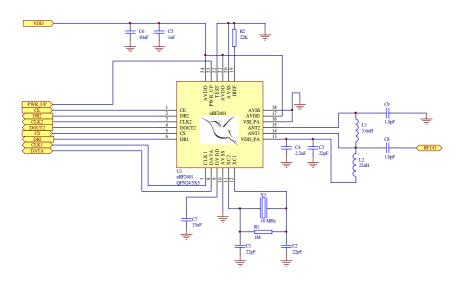

Figure 1 nRF2401 with external components.

# **PIN FUNCTIONS**

| Pin | Name   | Pin function   | Description                                                                 |

|-----|--------|----------------|-----------------------------------------------------------------------------|

| 1   | CE     | Digital Input  | Chip Enable Activates RX or TX mode                                         |

| 2   | DR2    | Digital Output | RX Data Ready at Data Channel 2 (ShockBurst <sup>™</sup> only)              |

| 3   | CLK2   | Digital I/O    | Clock Output/Input for RX Data Channel 2                                    |

| 4   | DOUT2  | Digital Output | RX Data Channel 2                                                           |

| 5   | CS     | Digital Input  | Chip Select Activates Configuration Mode                                    |

| 6   | DR1    | Digital Output | RX Data Ready at Data Channel 1 (ShockBurst <sup>™</sup> only)              |

| 7   | CLK1   | Digital I/O    | Clock Input (TX) & Output/Input (RX) for Data Channel 1<br>3-wire interface |

| 8   | DATA   | Digital I/O    | RX Data Channel 1/TX Data Input/ 3-wire interface                           |

| 9   | DVDD   | Power          | Positive Digital Supply output for decoupling purposes                      |

| 10  | VSS    | Power          | Ground (0V)                                                                 |

| 11  | XC2    | Analog Output  | Crystal Pin 2                                                               |

| 12  | XC1    | Analog Input   | Crystal Pin 1                                                               |

| 13  | VDD_PA | Power Output   | Power Supply (+1.8V) to Power Amplifier                                     |

| 14  | ANT1   | RF             | Antenna interface 1                                                         |

| 15  | ANT2   | RF             | Antenna interface 2                                                         |

| 16  | VSS_PA | Power          | Ground (0V)                                                                 |

| 17  | VDD    | Power          | Power Supply (+3V DC)                                                       |

| 18  | VSS    | Power          | Ground (0V)                                                                 |

| 19  | IREF   | Analog Input   | Reference current                                                           |

| 20  | VSS    | Power          | Ground (0V)                                                                 |

| 21  | VDD    | Power          | Power Supply (+3V DC)                                                       |

| 22  | VSS    | Power          | Ground (0V)                                                                 |

| 23  | PWR_UP | Digital Input  | Power Up                                                                    |

| 24  | VDD    | Power          | Power Supply (+3V DC)                                                       |

Table 3 nRF2401 pin function

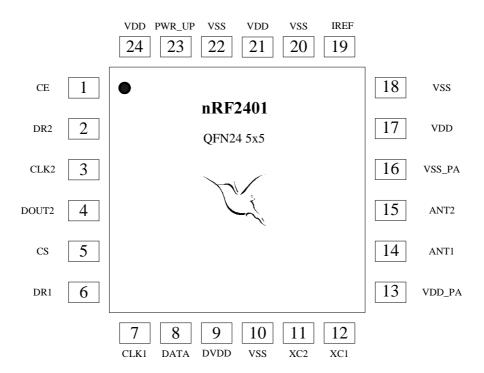

# **PIN ASSIGNMENT**

Figure 2. nRF2401 pin assignment (top view) for a QFN24 5x5 package.

# **ELECTRICAL SPECIFICATIONS**

| Conditions: | VDD = +3V, | $VSS = 0V, T_A$ | $= -40^{\circ}C \text{ to} + 85^{\circ}C$ |

|-------------|------------|-----------------|-------------------------------------------|

|-------------|------------|-----------------|-------------------------------------------|

| Symbol                      | Parameter (condition)                                                 | Notes | Min.      | Тур. | Max.         | Units        |

|-----------------------------|-----------------------------------------------------------------------|-------|-----------|------|--------------|--------------|

|                             | <b>Operating conditions</b>                                           |       |           |      |              |              |

| VDD                         | Supply voltage                                                        |       | 1.9       | 3.0  | 3.6          | V            |

| TEMP                        | Operating Temperature                                                 |       | -40       | +27  | +85          | °C           |

|                             |                                                                       |       |           |      |              |              |

|                             | Digital input pin                                                     |       |           |      | •            | 1            |

| $V_{IH}$                    | HIGH level input voltage                                              |       | VDD- 0.3  |      | VDD          | V            |

| V <sub>IL</sub>             | LOW level input voltage                                               |       | Vss       |      | 0.3          | V            |

|                             | Digital output pin                                                    |       |           |      |              |              |

| V <sub>OH</sub>             | HIGH level output voltage (I <sub>OH</sub> =-0.5mA)                   |       | VDD- 0.3  |      | VDD          | V            |

| V <sub>OL</sub>             | LOW level output voltage (I <sub>OL</sub> =0.5mA)                     |       | Vss       |      | 0.3          | V            |

| <u>OL</u>                   |                                                                       |       |           |      |              |              |

| £                           | General RF conditions                                                 | 1)    | 2400      |      | 2524         | MII-         |

| f <sub>OP</sub>             | Operating frequency                                                   | 1)    | 2400<br>4 |      | 2524<br>20   | MHz          |

| $\frac{f_{XTAL}}{\Delta f}$ | Crystal frequency<br>Frequency deviation                              | 2)    | 4         | ±156 | 20           | MHz<br>kHz   |

|                             | Data rate ShockBurst <sup>TM</sup>                                    |       | > 0       | ±130 | 1000         |              |

| R <sub>GFSK</sub>           | Data rate Direct Mode                                                 | 3)    | >0<br>250 |      | 1000<br>1000 | kbps<br>kbps |

| R <sub>GFSK</sub>           | Channel spacing                                                       | 3)    | 230       | 1    | 1000         | MHz          |

| F <sub>CHANNEL</sub>        | Channel spacing                                                       |       |           | 1    |              | IVITIZ       |

|                             | Transmitter operation                                                 |       |           |      |              |              |

| P <sub>RF</sub>             | Maximum Output Power                                                  | 4)    |           | 0    | +4           | dBm          |

| P <sub>RFC</sub>            | RF Power Control Range                                                |       | 16        | 20   |              | dB           |

| P <sub>RFCR</sub>           | <b>RF</b> Power Control Range Resolution                              |       |           |      | ±3           | dB           |

| P <sub>BW</sub>             | 20dB Bandwidth for Modulated Carrier                                  |       |           |      | 1000         | kHz          |

| P <sub>RF2</sub>            | 2 <sup>nd</sup> Adjacent Channel Transmit Power 2MHz                  |       |           |      | -20          | dBm          |

| P <sub>RF3</sub>            | 3rd Adjacent Channel Transmit Power 3MHz                              |       |           |      | -40          | dBm          |

| I <sub>VDD</sub>            | Supply current @ 0dBm output power                                    | 5)    |           | 13   |              | mA           |

| I <sub>VDD</sub>            | Supply current @ -20dBm output power                                  | 5)    |           | 8.8  |              | mA           |

| $\mathbf{I}_{\mathrm{VDD}}$ | Average Supply current @ -5dBm output power, ShockBurst <sup>TM</sup> | 6)    |           | 0.8  |              | mA           |

| I <sub>VDD</sub>            | Average Supply current in stand-by mode                               | 7)    |           | 12   |              | μΑ           |

| I <sub>VDD</sub>            | Average Supply current in power down                                  |       |           | 1    |              | μA           |

|                             | Receiver operation                                                    |       |           |      |              |              |

| I <sub>VDD</sub>            | Supply current one channel 250kbps                                    |       |           | 18   |              | mA           |

| I <sub>VDD</sub>            | Supply current one channel 1000kbps                                   |       |           | 19   |              | mA           |

| I <sub>VDD</sub>            | Supply current two channels 250kbps                                   |       |           | 23   | 1            | mA           |

| I <sub>VDD</sub>            | Supply current two channels 1000kbps                                  |       |           | 25   | 1            | mA           |

| RX <sub>SENS</sub>          | Sensitivity at 0.1%BER (@250kbps)                                     |       |           | -90  |              | dBm          |

| RX <sub>SENS</sub>          | Sensitivity at 0.1%BER (@1000kbps)                                    |       |           | -80  | 1            | dBm          |

| C/I <sub>CO</sub>           | C/I Co-channel                                                        |       |           | 6    |              | dB           |

| C/I <sub>1ST</sub>          | 1 <sup>st</sup> Adjacent Channel Selectivity C/I 1MHz                 |       |           | -1   |              | dB           |

| C/I <sub>2ND</sub>          | 2 <sup>nd</sup> Adjacent Channel Selectivity C/I 2MHz                 |       |           | -16  |              | dB           |

| C/I <sub>3RD</sub>          | 3 <sup>rd</sup> Adjacent Channel Selectivity C/I 3MHz                 |       |           | -26  |              | dB           |

| RX <sub>B</sub>             | Blocking Data Channel 2                                               |       |           | -20  |              | dB           |

|                             | band is determined by local regulations                               |       | 1         | 14   | 1            | 415          |

1) Usable band is determined by local regulations

2) The crystal frequency may be chosen from 5 different values (4, 8, 12, 16, and 20MHz) which are specified in the configuration word, see Table 8. 16MHz are required for 1Mbps operation.

3) Data rate must be either 250kbps or 1000kbps.

4) De-embedded Antenna load impedance =  $400 \Omega$

5) De-embedded Antenna load impedance =  $400 \Omega$ . Effective data rate 250kbps or 1Mbps.

6) De-embedded Antenna load impedance =  $400 \Omega$ . Effective data rate 10kbps.

7) Current if 4 MHz crystal is used.

### Table 4 nRF2401 RF specifications

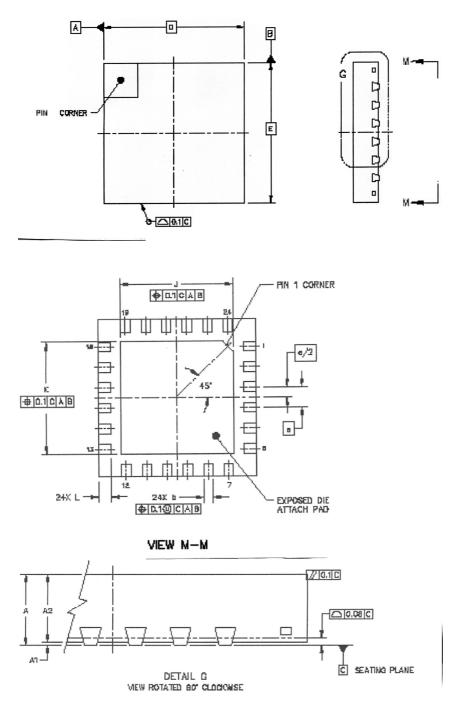

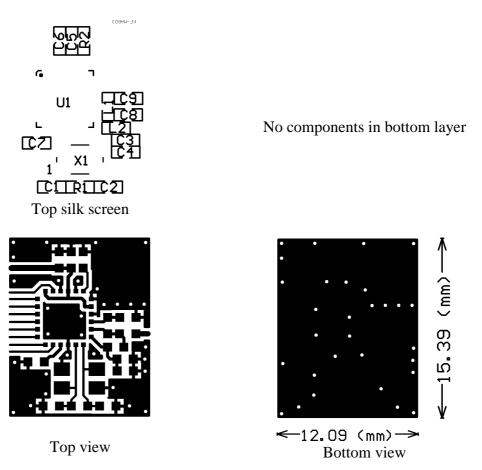

# PACKAGE OUTLINE

nRF2401 uses the QFN 24LD 5x5 package. Dimensions are in mm.

| Package Type |      | Α   | $A_1$ | A2   | b    | D     | Ε     | e        | J    | K    | L    |

|--------------|------|-----|-------|------|------|-------|-------|----------|------|------|------|

| QFN24        | Min  | 0.8 | 0.0   | 0.75 | 0.25 |       |       |          | 3.47 | 3.47 | 0.35 |

| (5x5 mm)     | typ. |     |       |      | 0.3  | 5 BSC | 5 BSC | 0.65 BSC | 3.57 | 3.57 | 0.4  |

|              | Max  | 1   | 0.05  | 1    | 0.35 |       |       |          | 3.67 | 3.67 | 0.45 |

nRF2401 Single Chip 2.4 GHz Radio Transceiver

# **Absolute Maximum Ratings**

### Supply voltages

VDD .....- 0.3V to + 3.6V VSS .....0V

### Input voltage

$V_I$ .....- 0.3V to VDD + 0.3V

### **Output voltage**

$V_{O} \hdots - 0.3 V$  to VDD + 0.3 V

### **Total Power Dissipation**

$P_D(T_A=85^{\circ}C).....90mW$

### Temperatures

Operating Temperature.... -  $40^{\circ}$ C to +  $85^{\circ}$ C Storage Temperature..... -  $40^{\circ}$ C to +  $125^{\circ}$ C

*Note: Stress exceeding one or more of the limiting values may cause permanent damage to the device.*

### **ATTENTION!**

Electrostatic Sensitive Device Observe Precaution for handling.

### nRF2401 Single Chip 2.4 GHz Radio Transceiver

# **Glossary of Terms**

| Term       | Description                     |

|------------|---------------------------------|

| CLK        | Clock                           |

| CRC        | Cyclic Redundancy Check         |

| CS         | Chip Select                     |

| CE         | Chip Enable                     |

| DR         | Data Ready                      |

| GFSK       | Gaussian Frequency Shift Keying |

| ISM        | Industrial-Scientific-Medical   |

| MCU        | Micro controller                |

| OD         | Overdrive                       |

| PWR_DWN    | Power Down                      |

| PWR_UP     | Power Up                        |

| RX Receive |                                 |

| ST_BY      | Standby                         |

| TX         | Transmit                        |

Table 5 Glossary

# **MODES OF OPERATION**

# Overview

The nRF2401 can be set in the following main modes depending on three control pins:

| Mode           | PWR_UP | CE | CS |

|----------------|--------|----|----|

| Active (RX/TX) | 1      | 1  | 0  |

| Configuration  | 1      | 0  | 1  |

| Stand by       | 1      | 0  | 0  |

| Power down     | 0      | Х  | Х  |

Table 6 nRF2401 main modes

For a complete overview of the nRF2401 I/O pins in the different modes please refer to Table 7.

# Active modes

The nRF2401 has two active (RX/TX) modes:

- ShockBurst<sup>TM</sup>

- Direct Mode

The device functionality in these modes is decided by the content of a configuration word. This configuration word is presented in configuration section.

# **ShockBurst**<sup>TM</sup>

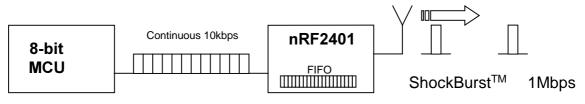

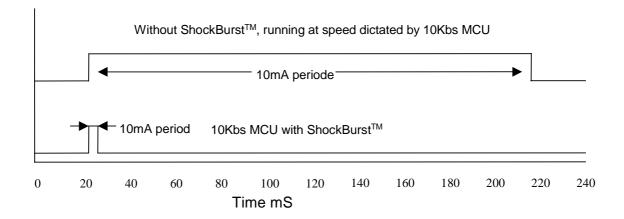

The ShockBurst<sup>™</sup> technology uses on-chip FIFO to clock in data at a low data rate and transmit at a very high rate thus enabling extremely power reduction.

When operating the nRF2401 in ShockBurst<sup>TM</sup>, you gain access to the high data rates (1 Mbps) offered by the 2.4 GHz band without the need of a costly, high-speed micro controller (MCU) for data processing.

By putting all high speed signal processing related to RF protocol on-chip, the nRF2401 offers the following benefits:

- Highly reduced current consumption

- Lower system cost (facilitates use of less expensive micro controller)

- Greatly reduced risk of 'on-air' collisions due to short transmission time

The nRF2401 can be programmed using a simple 3-wire interface where the data rate is decided by the speed of the micro controller.

By allowing the digital part of the application to run at low speed while maximizing the data rate on the RF link, the nRF ShockBurst<sup>TM</sup> mode reduces the average current consumption in applications considerably.

### ShockBurst<sup>™</sup> principle

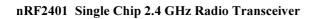

When the nRF2401 is configured in ShockBurst<sup>TM</sup>, TX or RX operation is conducted in the following way (10 kbps for the example only).

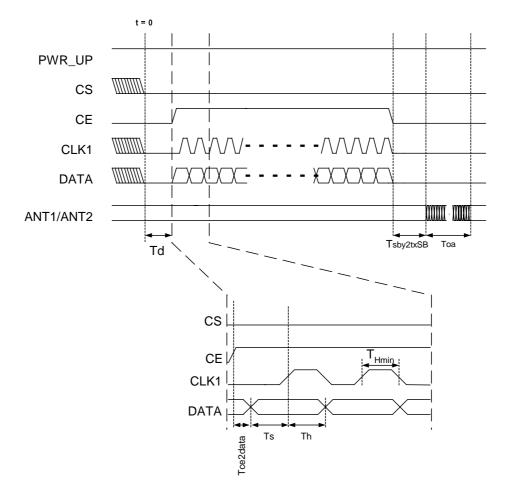

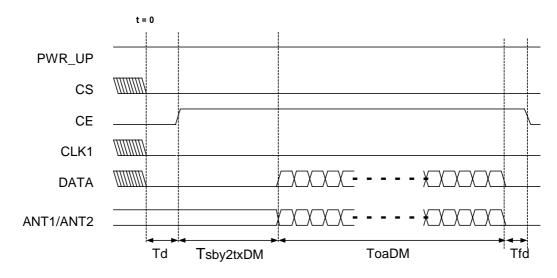

Figure 4 Clocking in data with MCU and sending with ShockBurst<sup>™</sup> technology

Figure 6 Flow Chart ShockBurst<sup>™</sup> Transmit of nRF2401

# nRF2401 ShockBurst<sup>TM</sup> Transmit:

MCU interface pins: CE, CLK1, DATA

- 1. When the application MCU has data to send, set CE high. This activates RF2401 on-board data processing.

- 2. The address of the receiving node (RX address) and payload data is clocked into the nRF2401. The application protocol or MCU sets the speed <1Mbps (ex: 10kbps).

- 3. MCU sets CE low, this activates a nRF2401 ShockBurst<sup>TM</sup> transmission.

- 4. nRF2401 ShockBurst<sup>TM</sup>:

- RF front end is powered up

- RF package is completed (preamble added, CRC calculated)

- Data is transmitted at high speed (250 kbps or 1 Mbps configured by user).

- nRF2401 return to stand-by when finished

### nRF2401 Single Chip 2.4 GHz Radio Transceiver

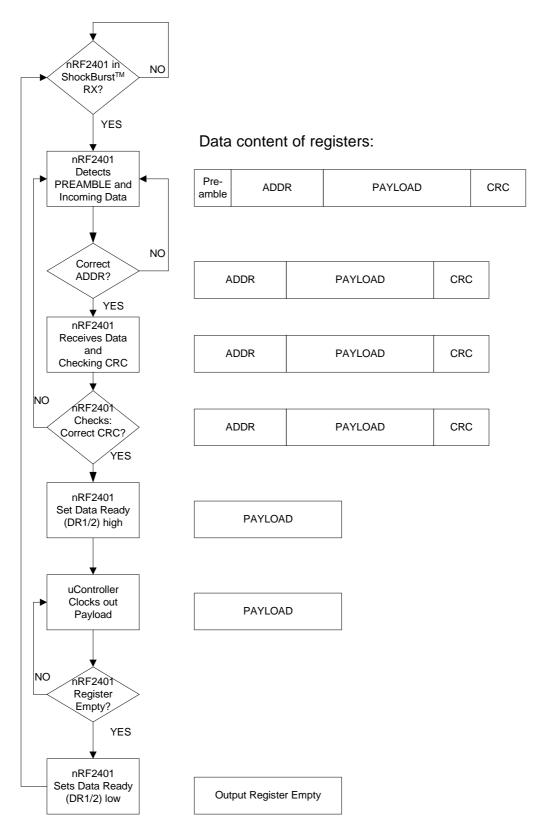

Figure 7 Flow Chart ShockBurst<sup>TM</sup> Receive of nRF2401

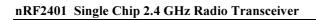

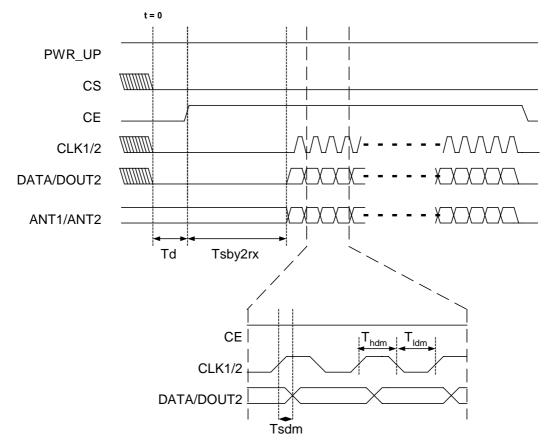

# nRF2401 ShockBurst<sup>TM</sup> Receive:

MCU interface pins: CE, DR1, CLK1 and DATA (one RX channel receive)

- 1. Correct address and size of payload of incoming RF packages are set when nRF2401 is configured to ShockBurst<sup>TM</sup> RX.

- 2. To activate RX, set CE high.

- 3. After 200  $\mu$ s settling, nRF2401 is monitoring the air for incoming communication.

- 4. When a valid package has been received (correct address and CRC found), nRF2401 removes the preamble, address and CRC bits.

- 5. nRF2401 then notifies (interrupts) the MCU by setting the DR1 pin high.

- 6. MCU may (or may not) set the CE low to disable the RF front end (low current mode).

- 7. The MCU will clock out just the payload data at a suitable rate (ex. 10 kbps).

- 8. When all payload data is retrieved nRF2401 sets DR1 low again, and is ready for new incoming data package if CE is kept high during data download. If the CE was set low, a new start up sequence can begin, see Figure 16.

# **Direct Mode**

In direct mode the nRF2401 works like a traditional RF device. Data must be at 1Mbps, or 250kbps at low data rate setting, for the receiver to detect the signals.

# **Direct Mode Transmit:**

MCU interface pins: CE, DATA

- 1. When application MCU has data to send, set CE high

- 2. The nRF2401 RF front end is now immediately activated, and after 200  $\mu$ s settling time, data will modulate the carrier directly.

- 3. All RF protocol parts must hence be implemented in MCU firmware (preamble, address and CRC).

# **Direct Mode Receive:**

MCU interface pins: CE, CLK1, and DATA

- 1. Once the nRF2401 is configured and powered up (CE high) in direct RX mode, DATA will start to toggle due to noise present on the air.

- 2. CLK1 will also start to toggle as nRF2401 is trying to lock on to the incoming data stream.

- 3. Once a valid preamble arrives, CLK1 and DATA will lock on to the incoming signal and the RF package will appear at the DATA pin with the same speed as it is transmitted.

- 4. To enable the demodulator to re-generate the clock, the preamble must be 8 bits toggling hi-low, starting with low if the first data bit low.

- 5. In this mode no data ready (DR) signals is available. Address and checksum verification must also be done in the receiving MC.

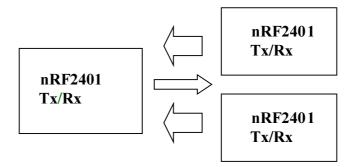

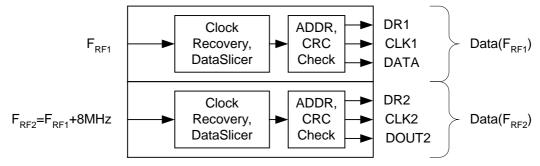

# DuoCeiver<sup>TM</sup> Simultaneous Two Channel Receive Mode

In both ShockBurst<sup>™</sup> & Direct modes the nRF2401 can facilitate simultaneous reception of two parallel independent frequency channels at the maximum data rate. This means:

- nRF2401 can receive data from two 1 Mbps transmitters (ex: nRF2401 or nRF2402) 8 MHz (8 frequency channels) apart through one antenna interface.

- The output from the two data channels is fed to two separate MCU interfaces.

- Data channel 1: CLK1, DATA, and DR1

- Data channel 2: CLK2, DOUT2, and DR2

- DR1 and DR2 are available only in ShockBurst<sup>TM</sup>.

The nRF2401 DuoCeiver<sup>TM</sup> technology provides 2 separate dedicated data channels for RX and replaces the need for two, stand alone receiver systems.

Figure 8 Simultaneous 2 channel receive on nRF2401

There is one absolute requirement for using the second data channel. For the nRF2401 to be able to receive at the second data channel the frequency channel must be 8MHz higher than the frequency of data channel 1. The nRF2401 must be programmed to receive at the frequency of data channel 1. No time multiplexing is used in nRF2401 to fulfil this function. In direct mode the MCU must be able to handle two simultaneously incoming data packets if it is not multiplexing between the two data channels. In ShockBurst<sup>TM</sup> it is possible for the MCU to clock out one data channel at a time while data on the other data channel waits for MCU availability, without any lost data packets, and by doing so reduce the needed performance of the MCU.

Figure 9 DuoCeiver<sup>TM</sup> with two simultaneously independent receive channels.

# **Configuration Mode**

In configuration mode a configuration word of up to 15 bytes is downloaded to nRF2401. This is done through a simple 3-wire interface (CS, CLK1 and DATA). For more information on configuration please refer to the nRF2401 Device configuration chapter on page16.

# **Stand-By Mode**

Stand by mode is used to minimize average current consumption while maintaining short start up times. In this mode, part of the crystal oscillator is active. Current consumption is dependent on crystal frequency (Ex:  $12 \ \mu A \ @ 4 \ MHz$ ,  $32 \ \mu A \ @ 16 \ MHz$ ). The configuration word content is maintained during stand by.

# **Power Down Mode**

In power down the nRF2401 is disabled with minimal current consumption, typically less than 1 $\mu$ A. Entering this mode when the device is not active minimizes average current consumption, maximizing battery lifetime. The configuration word content is maintained during power down.

Ì

nRF2401 Single Chip 2.4 GHz Radio Transceiver

# Pin configuration for the different modes of nRF2401

| PWR UP         CE         CS         CLK1         DATA         direction         dimate         dimate         dim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nRF2401                     | <b>INPUT PINS</b> | SNI |    | <b>BIDIR PINS</b> |             |           | OUTPI | <b>OUTPUT PINS</b> |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|-----|----|-------------------|-------------|-----------|-------|--------------------|-------|

| PWR UP         CE         CS         CLK1         DATA         CLK2           0         0         0         X $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ 0         0         0         X $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ 0         0         0         X $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ $\mathbf{D}$ 0         0         0         1         0 $\mathbf{D}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MODES                       |                   |     |    | direction         | direction   | direction |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | PWR UP            | CE  | CS | <b>CLK1</b>       | DATA        | CLK2      | DR1   | DR2                | DOUT2 |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Power down                  |                   |     |    | In                | In          | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | 0                 | 0   | X  | Х                 | Х           | X         | 0     | 0                  | 0     |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Stand by                    |                   |     |    | In                | In          | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | 1                 | 0   | 0  | Х                 | Х           | X         | 0     | 0                  | 0     |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Configuration               |                   |     |    | In                | In          | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | 1                 | 0   | 1  | CLK               | CONFIG DATA | CLK       | 0     | 0                  | 0     |

| $ \begin{array}{ c c c c c c c c } & 1 & 1 & 0 & CLK & DATA & X & X \\ \hline & & & & & & & & & \\ \hline & & & & & & &$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TX ShockBurst <sup>TM</sup> |                   |     |    | In                | In          | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | 1                 | 1   | 0  | CLK               | DATA        | Х         | 0     | 0                  | 0     |

| $ \begin{array}{ c c c c c c } & 1 & 1 & 0 & Set to 0 & DATA & CLK & \\ \hline M & 1 & 1 & 0 & In & 0ut & In & In & \\ \hline M & 1 & 1 & 0 & CLK & DATA & CLK & In & I$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TX Direct                   |                   |     |    | In                | In          | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | 1                 | 1   | 0  | Set to 0          | DATA        | CLK       | 0     | 0                  | 0     |

| $ \begin{array}{ c c c c c } \hline \mbox{M} & 1 & 1 & 0 & \mbox{CLK} & \mbox{DATA} & \mbox{DAT} & DAT$ | RX ShockBurst <sup>TM</sup> |                   |     |    | In                | Out         | In        |       |                    |       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | in one channel              | 1                 | 1   | 0  | CLK               | DATA        | CLK       | DR1   | 0                  | 0     |

| 1     1     1     0     CLK     DATA     CLK       1     1     0     0ut     0ut     0ut       1     1     0     CLK     DATA     0ut       1     1     0     0ut     0ut     0ut       1     1     0     0ut     0ut     0ut       1     1     0     CLK     DATA     0ut       1     1     0     0ut     0ut     0ut                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RX ShockBurst <sup>TM</sup> |                   |     |    | In                | Out         | In        |       |                    |       |

| 1         1         0         0ut         0ut         0ut           1         1         0         CLK         DATA         0           1         1         0         Out         0ut         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | in two channels             | 1                 | 1   | 0  | CLK               | DATA        | CLK       | DR1   | DR2                | DATA  |

| 1         1         0         CLK         DATA         0           1         1         0         Out         Out         0           1         1         0         Out         Out         0           1         1         0         Out         Out         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>RX</b> Direct            |                   |     |    | Out               | Out         | Out       |       |                    |       |

| 1 1 0 Out Out Out Out Out CI.K DATA CI.K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | in one channel              | 1                 | 1   | 0  | CLK               | DATA        | 0         | 0     | 0                  | 0     |

| CLK DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>RX</b> Direct            | 1                 | 1   | 0  | Out               | Out         | Out       | DR1   | DR2                | DATA  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | in two channels             |                   |     |    | CLK               | DATA        | CLK       |       |                    |       |

Table 7 Pin configuration of nRF2401.

Nordic VLSI ASA - Vestre Rosten 81, N-7075 Tiller, Norway -Revision: 1.0 Page 15 of 37

Fax +4772898989 March 2003 ı

Phone +4772898900

ï

### nRF2401 Single Chip 2.4 GHz Radio Transceiver

# **DEVICE CONFIGURATION**

All configuration of the nRF2401 is done via a 3-wire interface to a single configuration register. The configuration word can be up to 15 bytes long for ShockBurst<sup>TM</sup> use and up to 2 bytes long for direct mode.

# Configuration for ShockBurst<sup>™</sup> operation

The configuration word in ShockBurst<sup>TM</sup> enables the nRF2401 to handle the RF protocol. Once the protocol is completed and loaded into nRF2401 only one byte, bit[7:0], needs to be updated during actual operation.

The configuration blocks dedicated to ShockBurst<sup>TM</sup> is as follows:

- <u>Payload section width</u>: Specifies the number of payload bits in a RF package. This enables the nRF2401 to distinguish between payload data and the CRC bytes in a received package.

- <u>Address width</u>: Sets the number of bits used for address in the RF package. This enables the nRF2401 to distinguish between address and payload data.

- <u>Address</u> (RX Channel 1 and 2): Destination address for received data.

- <u>CRC</u>: Enables nRF2401 on-chip CRC generation and de-coding.

### NOTE:

These configuration blocks, with the exception of the CRC, are dedicated for the packages that a nRF2401 is to receive.

In TX mode, the MCU must generate an address and a payload section that fits the configuration of the nRF2401 that is to receive the data.

When using the nRF2401 on-chip CRC feature ensure that CRC is enabled and uses the same length for both the TX and RX devices.

| PRE-AMBLE | ADDRESS |      | PAYLOAD | CRC |

|-----------|---------|------|---------|-----|

|           | <b></b> | 10 D | 1       |     |

Figure 10 Data packet set-up

### **Configuration for Direct Mode operation**

For direct mode operation only the two first bytes (bit[15:0]) of the configuring word are relevant.

# **Configuration Word overview**

|                                        | Bit<br>position | Number<br>of bits | Name    | Function                                                 |

|----------------------------------------|-----------------|-------------------|---------|----------------------------------------------------------|

|                                        | 143:120         | 24                | TEST    | Reserved for testing                                     |

| ntion                                  | 119:112         | 8                 | DATA2_W | Length of data payload section RX channel 2              |

| gura                                   | 111:104         | 8                 | DATA1_W | Length of data payload section RX channel 1              |

| nfig                                   | 103:64          | 40                | ADDR2   | Up to 5 byte address for RX channel 2                    |

| и со                                   | 63:24           | 40                | ADDR1   | Up to 5 byte address for RX channel 1                    |

| stT                                    | 23:18           | 6                 | ADDR_W  | Number of address bits (both RX channels).               |

| Bui                                    | 17              | 1                 | CRC_L   | 8 or 16 bit CRC                                          |

| ShockBurst <sup>TM</sup> configuration | 16              | 1                 | CRC_EN  | Enable on-chip CRC generation/checking.                  |

|                                        | 15              | 1                 | RX2_EN  | Enable two channel receive mode                          |

| tion                                   | 14              | 1                 | СМ      | Communication mode (Direct or ShockBurst <sup>TM</sup> ) |

| figura                                 | 13              | 1                 | RFDR_SB | RF data rate (1Mbps requires 16MHz crystal)              |

| General device configuration           | 12:10           | 3                 | XO_F    | Crystal frequency                                        |

| ral dev                                | 9:8             | 2                 | RF_PWR  | RF output power                                          |

| Genei                                  | 7:1             | 7                 | RF_CH#  | Frequency channel                                        |

|                                        | 0               | 1                 | RXEN    | RX or TX operation                                       |

Table 8 Table of configuration words.

The configuration word is shifted in MSB first on positive CLK1 edges. New configuration is enabled on the falling edge of CS.

### NOTE.

On the falling edge of CS, the nRF2401 updates the number of bits actually shifted in during the last configuration.

Ex:

If the nRF2401 is to be configured for 2 channel RX in ShockBurst<sup>™</sup>, a total of 120 bits must be shifted in during the first configuration after VDD is applied. Once the wanted protocol, modus and RF channel are set, only one bit (RXEN) is shifted in to switch between RX and TX.

# **Configuration Word Detailed Description**

The following describes the function of the 144 bits (bit 143 = MSB) that is used to configure the nRF2401. General Device Configuration: bit[15:0] ShockBurst<sup>TM</sup> Configuration: bit[119:0]

Test Configuration: bit[143:120]

| MSB  |                      |      |      | TEST |      |      |      |         |  |  |  |

|------|----------------------|------|------|------|------|------|------|---------|--|--|--|

| D143 | D142                 | D141 | D140 | D139 | D138 | D137 | D136 |         |  |  |  |

|      | Reserved for testing |      |      |      |      |      |      |         |  |  |  |

| 1    | 0                    | 0    | 0    | 1    | 1    | 1    | 0    | Default |  |  |  |

| MSB  | MSB TEST                             |      |      |      |      |      |      |      |      |      | ]    |      |      |      |      |         |

|------|--------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------|

| D135 | D134                                 | D133 | D132 | D131 | D130 | D129 | D128 | D127 | D126 | D125 | D124 | D123 | D122 | D121 | D120 |         |

|      | Reserved for testing Close PLL in TX |      |      |      |      |      |      |      |      |      |      |      |      |      |      |         |

| 0    | 0                                    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | Default |

|      | DATA2_W                                              |      |      |      |      |      |      |         |  |  |  |

|------|------------------------------------------------------|------|------|------|------|------|------|---------|--|--|--|

| D119 | D118                                                 | D117 | D116 | D115 | D114 | D113 | D112 |         |  |  |  |

|      | Data width channel#2 in # of bits excluding addr/crc |      |      |      |      |      |      |         |  |  |  |

| 0    | 0                                                    | 1    | 0    | 0    | 0    | 0    | 0    | Default |  |  |  |

|      | DATA1_W                                              |      |      |      |      |      |      |         |  |  |  |

|------|------------------------------------------------------|------|------|------|------|------|------|---------|--|--|--|

| D111 | D110                                                 | D109 | D108 | D107 | D106 | D105 | D104 |         |  |  |  |

|      | Data width channel#1 in # of bits excluding addr/crc |      |      |      |      |      |      |         |  |  |  |

| 0    | 0                                                    | 1    | 0    | 0    | 0    | 0    | 0    | Default |  |  |  |

|       |                                    |     |     |     |     | OR2 | ADI |     |  |      |      |      |

|-------|------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|------|------|------|

|       | D64                                | D65 | D66 | D67 | D68 | D69 | D70 | D71 |  | D101 | D102 | D103 |

|       | Channel#2 Address RX (up to 40bit) |     |     |     |     |     |     |     |  |      |      |      |

| Defau | 1                                  | 1   | 1   | 0   | 0   | 1   | 1   | 1   |  | 0    | 0    | 0    |

|     |                                    |     |  |     | ADI | OR1 |     |     |     |     |     |   |

|-----|------------------------------------|-----|--|-----|-----|-----|-----|-----|-----|-----|-----|---|

| D63 | D62                                | D61 |  | D31 | D30 | D29 | D28 | D27 | D26 | D25 | D24 |   |

|     | Channel#1 Address RX (up to 40bit) |     |  |     |     |     |     |     |     |     |     |   |

| 0   | 0                                  | 0   |  | 1   | 1   | 1   | 0   | 0   | 1   | 1   | 1   | D |

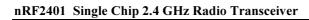

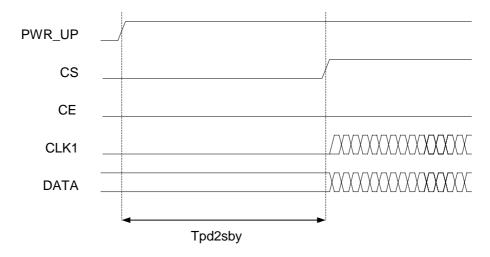

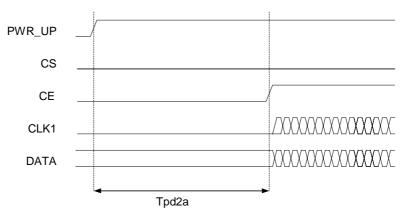

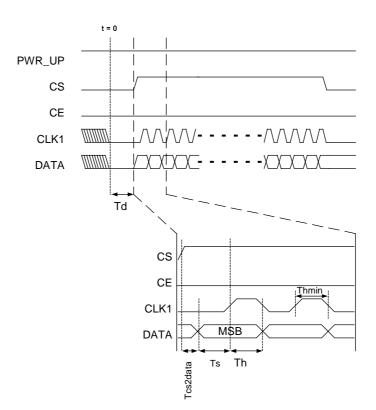

|     |                                            | ADD | R_W |     |     |         |  |  |  |  |  |