### **General Description**

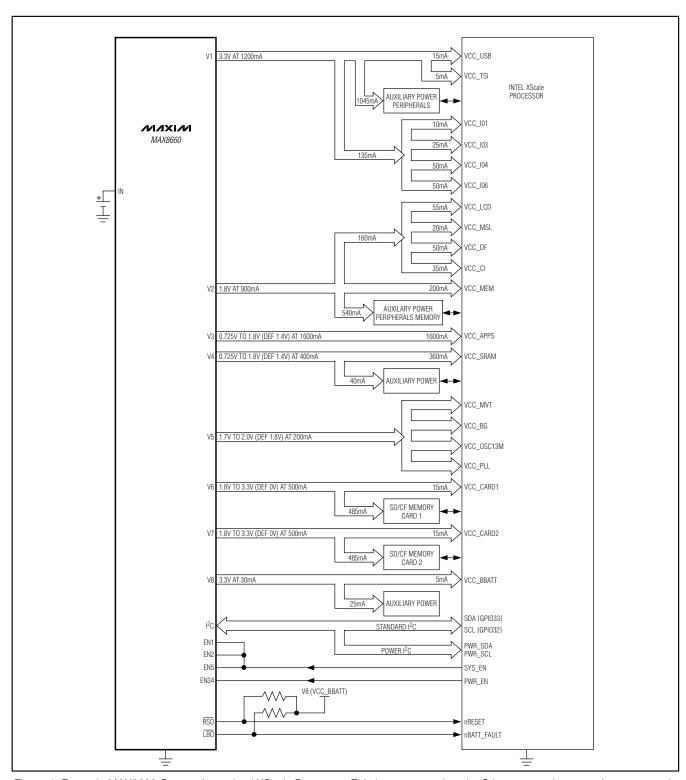

The MAX8660/MAX8661 power management ICs (PMICs) power Intel XScale® applications processors in smart cellular phones, PDAs, Internet appliances, and other portable devices.

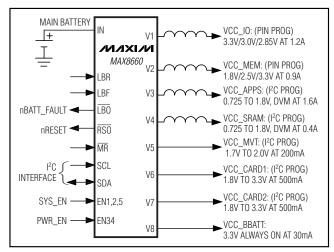

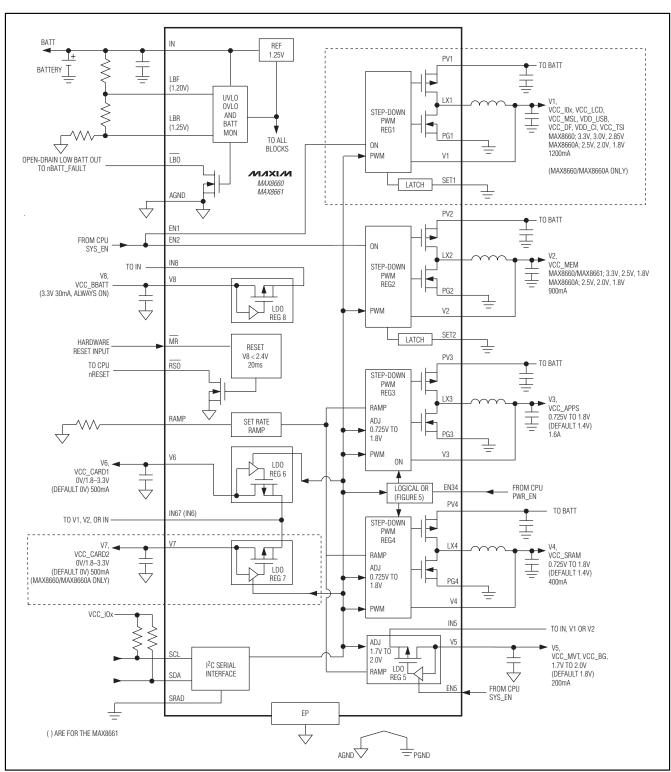

Four step-down DC-DC outputs, three linear regulators, and an 8th always-on LDO are integrated with powermanagement functions. Two dynamically controlled DC-DC outputs power the processor core and internal memory. Two other DC-DC converters power I/O, memory, and other peripherals. Additional functions include on/off control for outputs, low-battery detection, reset output, and a 2-wire I<sup>2</sup>C<sup>†</sup> serial interface. The MAX8661 functions the same as the MAX8660, except it lacks the REG1 step-down regulator and the REG7 linear regulator.

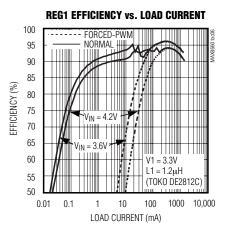

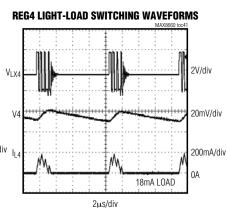

All step-down DC-to-DC outputs use fast 2MHz PWM switching and tiny external components. They automatically switch from PWM to high-efficiency light-load operation to reduce operating current and extend battery life. In addition, a forced PWM option allows lownoise operation at all loads. Overvoltage lockout protects the device against inputs up to 7.5V.

### **Applications**

PDAs, Palmtops, and Wireless Handhelds

Smart Cell Phones Personal Media Plavers Portable GPS Navigation Digital Cameras

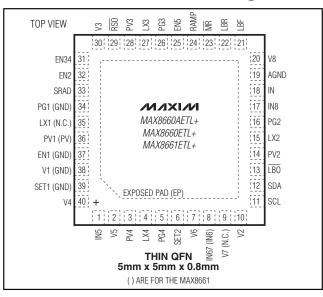

### Pin Configuration

### **Features**

- **Optimized for Intel XScale Processors**

- Protected to 7.5V—Shutdown Above 6.3V

- ♦ Four Synchronous Step-Down Converters REG1, REG2, REG3, REG4

- **♦ Four LDO Regulators** REG5, REG6, REG7, REG8

- **♦ 2MHz Switching Allows Small Components**

- ♦ Low, 20µA Deep-Sleep Current

- **♦ Low-Battery Monitor and Reset Output**

### **Ordering Information**

| PART          | PIN-<br>PACKAGE          | PKG<br>CODE | OPTIONS                                       |

|---------------|--------------------------|-------------|-----------------------------------------------|

| MAX8660ETL+   | 40 Thin QFN<br>5mm x 5mm | T4055-1     | V1: 3.3V, 3.0V, 2.85V<br>V2: 3.3V, 2.5V, 1.8V |

| MAX8660AETL+* | 40 Thin QFN<br>5mm x 5mm | T4055-1     | V1: 2.5V, 2.0V, 1.8V<br>V2: 2.5V, 2.0V, 1.8V  |

| MAX8661ETL+   | 40 Thin QFN<br>5mm x 5mm | T4055-1     | No REG1 and REG7<br>V2: 3.3V, 2.5V, 1.8V      |

**Note:** All devices are specified over the -40°C to 85°C operating temperature range.

- +Denotes lead-free package.

- \*Future product—contact factory for availability.

### Simplified Functional Diagram

Intel XScale is a registered trademark of Intel Corp.

†Purchase of I<sup>2</sup>C components from Maxim Integrated products, Inc., or one of its sublicensed Associated Companies, conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Maxim Integrated Products 1

| Table of (                                                  | Contents   |

|-------------------------------------------------------------|------------|

| General Description                                         | 1          |

| Applications                                                | 1          |

| Features                                                    | 1          |

| Ordering Information                                        | 1          |

| Simplified Functional Diagram                               | 1          |

| Pin Configuration                                           | 1          |

| Table of Contents                                           |            |

| Absolute Maximum Ratings                                    | 4          |

| Electrical Characteristics                                  | 4          |

| Typical Operating Characteristics                           |            |

| Pin Description                                             |            |

| Detailed Description                                        |            |

| Maxim vs. Intel Terminology                                 |            |

| Step-Down DC-DC Converters (REG1–REG4)                      |            |

| REG1 (VCC_IO) Step-Down DC-DC Converter (MAX8660 Only)      |            |

| REG2 (VCC_IO, VCC_MEM) Step-Down DC-DC Converters           |            |

| REG3 (VCC_APPS) Step-Down DC-DC Converters                  |            |

| REG1–REG4 Step-Down DC-DC Converter Operating Modes         |            |

| REG1-REG4 Synchronous Rectification                         |            |

| REG1/REG2 100% Duty-Cycle Operation (Dropout)               |            |

| Linear Regulators (REG5–REG8)                               | 28         |

| REGŠ (VCC_MVT, VCC_BG, VCC_OSC13M, VCC_PLL)                 |            |

| REG8 (VCC_BBATT) Always-On Regulator                        | 28         |

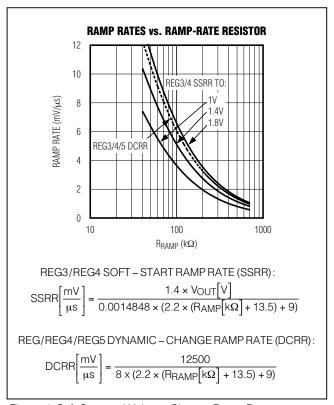

| Ramp Rate Control (RAMP)                                    |            |

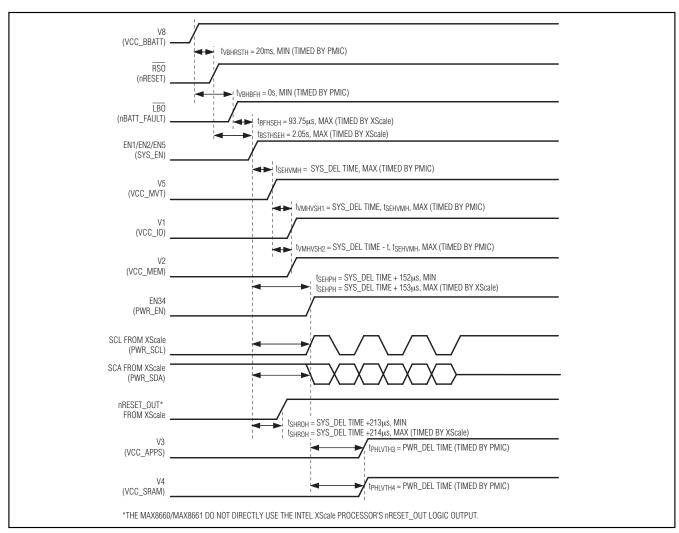

| Power Sequencing                                            |            |

| Enable Signals (EN_, PWR_EN, SYS_EN, I <sup>2</sup> C)      | 29<br>29   |

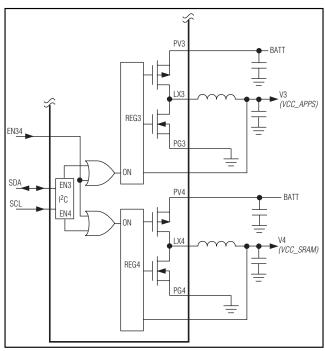

| REG3/REĞ4 Enable (EN34, EN3, EN4)                           | 30         |

| Power Modes                                                 |            |

| Power-Up and Power-Down Timing                              | 31<br>31   |

| Voltage Monitors, Reset, and Undervoltage-Lockout Functions | 32         |

| Undervoltage and Overvoltage Lockout                        |            |

| Reset Output (RSO) and MR Input                             | 32         |

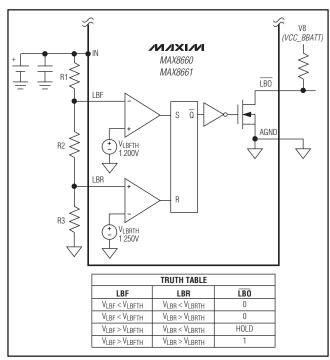

| Low-Battery Detector, (LBO, LBF, LBR)                       |            |

| Internal Off-Discharge Resistors                            |            |

| Thermal-Overload Protection                                 |            |

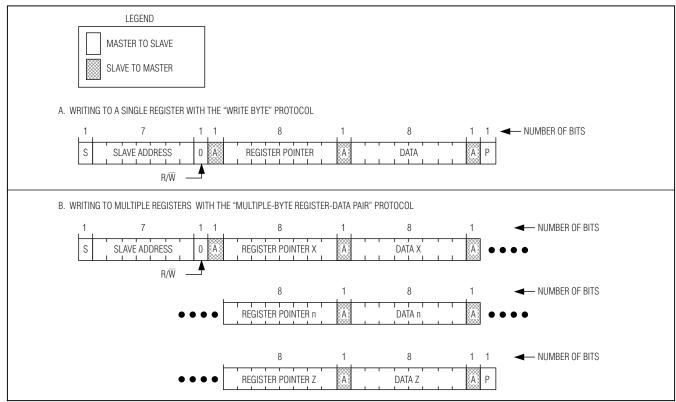

| I <sup>2</sup> C Interface                                  |            |

| Data Transfer                                               |            |

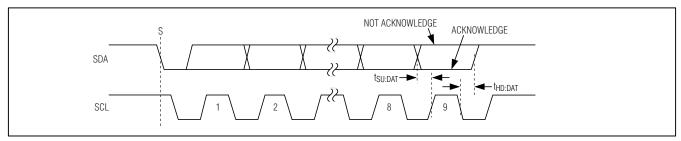

| Acknowledge Bit                                             |            |

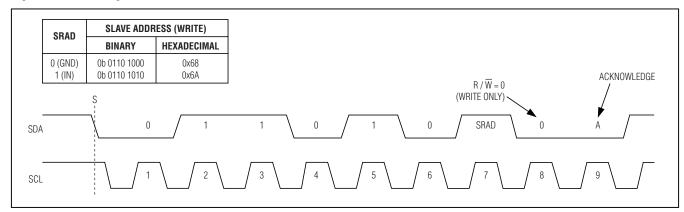

| Slave Address                                               | 37         |

| I <sup>2</sup> C Write Operation                            | 3 <i>1</i> |

| Table of Contents                                                           | (continued) |

|-----------------------------------------------------------------------------|-------------|

| Design Procedure                                                            |             |

| Setting the Output Voltages                                                 | 38          |

| Inductor Selection                                                          | 39          |

| Input Capacitor Selection                                                   | 39          |

| Output Capacitor Selection                                                  |             |

| Applications Information                                                    |             |

| Power Dissipation                                                           |             |

| PC Board Layout and Routing                                                 |             |

| Package Marking                                                             |             |

| Chip Information                                                            |             |

|                                                                             |             |

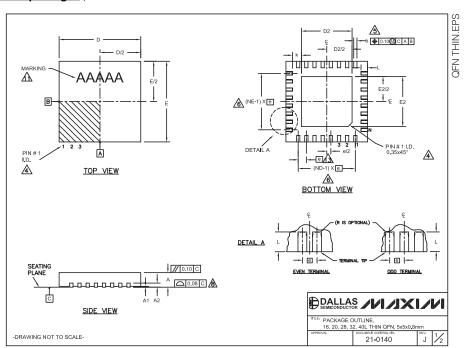

| Package Information                                                         | 41          |

| Tables                                                                      |             |

| Table 1. Maxim and Intel Power Domain Terminology                           |             |

| Table 2. Maxim and Intel Digital Signal Terminology                         |             |

| Table 3. SET1 Logic                                                         |             |

| Table 4. SET2 Logic                                                         |             |

| Table 5. Enable Signals                                                     |             |

| Table 6. Truth Table for V3/V4 Enable Logic                                 |             |

| Table 7. Power Modes and Corresponding Quiescent Operating Currents         |             |

| Table 8. Internal Off-Discharge Resistors                                   |             |

| Table 9. I <sup>2</sup> C Registers                                         |             |

| Table 10. DVM Voltage Change Register (VCC1, 0x20)                          |             |

| Table 11. Serial Codes for V5 (VCC_AFFS) and V4 (VCC_Shawl) Output Voltages |             |

| Table 13. Serial Codes for V6 and V7 Output Voltages                        |             |

| Figures                                                                     |             |

| Figure 1. Example MAX8660 Connection to Intel XScale Processor              |             |

| Figure 2. Functional Diagram                                                |             |

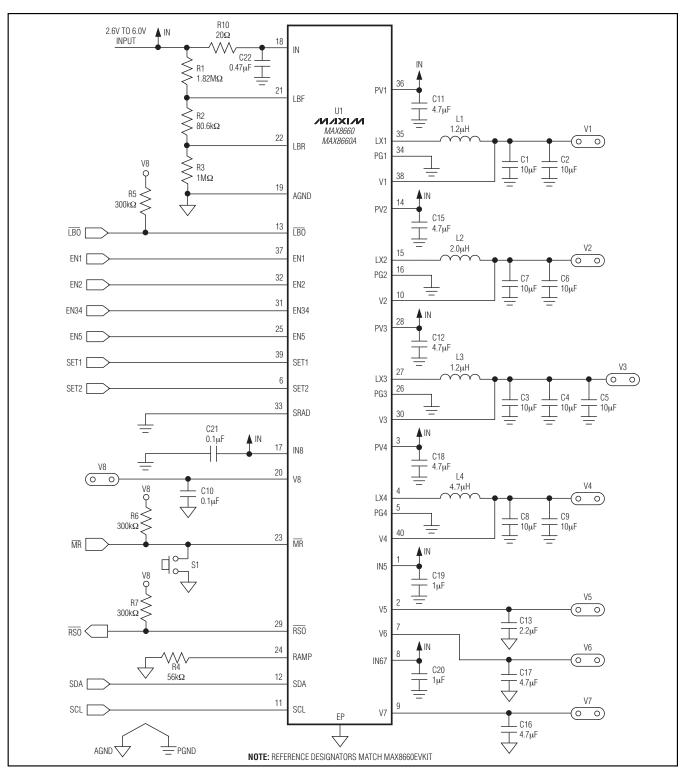

| Figure 3. Typical Applications Circuit                                      |             |

| Figure 4. Soft-Start and Voltage-Change Ramp Rates                          |             |

| Figure 5. V3/V4 Enable Logic                                                |             |

| Figure 6. Power-Up Timing                                                   |             |

| Figure 7. Low-Battery Detector Functional Diagram                           |             |

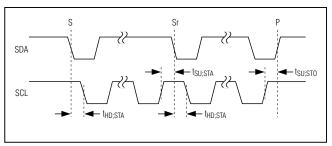

| Figure 8. START and STOP Conditions                                         |             |

| Figure 9. Acknowledge Bits                                                  | 37          |

| Figure 10. Slave Address Byte                                               |             |

| Figure 11. Writing to the MAX8660/MAX8661                                   |             |

### **ABSOLUTE MAXIMUM RATINGS**

| IN, IN5, IN6, IN67, EN2, EN34, EN5, SET2, V1, V2, V3, V4, SCL, SDA, |                             |

|---------------------------------------------------------------------|-----------------------------|

| SRAD to AGND                                                        |                             |

| LBF, LBR, EN1, RAMP to AGND                                         | 0.3V to $(V_{IN} + 0.3V)$   |

| V8 to AGND                                                          | 0.3V to $(V_{IN8} + 0.3V)$  |

| V5 to AGND                                                          | 0.3V to $(V_{IN5} + 0.3V)$  |

| V6, V7 to AGND                                                      | 0.3V to $(V_{IN67} + 0.3V)$ |

| PV1 to PG1                                                          | 0.3V to +7.5V               |

| PV2 to PG2                                                          | 0.3V to +7.5V               |

| PV3 to PG3                                                          | 0.3V to +7.5V               |

| PV4 to PG4                                                          | 0.3V to +7.5V               |

| PV, PV1, PV2, PV3, PV4, IN8 to IN                                   | 0.3V to +0.3V               |

| LX1 Continuous RMS Current (Note                                    | I)2.3A                      |

|                                                                     |                             |

| LX2 Continuous RMS Current (Note 1)                   | 2.0A           |

|-------------------------------------------------------|----------------|

| LX3 Continuous RMS Current (Note 1)                   | 2.6A           |

| LX4 Continuous RMS Current (Note 1)                   | 1.0A           |

| PG1, PG2, PG3, PG4, EP to AGND                        | 0.6V to +0.6V  |

| GND to AGND                                           | 0.3V to +0.3V  |

| All REGx Output Short-Circuit Duration                | Continuous     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| 40-Pin Thin QFN (derate 35.7mW/°C above               | +70°C)2857mW   |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

|                                                       |                |

Note 1: LX\_ has internal clamp diodes to PG\_ and PV\_. Applications that forward bias these diodes must take care not to exceed the IC's package power-dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                           | SYMBOL                                                                                             | C                                    | ONDITIONS                                                                                                | MIN                                                                                                         | TYP   | MAX   | UNITS |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------|-------|-------|

| PV1, PV2, PV3, PV4, IN, IN8<br>Supply Voltage Range | V <sub>IN</sub>                                                                                    | PV1, PV2, PV3, PV connected together | /4, IN, and IN8 must be<br>er externally                                                                 | 2.6                                                                                                         |       | 6.0   | V     |

| IN Undervoltage-Lockout                             | Vina                                                                                               | V <sub>IN</sub> rising               |                                                                                                          | 2.250                                                                                                       | 2.400 | 2.550 | V     |

| Threshold                                           | Vuvlo                                                                                              | V <sub>IN</sub> falling              |                                                                                                          | 2.200                                                                                                       | 2.350 | 2.525 | V     |

| IN Overvoltage-Lockout                              | Vovus                                                                                              | V <sub>IN</sub> rising               |                                                                                                          | 6.20                                                                                                        | 6.35  | 6.50  | V     |

| Threshold                                           | Vovlo                                                                                              | V <sub>IN</sub> falling              |                                                                                                          | 6.00                                                                                                        | 6.15  | 6.30  | V     |

|                                                     |                                                                                                    |                                      | Only V8 on (deep-sleep power mode)                                                                       |                                                                                                             | 20    |       |       |

| Input Current                                       |                                                                                                    | 00/1-005-10                          | V1, V2, and V8 on;<br>V1 and V2 in normal (skip)<br>operating mode                                       | 50                                                                                                          |       |       |       |

|                                                     | l <sub>IN</sub> +                                                                                  |                                      | V1, V2, V5, and V8 on<br>(sleep power mode);<br>V1 and V2 in normal (skip)<br>operating mode             | 90                                                                                                          |       |       |       |

|                                                     | I <sub>PV3</sub> +I <sub>PV4</sub> +<br>I <sub>IN5</sub> +<br>I <sub>IN67</sub> + I <sub>IN8</sub> |                                      |                                                                                                          | V1, V2, V3, V4, V5, and V8 on<br>(run power mode);<br>V1, V2, V3, and V4 in normal<br>(skip) operating mode |       | 140   |       |

|                                                     |                                                                                                    |                                      | V1, V2, V3, V4, V5, V6, V7,<br>and V8 (all on);<br>V1, V2, V3, and V4 in normal<br>(skip) operating mode |                                                                                                             | 250   |       |       |

|                                                     |                                                                                                    | Undervoltage lock                    | sout, $V_{IN} = 2.2V$                                                                                    |                                                                                                             | 1.5   |       |       |

|                                                     |                                                                                                    | Overvoltage locko                    | out, V <sub>IN</sub> = 6.5V                                                                              |                                                                                                             | 25    |       |       |

N/IXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.) (Note 2)

| PARAMETER                            | SYMBOL    | CON                                                                | DITIONS                     | MIN   | TYP   | MAX   | UNITS           |  |

|--------------------------------------|-----------|--------------------------------------------------------------------|-----------------------------|-------|-------|-------|-----------------|--|

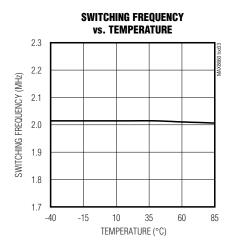

| PWM Switching Frequency              | fsw       |                                                                    |                             | 1.9   | 2.0   | 2.1   | MHz             |  |

| REG1—SYNCHRONOUS STEP-D              | OWN DC-DC | CONVERTER (MAX                                                     | 8660, MAX8660A only)        | •     |       |       | •               |  |

|                                      |           | SET1 = IN, V <sub>PV1</sub> = 4                                    | .2V, load = 600mA           | 3.250 | 3.300 | 3.350 |                 |  |

| V1 Voltage<br>Accuracy—MAX8860       | V1        | SET1 not connected load = 600mA                                    | $= V_{PV1} = 3.6V,$         | 2.955 | 3.000 | 3.045 | V               |  |

|                                      |           | SET1 = AGND, V <sub>PV1</sub>                                      | = 3.6V, load = 600mA        | 2.807 | 2.850 | 2.893 |                 |  |

| V1 Voltage                           |           | SET1 = IN, $V_{PV1} = 4$                                           |                             | 2.463 | 2.500 | 2.538 |                 |  |

| Accuracy—MAX8660A                    | V1        |                                                                    | $V_{PV1} = 3.6V, 600mA$     | 1.970 | 2.000 | 2.030 | V               |  |

| •                                    |           | SET1 = AGND, 3.6V                                                  |                             | 1.773 | 1.800 | 1.827 |                 |  |

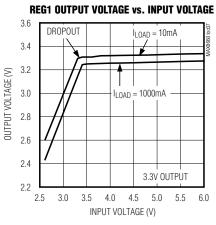

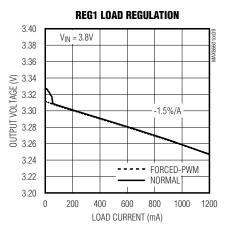

| V1 Load Regulation                   |           | Load = 0 to 1200mA                                                 |                             |       | -1.5  |       | %/A             |  |

| V1 Line Regulation                   |           |                                                                    |                             |       | 0.15  |       | %/V             |  |

| SET1 Input Leakage Current           |           |                                                                    |                             |       | 0.01  |       | μΑ              |  |

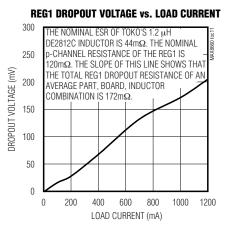

| V4.5                                 |           | Load = 800mA (Note                                                 | es 3, 4)                    |       | 150   |       |                 |  |

| V1 Dropout Voltage                   |           | Load = 1200mA (No                                                  | tes 3, 4)                   |       | 200   |       | <del>l</del> mV |  |

| p-Channel On-Resistance              |           |                                                                    |                             |       | 0.12  |       | Ω               |  |

| n-Channel On-Resistance              |           |                                                                    |                             |       | 0.15  |       | Ω               |  |

| p-Channel Current-Limit<br>Threshold |           |                                                                    |                             | 1.5   | 1.8   | 2.2   | А               |  |

| n-Channel Zero-Crossing<br>Threshold |           |                                                                    |                             |       | 25    |       | mA              |  |

| n-Channel Negative Current Limit     |           | Forced-PWM mode                                                    | only                        |       | -975  |       | mA              |  |

| REG1 Maximum Output Current          | lout1     | 2.6V ≤ V <sub>PV1</sub> ≤ 6V (No                                   | ote 5)                      | 1.2   |       |       | А               |  |

| V1 Bias Current                      |           |                                                                    | ,                           |       | 5     |       | μΑ              |  |

| LX1 Leakage Current                  |           | V <sub>PV1</sub> = 6V, LX1 = PG1 or PV1,                           | T <sub>A</sub> = +25°C      | -2    | ±0.03 | +2    |                 |  |

| LAT Leakage Current                  |           | $V_{\text{EN1}} = 0V$                                              | T <sub>A</sub> = +85°C      |       | ±0.2  |       | μΑ              |  |

| Soft-Start Ramp Rate—MAX8660         |           | To V1 = 3.3V (total ra<br>all V1 output voltage                    | amp time is 450µs for<br>s) | 5     | 7     | 9     | mV/μs           |  |

| Soft-Start Ramp Rate—<br>MAX8660A    |           | To V1 = 2.5V (total ramp time is 450μs for all V1 output voltages) |                             | 3     | 5     | 7     | mV/μs           |  |

| V5 to V1 Enable Time                 | tvmHvsH1  | Figure 6                                                           |                             |       | 350   |       | μs              |  |

| Internal Off-Discharge Resistance    |           |                                                                    |                             |       | 650   |       | Ω               |  |

| Minimum Duty Cycle                   |           | Forced-PWM mode only, min duty cycle in skip mode is 0%            |                             |       | 16.7  |       | %               |  |

| Maximum Duty Cycle                   |           |                                                                    |                             |       | 100   |       | %               |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                         | SYMBOL                                                       | CONE                                                            | DITIONS                     | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------|-------|-------|-------|-------|

| REG2—SYNCHRONOUS STEP-DO          | WN DC-DC                                                     | CONVERTER                                                       |                             |       |       |       |       |

|                                   |                                                              | SET2 = IN, $V_{PV2} = 4.3$                                      | 2V, load = 600mA            | 3.250 | 3.300 | 3.350 |       |

| V2 Voltage<br>Accuracy—MAX8660    | V2                                                           | SET2 not connected, load = 600mA                                | $V_{PV2} = 3.6V,$           | 2.463 | 2.500 | 2.538 | V     |

|                                   |                                                              | SET2 = AGND, V <sub>PV2</sub>                                   | = 3.6V, load = 600mA        | 1.773 | 1.800 | 1.827 |       |

|                                   | SET2 = IN, V <sub>PV2</sub> = 4.2V, load = 600mA 2.463 2.500 |                                                                 | 2.538                       |       |       |       |       |

| V2 Voltage Accuracy—MAX8660A      | V2                                                           | SET2 not connected, load = 600mA                                | $V_{PV2} = 3.6V$ ,          | 1.970 | 2.000 | 2.030 | V     |

|                                   |                                                              | SET2 = AGND, V <sub>PV2</sub>                                   | = 3.6V, load = 600mA        | 1.773 | 1.800 | 1.827 |       |

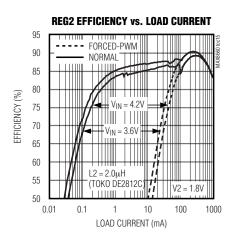

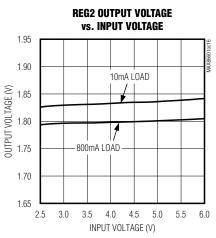

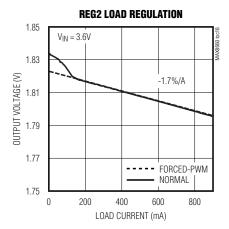

| V2 Load Regulation                |                                                              | Load = 0 to 900mA                                               |                             |       | -1.7  |       | %/A   |

| V2 Line Regulation                |                                                              |                                                                 |                             |       | 0.15  |       | %/V   |

| SET2 Input Leakage Current        |                                                              |                                                                 |                             |       | 0.01  |       | μΑ    |

| V2 Dropout Voltage                |                                                              | Load = 900mA (Note                                              | s 3, 4)                     |       | 225   |       | mV    |

| p-Channel On-Resistance           |                                                              |                                                                 |                             |       | 0.18  |       | Ω     |

| n-Channel On-Resistance           |                                                              |                                                                 |                             |       | 0.15  |       | Ω     |

| p-Channel Current-Limit Threshold |                                                              |                                                                 |                             | 1.10  | 1.30  | 1.50  | Α     |

| n-Channel Zero Crossing Threshold |                                                              |                                                                 |                             |       | 25    |       | mA    |

| n-Channel Negative Current Limit  |                                                              | Forced-PWM mode of                                              | only                        |       | -800  |       | mA    |

| REG2 Maximum Output Current       | I <sub>OUT2</sub>                                            | 2.6V ≤ V <sub>PV2</sub> ≤ 6V (No                                | te 5)                       | 0.9   |       |       | Α     |

| V2 Bias Current                   | İ                                                            |                                                                 |                             |       | 5     |       | μΑ    |

| LX2 Leakage Current               |                                                              | $V_{PV2} = 6V$ ,<br>LX2 = PG2 or PV2,                           | T <sub>A</sub> = +25°C      | -2    | ±0.03 | +2    | μΑ    |

|                                   |                                                              | $V_{EN2} = 0V$                                                  | $T_A = +85^{\circ}C$        |       | 0.2   |       | ,     |

| Soft-Start Ramp Rate              |                                                              | To V2 = 1.8V (total ra all V2 output voltages                   |                             | 2     | 4     | 6     | mV/μs |

| V5 to V2 Enable Time              | tvmHvSH2                                                     | Figure 6                                                        |                             |       | 350   |       | μs    |

| Internal Off-Discharge Resistance |                                                              |                                                                 |                             |       | 650   |       | Ω     |

| Minimum Duty Cycle                |                                                              | Forced-PWM mode of skip mode is 0%                              | only; min duty cycle in     |       | 16.7  |       | %     |

| Maximum Duty Cycle                |                                                              |                                                                 |                             |       | 100   |       | %     |

| REG3—SYNCHRONOUS STEP-DO          | WN DC-DC                                                     | CONVERTER                                                       |                             |       |       |       |       |

| V3 Output Voltage Accuracy        | V3                                                           | REG3 default output load = 600mA                                | voltage, $V_{PV3} = 3.6V$ , | 1.379 | 1.400 | 1.421 | V     |

| vo Output Voltage Accuracy        | VS                                                           | REG3 serial programmed from 0.9V to 1.8V, load = 600mA (Note 6) |                             | -1.5  |       | +1.5  | %     |

| V3 Load Regulation                |                                                              | Load = 0 to 1600mA                                              |                             |       | -17   |       | mV/A  |

| V3 Line Regulation                |                                                              | (Note 7)                                                        |                             |       | 0.05  |       | %/V   |

| p-Channel On-Resistance           |                                                              |                                                                 |                             |       | 0.12  |       | Ω     |

| n-Channel On-Resistance           |                                                              |                                                                 |                             |       | 0.08  |       | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.) (Note 2)

| PARAMETER                         | SYMBOL   | CONE                                                    | DITIONS                                       | MIN  | TYP   | MAX   | UNITS |

|-----------------------------------|----------|---------------------------------------------------------|-----------------------------------------------|------|-------|-------|-------|

| p-Channel Current-Limit Threshold |          |                                                         |                                               | 1.85 | 2.15  | 2.45  | Α     |

| n-Channel Zero-Crossing Threshold |          |                                                         |                                               |      | 25    |       | mA    |

| n-Channel Negative Current Limit  |          | Forced-PWM mode o                                       | nly                                           |      | -0.8  |       | Α     |

| REG3 Maximum Output Current       | lout3    | 2.6V ≤ V <sub>PV3</sub> ≤ 6V (No                        | ote 5)                                        | 1.6  |       |       | Α     |

| V3 Bias Current                   |          |                                                         |                                               |      | 0.01  |       | μΑ    |

| LX3 Leakage Current               |          | $V_{PV3} = 6V,$<br>LX3 = PG3 or PV3,                    | T <sub>A</sub> = +25°C                        | -2   | +0.03 | +2    | μΑ    |

|                                   |          | $V_{EN34} = 0V$                                         | T <sub>A</sub> = +85°C                        |      | 0.24  |       |       |

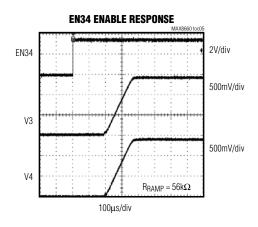

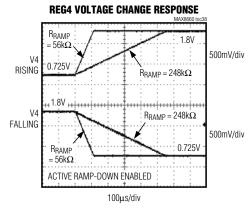

| Soft-Start Ramp Rate              |          | $R_{RAMP} = 56k\Omega$ to 1.4                           | V                                             |      | 8     |       | mV/µs |

| V3 Dynamic-Change Ramp Rate       |          | $R_{RAMP} = 56k\Omega$                                  |                                               |      | 10    |       | mV/µs |

| EN34 to V3 Enable Time            | tPHLVTH3 | Powering up to 1.4V, F                                  | igure 6, R <sub>RAMP</sub> = $56$ kΩ          |      | 400   |       | μs    |

| Internal Off-Discharge Resistance |          |                                                         |                                               |      | 550   |       | Ω     |

| Minimum Duty Cycle                |          | Forced-PWM mode only, min duty cycle in skip mode is 0% |                                               |      | 16.7  |       | %     |

| Maximum Duty Cycle                |          |                                                         |                                               |      | 100   |       | %     |

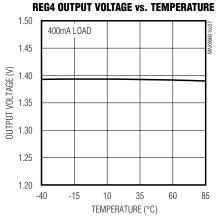

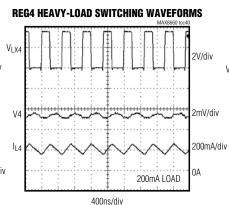

| REG4—SYNCHRONOUS STEP-DO          | WN DC-DC | CONVERTER                                               |                                               |      |       |       |       |

| VA Output Valtaga Assuma          | V4       | REG4 default output VPV3 = 3.6V, load = 2               | default output voltage,<br>3.6V, load = 200mA |      | 1.400 | 1.421 | V     |

| V4 Output Voltage Accuracy        | V4       | REG4 serial program load = 200mA (Note of               | med from 0.9V to 1.8V,<br>6)                  | -1.5 |       | +1.5  | %     |

| V4 Load Regulation                |          | Load = 0 to 400mA                                       |                                               |      | -40   |       | mV/A  |

| V4 Line Regulation                |          | (Note 7)                                                |                                               |      | 0.1   |       | %/V   |

| p-Channel On-Resistance           |          |                                                         |                                               |      | 0.37  |       | Ω     |

| n-Channel On-Resistance           |          |                                                         |                                               |      | 0.3   |       | Ω     |

| p-Channel Current-Limit Threshold |          |                                                         |                                               | 0.05 | 0.78  | 0.90  | А     |

| n-Channel Zero-Crossing Threshold |          |                                                         |                                               |      | 25    |       | mA    |

| n-Channel Negative Current Limit  |          | Forced-PWM mode o                                       | nly                                           |      | -975  |       | mA    |

| REG4 Maximum Output Current       | lout4    | 2.6V ≤ V <sub>PV3</sub> ≤ 6V (No                        | te 5)                                         | 0.4  |       |       | А     |

| V4 Bias Current                   |          |                                                         |                                               |      | 0.01  |       | μΑ    |

| LX4 Leakage Current               |          | $V_{PV4} = 6V$ ,<br>LX4 = PG4 or PV4,                   | T <sub>A</sub> = +25°C                        | -2   | ±0.02 | +2    | μΑ    |

| 271 Zsanago Garroni               |          | $V_{EN34} = 0V$                                         | $T_A = +85^{\circ}C$                          |      | 0.12  |       | μ, .  |

| Soft-Start Ramp Rate              |          | $R_{RAMP} = 56k\Omega$ to 1.4V                          |                                               |      | 8     |       | mV/µs |

| V4 Dynamic-Change Ramp Rate       |          | $R_{RAMP} = 56k\Omega$                                  |                                               |      | 10    |       | mV/µs |

| EN34 to V4 Enable Time            | tPHLVTH4 | Powering up to 1.4V, Figure 6, $R_{RAMP} = 56k\Omega$   |                                               |      | 400   |       | μs    |

| Internal Off-Discharge Resistance |          |                                                         |                                               |      | 550   |       | Ω     |

| Minimum Duty Cycle                |          | Forced-PWM mode only, min duty cycle in skip mode is 0% |                                               |      | 16.7  |       | %     |

| Maximum Duty Cycle                |          |                                                         |                                               |      | 100   |       | %     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                   | SYMBOL             | CONDITIONS                                                                              | MIN   | TYP   | MAX   | UNITS             |

|-----------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|-------|-------|-------|-------------------|

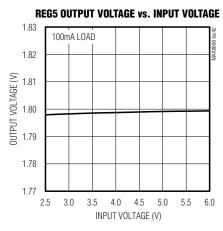

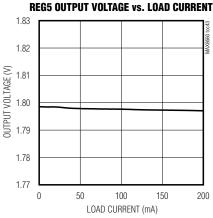

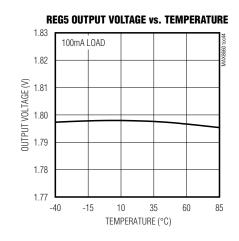

| REG5 LDO                                                                    |                    |                                                                                         | I     |       |       | ı                 |

| IN5 Input Voltage Range                                                     | V <sub>IN5</sub>   |                                                                                         | 2.35  |       | VIN   | V                 |

| VE Output Valtage                                                           | VE                 | REG5 default output voltage, $2.35V \le V_{IN5} \le 6V$ , load = 0 to 200mA             | 1.764 | 1.800 | 1.836 | V                 |

| V5 Output Voltage                                                           | V5                 | REG5 serial programmed from 1.7V to 2.0, $2.35V \le V_{IN5} \le 6V$ , load = 0 to 200mA | -2    |       | +2    | %                 |

| V5 Output Current Limit                                                     | I <sub>OUT5</sub>  |                                                                                         | 225   | 350   | 500   | mA                |

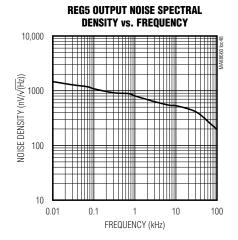

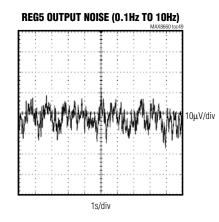

| V5 Output-Voltage Noise                                                     |                    | 10Hz to 100kHz, I <sub>OUT5</sub> = 10mA                                                |       | 160   |       | μV <sub>RMS</sub> |

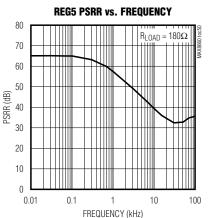

| V5 Power-Supply Rejection                                                   |                    | $V_{IN5} = (V5 + 1V), I_{OUT5} = 10mA, f = 10kHz$                                       |       | 40    |       | dB                |

| V5 Soft-Start Ramp Rate                                                     |                    | Powering up to 1.8V (total ramp time is 225µs for all V5 output voltages)               | 5     | 7     | 9     | mV/µs             |

| EN5 to V5 Enable Time                                                       | tsehvmh            | Figure 6                                                                                |       | 290   |       | μs                |

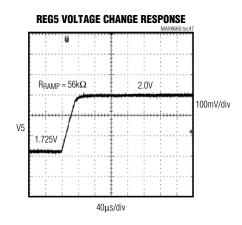

| V5 Dynamic-Change Ramp Rate                                                 |                    | $R_{RAMP} = 56k\Omega$                                                                  |       | 10    |       | mV/µs             |

| Internal Off-Discharge Resistance                                           |                    |                                                                                         |       | 2     |       | kΩ                |

| REG6, REG7 LDOs                                                             |                    |                                                                                         |       |       |       |                   |

| IN67 Input Voltage Range                                                    | V <sub>IN67</sub>  |                                                                                         | 2.35  |       | VIN   | V                 |

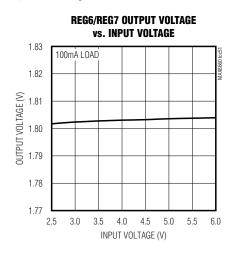

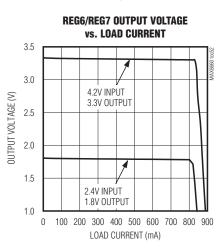

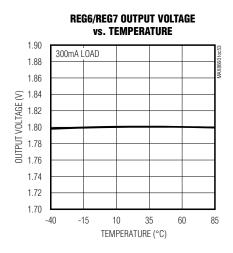

| REG6 and REG7 Output Voltage<br>(POR Default to 0V, Set by Serial<br>Input) | V6<br>V7           | Setting from 1.8V to 3.3V in 0.1V steps, load = 0 to 300mA                              | -3    |       | +3    | %                 |

| V6, V7 Dropout Voltage                                                      |                    | 3V mode, load = 300mA (Note 3)                                                          |       | 55    | 100   | mV                |

| V6, V7 Output Current Limit                                                 | IOUT6<br>IOUT7     | V <sub>IN67</sub> = 3.6V                                                                |       | 750   |       | mA                |

| V6, V7 Soft-Start Ramp Rate                                                 |                    | Powering up to 3.3V, (total ramp time is 450µs for all V6/V7 output voltages)           | 5     | 7     | 9     | mV/μs             |

| Internal Off-Discharge Resistance                                           |                    |                                                                                         |       | 350   |       | Ω                 |

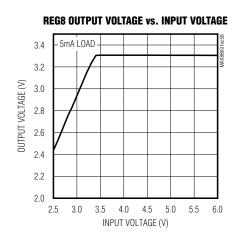

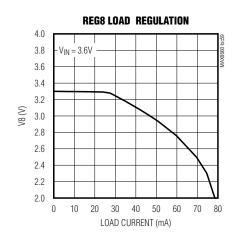

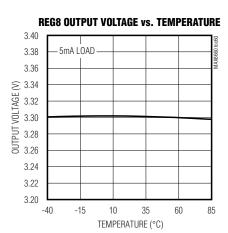

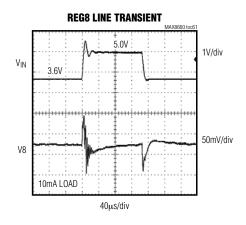

| REG8 ALWAYS-ON LDO                                                          |                    |                                                                                         | U.    |       |       | <u> </u>          |

| VO Output Valtage                                                           | \/0                | Load = 0 to 15mA                                                                        | 3.168 | 3.300 | 3.432 | V                 |

| V8 Output Voltage                                                           | V8                 | Load = 30mA                                                                             | 2.800 | 3.2   | 3.432 | V                 |

| V8 Dropout Voltage                                                          |                    | Load = 15mA (Note 3)                                                                    |       | 180   |       | mV                |

| V8 Output Current Limit                                                     | I <sub>OUT8</sub>  | V8 = 2.5V                                                                               | 30    | 70    | 135   | mA                |

| Internal Off-Discharge Resistance                                           |                    |                                                                                         |       | 1.5   |       | kΩ                |

| LOW-BATTERY DETECTOR (LBF                                                   | , LBR, LBO)        |                                                                                         |       |       |       |                   |

| Low-Battery Falling Threshold                                               | V <sub>LBFTH</sub> |                                                                                         | 1.182 | 1.200 | 1.218 | V                 |

| Low-Battery Rising Threshold                                                | V <sub>LBRTH</sub> |                                                                                         | 1.231 | 1.250 | 1.268 | V                 |

| LBO, RSO Output-High Leakage Current                                        |                    | V <sub>IN</sub> = 6V, T <sub>A</sub> = +25°C                                            |       |       | 0.2   | μΑ                |

| LBO Output Low Level                                                        |                    | 2.6V ≤ V <sub>IN</sub> ≤ 6V, sinking 3mA                                                |       |       | 0.2   | V                 |

| LDO Odipul Low Level                                                        |                    | V <sub>IN</sub> = 1V, sinking 100μA                                                     |       |       | 0.4   | V                 |

| Minimum V <sub>IN</sub> for LBO Assertion                                   |                    | LBO is forced low when the device is in UVLO                                            | 1     |       |       | V                 |

WWW.DataSneet4U.com

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $T_{A} = +25$ °C.) (Note 2)

| PARAMETER                                 | SYMBOL          | CONDITIONS                                     | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|-----------------|------------------------------------------------|------|------|------|-------|

| LBO Deassert Delay                        | tvbhbfh         | Figure 6                                       | 0    | 3    |      | μs    |

| 105 11001 10: 0                           |                 | T <sub>A</sub> = +25°C                         | -50  | 0    | +50  |       |

| LBF and LBR Input Bias Current            |                 | T <sub>A</sub> = +85°C                         |      | 0.5  |      | nA    |

| RESET (MR, RSO)                           | •               |                                                |      |      |      |       |

| RSO Threshold                             | VRSOTH          | Voltage on V8, falling, hysteresis is 5% (typ) | 2.1  | 2.2  | 2.3  | V     |

| RSO Deassert Delay                        | tvbhrsth        | Figure 6                                       | 20   | 24   | 28   | ms    |

| RSO Output-High Leakage Current           |                 | V <sub>IN</sub> = 6V, T <sub>A</sub> = +25°C   |      |      | 0.2  | μΑ    |

|                                           |                 | 2.6V ≤ V <sub>IN</sub> ≤ 6V, sinking 3mA       |      |      | 0.2  |       |

| RSO Output Low Level                      |                 | V <sub>IN</sub> = 1V, sinking 100μA            |      |      | 0.4  | V     |

| Minimum V <sub>IN</sub> for RSO Assertion |                 | RSO is forced low when the device is in UVLO   | 1    |      |      | V     |

| MR Input High Level                       |                 | $2.6V \le V_{IN} \le 6V$                       | 1.4  |      |      | V     |

| MR Input Low Level                        |                 | $2.6V \le V_{IN} \le 6V$                       |      |      | 0.4  | V     |

| MR Input Leakage Current                  |                 | V <sub>IN</sub> = 6V, T <sub>A</sub> = +25°C   | -0.2 |      | +0.2 | μΑ    |

| MR Minimum Pulse Width                    | t <sub>MR</sub> |                                                |      | 1    |      | μs    |

| THERMAL-OVERLOAD PROTEC                   | TION            |                                                |      |      |      |       |

| Thermal-Shutdown Temperature              |                 | T <sub>J</sub> rising                          |      | +160 |      | °C    |

| Thermal-Shutdown Hysteresis               |                 |                                                |      | 15   |      | °C    |

| ENABLE INPUTS (EN1, EN2, EN               | 34, EN5)        |                                                |      |      |      |       |

| EN_ Input High Level                      |                 | $2.6V \le V_{IN} \le 6V$                       | 1.4  |      |      | V     |

| EN_ Input Low Level                       |                 | $2.6V \le V_{IN} \le 6V$                       |      |      | 0.4  | V     |

| EN_ Input Leakage Current                 |                 | V <sub>IN</sub> = 6V, T <sub>A</sub> = +25°C   | -0.2 |      | +0.2 | μΑ    |

| I <sup>2</sup> C LOGIC (SDA, SCL, SRAD)   |                 |                                                |      |      |      |       |

| SCL, SDA Input High Voltage               |                 |                                                | 1.4  |      |      | V     |

| SCL, SDA Input Low Voltage                |                 |                                                |      |      | 0.4  | V     |

| SCL, SDA Input Hysteresis                 |                 |                                                |      | 0.1  |      | V     |

| SCL, SDA Input Current                    |                 | $T_A = +25$ °C, $IN = AGND$ , $V_{IN} = 6V$    | -10  |      | +10  | μΑ    |

| SDA Output Low Voltage                    |                 | 2.6V ≤ V <sub>IN</sub> ≤ 6V, sinking 3mA       |      |      | 0.2  | V     |

| SRAD Input High Level                     |                 | $2.6V \le V_{IN} \le 6V$                       | 1.4  |      |      | V     |

| SRAD Input Low Level                      |                 | $2.6V \le V_{IN} \le 6V$                       |      |      | 0.4  | V     |

| SRAD Input Leakage Current                |                 | $V_{IN} = 6V, T_A = +25^{\circ}C$              | -0.2 |      | +0.2 | μΑ    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{IN5} = V_{IN67} = V_{IN8} = 3.6V$ , Figure 3,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                                                              | SYMBOL  | CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------------------------------------------------------|---------|------------|-----|-----|-----|-------|

| I <sup>2</sup> C TIMING                                                                                | •       |            |     |     |     | •     |

| Clock Frequency                                                                                        | fscl    |            |     |     | 400 | kHz   |

| Hold Time (Repeated) START Condition                                                                   | thd;sta | Figure 8   | 0.6 |     |     | μs    |

| CLK Low Period                                                                                         | tLOW    |            | 1.3 |     |     | μs    |

| CLK High Period                                                                                        | tHIGH   |            | 0.6 |     |     | μs    |

| Set-Up Time for a Repeated START Condition                                                             | tsu;sta | Figure 8   | 0.6 |     |     | μs    |

| DATA Hold Time                                                                                         | thd;dat | Figure 9   | 0   |     |     | μs    |

| DATA Set-Up Time                                                                                       | tsu;dat | Figure 9   | 100 |     |     | ns    |

| Set-Up Time for STOP Condition                                                                         | tsu;sto | Figure 8   | 0.6 |     |     | μs    |

| Bus-Free Time Between STOP and START                                                                   | tBUF    |            | 1.3 |     |     | μs    |

| Maximum Pulse Width of Spikes that Must Be Suppressed by the Input Filter of Both DATA and CLK Signals |         |            |     | 50  |     | ns    |

Note 2: Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed through correlation using statistical quality control (SQC) methods.

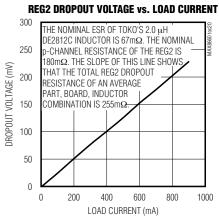

Note 3: The dropout voltage is defined as VIN - VOUT when VOUT is 100mV below the nominal value of VOUT.

Note 4: Dropout voltage (VDO) is a function of the p-channel switch resistance (RPCH) and the inductor resistance (RI). The given values assume  $R_L = 50m\Omega$  for the REG1 inductor and  $67m\Omega$  for the REG2 inductor:

$$V_{DO} = I_{LOAD} (R_P + R_L)$$

Note 5: The maximum output current (IOUT(MAX)) is:

$$I_{OUT(MAX)} = \frac{I_{LIM} - \frac{V_{OUT}(1-D)}{2 \times f \times L}}{1 + (R_N + R_L) \frac{(1-D)}{2 \times f \times L}}$$

where:

R<sub>N</sub> = n-channel synchronous rectifier RDS (on)

$R_P = p$ -channel power switch RDS (on)

R<sub>L</sub> = external inductor ESR

IOUT(MAX) = maximum output current provided by the PMIC

IOUT(TARGET) = maximum desired output current

f = operating frequency minimum

L = external inductor value

Note 6: Tested at 1.4V, default output voltage.

Note 7: All output voltages are possible in normal mode. In forced-PWM mode, the minimum output voltage is limited by 0.167 x  $V_{IN}$ . For example, with  $V_{IN} = 5.688V$ , the minimum output is 0.95V.

N/IXI/N

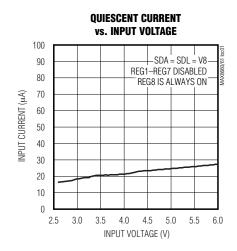

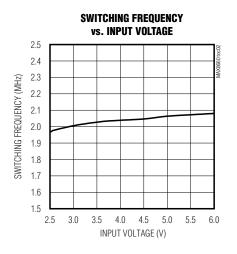

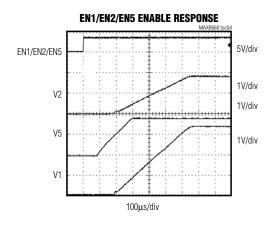

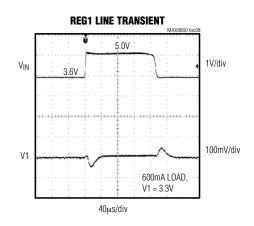

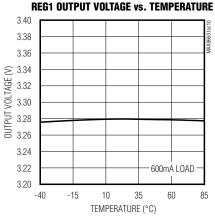

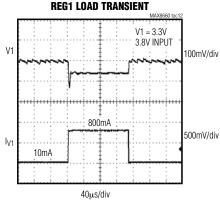

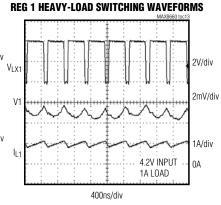

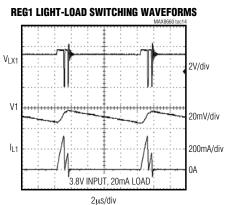

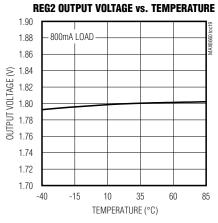

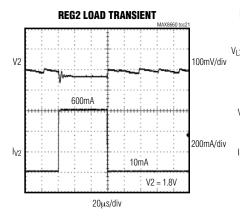

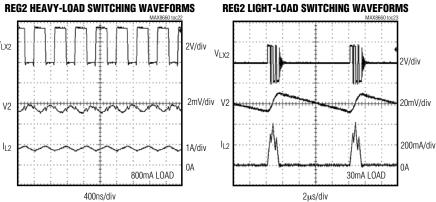

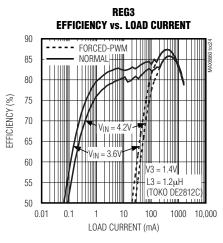

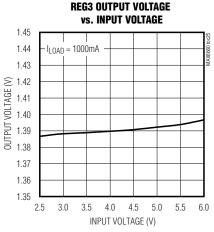

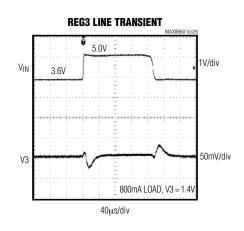

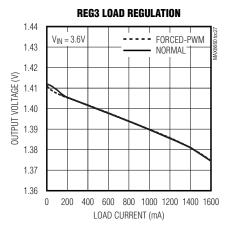

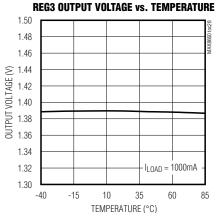

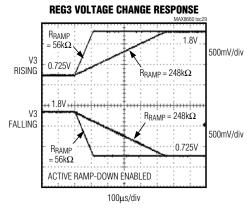

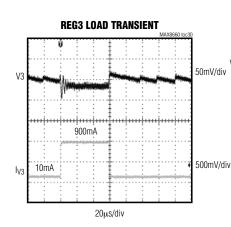

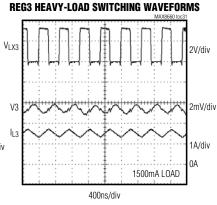

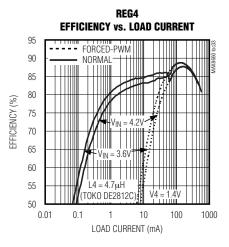

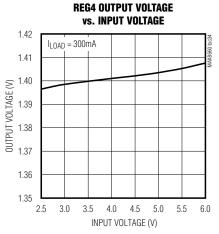

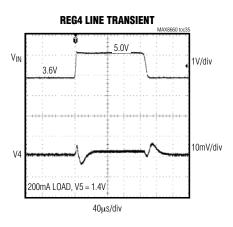

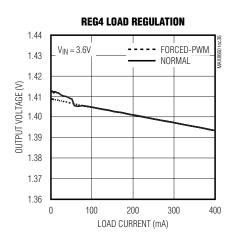

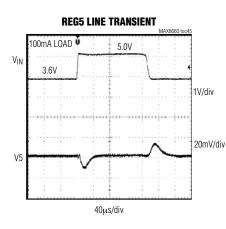

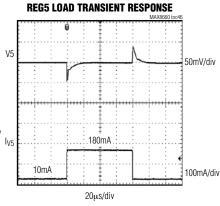

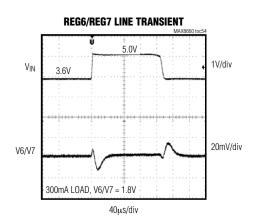

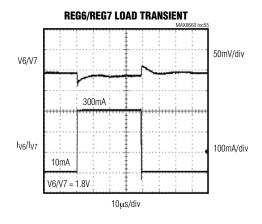

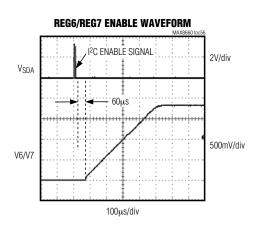

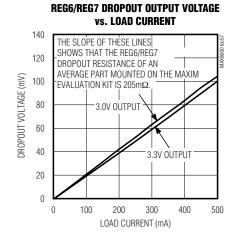

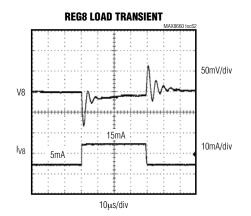

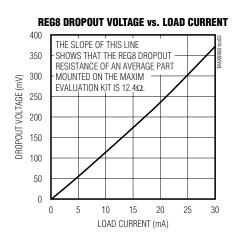

### **Typical Operating Characteristics**

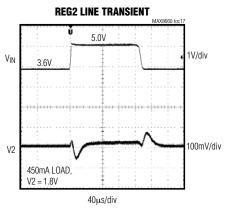

(Circuit of Figure 3,  $V_{IN} = 3.6V$ ,  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 3, V<sub>IN</sub> = 3.6V, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 3,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 3,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

WWW.DataSheet4U.com

### \_Typical Operating Characteristics (continued)

(Circuit of Figure 3, V<sub>IN</sub> = 3.6V, T<sub>A</sub> = +25°C, unless otherwise noted.)

# REG4 LOAD TRANSIENT RESPONSE MAX8680 10c39 50mV/div 10mA 200mV/div 20μs/div

### Typical Operating Characteristics (continued)

(Circuit of Figure 3,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

WWW.DataSheet4U.com

### Typical Operating Characteristics (continued)

(Circuit of Figure 3,  $V_{IN} = 3.6V$ ,  $T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Circuit of Figure 3,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

WWW.DataSheet4U.com

### **Pin Description**

|     |         |            | Pin Description                                                                                                                                                                                                                                                                                                                          |

|-----|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NA      | ME         | FUNCTION                                                                                                                                                                                                                                                                                                                                 |

|     | MAX8660 | MAX8661    | TONOTION                                                                                                                                                                                                                                                                                                                                 |

| 1   | IN5     | IN5        | REG5 Power Input. Connect IN5 to IN to ensure V5 rises first to meet Intel sequencing requirements. If adherence to Intel specifications is not required, IN5 can be connected to V1, V2, or another supply between 2.35V and V <sub>IN</sub> . See the <i>Linear Regulators (REG5–REG8)</i> section for more information.               |

| 2   | V5      | V5         | REG5 Linear-Regulator Output. V5 defaults to 1.8V and is adjustable from 1.7V to 2.0V through the serial interface. The input to the V5 regulator is IN5. Use V5 to power $VCC\_MVT$ , $VCC\_BG$ , $VCC\_OSC13M$ , and $VCC\_PLL$ on Intel XScale processors. V5 is internally pulled to AGND through $2k\Omega$ when REG5 is shut down. |

| 3   | PV4     | PV4        | REG4 Power Input. Connect a 4.7µF ceramic capacitor from PV4 to PG4. All PV pins and IN must be connected together externally.                                                                                                                                                                                                           |

| 4   | LX4     | LX4        | REG4 Switching Node. Connect LX4 to the REG4 inductor. LX4 is high impedance when REG4 is shut down.                                                                                                                                                                                                                                     |

| 5   | PG4     | PG4        | REG4 Power Ground. Connect PG1, PG2, PG3, PG4, and AGND together. Refer to the MAX8660 EV kit data sheet for more information.                                                                                                                                                                                                           |

| 6   | SET2    | SET2       | REG2 Voltage Select Input. SET2 is a tri-level logic input. Connect SET2 to select the V2 output voltage as detailed in Table 4. The REG2 output voltage selected by SET2 is latched at the end of the REG2 soft-start period. Changes to SET2 after the startup period have no effect.                                                  |

| 7   | V6      | V6         | REG6 Linear-Regulator Output. REG6 is activated and programmed through the serial interface to output from 1.8V to 3.3V in 0.1V steps. REG6 is off by default. V6 is internally pulled to AGND through 350Ω when REG6 is shut down. V6 optionally powers <i>VCC_CARD1</i> on Intel XScale processors.                                    |

| 0   | IN67    | _          | REG6 and REG7 Power Input. IN67 is typically connected to IN. IN67 can also be connected to any supply between 2.35V to V <sub>IN</sub> .                                                                                                                                                                                                |

| 8   | _       | IN6        | REG6 Power Input. IN6 is typically connected to IN. IN6 can also be connected to any supply between 2.35V to V <sub>IN</sub> .                                                                                                                                                                                                           |

| 9   | V7      | _          | REG7 Linear-Regulator Output. REG7 is activated and programmed through the serial interface to output from 1.8V to 3.3V in 0.1V steps. REG7 is off by default. V7 is internally pulled to AGND through 350Ω when REG7 is shut down. V7 optionally powers <i>VCC_CARD2</i> on Intel XScale processors.                                    |

|     | _       | N.C.       | No Internal Connection                                                                                                                                                                                                                                                                                                                   |

| 10  | V2      | V2         | REG2 Voltage Sense Input. Connect V2 directly to the REG2 output voltage. The output voltage of REG2 is selected by SET2. V2 is internally pulled to AGND through $650\Omega$ when REG2 is shut down. V2 powers $VCC\_MEM$ on Intel XScale processors.                                                                                   |

| 11  | SCL     | SCL        | Serial-Clock Input. See the <i>I</i> <sup>2</sup> <i>C Interface</i> section.                                                                                                                                                                                                                                                            |

| 12  | SDA     | SDA        | Serial-Data Input. See the I <sup>2</sup> C Interface section.                                                                                                                                                                                                                                                                           |

| 13  | LBO     | <u>LBO</u> | Low-Battery Output. $\overline{\text{LBO}}$ is an open-drain output that pulls low when LBF is below its threshold. $\overline{\text{LBO}}$ typically connects to the $nBATT\_FAULT$ input of the Intel XScale processor to indicate that the battery has been removed or discharged.                                                    |

| 14  | PV2     | PV2        | REG2 Power Input. Connect a 4.7µF ceramic capacitor from PV2 to PG2. All PV pins and IN must be connected together externally.                                                                                                                                                                                                           |

| 15  | LX2     | LX2        | REG2 Switching Node. Connect LX2 to the REG2 inductor. LX2 is high impedance when REG2 is shut down.                                                                                                                                                                                                                                     |

| 16  | PG2     | PG2        | REG2 Power Ground. Connect PG1, PG2, PG3, PG4, and AGND together. Refer to the MAX8660 EV kit data sheet for more information.                                                                                                                                                                                                           |

| 17  | IN8     | IN8        | REG8 Input Power Connection. IN8 must be connected to IN.                                                                                                                                                                                                                                                                                |

| 18  | IN      | IN         | Main Battery Input. This input provides power to the IC. Connect a 0.47µF ceramic capacitor from IN to AGND.                                                                                                                                                                                                                             |

### Pin Description (continued)

|     | NA      | ME      |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | MAX8660 | MAX8661 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 19  | AGND    | AGND    | Analog Ground. Connect PG1, PG2, PG3, PG4, and AGND together. Refer to the MAX8660 EV kit data sheet for more information.                                                                                                                                                                                                                                                                                                                                 |

| 20  | V8      | V8      | REG8 Always-On 3.3V LDO Output. REG8 is the first regulator that powers up in the MAX8660/MAX8661. REG8 is supplied from IN and supplies up to 30mA. V8 is internally pulled to AGND through 1.5k $\Omega$ during IN undervoltage or overvoltage lockout. Connect V8 to $VCC\_BBATT$ on Intel XScale processors.                                                                                                                                           |

| 21  | LBF     | LBF     | Low-Battery Detect Falling Input. The LBF threshold is 1.20V. Connect LBF to LBR for 50mV hysteresis. Use a three-resistor voltage-divider for larger hysteresis. LBF sets the falling voltage at which LBO goes low. See the <i>Low-Battery Detector</i> (LBO, LBF, LBR) section for more information.                                                                                                                                                    |

| 22  | LBR     | LBR     | Low-Battery Detect Rising Input. The LBR threshold is 1.25V. Connect LBF to LBR for 50mV hysteresis. Use a three-resistor voltage-divider for larger hysteresis. LBR sets the rising voltage at which LBO goes high. See the <i>Low-Battery Detector</i> (LBO, LBF, LBR) section for more information.                                                                                                                                                     |

| 23  | MR      | MR      | Manual Reset Input. A low $\overline{\text{MR}}$ input causes $\overline{\text{RSO}}$ to go low and resets all serial programmed registers to their default values. See the <i>Reset Output (RSO)</i> and $\overline{\text{MR}}$ Input section for more information.                                                                                                                                                                                       |

| 24  | RAMP    | RAMP    | Ramp-Rate Input. Connect a resistor from RAMP to AGND to set the regulator ramp rates. See the <i>Ramp-Rate Control (RAMP)</i> section for more information.                                                                                                                                                                                                                                                                                               |

| 25  | EN5     | EN5     | REG5 Enable Input. Drive EN5 high to turn on REG5. EN5 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. EN5 is typically driven by the SYS_EN output of an Intel XScale processor.                                                                                                                                                                                                                         |

| 26  | PG3     | PG3     | REG3 Power Ground. Connect PG1, PG2, PG3, PG4, and AGND together. Refer to the MAX8660 EV kit data sheet for more information.                                                                                                                                                                                                                                                                                                                             |

| 27  | LX3     | LX3     | REG3 Switching Node. Connect LX3 to the REG3 inductor. LX3 is high impedance when REG3 is shut down.                                                                                                                                                                                                                                                                                                                                                       |

| 28  | PV3     | PV3     | REG3 Power Input. Connect a 4.7μF ceramic capacitor from PV3 to PG3. All PV pins and IN must be connected together externally.                                                                                                                                                                                                                                                                                                                             |

| 29  | RSO     | RSO     | Open-Drain Reset Output. $\overline{\text{RSO}}$ typically connects to the nRESET input on an Intel XScale processor. An output low from the MAX8660/MAX8661 $\overline{\text{RSO}}$ resets all serial programmed registers to their default values and causes the processor to enter its reset state. See the <i>Reset Output (RSO)</i> and $\overline{\text{MR}}$ Input section for more information.                                                    |

| 30  | V3      | V3      | REG3 Voltage Sense Input. Connect V3 directly to the REG3 output voltage. The output voltage defaults to 1.4V and is adjustable from 0.725V to 1.8V through the serial interface. V3 is internally pulled to AGND through $550\Omega$ when REG3 is shut down. V3 connects to $VCC\_APPS$ on Intel XScale processors.                                                                                                                                       |

| 31  | EN34    | EN34    | REG3 and REG4 Active-High Hardware Enable Input. Drive EN34 high to enable both REG3 and REG4. Drive EN34 low to allow the serial interface to enable REG3 and REG4 independently. EN34 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. EN34 is typically driven by the <i>PWR_EN</i> output of an Intel XScale processor. See the <i>REG3/REG4 Enable (EN34, EN3, EN4)</i> section for more information. |

| 32  | EN2     | EN2     | REG2 Enable Input. Drive EN2 high to turn on REG2. EN2 has hysteresis so that an RC can be used to implement manual sequencing with respect to other inputs. EN2 is typically driven by the <i>SYS_EN</i> output of an Intel XScale processor.                                                                                                                                                                                                             |

| 33  | SRAD    | SRAD    | Serial-Address Input. Connect SRAD to AGND for a 7-bit slave address of 0110 100 (0x68). Connect SRAD to IN to change the address to 0110 101 (0x6A). The eighth slave address bit is always zero since the MAX8660/MAX8661 are write-only. See the <i>Slave Address</i> section for more information.                                                                                                                                                     |

| 34  | PG1     | _       | REG1 Power Ground. Connect PG1, PG2, PG3, PG4, and AGND together. Refer to the MAX8660 EV kit data sheet for more information.                                                                                                                                                                                                                                                                                                                             |

|     | _       | GND     | Ground. Connect all GND pins to EP.                                                                                                                                                                                                                                                                                                                                                                                                                        |

### **Pin Description (continued)**

| PIN   | NA      | ME      | FUNCTION                                                                                                                                                                                                                                                                                                           |

|-------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - 111 | MAX8660 | MAX8661 | TONCTION                                                                                                                                                                                                                                                                                                           |

| 35    | LX1     | _       | REG1 Switching Node. Connect LX1 to the REG1 inductor. LX1 is high impedance when REG1 is shutdown.                                                                                                                                                                                                                |

|       | _       | N.C.    | No Internal Connection                                                                                                                                                                                                                                                                                             |