INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC01 January 1995

**Philips Semiconductors**

# SAA2501

| CONTENTS         |                                                                       | 7.20.13          | Speed limitations of the L3 interface           |

|------------------|-----------------------------------------------------------------------|------------------|-------------------------------------------------|

|                  |                                                                       | 7.20.14          | Default item data values after reset            |

|                  | FEATURES                                                              | 8                | APPENDIX                                        |

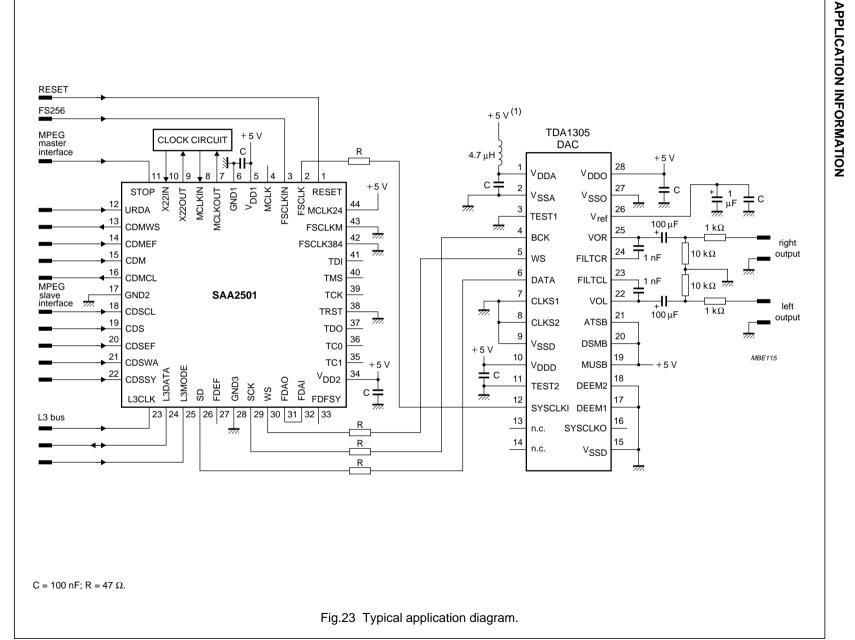

| 2                | APPLICATION                                                           | 8.1              | Preliminary specification 3-line 'L3' interface |

| 3                | GENERAL DESCRIPTION                                                   | 8.1.1            | Introduction                                    |

| 4                | ORDERING INFORMATION                                                  | 8.1.1.1          | Addressing mode                                 |

| 5                | BLOCK DIAGRAM                                                         | 8.1.1.2          | Special function operational address            |

| 6                | PINNING                                                               | 8.1.1.3          | Data mode                                       |

| 7                | FUNCTIONAL DESCRIPTION                                                | 8.1.1.4<br>8.1.2 | Halt mode<br>Device interface reset             |

| -                |                                                                       | 8.1.3            | Extended addressing                             |

| 7.1              | Coding system                                                         | 8.1.3.1          | Operational address declaration                 |

| 7.2              | Basic functionality                                                   | 8.1.3.2          | Operational address invalidation                |

| 7.3              | SAA2501 clocks                                                        | 8.1.4            | Example of a data transfer                      |

| 7.4              | Crystal oscillator                                                    | 8.1.5            | Timing requirements                             |

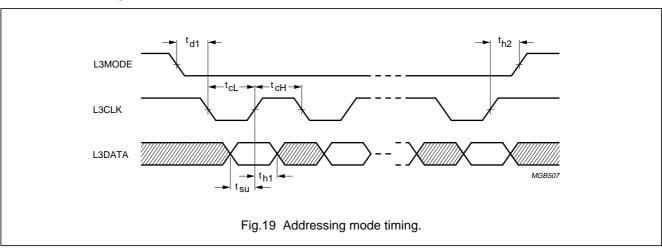

| 7.5              | Clock frequencies when using the slave input                          | 8.1.5.1          | Addressing mode                                 |

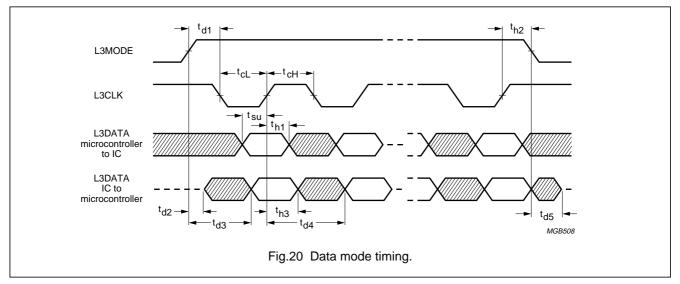

| 7.6              | Clock frequencies when using the master input                         | 8.1.5.2          | Data mode                                       |

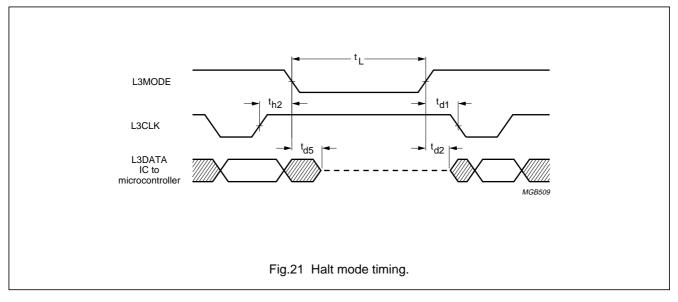

| 7.7              | Target applications; applying the SAA2501 with                        | 8.1.5.3          | Halt mode                                       |

| 7.0              | 2 ISO/MPEG sources                                                    | 8.2              | SAA2501 L3 protocol enhancement options         |

| 7.8              | Buffered clock outputs                                                | 8.2.1            | Testing L3RDY by polling L3DATA                 |

| 7.9              | Functionality issues                                                  | 8.2.2            | Options to increase the timing accuracy of the  |

| 7.10             | Synchronization to input data bitstreams                              | 0.2.2            | APU coefficient writing                         |

| 7.11<br>7.12     | Master input bit rate selection                                       | 9                | LIMITING VALUES                                 |

| 7.12             | Sample rate selection<br>Handling of errors in the coded input data   |                  |                                                 |

| 7.13             | sub-band filter signals                                               | 10               | DC CHARACTERISTICS                              |

| 7.15             | Baseband audio processing                                             | 11               | AC CHARACTERISTICS                              |

| 7.16             | Decoding control signals                                              | 12               | APPLICATION INFORMATION                         |

| 7.17             | Coded data interfaces                                                 | 13               | PACKAGE OUTLINE                                 |

| 7.17.1           | The coded data master input interface                                 | 14               | SOLDERING                                       |

| 7.17.2           | The coded data slave input interface                                  |                  |                                                 |

| 7.17.3           | Slave input transfer speed of first frame                             | 14.1<br>14.1.1   | Plastic quad flat-packs                         |

| 7.17.4           | Slave input transfer speed of subsequent                              | 14.1.1           | By wave<br>By solder paste reflow               |

|                  | frames                                                                | 14.1.2           | Repairing soldered joints (by hand-held         |

| 7.18             | The sub-band filter interface                                         | 14.1.5           | soldering iron or pulse-heated solder tool)     |

| 7.19             | The baseband output interface                                         | . –              |                                                 |

| 7.20             | The L3 control interface                                              | 15               | DEFINITIONS                                     |

| 7.20.1<br>7.20.2 | L3 signals                                                            | 16               | LIFE SUPPORT APPLICATIONS                       |

| 7.20.2           | L3 transfer types<br>L3 interface initialization at an SAA2501 device |                  |                                                 |

| 7.20.3           | reset                                                                 |                  |                                                 |

| 7.20.4           | L3 interface control                                                  |                  |                                                 |

| 7.20.5           | SAA2501 status                                                        |                  |                                                 |

| 7.20.6           | Data items                                                            |                  |                                                 |

| 7.20.6.1         | General data items                                                    |                  |                                                 |

| 7.20.7           | SAA2501 settings item                                                 |                  |                                                 |

| 7.20.8           | Input data frame header items                                         |                  |                                                 |

| 7.20.9           | Error report item                                                     |                  |                                                 |

| 7.20.9           | Audio service synchronized data item                                  |                  |                                                 |

| 7.20.10          | Ancillary Data/XPAD item                                              |                  |                                                 |

| 1.20.11          |                                                                       |                  |                                                 |

7.20.12 APU coefficients item

# SAA2501

#### **1 FEATURES**

- Advanced error protection

- Integrated audio post processing for control of signal level and inter-channel crosstalk

- Demultiplexing of Program Associated Data (PAD) in the input bitstream

- Automatic digital de-emphasis of the decoded audio signal

- Separate master and slave inputs

**ORDERING INFORMATION**

- Automatic sample frequency and bit-rate switching in master input mode

- Automatic synchronization of input and output interface clocks in master input mode

- Selectable audio output precision; 16, 18, 20 or 22 bit

- Low power consumption

- Decoded sub-band signal and error flag outputs for error concealment.

#### 2 APPLICATION

• Digital Audio Broadcast systems as defined in "Eureka 147".

#### **3 GENERAL DESCRIPTION**

The SAA2501 audio source decoder supports ISO/IEC MPEG layers I and II and all DAB specific features as described in *"Eureka 147 draft specification (EU147)"*.

| TYPE NUMBER |                                                                                                             | PACKAGE     |          |

|-------------|-------------------------------------------------------------------------------------------------------------|-------------|----------|

|             |                                                                                                             | DESCRIPTION | VERSION  |

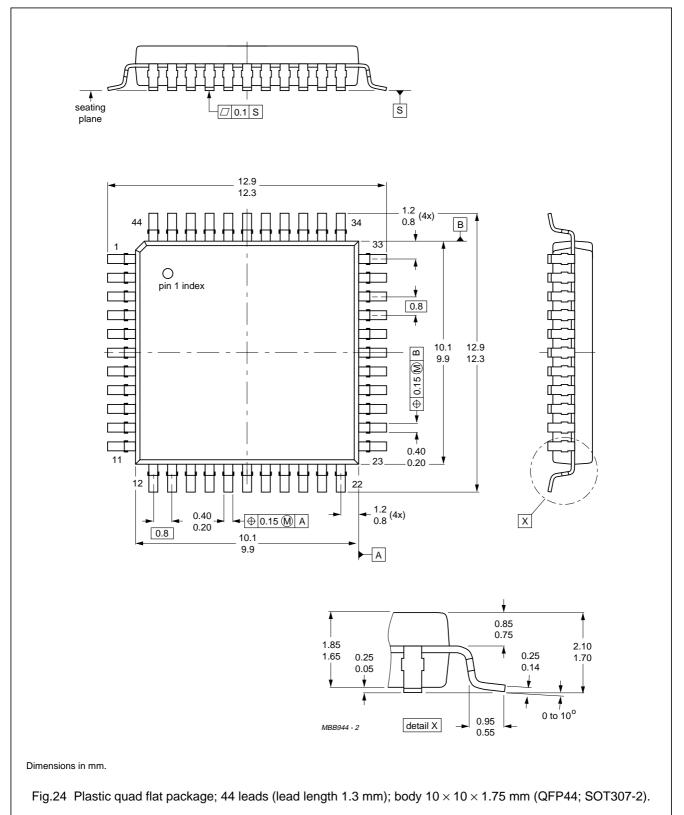

| SAA2501H    | QFP44(1)plastic quad flat package; 44 leads (lead length 1.3 mm);<br>body $10 \times 10 \times 1.75$ mmSOT3 |             | SOT307-2 |

#### Note

4

1. When using IR reflow soldering it is recommended that the Drypack instructions in the "Quality Reference Handbook" (order number 9398 510 63011) are followed.

Supply of this *"ISO/IEC 11172-3"* audio standard Layer I or layer II compatible IC does not convey a licence nor imply a right under any patent, or any Industrial or Intellectual Property Right, to use this IC in any ready-to-use electronic product.

# SAA2501

#### 5 BLOCK DIAGRAM

# SAA2501

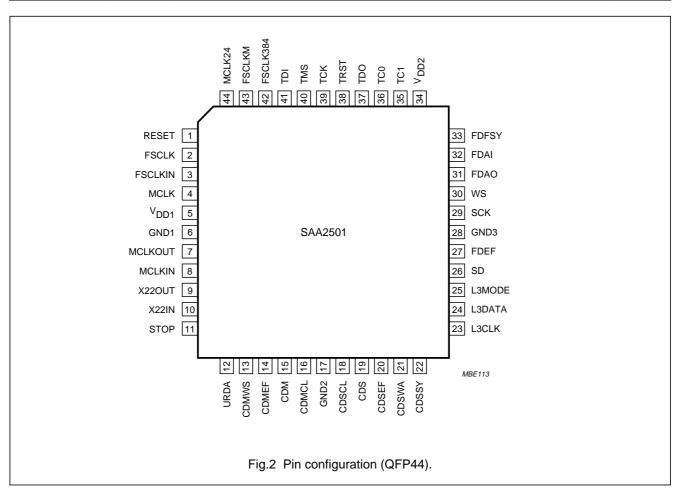

#### 6 PINNING

| SYMBOL           | PIN | DESCRIPTION                                                                                 | TYPE |

|------------------|-----|---------------------------------------------------------------------------------------------|------|

| RESET            | 1   | master reset input                                                                          | I    |

| FSCLK            | 2   | sample rate clock output; buffered signal                                                   |      |

| FSCLKIN          | 3   | sample rate clock signal input (see Table 1)                                                | I    |

| MCLK             | 4   | master clock output; buffered signal                                                        | 0    |

| V <sub>DD1</sub> | 5   | supply voltage 1                                                                            | _    |

| GND1             | 6   | ground 1                                                                                    | _    |

| MCLKOUT          | 7   | master clock oscillator output                                                              | 0    |

| MCLKIN           | 8   | master clock oscillator input or signal input                                               | I    |

| X22OUT           | 9   | 22.579 MHz clock oscillator output                                                          | 0    |

| X22IN            | 10  | 22.579 MHz clock oscillator input or signal input                                           | I    |

| STOP             | 11  | stop decoding input                                                                         | I    |

| URDA             | 12  | unreliable data input; interrupt decoding                                                   | I    |

| CDMWS            | 13  | coded data (master input) word select output                                                | 0    |

| CDMEF            | 14  | coded data (master input) error flag input                                                  | I    |

| CDM              | 15  | ISO/MPEG coded data (master input)                                                          | I    |

| CDMCL            | 16  | coded data (master input) bit clock output                                                  | 0    |

| GND2             | 17  | ground 2                                                                                    | _    |

| CDSCL            | 18  | coded data (slave input) bit clock                                                          | I    |

| CDS              | 19  | ISO/MPEG or EU147 (see Table 8) coded data (slave input)                                    | I    |

| CDSEF            | 20  | coded data (slave input) error flag                                                         |      |

| CDSWA            | 21  | coded data (slave input) burst window signal                                                |      |

| CDSSY            | 22  | coded data (slave input) frame sync                                                         |      |

| L3CLK            | 23  | L3 interface bit clock input                                                                | I    |

| L3DATA           | 24  | L3 interface serial data input/output                                                       |      |

| L3MODE           | 25  | L3 interface address/data select input                                                      |      |

| SD               | 26  | baseband audio I <sup>2</sup> S data output                                                 |      |

| FDEF             | 27  | filter data error flag output                                                               | 0    |

| GND3             | 28  | ground 3                                                                                    | _    |

| SCK              | 29  | baseband audio data I <sup>2</sup> S clock output                                           | 0    |

| WS               | 30  | baseband audio data I <sup>2</sup> S word select output                                     | 0    |

| FDAO             | 31  | filter data output                                                                          | 0    |

| FDAI             | 32  | filter data input                                                                           |      |

| FDFSY            | 33  | filter data output frame sync                                                               |      |

| V <sub>DD2</sub> | 34  | supply voltage 2                                                                            |      |

| TC1              | 35  | do not connect; factory test control 1 input, with integrated pull-down resistor            |      |

| TC0              | 36  | do not connect; factory test control 0 input, with integrated pull-down resistor            |      |

| TDO              | 37  | boundary scan test data output                                                              |      |

| TRST             | 38  | boundary scan test reset input; this pin should be connected to ground for normal operation |      |

| ТСК              | 39  | boundary scan test clock input                                                              | I    |

|                  |     |                                                                                             |      |

| SYMBOL   | PIN | IN DESCRIPTION                                          |  |

|----------|-----|---------------------------------------------------------|--|

| TMS      | 40  | boundary scan test mode select input                    |  |

| TDI      | 41  | boundary scan test data input I                         |  |

| FSCLK384 | 42  | sample rate clock frequency indication input I          |  |

| FSCLKM   | 43  | sample rate clock source selection for the master input |  |

| MCLK24   | 44  | master clock frequency indication input I               |  |

#### 7 FUNCTIONAL DESCRIPTION

#### 7.1 Coding system

The perceptual audio encoding/decoding scheme defined within the "*ISO/IEC 11172-3 MPEG Standard*" allows for a high reduction in the amount of data needed for digital audio whilst maintaining a high perceived sound quality. The coding is based upon a psycho-acoustic model of the human auditory system. The coding scheme exploits the fact that the human ear does not perceive weak spectral components that are in the proximity (both in time and frequency) of loud components. This phenomenon is called masking.

For layers I and II of ISO/MPEG the broadband audio signal spectrum is split into 32 sub-bands of equal bandwidth. For each sub-band signal a masking threshold is calculated. The sub-band samples are then re-quantized to such an accuracy that the spectral distribution of the re-quantization noise does not exceed the masking threshold. It is this reduction of representation accuracy which yields the data reduction. The re-quantized sub-band signals are multiplexed, together with ancillary information regarding the actual re-quantization, into a MPEG audio bitstream.

### SAA2501

### SAA2501

During decoding, the SAA2501 de-multiplexes the MPEG audio bitstream, and with knowledge of the ancillary information, reconstructs and combines the sub-band signals into a broadband audio output signal.

#### 7.2 Basic functionality

From a functional point of view, several blocks can be distinguished in the SAA2501. A clock generator section derives the internally and externally required clock signals from its clock inputs. The SAA2501 can switch between a master and a slave input interface to receive the coded input data. The input processor parses and de-multiplexes the input data stream. The de-quantization and scaling processor performs the transformation and scaling operations on the sample representations in the input bitstream to yield sub-band domain samples.

The sub-band samples are transferred via an external detour to the synthesis sub-band filter bank processor. The detour can be used to process the decoded audio in the sub-band domain. The baseband audio samples, reconstructed by the sub-band filter bank, can be processed before being output.

The decoding control block houses the L3 control interface, and handles the response to external control signals. The L3 control interface enables the application to

configure the SAA2501, to read its decoding status, to read Program Associated Data, and so on.

Several pins are reserved for Boundary Scan Test and Scan Test purposes.

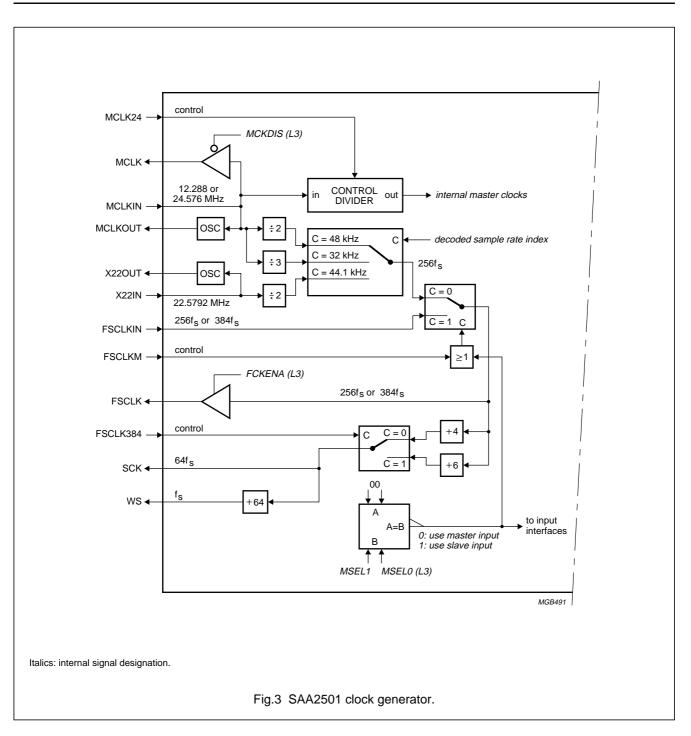

#### 7.3 SAA2501 clocks

The SAA2501 clock interfacing is designed for application versatility. It consists of 10 signals (see Table 1).

From a functional point of view, the clock generator inside the device can be represented as shown in Fig.3.

As described above, the SAA2501 incorporates a master input interface on which it requests for coded input data itself, as well as a slave input interface for an imposed coded data input bitstream. The input interface is selected with flags MSEL0 and MSEL1, controlled via the L3 microcontroller interface.

Depending on the selected input interface, only a limited number of the three possible input clocks (MCLKIN, X22IN and FSCLKIN) is actually required. The various clock options are selected with the 3 external control signals MCLK24, FSCLKM and FSCLK384. These control signals must be stationary while the device reset signal at pin RESET is de-activated; changing any of these 3 signals without simultaneously resetting the SAA2501 can result in malfunctioning.

| SIGNAL   | DIRECTION | FUNCTION                                                                   |  |

|----------|-----------|----------------------------------------------------------------------------|--|

| MCLKIN   | input     | master clock oscillator input or signal input                              |  |

| MCLKOUT  | output    | master clock oscillator output                                             |  |

| MCLK     | output    | master clock output; buffered signal                                       |  |

| MCLK24   | input     | master clock frequency indication input:                                   |  |

|          |           | MCLK24 = 0; MCLKIN frequency is 12.288 MHz ( $256 \times 48$ kHz)          |  |

|          |           | MCLK24 = 1; MCLKIN frequency is 24.576 MHz ( $512 \times 48$ kHz)          |  |

| X22IN    | input     | 22.5792 MHz (512 $\times$ 44.1 kHz) clock oscillator input or signal input |  |

| X22OUT   | output    | 22.5792 MHz (512 × 44.1 kHz) clock oscillator output                       |  |

| FSCLKIN  | input     | sample rate clock signal input                                             |  |

| FSCLK    | output    | sample rate clock signal input; buffered signal                            |  |

| FSCLK384 | input     | sample rate clock signal frequency indication input:                       |  |

|          |           | FSCLK384 = 0; FSCLKIN frequency is 256f <sub>s</sub>                       |  |

|          |           | FSCLK384 = 1; FSCLKIN frequency is 384f <sub>s</sub>                       |  |

| FSCLKM   | input     | sample rate clock source selection when using the master input:            |  |

|          |           | FSCLKM = 0; use MCLKIN or X22IN as source                                  |  |

|          |           | FSCLKM = 1; use FSCLKIN as source                                          |  |

Table 1

Clock interfacing signals

### SAA2501

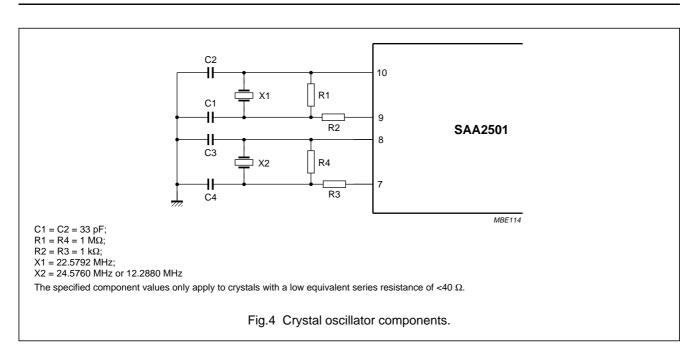

#### 7.4 Crystal oscillator

The recommended crystal oscillator configuration is shown in Fig.4. The specified component values only apply to crystals with a low equivalent series resistance of <40  $\Omega$ .

SAA2501

### Digital Audio Broadcast (DAB) decoder

#### 7.5 Clock frequencies when using the slave input

If the slave input is used (MSEL1 and MSEL0 = 10 or 11), the SAA2501 clock sources are MCLKIN and FSCLKIN and X22IN is not used. The I<sup>2</sup>S clocks SCK and WS are generated by the SAA2501 from FSCLKIN. FSCLKIN may be designated to have a frequency of 256 times (indicated by FSCLK384 = 0) or 384 times (indicated by FSCLK384 = 1) the sample frequency of the coded input data. Master clock signal MCLKIN may be chosen to have a frequency of 12.288 MHz (indicated by MCLK24 = 0) or 24.576 MHz (indicated by MCLK24 = 1). MCLKIN and FSCLKIN do not have to be phase or frequency locked. If the application is based on a sample frequency of 48 kHz or 32 kHz, and a sample rate related clock of 12.288 MHz  $(256 \times 48 \text{ kHz}; 384 \times 32 \text{ kHz})$  is available, this can be taken advantage of by using this signal for both MCLKIN and FSCLKIN.

#### 7.6 Clock frequencies when using the master input

If the master input is used (MSEL1 and MSEL0 = 00), one out of two configurations is selected with signal FSCLKM with respect to the clock sources:

If FSCLKM = 0, MCLKIN and X22IN are the clock sources. FSCLKIN is not used in this configuration. FSCLK384 must be set to logic 0 for reasons of internal connections in the clock generator circuitry. MCLKIN may have only frequency 24.576 MHz (so mandatory accompanied by MCLK24 = 1), and X22IN must have a frequency of 22.5792 MHz. MCLKIN and X22IN do not have to be phase or frequency locked. The main advantage of this configuration is that the SAA2501 determines automatically which sample rate is active from the sampling rate setting of the input data bitstream, and then selects either MCLKIN or X22IN as the clock source for the I<sup>2</sup>S clocks SCK and WS. This configuration is therefore particularly suited in applications with more than one possible sample rate setting.

If FSCLKM = 1, the configuration is comparable to the configuration when using the slave input (see Section 7.5). MCLKIN and FSCLKIN are used as the clock sources, and X22IN is not required. MCLKIN may again have a frequency of 12.288 MHz (indicated by MCLK24 = 0) or 24.576 MHz (indicated by MCLK24 = 1), and FSCLKIN may have a frequency of 256 times (indicated by FSCLK384 = 0) or 384 times (indicated by FSCLK384 = 1) the sample frequency of the input data. MCLKIN and FSCLKIN do not have to be phase or frequency locked.

# 7.7 Target applications; applying the SAA2501 with 2 ISO/MPEG sources

In Table 2 the three target applications of the SAA2501 are summarised. The slave input application is labelled S, and the master input applications are labelled M0 and M1.

### SAA2501

#### **Table 2**Target applications

| ATTRIBUTE CONDITIONS |                 | APPLICATION             |                          |                   |

|----------------------|-----------------|-------------------------|--------------------------|-------------------|

|                      |                 | SLAVE INPUT             | MASTER INPUT             |                   |

| INPUT INTERFACE      | CONDITIONS      | <b>S</b> <sup>(1)</sup> | <b>MO</b> <sup>(2)</sup> | M1                |

| FSCLKM               |                 | X                       | 0                        | 1                 |

| MCLKIN               | MCLK24 = 1      | 24.576 MHz              | 24.576 MHz               | 24.576 MHz        |

|                      | MCLK24 = 0      | 12.288 MHz              | illegal                  | 12.288 MHz        |

| X22IN                |                 | note 3                  | 22.579 MHz               | note 3            |

| FSCLKIN              | FSCLK384 = 1    | 384f <sub>s</sub>       | illegal                  | 384f <sub>s</sub> |

|                      | FSCLK384 = 0    | 256f <sub>s</sub>       | note 3                   | 256f <sub>s</sub> |

| FSCLK                | FCKENA = 1 (L3) | copy of FSCLKIN         | 256f <sub>s</sub>        | copy of FSCLKIN   |

#### Notes

- 1. FSCLKIN must be locked to input data clock CDSCL; see Section 7.17.2.

- 2. FSCLKIN is not used, but FSCLK384 must be LOW.

- 3. Must be electrically defined; e.g. LOW.

Sections 7.5 and 7.6 explain which clock sources are activated by the SAA2501 depending on the selected input interface. This automatic clock source selection makes it easy to apply the SAA2501 in systems with two ISO/MPEG coded data sources (one connected to the master input, an one to the slave input), even if these data sources use different clocks.

#### 7.8 Buffered clock outputs

The SAA2501 provides a signal MCLK which is a buffered version of MCLKIN. MCLK can be set to 3-state by setting the L3 control interface flag MCKDIS to 1 in applications where MCLK is not needed.

Signal FSCLK is copied from the FSCLKIN input for application types S and M1 or generated with a frequency of 256f<sub>s</sub> by the SAA2501 for application type M0. After a device reset, FSCLK must be enabled explicitly by setting L3 flag FCKENA, or can alternatively be left 3-stated in applications where it is not needed.

After a device reset, MCLK is enabled; FSCLK is disabled (i.e. both MCKDIS and FCKENA are set to logic 0).

#### 7.9 Functionality issues

The SAA2501 fully complies with ISO/MPEG layer I and II and EU147 with the slave input. With the master input, the SAA2501 complies with ISO/MPEG layer I and II, excluding the free format bit rate. Several aspects of the

decoding process, as well as the audio post-processing features, offered by the SAA2501, are described in more detail in Section 7.10.

#### 7.10 Synchronization to input data bitstreams

After a reset, the SAA2501 mutes both sub-band and baseband audio data. After data inputting has started, the SAA2501 searches either for a sync pattern or a sync pulse. The speed at which input data is read by the master input to search for synchronization is described below. If the application is such that the SAA2501 starts at a random moment in time compared to the bitstream, maximal one frame is skipped before a synchronization pattern or pulse is encountered.

When the SAA2501 has detected the first synchronization word or pulse, a number of frames are decoded in order to verify synchronization; the input data for these frames is read and decoded, but meanwhile the audio output is muted. The number of muted frames depends on the input data format (ISO/MPEG or EU147), whether the ISO/MPEG Cyclic Redundancy Check (CRC) is active, and whether the bit rate is free format. If the synchronization is found to be false, the SAA2501 resumes the initial synchronization as described above. If the detected pulse/pattern is concluded to be a real synchronization pulse/pattern, Table 3 indicates the number of muted frames.

### SAA2501

#### Table 3Muted frames

| CRC    |                         | OF MUTED FRAMES             |

|--------|-------------------------|-----------------------------|

| CRC    | FREE FORMAT BIT<br>RATE | NON-FREE-FORMAT<br>BIT RATE |

| No CRC | 2                       | 1                           |

| CRC    | 1                       | 0                           |

#### 7.11 Master input bit rate selection

As explained in Section 7.10, the SAA2501 can be used to alternate between two applications: one with the slave input, and one with the master input. When using the master input, the SAA2501 should fetch data with the effective bit rate, but cannot know what the bit rate of the input data is until it has established synchronization. To overcome this paradox, the input requesting is done at the last selected bit rate.

After a device reset, the master input bit rate selection defaults to the value indicated in Table 4.

#### Table 4 Defaults master input bit rate

| FSCLKM | FSCLK384 | FSCLKIN                     | DEFAULT MASTER INPUT<br>BIT RATE (kbits/s) |

|--------|----------|-----------------------------|--------------------------------------------|

| 0      | 0        | X <sup>(1)</sup>            | 384                                        |

| 1      | 0        | 256 × 32 kHz                | 278.64                                     |

|        | 1        | $384 \times 32 \text{ kHz}$ |                                            |

|        | 0        | 256 × 44.1 kHz              | 384                                        |

|        | 1        | 384 × 44.1 kHz              |                                            |

|        | 0        | 256 × 48 kHz                | 417.96                                     |

|        | 1        | $384 \times 48 \text{ kHz}$ |                                            |

#### Note

#### 1. X = don't care.

When FSCLKM = 0, the default master input bit rate is 384 kbits/s. When FSCLKM = 1, the SAA2501 uses signal FSCLKIN to derive the selected bit rate, but it has no indication concerning the sample rate corresponding to FSCLKIN. Therefore, a bit rate of 384 kbits/s is selected at an assumed sample rate of 44.1 kHz; with other sample rates, the bit rate changes proportionally.

The consequence is that while the SAA2501 synchronises (e.g. after a device reset), the application must at least be able to supply at the given default bit rate the required number of frames plus one additional frame (because of the random decoding start point in the input bitstream). Buffers in the application must thus be chosen sufficiently large to prevent under or overflows.

The speed with which input data is requested by the master input is changed by the SAA2501 in each of the following cases:

When input synchronization is established after checking a number of frames and the bit rate index of the newly decoded bitstream indicates a different bit rate than that currently selected. In this event, the bit rate is adapted to the newly decoded index.

- 2. When the active input interface is changed from the master to the slave input, or the signal STOP is activated; in these events input requesting stops.

- 3. When the active input interface is changed from the slave to the master input, or the signal STOP is deactivated; the bit rate is set to the last selected master input bit rate (the last selected master input bit rate is memorised while using the slave input).

In all other events (e.g. when the SAA2501 goes and stays out of synchronization), the data requesting speed of the master input is maintained.

#### 7.12 Sample rate selection

When using the slave input, or when using the master input with FSCLKM = 1, the application must know the sample rate: FSCLKIN must be applied, which has a frequency which is a multiple of the sample rate; the (sample rate dependent) I<sup>2</sup>S timing signals SCK and WS are generated from FSCLKIN. These configurations will normally be used in applications with a fixed sample rate. Should the sample rate change, then the SAA2501 must be reset.

### SAA2501

When using the master input with FSCLKM = 0, the SAA2501 selects the active sample rate autonomously, and generates the signals SCK and WS from its crystal clocks. After a device reset, the SAA2501 selects a sample rate of 44.1 kHz by default.

SCK and WS may, and will only, show phase or frequency changes in any of the following 3 situations:

- 1. When the SAA2501 establishes synchronization with the coded data input bitstream.

- When the active input interface is changed from the master input with FSCLKM = 0 to the slave input (i.e. the timing source for the generation of SCK and WS is switched from the crystal clocks to FSCLKIN).

- 3. When the active input interface is changed from the slave input to the master input with FSCLKM = 0 (i.e. the timing source for the generation of SCK and WS is switched from FSCLKIN to the crystal clocks); the sample rate is set to the last selected sample rate that was used with the master input (the last selected sample rate is memorized while using the slave input).

In all other cases, SCK and WS keep on running without phase or frequency changes, and the sample rate selection remains unchanged.

#### 7.13 Handling of errors in the coded input data

The SAA2501 can handle errors in the input data. Errors are assumed to be present in 3 events:

- 1. If errors are indicated with the coded input data error flag CDSEF and/or CDMEF.

- 2. On CRC failure if ISO/MPEG error protection is active.

- 3. If input bitstream syntax errors are detected.

Errors in the input data have an effect on the decoding process if the corrupted data is inside the header, bit

allocation or scale factor select information field in a frame (then the SAA2501 will mute) or inside the scale factor field (then the previous scale factor will be copied). Errors in other data fields are not handled explicitly. If the ISO/MPEG CRC is active, only the CRC result is interpreted: CDSEF/CDMEF un-reliability indications for bit allocation and scale factor select information are neglected.

In applications where the ISO/MPEG CRC is always present, the protection bit (which itself is not protected) in the ISO/MPEG header may be overruled by making L3 settings flag CRCACT HIGH. In this manner, the SAA2501 is made robust for data errors on the protection bit.

#### 7.14 Sub-band filter signals

The decoded sub-band signals are output, together with an error indication so that concealment can be applied externally. The optionally concealed sub-band signals are put back into the SAA2501 for synthesis filtering.

#### 7.15 Baseband audio processing

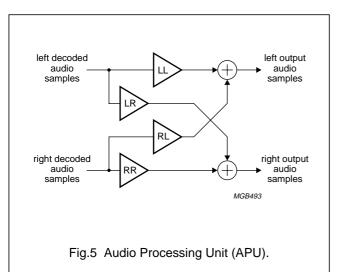

The baseband audio de-emphasis as indicated in the ISO/MPEG input data is performed digitally inside the SAA2501. The incorporated 'Audio Processing Unit' (APU) (see Fig.5) can be used to apply inter-channel crosstalk or independent volume control per channel. The APU attenuation coefficients LL, LR, RL and RR may be changed dynamically by the host microcontroller, writing their 8-bit indices to the SAA2501 over the L3 control bus. The coefficient changes become effective within one sample period after the coefficient index writing.

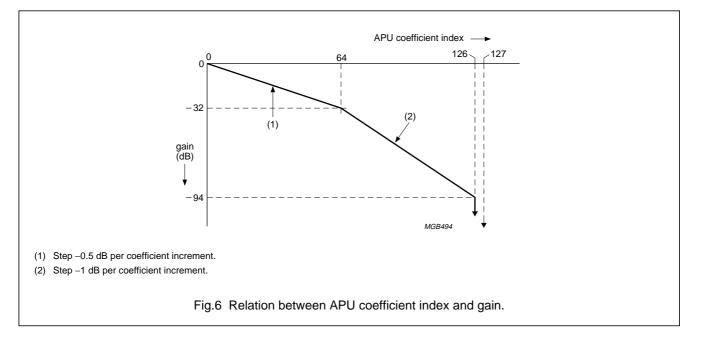

To avoid clicks at coefficient changes, the transition from the current attenuation to the next is smoothed. The relation between the APU coefficient index and the actual coefficient (i.e. the gain) is given in Table 5.

### SAA2501

| APU COEFFICIENT      | APU<br>COEFFICIENT |                       |

|----------------------|--------------------|-----------------------|

| BINARY               |                    |                       |

| 00000000 to 00111111 | 0 to 63            | $2^{-\frac{C}{12}}$   |

| 01000000 to 01111110 | 64 to 126          | $2^{-\frac{C-32}{6}}$ |

| 01111111             | 127                | 0                     |

| 1XXXXXXX             | 128 to 255         | reserved              |

Table 5

APU coefficient index and actual coefficient

From Table 5 we learned that up to coefficient index 64 the step size is approximately -0.5 dB per coefficient increment, and from coefficient index 64 to index 126 the step size is approximately -1 dB per increment.

Note that the APU has no built-in overflow protection, so the application must take care that the output signals of the APU cannot exceed 0 dB level. For an update of the APU coefficients, it may be required to increase some of the coefficients and decrease some others. The APU coefficients are always written sequentially in the fixed sequence LL, LR, RL and RR. Therefore, to prevent internal APU data overflow due to non-simultaneous coefficient updating, the following steps can be followed:

- Write LL, LR, RL, RR once, but change only those coefficients that must decrease; overwrite the coefficients that must increase with their old value (so do not change these yet).

- 2. Write LL, LR, RL, RR again, but now change those coefficients that must increase, keeping the other coefficients unchanged.

The consequence of this two-pass coefficient updating is that the application must keep a shadow of the current APU coefficients (the L3 APU coefficients data item is write-only).

#### 7.16 Decoding control signals

The decoding is performed by 3 signals as shown in Table 6.

| SIGNAL | DIRECTION | FUNCTION <sup>(1)</sup>                      |

|--------|-----------|----------------------------------------------|

| RESET  |           | reset SAA2501 to default state               |

| STOP   | input     | stop decoding                                |

| URDA   | input     | unreliable input data;<br>interrupt decoding |

The master reset signal RESET forces the SAA2501 into its default state when HIGH. RESET must stay HIGH during at least 24 MCLKIN periods if MCLKIN has frequency of 24 MHz (i.e. MCLK24 = 1) or 12 MCLKIN periods if MCLKIN has a frequency of 12 MHz (MCLK24 = 0). At a reset, the SAA2501 synchronization to the input bitstream is lost, the sub-band filter and baseband audio output signals are muted, and the SAA2501 settings are initialized.

The decoding can be stopped by making input signal STOP HIGH. Stopping the decoding forces the SAA2501 to end decoding of input data, yet feeding zeroed sub-band samples to the synthesis sub-band filter bank to create a soft muting. When using the master input, input requesting is also stopped. CDMWS stays in its current state while STOP is asserted. The SAA2501 assumes the input synchronization to be lost when the decoding is stopped, thus causing re-synchronization when STOP is de-activated again. Then the SAA2501 mutes, meanwhile searching for a frame sync pattern or frame sync pulse (the synchronization mode is selected via the L3 control bus) at the input.

If synchronization is found, the SAA2501 starts producing output data. The maximum response time to the activation of signal STOP is half a sample period; the re-synchronization time after STOP going LOW again differs in various situations.

An 'unreliable data' indication can be given to the SAA2501 by making signal URDA HIGH. URDA, like STOP, mutes the sub-band signals and forces the SAA2501 out of synchronization. However, in contrast to STOP, master input data requesting continues at the bit rate that was decoded before URDA became active. The maximum response time to URDA is half a sample period.

#### 7.17 Coded data interfaces

The SAA2501 contains:

- A coded data master input interface

- A coded data slave input interface (designed for EU147 format).

#### 7.17.1 THE CODED DATA MASTER INPUT INTERFACE

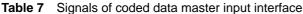

When using the master input, the SAA2501 requests for input data. With the master input, the coded input data may not use the ISO/MPEG free format bit rate or be in EU147 format. The coded data master input interface consists of 4 signals (see Fig.7).

# SAA2501

Preliminary specification

14

SAA2501

### Digital Audio Broadcast (DAB) decoder

| SIGNAL | DIRECTION | FUNCTION                                     |  |

|--------|-----------|----------------------------------------------|--|

| CDM    | input     | Dut ISO/MPEG coded input data (master input) |  |

| CDMEF  | input     | t coded data (master input) error flag       |  |

| CDMCL  | output    | coded data (master input) bit clock          |  |

| CDMWS  | output    | coded data (master input) word select        |  |

Data clock CDMCL is being output, having a fixed frequency of 768 kHz. Signal CDM carries the coded data in bursts of 16 valid bits. Coded data input frames may only start either at the first or at the ninth bit of a 16 bit valid data burst (i.e. only at a byte boundary). The value of word select signal CDMWS is changed every time new input data is needed: one CDMCL period after each transition in CDMWS, 16 bits of valid data are read serially. Assume N is the number of CDMCL periods between two transitions of CDMWS, and R is the number of CDMCL periods to obtain the effective bit rate E (in kbits/s) at a transferring data rate of 768 kbits/s, i.e. R =  $\frac{16 \times 768}{E}$ . The SAA2501

keeps N close to R, but N can vary plus or minus two:  $N \in {round(R)-2,...,round(R)+2}.$

Error flag CDMEF is used to indicate input data insecurities (e.g. due to erratic channel behaviour). In Fig.7, an example with one unreliable bit is shown. The value of CDMEF may vary for each valid data bit, but is combined by the SAA2501 for every group of 8 input bits.

#### 7.17.2 THE CODED DATA SLAVE INPUT INTERFACE

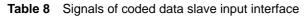

The coded data slave input interface signals are shown in Fig.8. The coded data master input interface consists of 5 signals (see Table 8).

SAA2501

| SIGNAL                                          | DIRECTION | FUNCTION                                         |

|-------------------------------------------------|-----------|--------------------------------------------------|

| CDS input ISO/MPEG or EU147 coded input data    |           | ISO/MPEG or EU147 coded input data (slave input) |

| CDSEF input coded data (slave input) error flag |           |                                                  |

| CDSCL input coded data (slave input) bit clock  |           |                                                  |

| CDSWA                                           | input     | coded data (slave input) burst window signal     |

| CDSSY                                           | input     | coded data (slave input) frame sync              |

CDS is the SAA2501 input data bitstream. Data clock CDSCL must have a frequency equal to or higher than the bit rate. The maximum CDSCL frequency is 768 kHz. Error flag CDSEF is handled in the same way as CDMEF is handled for the master input (in Fig.8, one unreliable data bit is shown as an example). The value of CDSEF is neglected for those bits where CDSWA is LOW. Window signal CDSWA being HIGH indicates valid data; in this way, burst input data is allowed. The constraints for the ability to use 'burst signals' are explained later in this Section 7.17.2. Frame sync signal CDSSY indicates the start of each input data frame. CDSSY is synchronous with CDSCL. CDSSY may be present or not: as described later in this Section 7.17.2. The first valid CDS bit after a leading edge of CDSSY is interpreted to be the first frame bit.

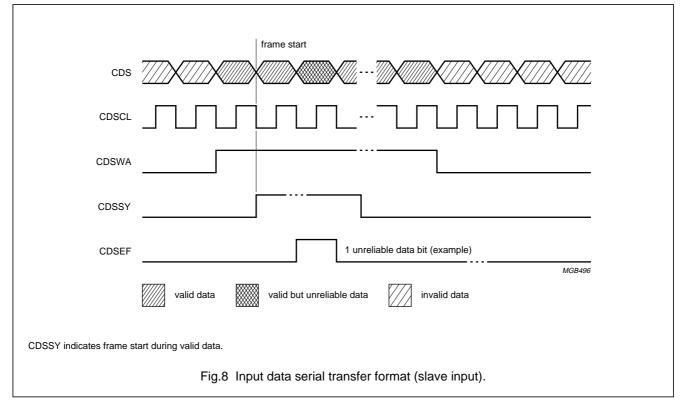

The minimum time for CDSSY to stay HIGH is one CDSCL period; the maximum HIGH period is constrained by the requirement that CDSSY must be LOW at least during one CDSCL period per frame (a leading edge, i.e. a frame start indication, must be present every frame). Leading edges of CDSSY can occur while CDSWA is HIGH, as in Fig.8. Alternatively, a situation as shown in Fig.9 is also allowed, where CDSSY has a leading edge while CDSWA is LOW, i.e. during invalid data. The first CDS bit after CDSWA going HIGH is now interpreted to be the first frame bit.

### SAA2501

Whether frame sync signal CDSSY is present or not must be selected with L3 settings flags MSEL1 and MSEL0 (see Section 7.20.7). With respect to the presence of CDSSY, two situations can be distinguished:

- 1. For EU147 coded input data CDSSY is mandatory.

- For ISO/MPEG input data if CDSSY is supplied, CDSWA may change each CDSCL period.

- 3. If CDSSY is not supplied, CDSCL must have a frequency higher than the bit rate (i.e. CDSWA cannot be continuously HIGH), and CDSWA HIGH periods may have only lengths of a multiple of 8 CDSCL periods: data is input in byte bursts. Furthermore, these bursts must be byte aligned with the frame bounds: frames are only allowed to start at the 1<sup>st</sup>, 9<sup>th</sup>, 17<sup>th</sup> etc. bit in a valid data burst. For applications where data is input in bursts of exactly one frame, and where CDSCL has a higher frequency than the bit rate, CDSWA and CDSSY may be interconnected.

#### 7.17.3 SLAVE INPUT TRANSFER SPEED OF FIRST FRAME

Both the average and the instantaneous speed at which data is transferred to the slave input interface are limited.

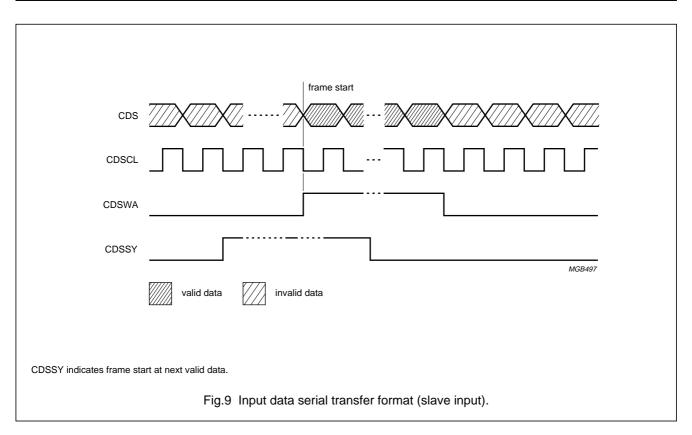

The data transferring of the first ISO/MPEG or EU147 frame after starting to decode is shown in Fig.10.

It shows the transferring of n-frame bits in one frame between time 0 and t, where t corresponds to 384 sample periods (ISO/MPEG layer I input data) or 1152 sample periods (ISO/MPEG layer II input data). Buffer margin B equals 16 bytes (128 bits). In Fig.10 an effective transferring characteristic is drawn, representing any of the possible ISO/MPEG bit rates. However, input data may be transferred at a higher-than-effective speed (in other words: CDSCL may have a higher frequency than the effective bit rate) in periods during which CDSWA is HIGH, interleaved with invalid data periods where CDSWA is LOW. In the example of Fig.9 this is used to transfer the data of the frame in two bursts, as shown by the actual transferring characteristic. The actual transferring characteristic has a slope equal to the CDSCL frequency while CDSWA is HIGH, and is horizontal during the periods in which CDSWA is LOW (no bits are being transferred).

SAA2501

The shaded area in Fig.10 represents the restrictions to the actual transferring characteristic of all frames. The actual transferring characteristic may not undercut the effective transferring characteristic by more than B bits to avoid an input underflow. On the other hand, the actual transferring characteristic may not cross the shown upper limit of the shaded area to prevent an input buffer overflow. The slope of this upper limit is determined by the maximum effective input bit rate (depending on the input data format). Table 9 summarizes the slopes as determined by the bit rates supported by ISO/MPEG and EU147.

#### Table 9 Slopes determined by bit rates supported by ISO/MPEG and EU147

| ISO/MPEG<br>AND EU147<br>LAYER | EFFECTIVE<br>INPUT BIT<br>RATE<br>(kbits/s) | TRANSFERRING<br>UPPER LIMIT<br>SLOPE<br>(kbits/s) |  |

|--------------------------------|---------------------------------------------|---------------------------------------------------|--|

| ISO/MPEG<br>layer l            | $\pm 13.3^{(1)}$ to $\pm 448$               | 448                                               |  |

| ISO/MPEG<br>layer II           | 3.5 <sup>(1)</sup> to 384                   | 384                                               |  |

#### Note

1. Achieved using the free format option and the minimum amount of the side information that must be

transmitted (this means using single channel mode, no CRC and 32 kHz sample rate).

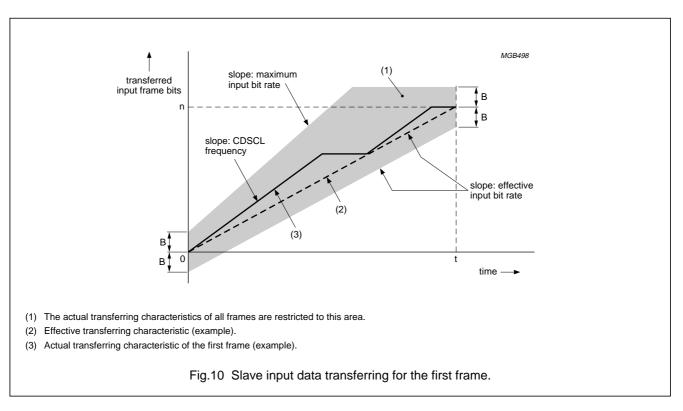

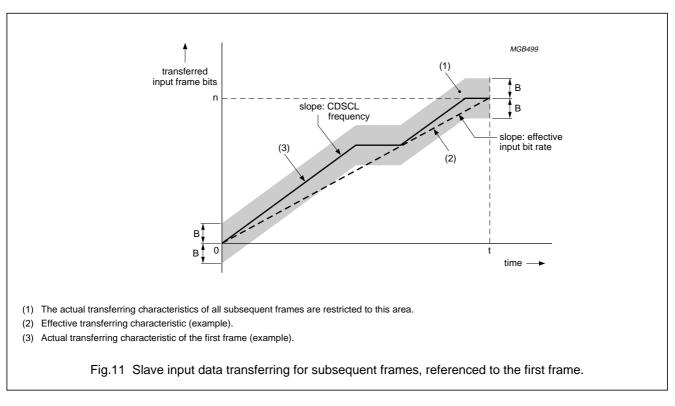

# 7.17.4 SLAVE INPUT TRANSFER SPEED OF SUBSEQUENT FRAMES

The SAA2501 starts decoding as soon as enough data of the first ISO/MPEG or EU147 input data frame has been received. Thus the start moment of decoding depends on the actual transferring characteristic of the first frame. Decoding start times of subsequent input data frames are also governed by this initial start time.

For this reason the transferring characteristic of all subsequent frames must approximate the characteristic of the first frame within the buffer margin  $\pm B$ . For the example shown in Fig.10, subsequent frames must be transferred within the shaded area shown in Fig.11.

# SAA2501

Note that the actual transferring characteristics of all frames must also remain inside the shaded area of Fig.11.

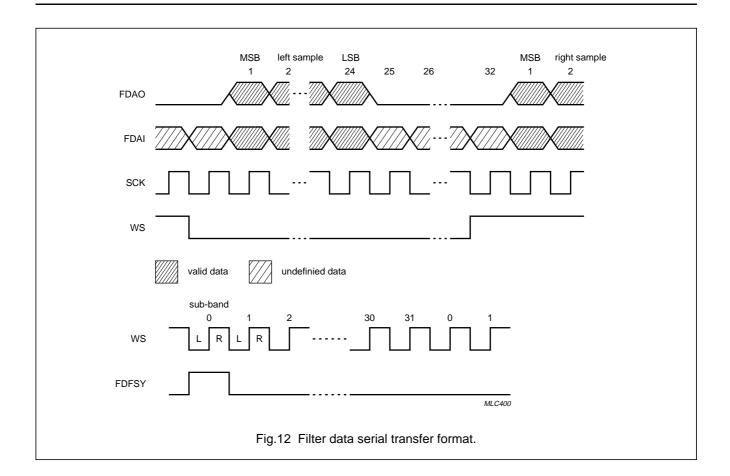

#### 7.18 The sub-band filter interface

As mentioned earlier, decoded signals in the sub-band domain (before synthesis filtering) are available externally for processing. The associated interface has an I<sup>2</sup>S-like format (see Fig.12).

The filter data interface uses 6 signals as shown in Table 10.

SAA2501

| <b>U</b> |           |                    |

|----------|-----------|--------------------|

| SIGNAL   | DIRECTION |                    |

| FDAO     | output    | filter data output |

Table 10 Signals of filter data interface

| SIGNAL DIRECTION FUNCTION                                                             |                                                | FUNCTION                                                                   |  |  |

|---------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------|--|--|

| FDAO output                                                                           |                                                | filter data output                                                         |  |  |

| FDEF         output         filter data error flag                                    |                                                | filter data error flag                                                     |  |  |

| FDAI                                                                                  | input filter data input (optionally processed) |                                                                            |  |  |

| SCK output filter data (output/input common) bit clock; I <sup>2</sup> S clock output |                                                | filter data (output/input common) bit clock; I <sup>2</sup> S clock output |  |  |

| WS                                                                                    | output                                         | filter data (output/input common) word select; I <sup>2</sup> S            |  |  |

| FDFSY                                                                                 | output                                         | filter data output frame synchronization                                   |  |  |

Two sub-band samples (one per channel) are transmitted per sample period with output FDAO. The transmission pattern of the samples S [sb, ch] (sb: sub-band index; ch: channel) is: S [0, L], S [0, R], S [1, L], S [1, R],..., S [31, R], S [0, L], S [0, R], etc. Word select signal WS indicates the channel of each sample (WS is also used for the baseband audio output interfacing).

The sub-band sample bit clock SCK has a frequency of 64 times the sample frequency. The sub-band samples are transmitted in 24 bit two's complement Pulse Code Modulation (PCM) form, MSB first. Thus, of the available 32 FDAO bits per sample per channel, only 24 are used.

The MSB of a sample follows one SCK period after each transition in WS. The 8 unused bits between individual samples in FDAO are zero (SCK is used for the baseband audio output interface as well). The optionally processed sub-band data signal is fed back as input FDAI in a similar format as FDAO, but now the 8 unused bits between individual samples are undefined; they are neglected by the SAA2501.

A leading edge in signal FDFSY indicates the start of each FDAO frame. The length of each FDFSY pulse is one sample period; FDFSY is HIGH during a S[0,L] and S[0,R]

### SAA2501

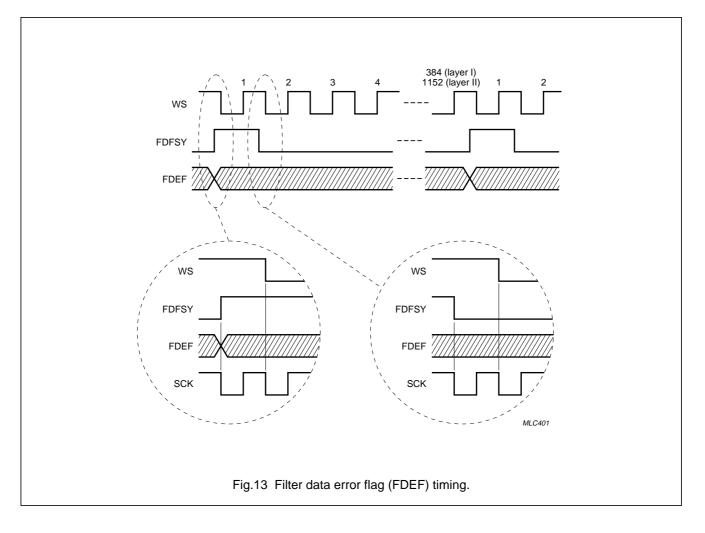

pair. Signal FDEF being HIGH indicates muting of FDAO due to input data errors (see Fig.13).

FDEF can only change value at each FDFSY leading edge, i.e. after each 384 sample periods (ISO/MPEG layer I input data) or 1152 sample periods (ISO/MPEG layer II input data): only whole frames are marked to be correct or muted. As shown in detail in Fig.13, transitions of FDFSY and FDEF take place one SCK period before a trailing edge of WS.

The optionally processed sub-band data FDAI must be synchronous to SCK and WS. Furthermore, the sub-band index of the FDAI samples must be synchronized to FDFSY: a sub-band logic 0 sample pair must be input when FDFSY is HIGH (as shown in Fig.12). This means that the delay of the external processing is allowed to be any integer multiple of 32 sample periods. If no external processing is to be applied, FDAO must be input back directly to FDAI.

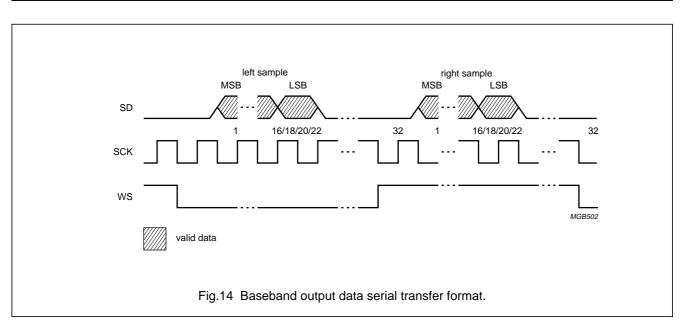

#### 7.19 The baseband output interface

The decoded baseband audio data is output in an  $I^2S$ -like format (see Fig.14).

The output interfacing consists of 3 signals (see Table 11).

### SAA2501

#### Table 11 Signals of output interfacing

| SIGNAL | DIRECTION | FUNCTION            |  |  |

|--------|-----------|---------------------|--|--|

| SD     | output    | baseband audio data |  |  |

| SCK    | output    | data clock          |  |  |

| WS     | output    | word select         |  |  |

The frequency of clock SCK is 64 times the sample frequency (SCK is also used for the sub-band filter interface).

The signal SD is the serial baseband audio data, sample by sample (left/right interleaved; the left sample and the right immediately following it form one stereo pair). 32 bits are transferred per sample per channel. The samples are transmitted in two's complement, MSB first. The output samples are rounded to either 16, 18, 20 or 22 bit precision, selectable by the host with L3 control interface flags RND1 and RND0. The remainder of the 32 transferred bits per sample per channel are zero.

The word select signal WS indicates the channel of the output samples (LOW if left, HIGH if right); WS is used for the sub-band filter interface as well. If indicated in the coded input data, de-emphasis filtering is performed digitally on the output data, thus avoiding the need of analog de-emphasis filter circuitry.

#### 7.20 The L3 control interface

The SAA2501 uses the L3 protocol with the associated bus as the control interface with an optional host microcontroller (see Chapter 8 for more information). In the programming sections a general transfer protocol outline is presented. In Section 8.2 several optional protocol enhancements are given, which on the one hand are less transparent from the applicant's point of view, but on the other hand increase the efficiency of the L3 interfacing.

#### 7.20.1 L3 SIGNALS

The L3 protocol uses 3 signals (see Table 12).

| Table 12 | Signals | of L3 | protocol |

|----------|---------|-------|----------|

|----------|---------|-------|----------|

| SIGNAL | DIRECTION    | FUNCTION                            |

|--------|--------------|-------------------------------------|

| L3DATA | input/output | L3 interface serial data            |

| L3CLK  | input        | L3 interface bit clock              |

| L3MODE | input        | L3 interface<br>address/data select |

The signals operate according to the L3 protocol description. After each device reset, the L3 interface of the SAA2501 must be initialised and as a consequence, the L3 interface cannot be used while the device reset signal is activated.

### SAA2501

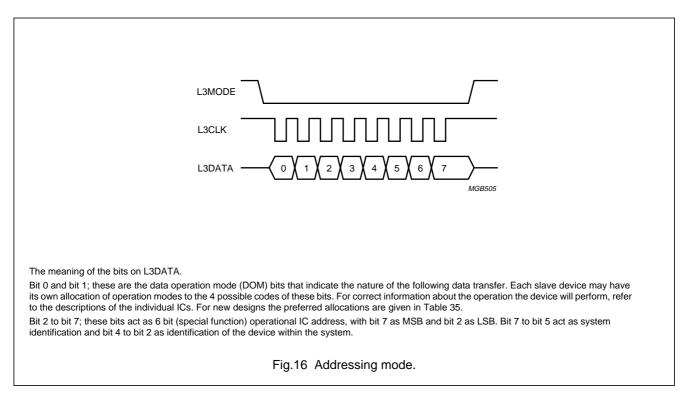

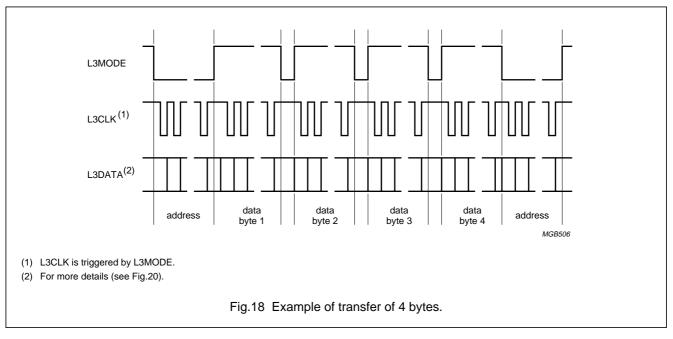

#### 7.20.2 L3 TRANSFER TYPES

The L3 protocol enables the reading and writing of control, status and data. In the L3 protocol, the host first issues an 8 bit wide 'operational address' on L3DATA while keeping L3MODE LOW. All devices connected to the L3 bus read the operational address. Next, data transfers from or to the host are done while keeping L3MODE HIGH. The devices

with an L3 operational address differing from the issued one must ignore these data transfers until the next operational address is issued. Only the device with an address equal to the issued operational address performs the transfer.

The SAA2501 has the L3 operational address as shown in Table 13.

Table 13 L3 operational address.

| 7 | 6 | 5 | 4 | 3 | 2 | 1                   | 0                   |

|---|---|---|---|---|---|---------------------|---------------------|

| 0 | 1 | 1 | 0 | 0 | 0 | DOM1 <sup>(1)</sup> | DOM0 <sup>(1)</sup> |

#### Note

1. The 'Data Operation Mode' bits DOM1 and DOM0 determine the mode in which the SAA2501 L3 interface will stay until the next time an L3 operational address is issued (see Table 14).

#### Table 14 DOM1 and DOM0 bits

| DOM1 | DOM0 | TRANSFER TYPE            |  |

|------|------|--------------------------|--|

| 0    | 0    | write item data          |  |

| 0    | 1    | read item data           |  |

| 1    | 0    | write control to SAA2501 |  |

| 1    | 1    | read SAA2501 status      |  |

Control bytes can be written to the SAA2501.

Data is transferred to or from the SAA2501 in so-called data items. The items can be a readable or writeable type. A data item transfer is initiated by writing the

corresponding control byte to the SAA2501 first. Next, the item data itself is transferred, always as an integer number of bytes.

The status of the SAA2501 can be read via L3. The SAA2501 status flag L3RDY must be monitored before transferring data item bytes to avoid transferring bytes faster than the L3 interface of the SAA2501 can handle.

# 7.20.3 L3 INTERFACE INITIALIZATION AT AN SAA2501 DEVICE RESET

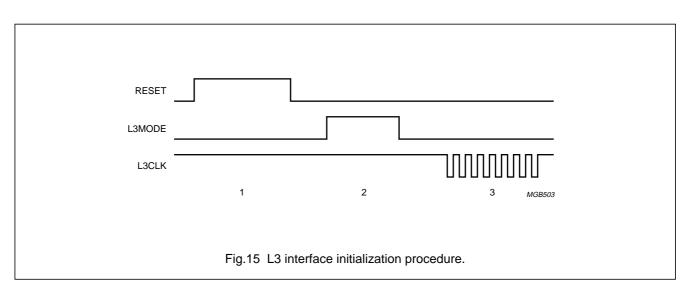

Figure 15 shows the mandatory actions that must be taken for correct L3 interface start-up at a device reset.

### SAA2501

The actions shown in Fig.15 are:

- 1. In order for the SAA2501 to keep L3DATA in 3-state, L3MODE must be kept LOW during the whole period that reset signal at pin RESET is asserted; meanwhile, no transfers can be performed (L3CLK stays HIGH).

- For a proper initialization of the L3 interface logic of the SAA2501, it is mandatory to make L3MODE HIGH and LOW again after the device reset has been de-activated. This must be done before any L3 transfer, even to or from other devices than the SAA2501, is performed. Figure 14 shows that L3CLK stays HIGH during this step.

- 3. Now the first transfer can be performed on the L3 bus. This transfer must be a operational address (indicated in Fig.14 by L3MODE = 0), addressing any of the devices connected to the L3 bus. The first transfer to the SAA2501 itself must always be either the writing of a control word or the reading of the SAA2501 status; the first transfer may never be a data item byte transfer.

**Remark:** any deviation from these steps may result in illegal L3 protocol behaviour of the SAA2501, even with the possibility of disturbing transfers to other devices connected to the L3 bus.

7.20.4 L3 INTERFACE CONTROL

The control of the SAA2501 L3 interface is performed with one-byte control words. Status polling is not necessary before writing control bytes. After writing the SAA2501 'write control' operational address, one or more control bytes may be written. Each written control byte overrules the previously sent control byte.

#### Table 15 L3 control

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CTRL7 | CTRL6 | CTRL5 | CTRL4 | CTRL3 | CTRL2 | CTRL1 | CTRL0 |

The definitions of the control bytes (CTRL7 to CTRL0) are given in Table 16.

#### Table 16 Explanation of control bytes

| CTRL7 TO CTRL0       | DEFINITION                       | TYPE <sup>(1)</sup> |

|----------------------|----------------------------------|---------------------|

| 0000000              | read/write SAA2501 settings item | I                   |

| 0000001              | read decoded frame header item   | I                   |

| 00000010             | read used frame header item      | I                   |

| 00000011             | read error report item           | I                   |

| 00000100             | reserved                         | I                   |

| 00000101             | read Ancillary Data item         | I                   |

| 00000110             | write APU coefficients item      | I                   |

| 00000111             | continue previous transfer       | С                   |

| 00001000 to 11111111 | reserved                         | -                   |

#### Note

1. Control bytes of type I initiate the transfer of a data item. The control byte of type C may be used after interrupting a transfer, in order to write APU coefficients, to return to the interrupted transfer.

SAA2501

#### 7.20.5 SAA2501 STATUS

The host can check the status of the SAA2501 by reading the one-byte status word. After writing the SAA2501 'read status' operational address, the status byte may be read an arbitrary number of times. If status is read more than once, it is updated by the SAA2501 between the individual readings. The status flags of the SAA2501 have the definition as shown in Table 17.

#### Table 17 Status flag definitions

| 7                   | 6                   | 5                   | 4         | 3         | 2         | 1                        | 0                    |

|---------------------|---------------------|---------------------|-----------|-----------|-----------|--------------------------|----------------------|

| DST2 <sup>(1)</sup> | DST1 <sup>(1)</sup> | DST0 <sup>(1)</sup> | undefined | undefined | undefined | INSYNC <sup>(2)(3)</sup> | L3RDY <sup>(4)</sup> |

#### Notes

- 1. By interpreting DST2 to DST0, the host can synchronize to the input frame frequency, and also determine at which moment which L3 data item is available to be read. The value of DST2 to DST0 is only valid if flag INSYNC is set.

- a) DST2 is a modulo 2 frame counter, i.e. DST2 inverts at the moment the decoding of a new frame is started. DST2 enables to host to sample the decoding subprocess DST1 to DST0 less frequently, meanwhile enabling the host to see if it missed a state.

- b) DST1 and DST0 values are explained in Table 18.

- 2. INSYNC is synchronization indication:

- a) INSYNC = 0; the SAA2501 is not synchronized to the input data.

- b) INSYNC = 1; the SAA2501 is synchronized to the input data.

- 3. As indicated in Section 7.20.8, some of the readable data item bits only have significance if INSYNC = 1.

- 4. L3RDY is L3 interface ready indication:

- a) L3RDY = 0; the L3 interface cannot perform a new item data transfer yet.

- b) L3RDY = 1; the L3 interface is ready for the next item data transfer.

After a device reset, L3RDY is cleared and will only become set after writing the first L3 control byte to the SAA2501. The value of L3RDY can be tested by polling signal L3DATA instead of transferring the whole status byte.

| DST1 | DST0 | FUNCTION                                                                 |

|------|------|--------------------------------------------------------------------------|

| 0    | 0    | subprocess 0; reading Ancillary Data or decoding header                  |

| 0    | 1    | subprocess 1; decoding bit allocation or scale factor select information |

| 1    | 0    | subprocess 2; decoding scale factors                                     |

| 1    | 1    | subprocess 3; decoding samples                                           |

#### Table 18 Status bytes DST1 and DST0

The DST1 and DST0 values in general do not have a determined duration. However, subprocess 3 takes at least  $\frac{1}{2}$  a frame period when ISO/MPEG layer I data is decoded, and  $\frac{5}{6}$  of a frame period when ISO/MPEG layer II data is decoded. Table 19 indicates the validity of the SAA2501 readable data items with respect to the decoding subprocess. Reading of a data item in a period when it is not valid renders undefined data.

### SAA2501

| S                    | AA2501 IS DEC  | ODING FRAM      | En                               | SAA2501 IS DECODING FRAME n + 1 |           |           |   |  |  |

|----------------------|----------------|-----------------|----------------------------------|---------------------------------|-----------|-----------|---|--|--|

| DST2 = 0; SUBPROCESS |                |                 |                                  | DST2 = 1; SUBPROCESS            |           |           |   |  |  |

| 0                    | 1              | 2               | 3                                | 0                               | 1         | 2         | 3 |  |  |

| not valid            | Ancillary Data | item (frame n   | – 1)                             | not valid                       | _         | -         | - |  |  |

| not valiu            | frame header   | items (frame n  | n) not vai                       |                                 | _         | -         | - |  |  |

| _                    |                | error report: E | error report: BALOK (frame n)    |                                 |           | -         | - |  |  |

| _                    | not valid      | not valid       | error report: DECFM<br>(frame n) |                                 | not valid | not valid | - |  |  |

**Table 19** Validity of SAA2501 readable data items with respect to the decoding subprocess (notes 1 and 2)

#### Notes

- 1. The Table shows following:

- a) The received Ancillary Data that was multiplexed in frame n–1 becomes valid after subprocess 0 of frame n, and may be read during subprocesses 1, 2 and 3 of frame n.

- b) The decoded and used frame headers for frame n become valid after subprocess 0 of frame n, and may be read during subprocesses 1, 2 and 3 of frame n.

- c) Flag BALOK for frame n in the error report item becomes valid after subprocess 1 of frame n, and may be read during subprocesses 2 and 3 of frame n and subprocess 0 of frame n+1.

- d) Flag DECFM for frame n in the error report item becomes valid after subprocess 2 of frame n, and may be read during subprocesses 3 of frame n and 0 of frame n+1.

- 2. Note that during subprocess 3 all data items can be read.

#### 7.20.6 DATA ITEMS

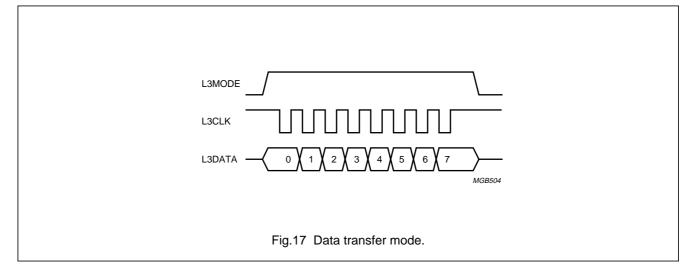

Data can be transferred to or from the SAA2501 in data items. This section describes the general protocol to accomplish item data transfer, followed by the individual SAA2501 data items. Optional enhancements on the general protocol are described in Chapter 8 Section 8.2.

#### 7.20.6.1 General data items

The data items of the SAA2501 are transferred (i.e. read or written, depending on whether the data item is of readable or writeable type) in bytes. A data item transfer is initiated by writing the corresponding type I control byte (see Section 7.20.4) to the SAA2501. The transfer of every subsequent item data byte must be preceded by reading the status until status flag L3RDY (see Section 7.20.5) is HIGH.

L3RDY may be tested alternatively by polling L3DATA, avoiding the need to transfer the whole status byte. Status polling is not required while transferring the APU coefficients item. Table 20 shows an example of how bytes 'DDDDDDDD' of a 2 byte data item, with the corresponding control byte 'CCCCCCCC', can be read. The writing of item data bytes occurs in a similar way.

#### TRANSFER L3DATA<sup>(1)</sup> L3MODE **EXPLANATION** SOURCE 01100010 host 0 indicates 'write control' transfer CCCCCCCC host 1 write transfer initiating (type I) control byte 01100011 host 0 indicates 'read status' transfer SSSSSSS SAA2501 1 read status (repeat step 4 until L3RDY = 1) 01100001 host 0 indicates 'read item data' transfer DDDDDDD SAA2501 1 read first item data byte 01100011 host 0 indicates 'read status' transfer SSSSSSS SAA2501 1 read status (repeat step 8 until L3RDY = 1) 01100001 0 indicates 'read item data' transfer host DDDDDDD SAA2501 1 read second item data byte

#### Table 20 Example of a 2 byte data item

#### Note

- 1. Explanation of bytes:

- a) CCCCCCCC = control byte.

- b) SSSSSSSS = status byte.

- c) DDDDDDDD = data byte.

Each data item has its own length in bytes. It is allowed to transfer less bytes than the data item length, skipping the last one or more bytes (it is even allowed to transfer no bytes at all). It is not allowed to transfer more bytes than the item length. This restriction does not hold for the APU coefficient item. After writing all APU coefficients (i.e. after writing all APU coefficient item bytes), they may be rewritten by continuing writing bytes to the APU coefficient item. Writing more than the specified number of bytes to a writeable data item or writing bytes to a read-only data item may cause the SAA2501 to malfunction. The reading of a write-only data item yields irrelevant data.

### SAA2501

### SAA2501

7.20.7 SAA2501 SETTINGS ITEM

The SAA2501 is configured with the SAA2501 settings. The initial value of the SAA2501 settings after reset is all zeros.

| Table 21 SAA2501 settings item; 1 byte (read/write) | Table 21 | SAA2501 | settings item; | 1 by | te (read/write) |

|-----------------------------------------------------|----------|---------|----------------|------|-----------------|

|-----------------------------------------------------|----------|---------|----------------|------|-----------------|

| 7                    | 6                    | 5                     | 4                     | 3                     | 2                     | 1                   | 0                   |

|----------------------|----------------------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------|---------------------|

| MSEL1 <sup>(1)</sup> | MSEL0 <sup>(1)</sup> | CRCACT <sup>(2)</sup> | MCKDIS <sup>(3)</sup> | FCKENA <sup>(4)</sup> | SELCH2 <sup>(5)</sup> | RND1 <sup>(6)</sup> | RND0 <sup>(6)</sup> |

#### Notes

- 1. MSEL1 and MSEL0; these bits select the used input interface, the input data format and the input synchronization type (see Table 22).

- 2. CRCACT; automatic/forced CRC activity:

- a) CRCACT = 0; the SAA2501 uses the protection bit in the ISO/MPEG frame header to determine the presence of the CRC.

- b) CRCACT = 1; the SAA2501 assumes the CRC always to be present. The protection bit in the used ISO/MPEG frame header is forced to 0.

- 3. MCKDIS; buffered master clock MCLK disabling:

- a) MCKDIS = 0; enable MCLK.

- b) MCKDIS = 1; disable (3-state) MCLK.

- 4. FCKENA; buffered  $256f_s$  or  $384f_s$  output signal FSCLK enabling:

- a) FCKENA = 0; disable (3-sate) FSCLK.

- b) FCKENA = 1; enable FSCLK.

- 5. SELCH2; with dual channel mode input data (with other modes of input data 'don't care':

- a) SELCH2 = 0; select channel I.

- b) SELCH2 = 1; select channel II.

- 6. RND1 and RND0; these bits select the rounding of the baseband audio output samples (see Table 23).

| MSEL1 | MSEL0 | USED INPUT INTERFACE | INPUT SYNCHRONIZATION               |

|-------|-------|----------------------|-------------------------------------|

| 0     | 0     | master               | to ISO/MPEG synchronization pattern |

| 0     | 1     | EU147                | to synchronization signal CDSSY     |

| 1     | 0     | slave                | to ISO/MPEG synchronization pattern |

| 1     | 1     | slave                | to synchronization signal CDSSY     |

#### Table 23 RND1 and RND0

| RND1 | RND0 | OUTPUT SAMPLE ROUNDING LENGTH |

|------|------|-------------------------------|

| 0    | 0    | 16 bits                       |

| 0    | 1    | 18 bits                       |

| 1    | 0    | 20 bits                       |

| 1    | 1    | 22 bits                       |

SAA2501

#### 7.20.8 INPUT DATA FRAME HEADER ITEMS

Information about the input data, derived by the SAA2501 from the input data frame headers, may be read from the frame header items. Both the frame header bytes decoded from the input bitstream and the header bytes used for the actual decoding may be read.

The decoded frame header item is valid independent of the value of status flag INSYNC, it e.g. shows the decoded

headers while the SAA2501 is in the process of synchronizing.

The used frame header item is only valid if status flag INSYNC is set. The used header bytes are derived by the SAA2501 from the decoded header bytes by overruling NOPR to 0 if settings bit CRCACT = 1, and overruling detected errors.

| T-1.1- 04 | Description of the | and the factor framework | . Is a star stress | 0.1 |        | (          |

|-----------|--------------------|--------------------------|--------------------|-----|--------|------------|

| Table 24  | Decoded in         | put data frame           | e neader item;     | 3 D | ytes ( | read-only) |

| SUBSEQUENT<br>BYTES      | 7                   | 6                   | 5                    | 4                    | 3                    | 2                    | 1                     | 0                     |

|--------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|

| Decoded header<br>byte 1 | SY3 <sup>(1)</sup>  | SY2 <sup>(1)</sup>  | SY1 <sup>(1)</sup>   | SY0 <sup>(1)</sup>   | ID <sup>(2)</sup>    | LAY1 <sup>(3)</sup>  | LAY0 <sup>(4)</sup>   | NOPR <sup>(5)</sup>   |

| Decoded header<br>byte 2 | BR3 <sup>(6)</sup>  | BR2 <sup>(6)</sup>  | BR1 <sup>(6)</sup>   | BR0 <sup>(6)</sup>   | FS1 <sup>(7)</sup>   | FS0 <sup>(7)</sup>   | undefined             | undefined             |

| Decoded header<br>byte 3 | MOD1 <sup>(8)</sup> | MOD0 <sup>(8)</sup> | MODX1 <sup>(9)</sup> | MODX0 <sup>(9)</sup> | COPR <sup>(10)</sup> | ORIG <sup>(11)</sup> | EMPH1 <sup>(12)</sup> | EMPH0 <sup>(12)</sup> |

| Table 25 Used input | data frame header item; 3 k | oytes (read-only) |

|---------------------|-----------------------------|-------------------|

|---------------------|-----------------------------|-------------------|

| SUBSEQUENT<br>BYTES   | 7                   | 6                   | 5                    | 4                    | 3                    | 2                    | 1                     | 0                     |

|-----------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|-----------------------|-----------------------|

| Used header<br>byte 1 | 1                   | 1                   | 1                    | 1                    | 1                    | 1                    | LAY0 <sup>(4)</sup>   | NOPR <sup>(5)</sup>   |

| Used header<br>byte 2 | BR3 <sup>(6)</sup>  | BR2 <sup>(6)</sup>  | BR1 <sup>(6)</sup>   | BR0 <sup>(6)</sup>   | FS1 <sup>(7)</sup>   | FS0 <sup>(7)</sup>   | undefined             | undefined             |

| Used header<br>byte 3 | MOD1 <sup>(8)</sup> | MOD0 <sup>(8)</sup> | MODX1 <sup>(9)</sup> | MODX0 <sup>(9)</sup> | COPR <sup>(10)</sup> | ORIG <sup>(11)</sup> | EMPH1 <sup>(12)</sup> | EMPH0 <sup>(12)</sup> |

Notes to "Table 24" and "Table 25"

- 1. SY3 to SY0; last 4 bits of the synchronization word. For ISO/MPEG only; undefined for EU147 input data.

- 2. ID; algorithm identification. For ISO/MPEG only; undefined for EU147 input data.

- 3. LAY1; layer Most Significant Bit (MSB). For ISO/MPEG only; undefined for EU147 input data.

- 4. LAY0; layer Least Significant Bit (LSB). When decoding EU147 input data these bits are undefined in the decoded header byte and equal 0 in the used header byte.

- 5. NOPR; CRC on header, bit allocation and scale factor select information activity flag. When decoding EU147 input data these bits are undefined in the decoded header byte and equal 0 in the used header byte.

- 6. BR3 to BR0; bit rate index.

- 7. FS1 and FS0; sample rate index.

- 8. MOD1 and MOD0; mode.

- 9. MODX1 and MODX0; mode extension.

- 10. COPR; copyright flag.

- 11. ORIG; original or home copy flag.

- 12. EMPH1 and EMPH0; audio de-emphasis, these bits are only meant to monitor the current de-emphasis mode; the corresponding de-emphasis is performed by the SAA2501 automatically before the baseband audio signal is output.

SAA2501

#### 7.20.9 ERROR REPORT ITEM