# MOS INTEGRATED CIRCUIT $\mu PD6901$

# 6 BIT D/A CONVERTER FOR VIDEO SIGNAL PROCESSING CMOS LSI

The  $\mu$ PD6901 is an 6 bit D/A converter for use in video applications. The high-speed CMOS processing technology and the matrix current cell method adopted for this CMOS device have enabled fast conversion rates to be achieved. Conversion rates of up to 20 Msps can be attained while operating at low power consumption, making this device ideal for a wide range of applications including digital TV systems and video systems.

#### **FEATURES**

• Resolution: 6 bits

Conversion rate: 20 Mpsps

Linearity: ±1/2 LSB MAX.

Reference voltage: 2.0 V TYP.

Power supply voltage: +5 V single

Low power consumption (110 mW TYP.)

TTL compatible (Digital inputs)

• 16 pin plastic DIP, and 16 pin plastic SOP (375 mil)

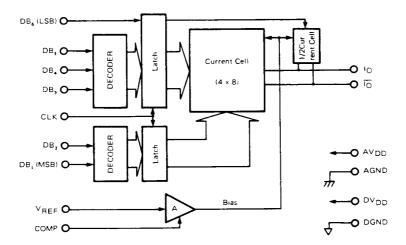

#### **BLOCK DIAGRAM**

#### ORDERING INFORMATION

| Ordering Name | Package                      |

|---------------|------------------------------|

| μPD6901C      | 16 pin plastic DIP (300 mil) |

| μPD6901G      | 16 pin plastic SOP (375 mil) |

NEC cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

The \* mark outside the columns denotes major points where revisions or additions are made in this edition.

© NEC Corporation 1987

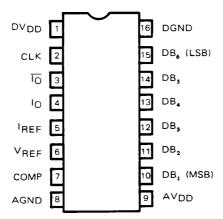

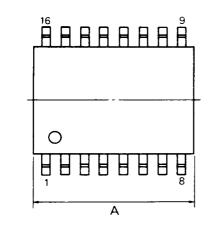

#### **CONNECTION DIAGRAM (Top View)**

| 1  | $DV_DD$         | Digital power supply          |

|----|-----------------|-------------------------------|

| 2  | CLK             | Sampling clock input          |

| 3  | ĪO              | Complementary current output  |

| 4  | Io              | Current output                |

| 5  | IREF            | Full-scale current adjustment |

| 6  | $v_{REF}$       | Reference voltage input       |

| 7  | COMP            | Amp compensation              |

| 8  | AGND            | Analog GND                    |

| 9  | $AV_{DD}$       | Analog power supply           |

| 10 | $DB_1$          | Digital input (MSB)           |

| 11 | $DB_2$          | Digital input (2nd)           |

| 12 | $DB_3$          | Digital input (3rd)           |

| 13 | DB <sub>4</sub> | Digital input (4th)           |

| 14 | DB <sub>5</sub> | Digital input (5th)           |

| 15 | $DB_6$          | Digital input (LSB)           |

| 16 | DGND            | Digital GND                   |

# ABSOLUTE MAXIMUM RATINGS ( $T_a = 25$ °C)

| Power supply voltage        | -0.3 to +7.0                 | V  |

|-----------------------------|------------------------------|----|

| Input terminal voltage      | -0.3 to V <sub>DD</sub> +0.3 | V  |

| Output terminal voltage     | -0.3 to V <sub>DD</sub> +0.3 | V  |

| Analog power supply voltage | DVDD-0.3 to DVDD +0.3        | V  |

| Analog GND voltage          | DGND-0.3 to DGND+0.3         | V  |

| Operating temperature range | -20 to +75                   | °C |

| Storage temperature range   | -40 to +125                  | °C |

# RECOMMENDED OPERATING CONDITIONS ( $T_a = -20 \text{ to } +75 \text{ °C}$ )

| CHARACTERISTIC                        | SYMBOL          | MIN. | TYP. | MAX. | UNIT | TEST CONDITION |

|---------------------------------------|-----------------|------|------|------|------|----------------|

| Power supply voltage                  | V <sub>DD</sub> | 4.5  | 5.0  | 5.5  | V    |                |

| Reference voltage                     | VREF            | 1.8  | 2.0  | 2.2  | V    |                |

| Reference resistance                  | RREF            |      | 390  |      | Ω    |                |

| Sampling clock                        | fsamp           | DC   |      | 20   | MHz  |                |

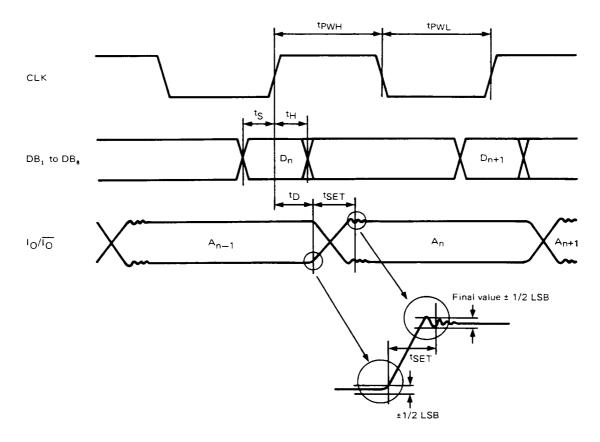

| Sampling clock low level pulse width  | tPWL            | 15   |      |      | ns   |                |

| Sampling clock high level pulse width | tPWH            | 15   |      |      | ns   |                |

| Data set up time                      | tS              | 20   |      |      | ns   |                |

| Data hold time                        | tн              | 10   |      |      | ns   |                |

| Digital input high level              | VIH             | 2.7  |      |      | V    |                |

| Digital input low level               | VIL             |      |      | 0.6  | v    |                |

| Compensation capacity                 | ССОМР           | 0.01 | 1.0  |      | μF   |                |

### ELECTRICAL CHARACTERISTICS ( $T_a$ = -20 to +75 °C, $V_{DD}$ = 5 V $\pm$ 0.5 V, $f_{samp}$ = 20 MHz)

| CHARACTERISTIC             | SYMBOL          | MIN. | TYP.  | MAX. | UNIT | TEST CONDITIONS                                                                        |

|----------------------------|-----------------|------|-------|------|------|----------------------------------------------------------------------------------------|

| Power supply current       | ¹DD             |      | 22    | 50   | mA   | V <sub>DD</sub> = 5.0 V                                                                |

| Resolution                 | RES             |      | 6     |      | bit  |                                                                                        |

| Non-linearity error        | NL              |      | ±0.11 | ±0.5 | LSB  | $T_a = 0 \text{ to } 60^{\circ}\text{C},$<br>$V_{DD} = 5 \text{ V} \pm 0.25 \text{ V}$ |

| Differential non-linearity | DNL             |      | ±0.04 | ±0.5 | LSB  | T <sub>a</sub> = 0 to 60° C,<br>V <sub>DD</sub> = 5 V ± 0.25 V                         |

| Output compliance          | v <sub>o</sub>  | 2.5  | 3.0   |      | V    | V <sub>DD</sub> = 5.0 V                                                                |

| Analog output delay time   | t <sub>D</sub>  |      | 40    |      | ns   |                                                                                        |

| Settling time              | †SET            |      | 40    |      | ns   |                                                                                        |

| Full-scale current         | IFS             | 9    | 10    | 11   | mA   | V <sub>REF</sub> =2.0 V, R <sub>REF</sub> =390 Ω                                       |

| Zero-scale offset current  | Izs             |      |       | 20   | μА   | V <sub>REF</sub> =2.0 V, R <sub>REF</sub> =390 Ω                                       |

| Digital input capacitance  | c <sub>DI</sub> |      | 10    | 20   | pF   |                                                                                        |

| Digital input current      | II              |      |       | 10   | μА   |                                                                                        |

#### TIMING CHART

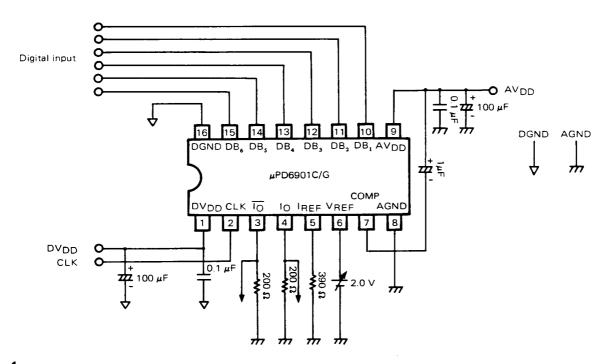

#### TEST CIRCUIT

4

#### PIN DESCRIPTIONS

| DGND | (Pin 16) | Digital system ground              |

|------|----------|------------------------------------|

| AGND | (Pin 8)  | Analog system ground               |

| DVDD | (Pin 1)  | Digital system power supply (+5 V) |

| AVDD | (Pin 9)  | Analog system power supply (+5 V)  |

The digital system power supply and ground is isolated from the analog system power supply and ground in the IC as a precaution against noise. The ground and power supply lines are also isolated on the circuit boards, the analog ground being as wide as possible for better stability.

Insert by-pass capacitors of about 0.01  $\mu$ F and 47  $\mu$ F between the analog power line and analog ground, and also between the digital power line and digital ground. These capacitors should be connected as close as possible, to the  $\mu$ PD6901C pins. Supply the digital system power from the analog power line through the low path filter to prevent from luch up.

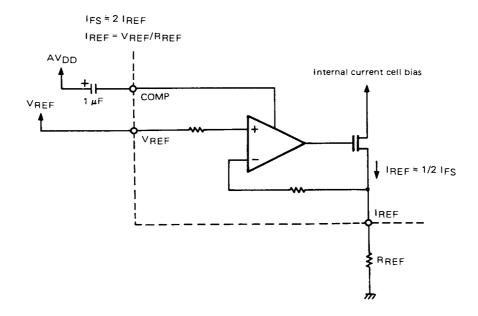

IREF (Pin 5) Full-scale current adjustment pin

VREF (Pin 6) Reference voltage input pin

These pins are used in adjustment of the analog output current (full-scale current).

The analog output current (full-scale current IFS) is set by the reference voltage VREF and the reference resistance RREF connected between the IREF pin and analog ground.

The recommended reference voltage and reference resistance values are VREF = 2.0 V and RREF = 390  $\Omega$  respectively. The output analog current IFS in this case will be 10 mA. Also connect by-pass capacitors of about 0.01  $\mu$ F and 47  $\mu$ F between the VREF pin and GND in the same way as the by-pass capacitors connected to the power pins.

COMP (Pin 7) Phase compensation capacitor connection

A capacitor for phase compensation of the internal amplifier is connected to this pin. Connect a 1.0  $\mu$ F capacitor between this pin and analog VDD.

DB<sub>1</sub> to DB<sub>6</sub> (Pins 10 thru 15) Digital data input pins

$DB_1$  to  $DB_6$  are the 6 bit digital data input pins. The code format is binary, and the input voltage level is TTL compatible.

| Digital input code       |                 |                 |                 |     |                          |                       |

|--------------------------|-----------------|-----------------|-----------------|-----|--------------------------|-----------------------|

| DB <sub>1</sub><br>(MSB) | DB <sub>2</sub> | DB <sub>3</sub> | DB <sub>4</sub> | DB₅ | DB <sub>6</sub><br>(LSB) | Analog output current |

| 0                        | 0               | 0               | 0               | 0   | 0                        | 0 note                |

| 0                        | 0               | 0               | 0               | 0   | 1                        | 1/64 IFS              |

| :                        | :               | :               | :               | :   | i ,                      | :                     |

| 1                        | 1               | 1               | 1               | 0   | 1                        | 61/64 IFS             |

| 1                        | 1               | 1               | 1               | 1   | 0                        | 62/64 IFS             |

| 1                        | 1               | 1               | 1               | 1   | 1                        | 63/64 I <sub>FS</sub> |

Note: Excluding offset current

Digital data (DB<sub>1</sub> to DB<sub>6</sub>) is latched by the rising edge of the sampling clock, and converted to corresponding analog outputs.

#### CLK (Pin 2) Sampling clock input pin

Digital data is latched by the rising edge of the clock signal applied to the sampling clock input pin, and is sub-sequently converted to analog outputs. The maximum clock frequency is 20 MHz.

I<sub>O</sub> (Pin 4) Analog signal output pin

In (Pin 3) Analog signal complementary output pin

These two pins are current output pins. The full-scale output current is determined by the reference resistance  $R_{RFF}$  and reference voltage  $V_{REF}$ .

$\overline{\text{IO}}$  is the complementary output pin of IO. The added output current from the IO and  $\overline{\text{IO}}$  pins becomes the full-scale current in accordance with the above equation. Analog output current can be easily converted to an analog output voltage by connecting a resistance between the IO or  $\overline{\text{IO}}$  pin and analog ground. In this case resistances must also be connected to the IO and  $\overline{\text{IO}}$  pins.

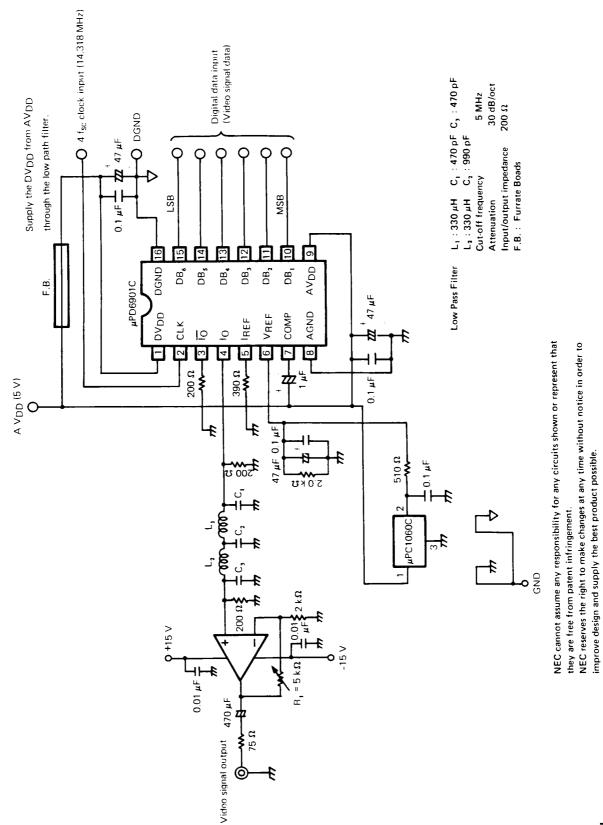

#### Example of an Application Circuit

This example shows D/A conversion of video signal (NTSC) digital data at a conversion rate of four times the subcarrier frequency (4  $f_{SC}$ ) to obtain the video output signal.

The analog output signal is passed via a low-pass filter (LPF) to a video amplifier to be amplified prior to output.

6

#### **APPLICATION CIRCUIT**

7

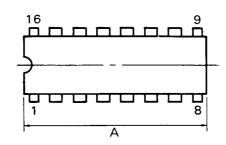

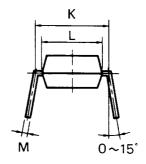

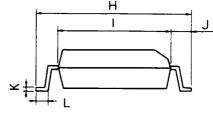

#### 16PIN PLASTIC DIP (300 mil)

P16C-100-300B

#### NOTES

- Each lead centerline is located within 0.25 mm (0.01 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS | INCHES       |

|------|-------------|--------------|

| Α    | 20.32 MAX.  | 0.800 MAX.   |

| В    | 1.27 MAX.   | 0.050 MAX.   |

| С    | 2.54 (T.P.) | 0.100 (T.P.) |

| D .  | 0.50 ±0 10  | 0.020-0.004  |

| F    | 1.1 MIN.    | 0.043 MIN.   |

| G    | 3.5 ±0 3    | 0.138=0 012  |

| н    | 0.51 MIN.   | 0.020 MIN.   |

| 1    | 4.31 MAX.   | 0.170 MAX.   |

| J    | 5.08 MAX.   | 0.200 MAX.   |

| К    | 7.62 (T.P.) | 0.300 (T.P.) |

| L    | 6.5         | 0.256        |

| М    | 0.25 -0 05  | 0.010 -0 003 |

| N    | 0.25        | 0.01         |

| Р    | 1.1 MIN.    | 0.043 MIN.   |

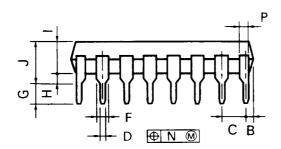

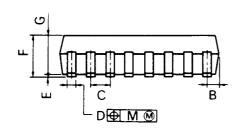

#### 16 PIN PLASTIC SOP (375 mil)

P16GM-50-375B

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS          | INCHES        |

|------|----------------------|---------------|

| Α    | 10.46 MAX.           | 0.412 MAX.    |

| В    | 0.78 MAX.            | 0.031 MAX.    |

| С    | 1.27 (T.P.)          | 0.050 (T.P.)  |

| D    | 0.40 -0.05           | 0.016 - 0.003 |

| E    | 0.1-0:1              | 0.004 - 0.008 |

| F    | 2.9 MAX.             | 0.115 MAX.    |

| G    | 2.50                 | 0.098         |

| Н    | 10.3 <sup>±0.3</sup> | 0.406 - 0.012 |

| 1    | 7.2                  | 0.283         |

| J    | 1.6                  | 0.063         |

| К    | 0.15 -0.06           | 0.006 +0.004  |

| L    | 0.8 <sup>±0.2</sup>  | 0.031-0.008   |

| M    | 0.12                 | 0.005         |