## PACE1754/SOS PROCESSOR INTERFACE CIRCUIT (PIC) CMOS/SOS SPACE PROCESSOR MICROPERIPHERAL

#### **FEATURES**

- The PACE1754 (PIC) is a support chip for the PACE1750A/AE Processors. It eliminates the SSI/MSI Logic and external system functions required in typical 1750A implementations.

- Provides a significant savings in part-count and power dissipation enhancing reliability and overall system speed performance.

- Provides an optimal interface when used with the PACE1753 MMU/COMBO in a full 1750A implementation.

- Provides the following additional important system functions:

- Programmable READY for memory and I/O

- Automatic READY during self-test and internal I/O instructions

- 100KHz timer clock output provided

- Programmable system watchdog—ranges from 1 µs to 1 minute

- Programmable Bus time-out function

- Memory Parity generation/detection

- Error detection of unimplemented memory and/or I/O space addressing

- First failing memory address register for diagnostics

- High drive three-state address latches

- Built-in system test program—automatically tests the PACE1750A/AE CPUs, PACE1753 MMU/COMBO, PACE1754 PIC and system address lines as well as memory and I/O strobes

- System configuration decoding and buffering

- Interrupt acknowledge decoder and strobe

- Start up ROM support per MIL-STD-1750A

- Memory or I/O READ/WRITE three-state strobes with external three-state control for DMA applications

- Available with Class S manufacturing, screening, and testing.

- SOS insulated substrate technology provides absolute latch-up immunity and excellent SEU tolerance.

- SOS devices are fully interchangeable with application-proven SMD CMOS P1754 devices.

- 20, 25 and 30 MHz operation over full Military Temperature Range

- Single 5V ± 10% Power Supply

- Available in:

- 68-Lead Quad Pack with optional Gull Wing Surface Mount

# PACE1754 PROCESSOR INTERFACE CIRCUIT DESCRIPTION

The PACE1754 Processor Interface Circuit (PIC) is a single chip implementation of many special system functions that are often required when using the PACE1750A/AE, a single chip microprocessor. The PIC allows a system designer to design a higher performance, more effecient microprocessor system which uses less power and takes up less board space.

The PIC provides many important system functions. These functions are governed by respective bit positions in a programmable Control Register which is incorporated in the PIC. The individual bits of the control register are set to select the various features and are set to a specified default value upon Reset.

#### **ABSOLUTE MAXIMUM RATINGS<sup>1</sup>**

| Supply Voltage Range                                         | 0.5V to +7.0V                  |

|--------------------------------------------------------------|--------------------------------|

| Input Voltage Range                                          | 0.5V to V <sub>CC</sub> + 0.5V |

| Storage Temperature Range                                    | −65°C to +150°C                |

| Input Current Range                                          | -30mA to +5mA                  |

| Current applied to any output <sup>3</sup>                   | 150mA                          |

| Maximum Power Dissipation <sup>2</sup>                       | 1.5W                           |

| Lead Temperature Range (soldering 10 seconds)                | 300°C                          |

| Thermal resistance (θ <sub>JC</sub> ):<br>Packages QL and QG | 8°C/W                          |

# RECOMMENDED OPERATING CONDITIONS

| Case Temperature | GND | V <sub>CC</sub> |

|------------------|-----|-----------------|

| −55°C to +125°C  | 0   | 4.5V to +5.5V   |

#### Notes:

- Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2. Must withstand the added power dissipation due to short circuit test e.g.,  $I_{\text{OS}}$ .

- 3. Duration 1 second or less.

#### DC ELECTRICAL SPECIFICATIONS (Over recommended operating conditions)

| Symbol            | Parameter                                                                                                                                                                                              |           | Min                   | Max                   | Unit | Conditi                                                              | ons <sup>1</sup>          |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|-----------------------|------|----------------------------------------------------------------------|---------------------------|

| V <sub>IH</sub>   | Input HIGH Voltage                                                                                                                                                                                     |           | 2.0                   | V <sub>CC</sub> + 0.5 | V    |                                                                      |                           |

| V <sub>IL</sub>   | Input LOW Voltage                                                                                                                                                                                      |           | -0.5                  | 0.8                   | V    |                                                                      |                           |

| V <sub>CD</sub>   | Input Clamp Diode Voltage                                                                                                                                                                              |           |                       | -1.2                  | V    | $V_{CC} = 4.5V, I_{IN} = -$                                          | 18mA                      |

|                   | O. to . t      O       / o   t o o o                                                                                                                                                                   |           | 2.4                   |                       | V    | $V_{CC} = 4.5V$ ,                                                    | $I_{OH} = -8.0 \text{mA}$ |

| V <sub>OH</sub>   | Output HIGH Voltage                                                                                                                                                                                    |           | V <sub>CC</sub> - 0.2 |                       | V    | $V_{IN} = 0.8V, 2.0V$                                                | I <sub>OH</sub> = -300μA  |

| \/                | Output LOW Voltage,                                                                                                                                                                                    |           |                       | 0.5                   | V    | $V_{CC} = 4.5V$ ,                                                    | $I_{OL} = 8.0 \text{mA}$  |

| V <sub>OL</sub>   | except A <sub>0</sub> - A <sub>15</sub>                                                                                                                                                                |           |                       | 0.2                   | V    | $V_{IN} = 0.8V, 2.0V$                                                | I <sub>OL</sub> = 300μA   |

| \/                | Output LOW Voltage,                                                                                                                                                                                    |           |                       | 0.5                   | V    | $V_{CC} = 4.5V$ ,                                                    | $I_{OL} = 20.0 \text{mA}$ |

| V <sub>OL</sub>   | $A_0 - A_{15}$                                                                                                                                                                                         |           |                       | 0.2                   | V    | $V_{IN} = 0.8V, 2.0V$                                                | I <sub>OL</sub> = 300μA   |

| lн                | Input HIGH Current,<br>except IB <sub>0</sub> – IB <sub>15</sub> , parity/IB <sub>16</sub> ,<br>SING ERR, A <sub>0</sub> /EXT AD <sub>0</sub> ,<br>A <sub>1</sub> /EXT AD <sub>1</sub> , STRBA         |           |                       | 300                   | μΑ   | $V_{IN} = V_{CC},$<br>$V_{CC} = 5.5V$                                |                           |

| l <sub>IH</sub>   | Input HIGH Current,<br>IB <sub>0</sub> – IB <sub>15</sub> , parity/IB <sub>16</sub> ,<br>A <sub>0</sub> /EXT AD <sub>0</sub> , A <sub>1</sub> /EXT AD <sub>1</sub>                                     |           |                       | 100                   | μΑ   | $V_{IN} = V_{CC},$<br>$V_{CC} = 5.5V$                                |                           |

| Iн                | Input HIGH Current,<br>STRBA, SING ERR                                                                                                                                                                 |           |                       | 300                   | μΑ   | $V_{IN} = V_{CC},$<br>$V_{CC} = 5.5V$                                |                           |

| I <sub>IL</sub>   | Input LOW Current,<br>except IB <sub>0</sub> – IB <sub>15</sub> , parity/IB <sub>16</sub> ,<br>SING ERR, A <sub>0</sub> /EXT AD <sub>0</sub> ,<br>A <sub>1</sub> /EXT AD <sub>1</sub> , STRBD, TEST ON |           |                       | -50                   | μΑ   | $V_{IN} = GND,$<br>$V_{CC} = 5.5V$                                   |                           |

| I <sub>IL</sub>   | Input LOW Current,<br>IB <sub>0</sub> – IB <sub>15</sub> , parity/IB <sub>16</sub> , SING ERR,<br>A <sub>0</sub> /EXT AD <sub>0</sub> , A <sub>1</sub> /EXT AD <sub>1</sub>                            |           |                       | -50                   | μΑ   | $V_{IN} = GND,$<br>$V_{CC} = 5.5V$                                   |                           |

| I <sub>IL</sub>   | Input LOW Current,<br>STRBD, TEST ON                                                                                                                                                                   |           |                       | 300                   | μΑ   | $V_{IN} = GND,$<br>$V_{CC} = 5.5V$                                   |                           |

| I <sub>OZH</sub>  | Output Three-State Cu                                                                                                                                                                                  | rrent     |                       | 50                    | μΑ   | $V_{OUT} = 2.4V, V_{CC}$                                             | = 5.5V                    |

| I <sub>OZL</sub>  | Output Three-State Cu                                                                                                                                                                                  | rrent     |                       | -50                   | μΑ   | $V_{OUT} = 0.5V, V_{CC}$                                             | = 5.5V                    |

| Iccac             | Quiescent Power Supply Current (CMOS Input Levels)                                                                                                                                                     |           |                       | 25                    | mA   | $V_{IN}$ < 0.2V or > $V_{C}$<br>f = 0MHz, Outputs<br>$V_{CC}$ = 5.5V | •                         |

| I <sub>CCQT</sub> | Quiescent Power<br>Supply Current<br>(TTL Input Levels)                                                                                                                                                |           |                       | 100                   | mA   | $V_{IN} = 3.4V$ , $f = 0M$<br>All Inputs, Outputs<br>$V_{CC} = 5.5V$ |                           |

|                   | Dynamic Power                                                                                                                                                                                          | f = 20MHz |                       | 90                    | mA   | $V_{IN} = 0V \text{ to } V_{CC},$                                    |                           |

| ICCD              | Supply Current f = 25MHz                                                                                                                                                                               |           |                       | 100                   | mA   | tr = tf = 2.5  ns typ.                                               | •,                        |

|                   |                                                                                                                                                                                                        | f = 30MHz |                       | 125                   | mA   | Outputs Open, V <sub>C</sub>                                         | <sub>C</sub> = 5.5V       |

| I <sub>OS</sub>   | Output Short Circuit Current <sup>2</sup>                                                                                                                                                              |           | -25                   |                       | mA   | $V_{OUT} = GND, V_{CC}$                                              | = 5.5V                    |

| C <sub>IN</sub>   | Input Capacitance                                                                                                                                                                                      |           |                       | 10                    | pF   | Inputs Only                                                          |                           |

| C <sub>OUT</sub>  | Output/Bi-directional<br>Capacitance                                                                                                                                                                   |           |                       | 15                    | pF   | Outputs Only<br>(Including I/O Buff                                  | ers)                      |

#### Notes:

$<sup>1. \ \ 4.5 \</sup>text{V} \leq \text{V}_{CC} \leq 5.5 \text{V}, \ -55 ^{\circ}\text{C} \leq \text{T}_{C} \leq \text{+}125 ^{\circ}\text{C}. \ \ \text{Unless otherwise specified, testing shall be conducted at worst-case conditions}.$

<sup>2.</sup> Duration of the short should not exceed one second; only one output may be shorted at a time.

#### AC ELECTRICAL CHARACTERISTICS<sup>1,2</sup>

$(V_{CC} = 5V \pm 10\% \text{ Over Recommended Operating Conditions})$

|                                                 |                                                                | 20 MHz |     | 25MHz |     | 30 MHz |     |      |

|-------------------------------------------------|----------------------------------------------------------------|--------|-----|-------|-----|--------|-----|------|

| Symbol                                          | Parameter                                                      | Min    | Max | Min   | Max | Min    | Max | Unit |

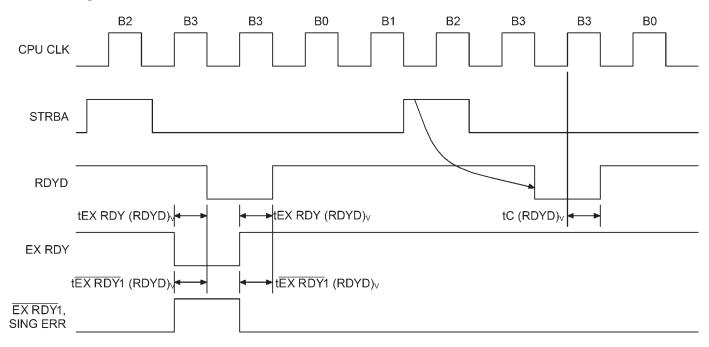

| tEXRDY (RDYD) <sub>V</sub>                      | Time from External Ready to<br>Ready Data Valid                |        | 19  |       | 15  |        | 14  | ns   |

| tC (RDYD) <sub>V</sub>                          | Time from Clock Read to<br>Ready Data Valid                    |        | 29  |       | 25  |        | 23  | ns   |

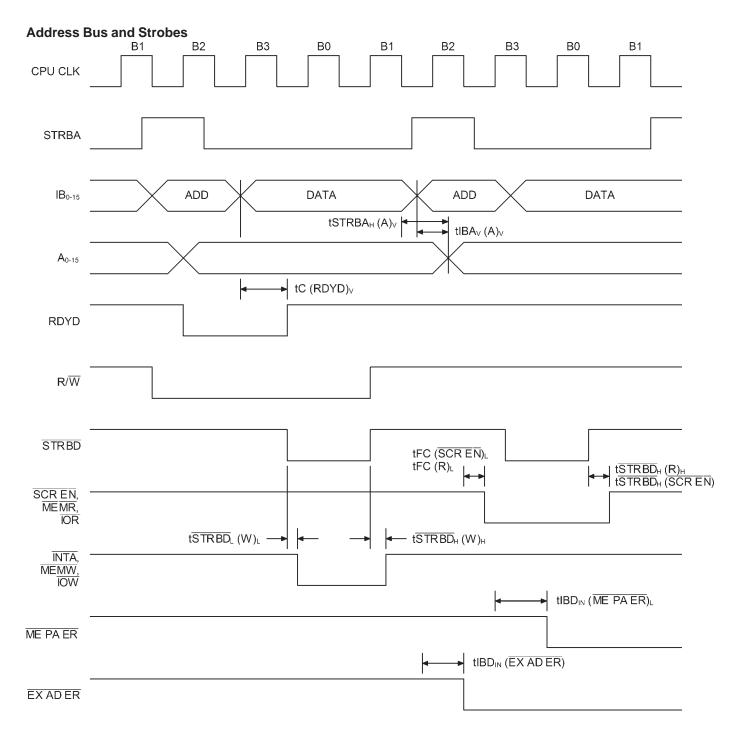

| tSTRBA <sub>H</sub> (A) <sub>V</sub>            | Time from Strobe Address HIGH to<br>Address Bus Valid          |        | 29  |       | 25  |        | 23  | ns   |

| $tIBA_V (A)_V$                                  | Time from Information Bus Address to Address Bus Valid         |        | 31  |       | 27  |        | 25  | ns   |

| tFC(R) <sub>L</sub>                             | Time from Falling Clock to Read LOW                            |        | 25  |       | 21  |        | 19  | ns   |

| $\overline{\text{tSTRBD}}_{H}(R)_{H}$           | Time from Strobe Data HIGH to Read HIGH                        |        | 25  |       | 21  |        | 19  | ns   |

| tSTRBD <sub>L</sub> (W) <sub>L</sub>            | Time from Strobe Data LOW to<br>Write LOW                      |        | 27  |       | 23  |        | 21  | ns   |

| tSTRBD <sub>H</sub> (W) <sub>H</sub>            | Time from Strobe Data HIGH to<br>Write HIGH                    |        | 27  |       | 23  |        | 21  | ns   |

| tIBD <sub>IN</sub> (ME PA ER) <sub>L</sub>      | Time from Information Bus Data into<br>Memory Parity Error LOW |        | 24  |       | 20  |        | 18  | ns   |

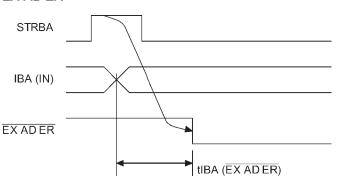

| tIBA <sub>IN</sub> (EX AD ER)                   | Time from Information Bus Address into External Address Error  |        | 32  |       | 28  |        | 26  | ns   |

| tSTRBD <sub>L</sub> -<br>(STRTROM) <sub>V</sub> | Time from Strobe Data LOW to<br>Start-up ROM Valid             |        | 27  |       | 23  |        | 21  | ns   |

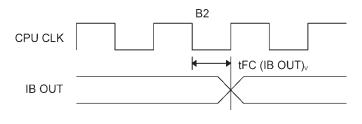

| tFC (IB OUT) <sub>V</sub>                       | Time from Falling Clock to<br>Information Bus Valid            |        | 32  |       | 28  |        | 26  | ns   |

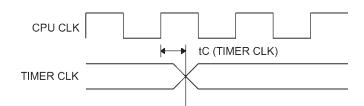

| tC (TIMER CLK)                                  | Time from Rising Edge of Clock to<br>Timer Clock               |        | 32  |       | 28  |        | 26  | ns   |

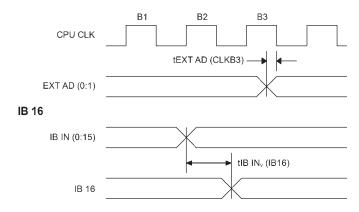

| tIB IN <sub>V</sub> (IB16)                      | Time from Information Bus Data to Parity Valid                 |        | 26  |       | 23  |        | 21  | ns   |

| tEXTAD (CLKB3)                                  | Extended Address<br>Setup Time                                 | 10     |     | 10    |     | 10     |     | ns   |

| tEXRDY1 (RDYD) <sub>V</sub>                     | Time from External Ready Data to Ready Data Valid              |        | 30  |       | 26  |        | 24  | ns   |

| tSTRBD <sub>H</sub> (SCREN)                     | Time from STRBD HIGH to SCR Enable;                            |        | 32  |       | 28  |        | 26  | ns   |

#### Notes

<sup>1.</sup>  $4.5\text{V} \le \text{V}_{CC} \le 5.5\text{V}$ ,  $-55^{\circ}\text{C} \le \text{T}_{C} \le +125^{\circ}\text{C}$ . Unless otherwise specified, testing shall be conducted at worst-case conditions.

<sup>2.</sup> All measurements of delay times on active signals are related to the 1.5V levels.

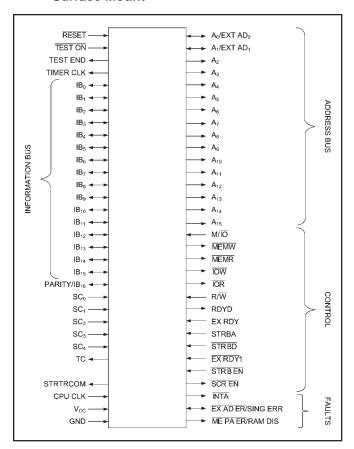

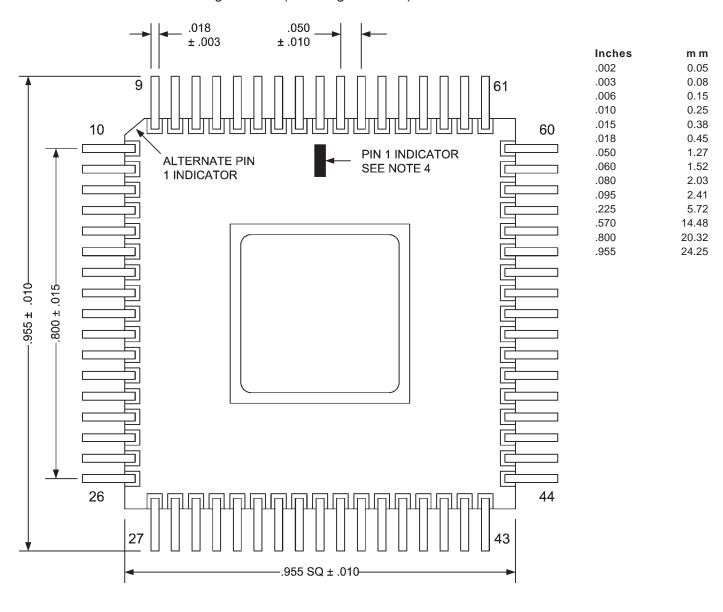

#### **TERMINAL CONNECTIONS - PACKAGES QL AND QG**

| Cas                | se Outlines         | U and Y            |                          |                    |                                    |

|--------------------|---------------------|--------------------|--------------------------|--------------------|------------------------------------|

| Terminal<br>Number | Terminal<br>Symbol  | Terminal<br>Number | Terminal<br>Symbol       | Terminal<br>Number | Terminal<br>Symbol                 |

| 1                  | GND                 | 24                 | IB <sub>12</sub>         | 47                 | A <sub>3</sub>                     |

| 2                  | $SC_0$              | 25                 | IB <sub>13</sub>         | 48                 | GND                                |

| 3                  | SC <sub>1</sub>     | 26                 | IB <sub>14</sub>         | 49                 | A <sub>2</sub>                     |

| 4                  | TEST ON             | 27                 | IB <sub>15</sub>         | 50                 | A <sub>1</sub> /EXTAD <sub>1</sub> |

| 5                  | RESET               | 28                 | PAR ITY/IB <sub>16</sub> | 51                 | A <sub>0</sub> /EXTAD <sub>0</sub> |

| 6                  | TESTEND             | 29                 | ME PA ER/RAM DIS         | 52                 | SC <sub>4</sub>                    |

| 7                  | TIMERCLK            | 30                 | EX AD ER/SING ERR        | 53                 | $SC_3$                             |

| 8                  | SC <sub>2</sub>     | 31                 | ĪNTA                     | 54                 | TC                                 |

| 9                  | V <sub>CC</sub>     | 32                 | STRTROM                  | 55                 | CPUCLK                             |

| 10                 | IB <sub>0</sub>     | 33                 | V <sub>CC</sub>          | 56                 | STRBA                              |

| 11                 | IB <sub>1</sub>     | 34                 | GND                      | 57                 | STRBD                              |

| 12                 | IB <sub>2</sub>     | 35                 | A <sub>15</sub>          | 58                 | STRBEN                             |

| 13                 | IB <sub>3</sub>     | 36                 | A <sub>14</sub>          | 59                 | EXRDY                              |

| 14                 | IB <sub>4</sub>     | 37                 | A <sub>13</sub>          | 60                 | RDYD                               |

| 15                 | IB <sub>5</sub>     | 38                 | A <sub>12</sub>          | 61                 | R/W                                |

| 16                 | IB <sub>6</sub>     | 39                 | A <sub>11</sub>          | 62                 | GND                                |

| 17                 | IB <sub>7</sub>     | 40                 | A <sub>10</sub>          | 63                 | M/ <del>IO</del>                   |

| 18                 | EX RDY <sub>1</sub> | 41                 | A <sub>9</sub>           | 64                 | MEMW                               |

| 19                 | IB <sub>8</sub>     | 42                 | A <sub>8</sub>           | 65                 | MEMR                               |

| 20                 | IB <sub>9</sub>     | 43                 | A <sub>7</sub>           | 66                 | ĪOW                                |

| 21                 | GND                 | 44                 | A <sub>6</sub>           | 67                 | ĪŌR                                |

| 22                 | IB <sub>10</sub>    | 45                 | A <sub>5</sub>           | 68                 | V <sub>CC</sub>                    |

| 23                 | IB <sub>11</sub>    | 46                 | A <sub>4</sub>           |                    |                                    |

#### **STRT ROM**

# STRBD tSTRBD (STRT ROM),

#### **Timer Clk**

#### IB Bus Output (0:15)

#### EX AD ER

#### **Extended Addresses (0:1)**

Note: All time measurements on active signals relate to 1.5V levels.

#### **RDYD Timing**

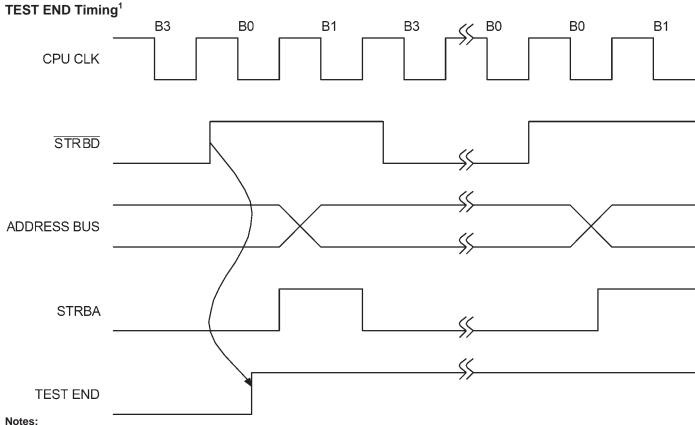

- 1. The last two instructions executed during system test are: XIO RA, 1F44, 0 and JC 7, 0000 hex, 0. After execution of the IOW bus cycle, the XIO proceeds by filling the instruction pipe with two memory read bus cycles where the opcode 7070 hex and 0000 hex are entered to the processor. As from the end of STRBD in the second cycle, TEST END is asserted. At this point, the execution of IC starts by first issuing two fetch cycles from the "old PC" (from addresses XXXX & XXXX+1). The data will be taken from system memory (because TEST END is asserted) but both the address and data are irrelevent. Following that, IC will start filling the pipe from address 0000 hex and 0001 hex, now from the system memory to start user's program execution.

- 2. All time measurements on active signals relate to 1.5V levels.

Note: All time measurements on active signals relate to 1.5V levels.

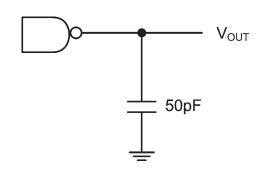

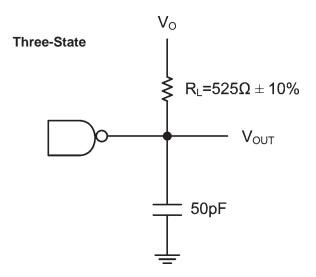

#### **TEST CIRCUITS**

#### **Standard Output (Non Three-State)**

Note: All time measurements on active signals relate to 1.5V levels.

| Parameter | Vo                 | V <sub>MEA</sub>       |

|-----------|--------------------|------------------------|

| TPLZ      | ≥ 3V               | 0.5V                   |

| TPHZ      | 0V                 | V <sub>CC</sub> - 0.5V |

| TPXL      | V <sub>CC</sub> /2 | 1.5V                   |

| TPXH      | V <sub>CC</sub> /2 | 1.5V                   |

#### **PIN FUNCTIONS**

| Symbol                             | Name                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPUCLK                             | CPU Clock                       | A single-phase input clock signal (0-40MHz, 40% to 60% duty cycle.)                                                                                                                                                                                                                                                                                                                                                                                                       |

| STRBA                              | Strobe Address                  | An active HIGH input which latches the contents of IB(0:15) into the address latches.                                                                                                                                                                                                                                                                                                                                                                                     |

| STRBD                              | Strobe Data                     | An active LOW input which is used for writing or reading data to or from the device and also to produce the external memory and I/O strobes.                                                                                                                                                                                                                                                                                                                              |

| TIMER CLK                          | Timer Clock                     | A 100KHz output (fixed frequency) based on the programmed operating frequency of the CPU clock.                                                                                                                                                                                                                                                                                                                                                                           |

| MEMW                               | Memory Write Strobe             | An active LOW output produced in memory write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MEMR                               | Memory Read Strobe              | An active LOW output produced in memory read cycles.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ĪŌW                                | I/O Write Strobe                | An active LOW output produced in output write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ĪŌR                                | I/O Read Strobe                 | An active LOW output produced in input read cycles.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ĪNTA                               | Interrupt Acknowledge<br>Strobe | An active LOW output produced after any interrupt, corresponding to an output write to address 1000 (hex).                                                                                                                                                                                                                                                                                                                                                                |

| SCR EN                             | System Configuration            | An active LOW output (in 64 pin only) produced any time an input read from address 8410 (hex), read system configuration is executed.                                                                                                                                                                                                                                                                                                                                     |

| STRBEN                             | Strobe Enable                   | An active LOW input, enabling the active state of the address outputs and the MEMR, MEMQ, IOR, and IOW outputs. When at a logic "1" (if enabled by bits EST, EAD of the control register) it will correspondingly enable the three-state state of the above signals.                                                                                                                                                                                                      |

| IB <sub>0</sub> - IB <sub>15</sub> | Information Bus (0:15)          | A bi-directional time multiplexed bus. It is an input during the address phase of any bus cycle and also during the data phase when writing. It is an output during the data phase when reading from the device.                                                                                                                                                                                                                                                          |

| IB <sub>16</sub>                   | Information Bus (16)            | A bi-directional line. It is an output during write cycles and an input during read cycles. It is used to implement the parity function at the system level.                                                                                                                                                                                                                                                                                                              |

| A(0:1)/<br>EX AD(0:1),<br>A(2:15)  | Address Bus (0:15)              | An active HIGH output bus. Contains the address of the current bus cycle as latched by the end of STRBA. In system configurations including the MMU function, the only active lines during memory are A(4:15). In this case, A(2:3) are high impedance (don't care) and A(0:1) turn into inputs called Extended Addresses, EXT ADR (0:1). In this case, these two lines supplied by the MMU, will be used to operate the programmable ready generation during bus cycles. |

| M/ <del>IO</del>                   | Memory I/O                      | An input qualifier indicating the nature of the current bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                        |

### PIN FUNCTIONS (Continued)

| Name                  | Description                                                                                                                                                                                                                                            |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read or Write         | An input qualifier indicating the nature of the current bus cycle, either Read (1) or Write (0).                                                                                                                                                       |

| External Reset        | An active LOW input used to initialize the device's hardware.                                                                                                                                                                                          |

| System Test Enable    | An active LOW input used to enable the execution of the System Test built into the device, immediately after completion of the P1750A/AE initialization and before fetching any instruction from the user program.                                     |

| System Test End       | An active HIGH output indicating whether the system test in the device has been completed. Whenever the system test is disabled by the TEST ON signal, the TEST END output will be at a logical "1" immediately after RESET is removed.                |

| Start Up ROM          | An output following the execution of the ESUR and DSUR, I/O commands as defined in MIL-STD-1750A. It will be at the logical "1" level after executing ESUR and at the logical "0" level after executing DSUR. Initially, it defaults to a logical "1". |

| Ready Data            | An active HIGH output to be connected to the P1750A/AE input to control the bus cycle termination.                                                                                                                                                     |

| External Ready Data   | An active HIGH input which at logical "0" overrides the internal RDYD generation and forces it to a logical "0".                                                                                                                                       |

| External Ready Data   | An active LOW input which at logical "1" overrides the internal RDYD generation and forces it to a logical "0".                                                                                                                                        |

| Memory Parity Error   | An active LOW output indicating a parity error when reading from memory. It becomes an active HIGH output called RAM DISABLE for handshaking with the P1753 MMU when the device is programmed to support EDAC.                                         |

| Illegal Address Error | An active LOW output indicating an illegal address error when referencing memory or I/O. It becomes an active HIGH output called SINGLE ERROR for handshaking with the P1753 MMU when the device is programmed to support EDAC.                        |

| Terminal Count        | An active HIGH output indicating a Bus time out or a watchdog trigger.                                                                                                                                                                                 |

| System Configuration  | Inputs which are buffered onto IB <sub>0</sub> –IB <sub>4</sub> when executing an I/O read from I/O address 8410 (hex), system configuration.                                                                                                          |

| Ground                | 0 volts system ground.                                                                                                                                                                                                                                 |

|                       | 5 volts ± 10% power supply.                                                                                                                                                                                                                            |

|                       | Read or Write  External Reset System Test Enable  System Test End  Start Up ROM  Ready Data  External Ready Data  External Ready Data  Memory Parity Error  Illegal Address Error  Terminal Count  System Configuration                                |

| Standardized Military<br>Drawing Part Number | Pyramid Semiconductor<br>CAGE Number | Pyramid Semiconductor<br>Part Number |

|----------------------------------------------|--------------------------------------|--------------------------------------|

| 5962-8864201UX                               | 3DTT2                                | P1754-20QLMB                         |

| 5962-8864201YX                               | 3DTT2                                | P1754-20QGMB                         |

| 5962-8864201ZX                               | 3DTT2                                | P1754-20PGMB                         |

| 5962-8864202UX                               | 3DTT2                                | P1754-30QLMB                         |

| 5962-8864202YX                               | 3DTT2                                | P1754-30QGMB                         |

| 5962-8864202ZX                               | 3DTT2                                | P1754-30PGMB                         |

| 5962-8864203UX                               | 3DTT2                                | P1754-40QLMB                         |

| 5962-8864203YX                               | 3DTT2                                | P1754-40QGMB                         |

| 5962-8864203ZX                               | 3DTT2                                | P1754-40PGMB                         |

| 5962-8864204TX                               | 3DTT2                                | P1754-20GMB                          |

| 5962-8864204XX                               | 3DTT2                                | P1754-20CMB                          |

| 5962-8864205TX                               | 3DTT2                                | P1754-30GMB                          |

| 5962-8864205XX                               | 3DTT2                                | P1754-30CMB                          |

| 5962-8864206TX                               | 3DTT2                                | P1754-40GMB                          |

| 5962-8864206XX                               | 3DTT2                                | P1754-40CMB                          |

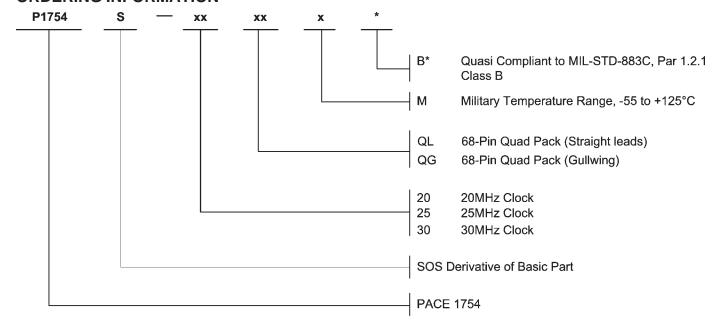

#### **ORDERING INFORMATION**

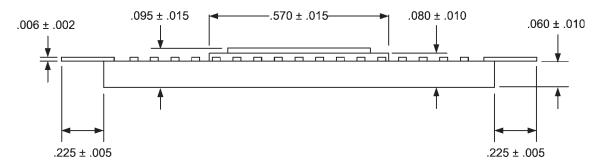

#### **CASE OUTLINE 1:**

68 Lead Quad Pack with Straight Leads (Ordering Code QL)

#### NOTES:

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Pin 1 indicator can be either rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5) Corners indicated as notched may be either notched or square.

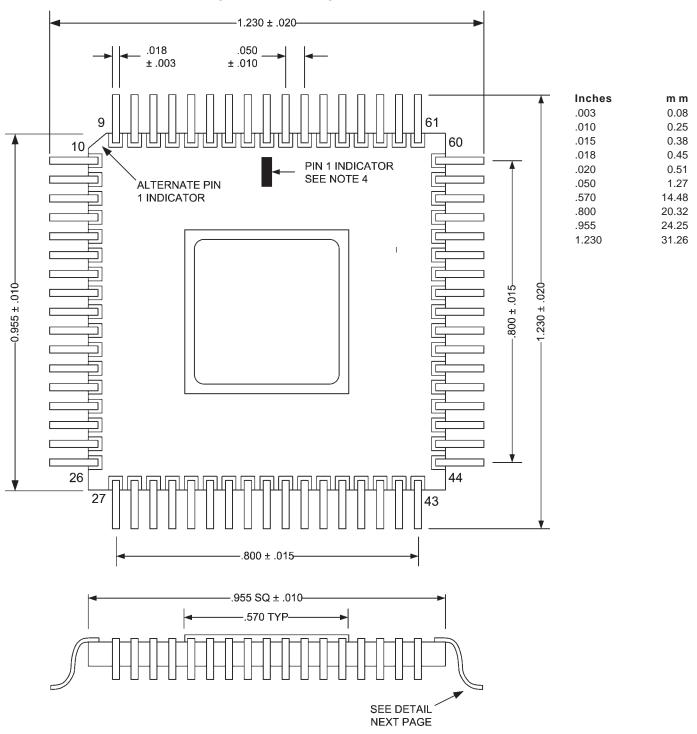

#### **CASE OUTLINE 2:**

68 Lead Quad Pack with Gullwing Leads (Ordering Code QG)

#### NOTES:

- 1) Dimensions are in inches.

- 2) Metric equivalents are given for general information only.

- 3) Unless otherwise specified, tolerances are .02 (0.5 mm) for two place decimals and .005 (0.13 mm) for three place decimals.

- 4) Pin 1 indicator can either be rectangle, dot, or triangle at specified location or referenced to the uniquely beveled corner.

- 5) Corners indicated as notched my be either notched or square (with radius).

- 6) Case 2 is derived from Case 1 by forming the leads to the shown gullwing configuration.

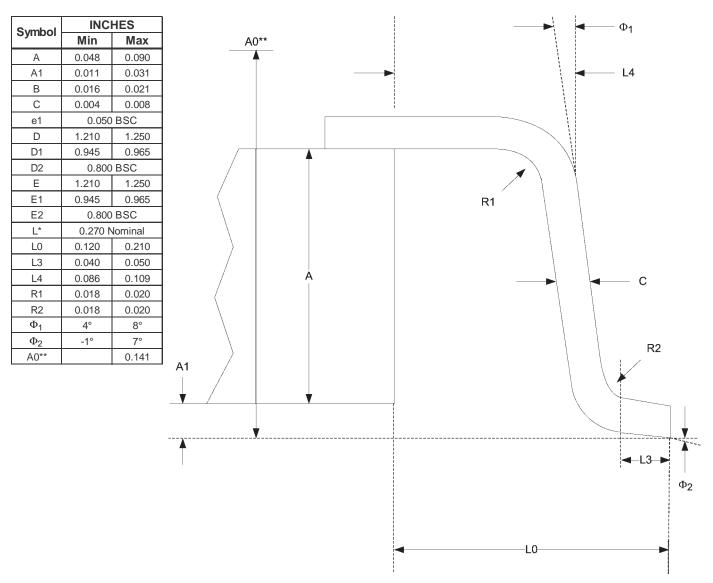

#### **LEAD FORM DETAIL**

<sup>\*</sup> Lead length in the straight lead configuration, prior to leadforming (used for all test and in-process WIP operations).

<sup>\*\*</sup> Measured from the highest of the top of the leads or the top of the lid.

#### **REVISIONS**

| DOCUMENT NUMBER:MICRO-9DOCUMENT TITLE:PACE175 |               |                    | 54/SOS MMU/COMBO              |

|-----------------------------------------------|---------------|--------------------|-------------------------------|

| REV.                                          | ISSUE<br>DATE | ORIG. OF<br>CHANGE | DESCRIPTION OF CHANGE         |

| ORIG                                          | May-89        | RKK                | New Data Sheet                |

| А                                             | Jul-04        | JDB                | Added Pyramid logo            |

| В                                             | Aug-05        | JDB                | Re-created electronic version |