#### 2.5V 512K × 32/36 pipeline burst synchronous SRAM

#### **Features**

- Organization: 524,288 words x 32/36 bits

- Fast clock speeds to 200MHz in LVTTL/LVCMOS

- Fast clock to data access: 3.0/3.5/4.0 ns

- Fast  $\overline{OE}$  access time: 3.0/3.5/4.0 ns

- Fully synchronous register-to-register operation

- Single register "Flow-through" mode

- Dual-cycle deselect

- Single-cycle deselect also available (AS7C25512PFS32A/ AS7C25512PFS36A)

- Pentium® \* compatible architecture and timing

- Asynchronous output enable control

- 100-pin TQFP package

- 119-Ball BGA (7 x 17 Ball Grid Array Package)

- Byte write enables

- Multiple chip enables for easy expansion

- 2.5V core power supply

- 2.5V I/O operation

- NTD<sup>TM\*</sup> pipeline architecture available (AS7C25512NTD32A/ AS7C25512NTD36A)

- \* Pentium<sup>®</sup> is a registered trademark of Intel Corporation. NTD<sup>TM</sup> is a trademark of Alliance Semiconductor Corporation. All trademarks mentioned in this document are the property of their respective owners.

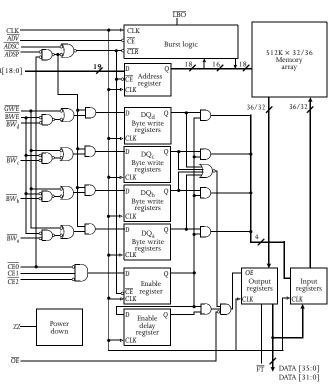

## Logic Block Diagram

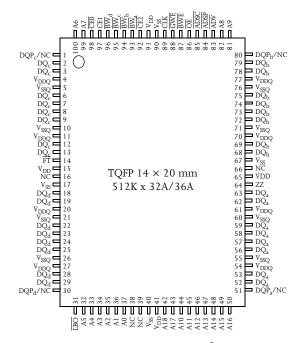

### Pin Arrangements:

Note: Pins 1,30,51,80 are NC for  $\times$ 32

| Selection guide                     | -200 | -166 | -100 | Units |

|-------------------------------------|------|------|------|-------|

| Minimum cycle time                  | 5    | 6    | 10   | ns    |

| Maximum clock frequency             | 200  | 166  | 100  | MHz   |

| Maximum pipelined clock access time | 3.0  | 3.5  | 4.0  | ns    |

| Maximum operating current           | 280  | 230  | 150  | mA    |

| Maximum standby current             | 100  | 70   | 50   | mA    |

| Maximum CMOS standby current (DC)   | 30   | 30   | 30   | mA    |

# Pin Configuration

119 BGA Top View

|   | 1                  | 2                 | 3               | 4                 | 5                 | 6    | 7                  |

|---|--------------------|-------------------|-----------------|-------------------|-------------------|------|--------------------|

| A | $V_{\mathrm{DDQ}}$ | A                 | A               | ADSP              | A                 | A    | $V_{\mathrm{DDQ}}$ |

| В | NC                 | A                 | A               | ADSC              | A                 | A    | NC                 |

| С | FT                 | A                 | A               | $V_{\mathrm{DD}}$ | A                 | A    | NC                 |

| D | DQC                | DQPc              | $V_{SS}$        | NC                | $V_{SS}$          | DQpb | DQb                |

| E | DQC                | DQc               | V <sub>SS</sub> | CE0               | V <sub>SS</sub>   | DQb  | DQb                |

| F | $V_{\mathrm{DDQ}}$ | DQc               | V <sub>SS</sub> | ŌĒ                | V <sub>SS</sub>   | DQb  | $V_{\mathrm{DDQ}}$ |

| G | DQC                | DQc               | BWc             | ADV               | BWb               | DQb  | DQb                |

| Н | DQC                | DQc               | V <sub>SS</sub> | GWE               | V <sub>SS</sub>   | DQb  | DQb                |

| J | $V_{\mathrm{DDQ}}$ | $V_{\mathrm{DD}}$ | NC              | $V_{\mathrm{DD}}$ | NC                | VDD  | $V_{\mathrm{DDQ}}$ |

| K | DQd                | DQd               | $V_{SS}$        | CLK               | VSS               | DQa  | DQa                |

| L | DQd                | DQd               | BWd             | NC                | BWa               | DQa  | DQa                |

| M | $V_{\mathrm{DDQ}}$ | DQd               | V <sub>SS</sub> | BWE               | V <sub>SS</sub>   | DQa  | $V_{\mathrm{DDQ}}$ |

| N | DQd                | DQd               | $V_{SS}$        | A1                | V <sub>SS</sub>   | DQa  | DQa                |

| P | DQd                | DQpd              | V <sub>SS</sub> | A0                | V <sub>SS</sub>   | DQPa | DQa                |

| R | NC                 | A                 | LBO             | $V_{\mathrm{DD}}$ | $V_{\mathrm{DD}}$ | A    | NC                 |

| T | NC                 | NC                | A               | A                 | A                 | NC   | ZZ                 |

| U | $V_{\mathrm{DDQ}}$ | TMS               | TDI             | TCK               | TDO               | NC   | $V_{\mathrm{DDQ}}$ |

Note: For P/N AS7C25512PFD32A, 4 of the I/O Pins must be left open (N.C.)

10/3/01; v.0.9.1

#### **Alliance Semiconductor**

2 of 2

© Copyright Alliance Semiconductor Corporation. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights, mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems impl