# 1 MEGABIT (128K x 8) REGISTERED/BUFFERED/ LATCHED CMOS STATIC RAM SUBSYSTEMS

## **FEATURES:**

- High-density 1024K-bit (128K x 8-bit) CMOS static RAM modules with registered/buffered/latched addresses and I/Os

- · High-speed registered access time:

- Military temperature range: 60ns (max.)

- Commercial temperature range: 50ns (max.)

- 20MHz read cycle time

- Low power consumption (typ.)

- Active: 1.5W

- Standby: 75mW

- Low input capacitance (typ.): input 20pF; output 25pF

- High output drive (min.): loL = 48mW; loH = -15mA

- Available in 64-pin, 900 mil centre sidebraze DIP (with LCCs on both sides), achieving very high memory density

- Module select output

- Separate inputs and outputs

- Clear data and clock enables on all registers

- Address, input and outputs on separate clocks or latch enables

- · Registered write enable

- Internal bypass capacitors for minimizing power supply noise

- TTL-compatible; single 5V (±10%) power supply

- Five GND pins for maximum noise immunity, five Vcc pins

- Military grade module available with semiconductor components compliant to the latest revision of MIL-STD-883, Class B

## **DESCRIPTION:**

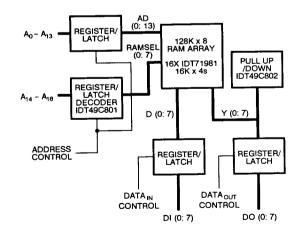

The IDT7M824 family is a set of 1024K-bit (128K x 8-bit) high-speed CMOS static RAM modules with registered/buffered/latched addresses and I/Os. They are constructed on co-fired, multi-layered ceramic substrates with sidebrazed leads using 16 IDT71981 (16K x 4) static RAMs, IDT logic devices and decoupling capacitors. Devices in leadless chip carriers are mounted top and bottom for maximum density.

Extremely high speeds are achievable by the use of IDT71981s and logic devices fabricated in IDT's high-performance, high-reliability CEMOS ™ technology. This state-of-the-art technology, combined with innovative circuit design techniques, provides the fastest circuits possible. The IDT7M824 has registered access times of 50ns (max.) over the commercial temperature range and can be operated with cycle times as fast as 20MHz.

Designing with this device can be very flexible because of such features as module select output and clock enables on all registers, registered write enable and 8-bit separate inputs and outputs. Because of the proprietary IDT49C801, the modules are cascadable in terms of depth with no additional external decoding. The write enable can be turned off when the module is deselected. Immunity to noise has been extended with such features as 8-bit separate inputs and outputs; addresses, inputs, and outputs on separate clocks; internal decoupling capacitors; five ground pins and five Vcc pins.

The semiconductor components used on all IDT military modules are manufactured in compliance with the latest revision of MIL-STD-883, Class B, making them ideally suited to applications demanding the highest level of performance and reliability.

# **FUNCTIONAL BLOCK DIAGRAM**

## PRODUCT SELECTOR GUIDE

|                | _ ,,                                      | I/O AND ADDRESS FEATURES |  |  |  |

|----------------|-------------------------------------------|--------------------------|--|--|--|

| ADDRESS<br>BUS | INPUT<br>DATA BUS                         | OUTPUT<br>DATA BUS       |  |  |  |

| L/B            | L/B                                       | L/B                      |  |  |  |

| L/B            | R                                         | R                        |  |  |  |

| L/B            | R                                         | L/B                      |  |  |  |

| L/B            | L/B                                       | R                        |  |  |  |

| R              | R                                         | R                        |  |  |  |

| R              | R                                         | L/B                      |  |  |  |

| R              | L/B                                       | R                        |  |  |  |

| R              | L/B                                       | L/B                      |  |  |  |

|                | L/B<br>L/B<br>L/B<br>L/B<br>L/B<br>R<br>R | BUS                      |  |  |  |

## NOTES:

- 1. L/B = LATCHED/BUFFERED R = REGISTERED

- For module dimensions, please refer to module drawing M8 in the packaging section.

CEMOS is a trademark of Integrated Device Technology, Inc.

**MILITARY AND COMMERCIAL TEMPERATURE RANGES**

**DECEMBER 1987**

© 1987 Integrated Device Technology, Inc

13-168

DSC-7000/-

### **PIN NAMES**

| NAME                                                  | DESCRIPTION                                    |  |  |

|-------------------------------------------------------|------------------------------------------------|--|--|

| A <sub>0</sub> - A <sub>16</sub>                      | Addresses                                      |  |  |

| DI <sub>0</sub> - DI <sub>7</sub>                     | Data input                                     |  |  |

| DO <sub>0</sub> - DO <sub>7</sub>                     | Data output                                    |  |  |

| CLRDIN                                                | Data input clear                               |  |  |

| CPDIN/LEDIN                                           | Data input register clock/latch enable         |  |  |

| ENDIN/PREDIN                                          | Data input register clock enable/latch preset  |  |  |

| OE, OE, OE,                                           | Output enable                                  |  |  |

| CPDOUT/LEDOUT                                         | Data output register clock/latch enable        |  |  |

| ENDOUT/PREDOUT                                        | Data output register clock enable/latch preset |  |  |

| CS <sub>1</sub> , CS <sub>2</sub> , & CS <sub>3</sub> | Chip select                                    |  |  |

| WE                                                    | Write enable                                   |  |  |

| SEL                                                   | Select output                                  |  |  |

| LE/CP                                                 | Latch enable/clock pulse control input         |  |  |

| CE/GND                                                | Clock enable/ground                            |  |  |

| REG/LAT                                               | Register/latch (low active) input control      |  |  |

| Vcc                                                   | Power                                          |  |  |

| GND                                                   | Ground                                         |  |  |

## CAPACITANCE (TA = +25°C, f = 1.0MHz)

| SYMBOL           | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |

|------------------|--------------------|-----------------------|------|------|

| CIN              | Input Capacitance  | V <sub>IN</sub> = 0V  | 20   | рF   |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 25   | pF   |

#### NOTE:

1. This parameter is sampled and not 100% tested.

# **ABSOLUTE MAXIMUM RATINGS (1)**

| SYMBOL            | RATING                                     | COMMERCIAL MILITARY     |             | UNIT |  |

|-------------------|--------------------------------------------|-------------------------|-------------|------|--|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 -0.5 to +7 |             | ٧    |  |

| T <sub>A</sub>    | Operating<br>Temperature                   | 0 to +70 -55 to +125    |             | ů    |  |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -55 to +125             | -65 to +135 | °C   |  |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to + 125            | -65 to +150 | °C   |  |

| lour              | DC Output Current                          | 120                     | 120         | mA   |  |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

13

# DC ELECTRICAL CHARACTERISTICS

Following Conditions Apply Unless Otherwise Specified:  $V_{CC} = 5.0V \pm 10\%$ T<sub>A</sub> = -55°C to + 125°C

Min. = 4.50V

Max. = 5.50V (Military)

$V_{LC} = 0.2V$  $V_{HC} = V_{CC} - 0.2V$

| SYMBOL           | PARAMETER                          | TEST CONDITIONS (1)                                                            |                                | MIN.            | TYP. <sup>(2)</sup> | MAX.            | UNIT |

|------------------|------------------------------------|--------------------------------------------------------------------------------|--------------------------------|-----------------|---------------------|-----------------|------|

| V <sub>H</sub>   | Input HIGH Level                   | Guaranteed Logic High Level                                                    |                                | 2.0             | -                   |                 | V    |

| V <sub>IL</sub>  | Input LOW Level                    | Guaranteed Logic Low Level                                                     |                                |                 |                     | 0.8             | V    |

|                  | Input HIGH Current                 | V <sub>CC</sub> = Max., V <sub>IN</sub> = V <sub>CC</sub>                      |                                |                 |                     | 5               | μА   |

| I <sub>IH</sub>  | Input LOW Current                  | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND                                  |                                |                 |                     | -5              | μA   |

| <u> </u>         | Short Circuit Current              | V <sub>CC</sub> = Max. <sup>(3)</sup>                                          |                                | -60             | -120                | -               | mA   |

| lsc              | Short Singuit Similar              | $V_{CC} = 3V$ , $V_{IN} = V_{LC}$ or $V_{HC}$ , $I_{OH} = -32\mu A$            |                                | V <sub>HC</sub> | V <sub>CC</sub>     |                 |      |

|                  |                                    |                                                                                | I <sub>OH</sub> = -300µA       | V <sub>HC</sub> | Vcc                 | _               | V    |

| V <sub>OH</sub>  | Output HIGH Voltage                | $V_{CC} = Min.$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                        | I <sub>OH</sub> = -12mA MIL.   | 2.4             | 4.3                 |                 |      |

|                  |                                    |                                                                                | I <sub>OH</sub> = -15mA COM'L. | 2.4             | 4.3                 |                 |      |

|                  |                                    | $V_{CC} = 3V, V_{IN} = V_{LC} \text{ or } V_{HC}, I_{OL} = 300 \mu\text{A}$    |                                | -               | GND                 | V <sub>LC</sub> |      |

|                  | V <sub>OL</sub> Output LOW Voltage | V <sub>CC</sub> = Min.<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> | l <sub>OL</sub> = 300µA        | _               | GND                 | V <sub>LC</sub> | l v  |

| VoL              |                                    |                                                                                | loL = 32mA MIL.                | T -             | <u> </u>            | 0.4             |      |

|                  |                                    |                                                                                | I <sub>OL</sub> = 48mA COM'L.  | _               |                     | 0.5             |      |

| l <sub>CC1</sub> | Operating Power Supply Current     | CS = V <sub>IL</sub> V <sub>CC</sub> = Max., Output Open f = 0                 |                                | _               | 300                 | 600             | mA   |

| I <sub>CC2</sub> | Dynamic Operating Current          | CS = V <sub>IL</sub> V <sub>CC</sub> = Max., Output Open f = f <sub>MAX</sub>  |                                | _               | 320                 | 650             | mA   |

| I <sub>SB</sub>  | Standby Power Supply Current       | $CS \ge V_{H}$ $V_{CC} = Max$ . Output Open, $f = f_{MAX}$                     |                                |                 | 15                  | 330             | mA   |

## NOTES:

2. Typical values are at  $V_{CC} = 5.0V$ , +25 °C ambient and maximum loading.

<sup>1.</sup> For conditions shown as max, or min., use appropriate value specified under Electrical Characteristics for the applicable device type.

<sup>3.</sup> Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

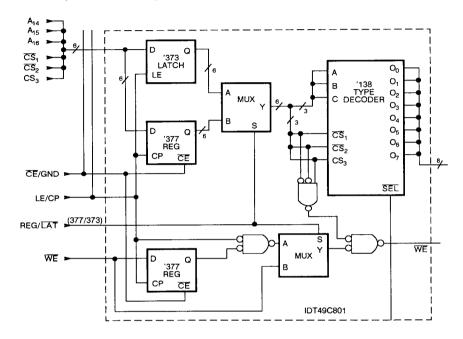

#### IDT49C801

# REGISTERED/LATCHED DECODER

The IDT49C801 is a proprietary IDT gate array that includes a 138-type 1-of-8 decoder, as well as latches and registers for all inputs and controls for WRITE ENABLE (WE). The latch or register mode is controlled by a single input, REG/LAT.

With the IDT49C801 in the Latch mode, the three address and the three chip select inputs are latched by a 373-type latch. When LE is high, the latch is transparent and, when LE goes low, all data

that meets the required set-up time is latched. The  $\overline{WE}$  input is not latched but it is gated by the result of the three chip select inputs. With the IDT49C801 in the Register mode, the three address and chip select inputs are registered by a 377-type register. All data that meets the set-up time requirements before the rising edge of CP will be transferred to the output of the register provided Clock Enable ( $\overline{CE}$ ) is asserted. In this mode,  $\overline{WE}$  is also registered but the output of its register is gated with CP so that when CP goes low, the output of  $\overline{WE}$  is applied to the RAMs.

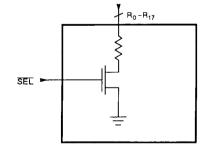

#### IDT49C802

#### UNIVERSAL PULL-UP/DOWN RESISTORS

The IDT49C802 is a proprietary gate array that has 18 selectable pull-up or pull-down resistors, only eight of which are used on

these parts. The purpose of the pull-down resistor, as used in these parts, is to prevent the RAM DO pins from floating when the RAM array is deselected. When the RAM array is selected, the pull-down resistor is inhibited. The value of the resistors is approximately  $15K\Omega$ .

13