3033-1.3 November 1991

# MCT83100 Series

## MIL-STD-1553B STANAG 3838 REMOTE TERMINAL UNIT

(Supersedes H10401FUG all versions)

The MCT83100 series is a range of complete dual redundant MIL-STD-1553B (STANAG 3838) Remote Terminal Units with an easy to use processor interface. Each device comprises two low power transceivers, a monolithic Remote Terminal (RT) protocol device, a memory control device, and a 4K x 16 bit double buffered dual port RAM, all in a single co-fired ceramic package. Additionally four MSI devices buffer the Initialise Word and make available the 1553B Command Word

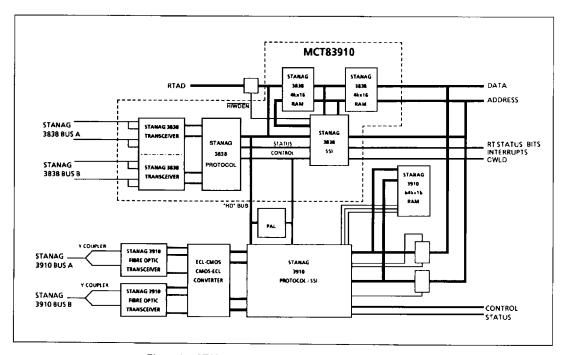

The MCT83910 thru MCT83912 are identical to the MCT83100 series except that the four MSI devices are omitted. This makes available the internal highway (HD0-15) allowing STANAG 3910 Action and Status Words to be transferred. A number of control lines are also available to provide a means of interfacing to the internal highway.

## **FEATURES**

- Single package device providing comprehensive remote terminal 1553B interface compatibility with most processing systems/devices

- Integral Transceivers

- Integral 4K x 16 Bit Fully Double Buffered Dual Port Static RAM Devices

- All MIL-STD-1553B Data Words are Memory Mapped, so providing a minimum of Software and Hardware overheads

- Separate Data Buffering for Broadcast Commands (in accordance with MIL-STD-1553B Notice 2)

- Contains full memory contention resolution and control

- Provides powerful built in test features initiated either by Host Subsystems or via the 1553B Data Highway

- Integral Illegal Command Monitoring

- Low Power Dissipation

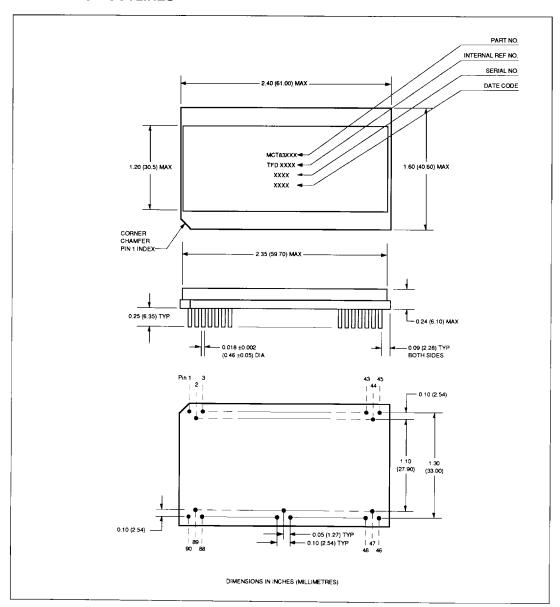

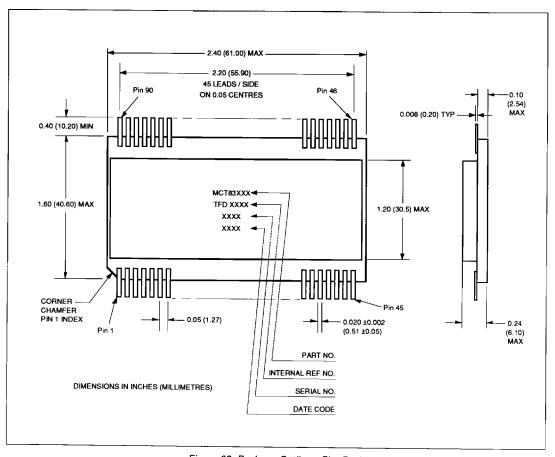

- 90 Pin Quad In Line or Flat Pack Package 2.4 x 1.6 Inches (61 x 41mm)

- Can be configured to operate in either 16 Bit or 8 Bit

Mode

- Operates over the full Military Temperature Range (-55°C to +125°C)

| Device     | Transceiver Voltages | RAM Options (k) |

|------------|----------------------|-----------------|

| MCT83102   | -15, +5              | 4               |

| MCT83102-3 | ±15, +5              |                 |

| MCT83103   | -12, +5              | 4               |

| MCT83103-3 | ±12, +5              |                 |

| MCT83105   | +5                   | 4               |

| MCT83910   | -15, +5              | 4+3910 l/F      |

| MCT83910-3 | ±15, +5              |                 |

| MCT83911   | -12, +5              | 4+3910 I/F      |

| MCT83911-3 | ±12, +5              |                 |

| MCT83912   | +5                   | 4+3910 I/F      |

#### Notes:

- 1. Package size: 2.4"x1.6" (61mmx41mm)

- 2. RAM Access Time: 100ns

- Refer to Customer Services for availability of MCT83102, 83103, 83910, 83911

Table 1: MCT83100 Series

## **GENERAL DESCRIPTION**

Each of the MCT83100 series of devices provides an intelligent, fully double buffered interface between either a single or a dual redundant 1553B data bus and any 16-bit or 8-bit based CPU. The interface appears to a host CPU as a 4kx16-bit area of static RAM into which all 1553B transfers are memory mapped. A host CPU has access to the memory at all time. Only complete, valid messages will be presented to, or transmitted from the CPU.

All of the 1553B RT options are implemented by the MCT83100 series of devices. These along with a number of software and hardware programmable interface options provide a high degree of operational flexibility. A Message Error input is provided in order that any number of broadcast-T/R-subaddress-word count combinations may be declared illegal. The devices also allow a host CPU to make use of the 1553B reserved status bits and mode commands if required in specialist applications.

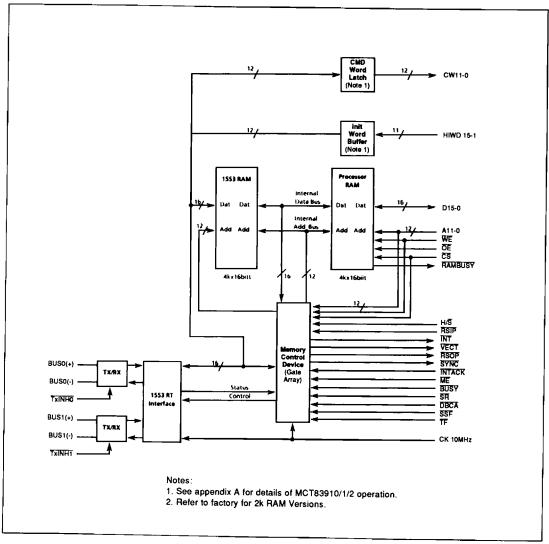

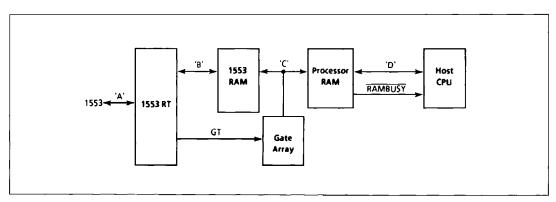

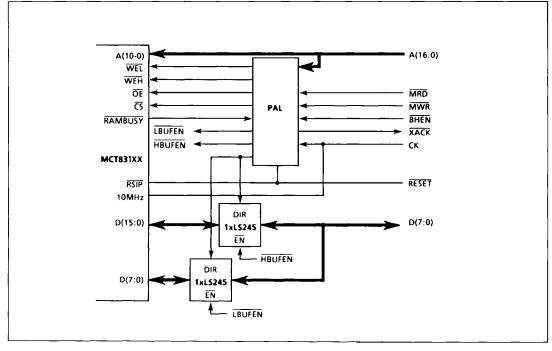

Figure 1: MCT83102 Block Diagram

## 1. FUNCTION

Figure 1 is a block diagram of the MCT83102 (4k x 16-bit RAM version), the device can be seen to contain the following functions:-

- 1. Two 1553B transceivers.

- A 1553B RT protocol device.

- A 4k x 16-bit area of dual port RAM accessed by the host CPU referred to as the "Processor RAM".

- A 4k x 16-bit area of dual port RAM accessed by the 1553B protocol device referred to as the "1553 RAM".

- A gate array responsible for memory contention resolution and control.

- 6. Two output latches which contain the latest Command

- Two input buffers which buffer the devices Initialise Word.

Mil-Std-1553B Command and Data words are received by the transceivers and validated by the 1553 RT protocol device. The 1553 protocol device accesses the left hand side (LHS) of the "1553 RAM". The host CPU has access to the right hand side (RHS) of the "Processor RAM". The gate array performs data transfers between the RAMs.

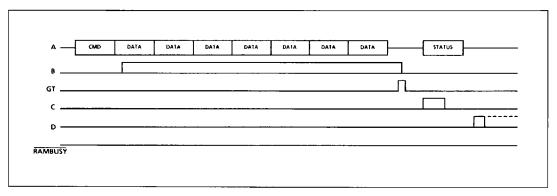

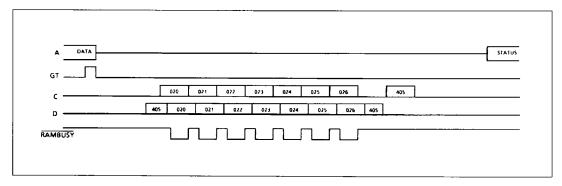

After reception of a 1553 receive Command Word followed contiguously by receive data, the 1553 protcol device stores the data in the "1553 RAM". The data is memory mapped using the 1553 Command Word subaddress bits. Upon message validation the 1553 protocol device transmits a Status Word then instructs the gate array to transfer the data from the "1553 RAM" to the "Processor RAM". This transfer may be prevented by the host CPU writing the subaddress value of the data into location 405 (hex) - the Receive Access Control word (RACWd).

The 1553 protocol device will always store receive data in the "1553 RAM" irrespective of the RACWd contents. The gate array compares the RACWd value with the subaddress in the command word after message validation. If the RACWd value matches the subaddress then the "1553 RAM" to "Processor RAM" data transfers will be delayed until the RACWd contents are altered. If the RACWd value does not match the subaddress then the "1553 RAM" to "Processor RAM" data transfer takes place immediately.

In order to read a receive message, the host CPU merely writes the appropriate subaddress value of the data into the RACWd, then reads the data in ascending order, before clearing the RACWd to zero.

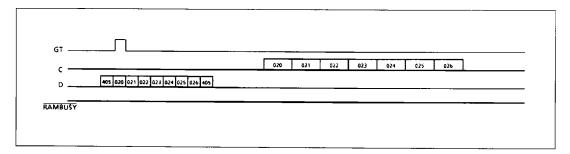

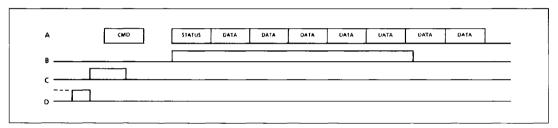

Transmit data is stored in the "Processor RAM" by the host CPU. Once the message is complete the host CPU instructs the gate array to transfer the message to the "1553 RAM". The transfer is initiated by the host CPU writing the expected transmit Command Word into either location 406 (hex) or location 407 (hex) - Transfer Control Words 0 and 1 (TCWd). When the 1553 protocol device decodes a transmit Command Word it transmits a Status Word followed by the required number of Data Words - which it reads from the "1553 RAM".

Upon completion of a "Processor RAM" to the "1553 RAM" data transfer the gate array clears the relevant TCWd. The host CPU must not write to a TCWd that has not been cleared. The "Processor RAM" to the "1553 RAM" data transfer may be delayed by up to 640µs if the 1553 protocol device is performing a transmit command using the same subaddress value as contained in the TCWd. Hence a second TCWd is provided.

In order to update a transmit message, the host CPU writes the transmit data into the "Processor RAM". When the message is complete the host CPU interrogates the TCWds in order to ascertain which is clear, before writing the expected transmit command word value into that TCWd.

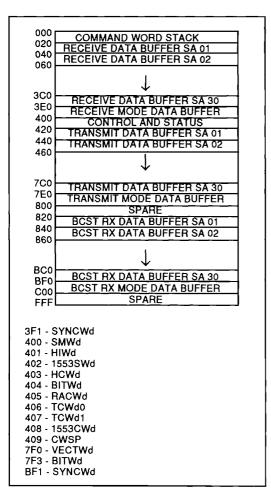

It is intended that the host CPU views the 83100 interface merely as a block of RAM, hence all Command, Control, Status and Data Words are memory mapped within the 4k boundary. 4k RAM is provided in order that Data Words associated with broadcast commands may be stored independently of non-broadcast data. Figure 5 details the MCT83102 memory architecture.

A 12-bit latched Command Word output and a message error Status Word input are provided in order to allow Command Words to be illegalised with the minimum of external hardware. All 1553B defined illegal commands are automatically illegalised without the addition of external hardware. Four interrupt outputs and six 1553 Status Word inputs are provided should they be required. A further group of eleven inputs is also provided in order to allow the host CPU designer to hard-wire the Hybrid Initialise word.

## 2. SIGNAL DESCRIPTIONS

| Pin | Name                | Dir | Logic |                                                  | Description                                                                                                                                                                                                           |                                                  |  |  |  |

|-----|---------------------|-----|-------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|--|

| 1   | BUS1(+)             | 1/0 | 1553B | Positive thres                                   | shold exceeded bus 1                                                                                                                                                                                                  |                                                  |  |  |  |

| 2   | BUS1(-)             | I/O | 1553B | Negative thre                                    | shold exceeded bus 1                                                                                                                                                                                                  | _                                                |  |  |  |

| 3   | V <sub>EE</sub> (1) | I/P | -     | -15V/-12V su                                     | 5V/-12V supply to bus 1 transceiver (see note 3) (HIGH CURRENT                                                                                                                                                        |                                                  |  |  |  |

| 4   | V <sub>DD</sub> (1) | I/P | -     | +15V/+12V/+                                      | +15V/+12V/+5V supply to bus 1 transceiver (see note 4) (HIGH CURRENT)                                                                                                                                                 |                                                  |  |  |  |

| 5   | ٥V                  | I/P |       | 0V return for                                    | all supplies                                                                                                                                                                                                          |                                                  |  |  |  |

| 6   | V <sub>CC</sub>     | I/P | -     | +5V supply (s                                    | see note 5)                                                                                                                                                                                                           |                                                  |  |  |  |

| 7   | TP1                 | O/P | -     | Factory use of                                   | only                                                                                                                                                                                                                  |                                                  |  |  |  |

| 8   | TP2                 | O/P | -     | Factory use of                                   | only                                                                                                                                                                                                                  |                                                  |  |  |  |

| 9   | TXINHI              | I/P | T2    | Active low bu                                    | ow bus 1 transmitter inhibit (open circuit enables transmitter) (note 3)                                                                                                                                              |                                                  |  |  |  |

| 10  | H/S                 | I/P | C2    | 401 (hex) of t                                   | ng this input to logic 0 will cause the HIWd to be defined by location of the 1553B RAM. Leaving this input open circuit will cause the HIWd ned by the HI15-1 inputs.                                                |                                                  |  |  |  |

| 11  | 10MHz               | l/P | C3    | 10MHz clock                                      | input. Note: clock must have a mark/space ra                                                                                                                                                                          | tio of 1:1±10%                                   |  |  |  |

| 12  | RSIP                | I/P | C2    | This input mu                                    | This input must be held to a logic 0 for 1.0 $\mu$ s after power up ie $V_{CC}=4.5V$                                                                                                                                  |                                                  |  |  |  |

| 13  | RSOP                | O/P | C1    |                                                  | This output will pulse low for nominally 300ns after reception of a valid Reset RT mode command.                                                                                                                      |                                                  |  |  |  |

| 14  | VECT                | O/P | C1    |                                                  | This output will pulse low for nominally 300ns after reception of a valid<br>Transmit Vector Word mode command.                                                                                                       |                                                  |  |  |  |

| 15  | SYNC                | O/P | C1    | Synchronise                                      | This output will pulse low for nominally 300ns after reception of a valid<br>Synchronise Without Data mode command and after reception of a valid<br>Synchronise With Data mode command if bit 14 of the HCWd is set. |                                                  |  |  |  |

| 16  | ĪNT                 | O/P | C1    | will go low un                                   | on of a valid command (if the relevant HCWd<br>ntil INTACK is taken to logic 0. If INTACK is co<br>will pulse low for nominally 300ns.                                                                                |                                                  |  |  |  |

| 17  | INTACK              | I/P | C2    |                                                  | nput to a logic 0 will cause the INT output to r<br>Minimum INT pulse width is nominally 300ns.                                                                                                                       |                                                  |  |  |  |

| 18  | HI15                | I/P | T2    | RTAD4                                            |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 19  | HI14                | I/P | T2    | RTAD3                                            |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 20  | HI13                | I/P | T2    | RTAD2                                            |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 21  | HI12                | I/P | T2    | RTAD1                                            | These inputs define the device's HIWd if the                                                                                                                                                                          | e H/S input is open                              |  |  |  |

| 22  | HI11                | I/P | T2    | RTAD0                                            | circuit or at logic 1. The HIWd is only loade                                                                                                                                                                         | d into the 1553 RT                               |  |  |  |

| 23  | HI10                | I/P | T2    | RTADPAR                                          | Interface device either on the low-to- high to<br>RTON bit in the HCWd or upon reception of                                                                                                                           |                                                  |  |  |  |

| 24  | H19/8               | I/P | 2xT2  | BCST                                             | mode command. The bit allocation of the H                                                                                                                                                                             |                                                  |  |  |  |

| 25  | HI7                 | I/P | T2    | FLAGOP                                           | table 3                                                                                                                                                                                                               |                                                  |  |  |  |

| 26  | НІЗ                 | I/P | T2    | TM1                                              |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 27  | HI2                 | I/P | T2    | TMO                                              |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 28  | HI1                 | I/P | T2    | ĀBR                                              |                                                                                                                                                                                                                       |                                                  |  |  |  |

| 29  | RAMWEH              | I/P | RA    | Pulsing this in<br>the "Processo<br>by the A11-0 | nput with RAMCS low will cause the most sigror RAM" (D 15-8) to be written to. Note: The a inputs.                                                                                                                    | nificant eight bits of<br>ddress will be defined |  |  |  |

| 30  | RAMWEL              | I/P | RW    | of the "Proce                                    | nput low with RAMCS low will cause the least<br>ssor RAM" (D7-0) to be written to. Note: in 8 b<br>precede a pulse on RAMWEH.                                                                                         | significant eight bits<br>bit mode a pulse on    |  |  |  |

#### Notes

- 1. Logic types (RB, RD etc) are described in the Electrical Characteristics section.

- 2. A bar indicates an active low level signal.

- 3. Connection to this pin is not required on MCT83105 and MCT83912.

- Refer to Table 1 for the connection of the appropriate voltage to this pin. For MCT83102, 83103, 83910,83911 this

pin is open circuit.

- 5. Logic supply and with the exception of MCT83105 and MCT83912 it is also the +5V supply to the transceiver.

| Pin | Name    | Dir | Logic | Description                                                                                                                                                                                                          |

|-----|---------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | RAMOE   | I/P | RW    | Setting this input low whilst RAMCS is low will allow the device's "Processor RAM" to be read.                                                                                                                       |

| 32  | RAMCS   | I/P | C2    | Setting this input low will allow access to the "Processor RAM".                                                                                                                                                     |

| 33  | A11     | I/P | RA    |                                                                                                                                                                                                                      |

| 34  | A10     | I/P | RA    |                                                                                                                                                                                                                      |

| 35  | A9      | I/P | RA    |                                                                                                                                                                                                                      |

| 36  | A8      | I/P | RA    |                                                                                                                                                                                                                      |

| 37  | A7      | I/P | RA    | These inputs form the address bus of the "Processor RAM"                                                                                                                                                             |

| 38  | A6      | I/P | RA    | '                                                                                                                                                                                                                    |

| 39  | A5      | I/P | RA    |                                                                                                                                                                                                                      |

| 40  | A4      | I/P | RA    |                                                                                                                                                                                                                      |

| 41  | A3      | I/P | RA    |                                                                                                                                                                                                                      |

| 42  | A2      | I/P | RA    |                                                                                                                                                                                                                      |

| 43  | A1      | I/P | RA    |                                                                                                                                                                                                                      |

| 44  | A0      | I/P | RA    |                                                                                                                                                                                                                      |

| 45  | οV      | I/P | -     | 0V return for all supplies                                                                                                                                                                                           |

| 46  | CASE    | I/P | -     | Case connection                                                                                                                                                                                                      |

| 47  | RAMBUSY | O/P | RB    | This output will go active low if both the host CPU and the gate array attempt to access the same location in the "Processor RAM". Note: The host CPU must not access the MCT83100 RAM whilst this output is active. |

| 48  | D15     | 1/0 | RD    |                                                                                                                                                                                                                      |

| 49  | D14     | 1/0 | RD    |                                                                                                                                                                                                                      |

| 50  | D13     | 1/0 | RD    |                                                                                                                                                                                                                      |

| 51  | D12     | I/O | RD    |                                                                                                                                                                                                                      |

| 52  | D11     | I/O | RD    |                                                                                                                                                                                                                      |

| 53  | D10     | I/O | RD    |                                                                                                                                                                                                                      |

| 54  | D9      | 1/0 | RD    |                                                                                                                                                                                                                      |

| 55  | D8      | I/O | RD    |                                                                                                                                                                                                                      |

| 56  | D7      | I/O | RD    | These 16 bi-directional lines form the data bus connections to the "Processor RAM".                                                                                                                                  |

| 57  | D6      | 1/0 | RD    |                                                                                                                                                                                                                      |

| 58  | D5      | I/O | RD    |                                                                                                                                                                                                                      |

| 59  | D4      | I/O | RD    |                                                                                                                                                                                                                      |

| 60  | D3      | I/O | RD    |                                                                                                                                                                                                                      |

| 61  | D2      | 1/0 | RD    |                                                                                                                                                                                                                      |

| 62  | D1      | I/O | RD    |                                                                                                                                                                                                                      |

| 63  | D0      | 1/0 | RD    |                                                                                                                                                                                                                      |

## Notes:

- 1. Logic types (RB, RD etc) are described in the Electrical Characteristics section.

- 2. A bar indicates an active low level signal.

- 3. Connection to this pin is not required on MCT83105 and MCT83912.

- 4. Refer to Table 1 for the connection of the appropriate voltage to this pin. For MCT83102, 83103, 83910,83911 this pin is open circuit.

- 5. Logic supply and with the exception of MCT83105 and MCT83912 it is also the +5V supply to the transceiver.

Table 2: Signal Descriptions (continued)

| Pin | Name                | Dir | Logic | Description                                                                                                                                                       |  |  |  |  |  |

|-----|---------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 64  | CW11                | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 65  | CW10                | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 66  | CW9                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 67  | CW8                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 68  | CW7                 | O/P | T1    | These 12 outputs hold the last valid Command Word received by the device These lines are updated 2.5µs before the on-board 1553B Status Word latel                |  |  |  |  |  |

| 69  | CW6                 | O/P | T1    | up dated prior to transmission.  CW11 will be a logic 1 after reception of a broadcast command and a logic 0                                                      |  |  |  |  |  |

| 70  | CW5                 | O/P | T1    | after a non-broadcast command. Note: these outputs allow the host CPU to                                                                                          |  |  |  |  |  |

| 71  | CW4                 | O/P | T1    | decode the <u>Co</u> mmand Word and then set the 1553B Message Error bit by driving the ME input to logic 0, so illegalising the command                          |  |  |  |  |  |

| 72  | CW3                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 73  | CW2                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 74  | CW1                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 75  | CW0                 | O/P | T1    |                                                                                                                                                                   |  |  |  |  |  |

| 76  | ME                  | I/P | C2    | Setting this input to a logic 0 will cause the Message Error bit to be set in subsequent 1553B Status Word transmissions. Note: Data transfers will be prevented. |  |  |  |  |  |

| 77  | SR                  | I/P | C2    | Setting this input to a logic 0 will cause the Service Request bit to be set in subsequent 1553B Status Word transmissions                                        |  |  |  |  |  |

| 78  | BUSY                | I/P | C2    | Setting this input to a logic 0 will cause the Busy bit to be set in subsequent 1553B Status Word transmissions. Note: Data Transfers will be prevented.          |  |  |  |  |  |

| 79  | SSF                 | I/P | C2    | Setting this input to a logic 0 will cause the Subsystem Flag bit to be set in subsequent 1553B Status Word transmissions.                                        |  |  |  |  |  |

| 80  | DBCA                | I/P | C2    | Setting this input to a logic 0 will cause the Dynamic Bus Control Accept bit to be set in response to Dynamic Bus Control mode commands.                         |  |  |  |  |  |

| 81  | TF                  | I/P | C2    | Setting this input to a logic 0 will cause the Terminal Flag bit to be set in subsequent 1553B Status Word transmissions.                                         |  |  |  |  |  |

| 82  | TXINH0              | I/P | T2    | Active low bus 0 transmitter inhibit. Open circuit enables transmitter) (Note 3).                                                                                 |  |  |  |  |  |

| 83  | TP4                 | O/P | _     | Factory use only                                                                                                                                                  |  |  |  |  |  |

| 84  | TP3                 | O/P | -     | Factory use only                                                                                                                                                  |  |  |  |  |  |

| 85  | V <sub>CC</sub>     | I/P | -     | +5V supply (see note 5)                                                                                                                                           |  |  |  |  |  |

| 86  | ov                  | I/P | -     | 0V return for all supplies                                                                                                                                        |  |  |  |  |  |

| 87  | V <sub>DD</sub> (0) | I/P | -     | +15V/+12V/+5V supply to bus 0 transceiver. (See note 4) (HIGH CURRENT)                                                                                            |  |  |  |  |  |

| 88  | V <sub>EE</sub> (0) | I/P | -     | -15V/-12V supply to bus 0 transceiver. (See note 3) (HIGH CURRENT)                                                                                                |  |  |  |  |  |

| 89  | BUS0(-)             | 1/0 | 1553B | Negative threshold exceeded bus 0.                                                                                                                                |  |  |  |  |  |

| 90  | BUS0(+)             | 1/0 | 1553B | Positive threshold exceeded bus 0.                                                                                                                                |  |  |  |  |  |

#### Notes

- 1. Logic types (RB, RD etc) are described in the Electrical Characteristics section.

- 2. A bar indicates an active low level signal.

- 3. Connection to this pin is not required on MCT83105 and MCT83912.

- 4. Refer to Table 1 for the connection of the appropriate voltage to this pin. For MCT83102, 83103, 83910,83911 this pin is open circuit.

- 5. Logic supply and with the exception of MCT83105 and MCT83912 it is also the +5V supply to the transceiver.

Table 2: Signal Descriptions (continued)

## 3. RECOMMENDED OPERATING CONDITIONS

## 3.1 MCT83102, MCT83910 -15V Device

| Parameter/Condition                                                                                            | Symbol | Min    | Тур   | Max    | Unit |

|----------------------------------------------------------------------------------------------------------------|--------|--------|-------|--------|------|

| Power Supply Voltages                                                                                          | VEE    | -14.25 | -15.0 | -15.75 | V    |

|                                                                                                                | VCC    | 4.5    | 5.0   | 5.5    | , V  |

| Supply Current - Standby mode, ie. less than 1%                                                                | IEE    | •      | 1     | 3      | mΑ   |

| duty cycle (Note 1 applies)                                                                                    | ICC    | •      | 237   | 540    | mΑ   |

| Supply Current transmitting at 1MHz into $35\Omega$ load at point A of Fig.2 - 25% duty cycle (Note 2 applies) | IEE25  | -      | 41    | 45     | mA   |

| Supply current transmitting at 1MHz into 35Ω load at point A of Fig.2 - 100% duty cycle (Note 2 applies)       | IEE100 | -      | 166   | 185    | mA   |

| Power dissipation of most critical device during continuous transmission (Note 3 applies)                      | PC     | 1      | 155   | 160    | mW   |

| Thermal Resistance of most critical device                                                                     | θJC    | -      | -     | 60     | °C/W |

| Operating Temperature Range (case)                                                                             | TOP    | -55    | -     | 125    | ပ္စ  |

| Storage Temperature Range                                                                                      | TST    | -65    | -     | 150    | ç    |

| Power Dissipation at less than 1% duty cycle                                                                   | Р      |        | 1.19  | 2.97   | 8    |

| Power Dissipation at 25% duty cycle                                                                            | P25    | •      | 1.38  | 3.17   | W    |

| Power Dissipation at 100% duty cycle                                                                           | P100   |        | 1.96  | 4.20   | W    |

## Notes:

- 1. <sub>CC</sub> limits do not change with duty cycle

2. Decreases linearly to applicable 'standby' value at zero duty cycle

- 3. Decreases linearly to zero at zero duty cycle.

Table 3: Recommended Operating Conditions - MCT83102, MCT83910

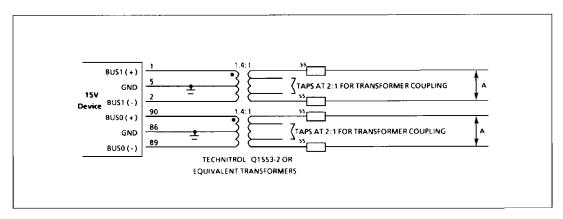

Figure 2: Bus Connections for 15V Devices

## 3.2 MCT83102-3, MCT83910-3 ±15V Devices

| Parameter/Condition                                                                                             | Symbol | Min    | Тур   | Max    | Unit |

|-----------------------------------------------------------------------------------------------------------------|--------|--------|-------|--------|------|

|                                                                                                                 | _VDD_  | +14.25 | +15.0 | +15.75 |      |

| Power Supply Voltages                                                                                           | VEE    | -14.25 | -15.0 | -15.75 | V    |

|                                                                                                                 | VCC    | 4.5    | 5.0   | 5.5    | ٧    |

| Supply Current - Standby mode, ie. less than 1%                                                                 | _IDD   | -      | 30    | 44     | mA   |

| duty cycle (Note 1 applies)                                                                                     | IEE    | -      | 50    | 70     | mΑ   |

|                                                                                                                 | CC     | -      | 237   | 540    | mĀ   |

| Supply Current transmitting at 1 MHz into $35\Omega$ load at point A of Fig.2 - 25% duty cycle (Note 2 applies) | IDD25  | •      | 70    | 100    | mA   |

| Supply current transmitting at 1MHz into 35Ω load at point A of Fig.2- 100% duty cycle (Note 2 applies)         | IDD100 | -      | 200   | 260    | mA   |

| Power dissipation of most critical device during continuous transmission (Note 3 applies)                       | PC     | -      | 350   | 500    | mW   |

| Thermal Resistance of most critical device                                                                      | θJC    | · -    |       | 60     | °C/W |

| Operating Temperature Range (case)                                                                              | TOP    | -55    | -     | 125    | °C   |

| Storage Temperature Range                                                                                       | TST    | -65    |       | 150    | °C   |

| Power Dissipation at less than 1% duty cycle                                                                    | Ρ_     | -      | 2.40  | 4.75   | W    |

| Power Dissipation at 25% duty cycle                                                                             | P25    | -      | 2.60  | 5.25   | W    |

| Power Dissipation at 100% duty cycle                                                                            | P100   | -      | 4.35  | 6.90   | W    |

#### Notes:

- 1.  $I_{CC}$  and  $I_{EE}$  limits do not change with duty cycle 2. Decreases linearly to applicable 'standby' value at zero duty cycle

- 3. Decreases linearly to zero at zero duty cycle

Table 4: Recommended Operating Conditions - MCT83102-3, MCT83910-3

## 3.3 MCT83103, MCT83911 -12V Device

| Parameter/Condition                                   | Symbol | Min   | Тур   | Max   | Unit |

|-------------------------------------------------------|--------|-------|-------|-------|------|

| Power Supply Voltages                                 | VEE    | -11.4 | -12.0 | -12.6 | ٧    |

|                                                       | VCC    | 4.5   | 5.0   | 5.5   | V    |

| Supply Current - Standby mode, ie.less than 1%        | IEE    |       | 1     | 3     | mA   |

| duty cycle (Note 1 applies)                           | ICC    |       | 237   | 540   | mA   |

| Supply Current transmitting at 1 MHz into 35Ω load    | IEE25  | -     | 64    | 68    | mA   |

| at point A of Fig.3 - 25% duty cycle (Note 2 applies) |        |       |       |       |      |

| Supply Current transmitting at 1 MHz into 35Ω load    |        |       |       |       |      |

| at point A of Fig.3 - 100% duty cycle (Note 2         | IEE100 | -     | 231   | 254   | mA   |

| applies)                                              |        |       |       |       |      |

| Power dissipation of most critical device during      | PC     | -     | 230   | 250   | mW   |

| continuous transmission (Note 3 applies)              |        |       |       |       |      |

| Thermal Resistance of most critical device            | θJC    | -     | -     | 60    | °C/W |

| Operating Temperature Range(case)                     | TOP    | -55   | -     | 125   | °C   |

| Storage Temperature Range                             | TST    | -65   | -     | 150   | °C   |

| Power Dissipation at less than 1% duty cycle          | Р      | -     | 1.19  | 2.97  | W    |

| Power Dissipation at 25% duty cycle                   | P25    | -     | 1.56  | 3 23  | W    |

| Power Dissipation at 100% duty cycle                  | P100   | -     | 2.24  | 4.6   | W    |

## Notes:

- I. I<sub>CC</sub> limits do not change with duty cycle

Decreases linearly to applicable 'standby' value at zero duty cycle

- 3. Decreases linearly to zero at zero duty cycle

Table 5: Recommended Operating Conditions - MCT83103, MCT83911

## 3.4 MCT83103-3, MCT83911-3 ±12V Devices

| Parameter/Condition                                                                                       | Symbol | Min   | Тур   | Max    | Unit |

|-----------------------------------------------------------------------------------------------------------|--------|-------|-------|--------|------|

|                                                                                                           | VDD    | +11.4 | +12.0 | +12.6  | V    |

| Power Supply Voltages                                                                                     | VEE    | -11.4 | -12.0 | -12.6_ | V    |

|                                                                                                           | VCC_   | 4.5   | 5.0   | 5.5    | V    |

| Supply Current - Standby mode, ie. less than 1%                                                           | IDD_   | •     | 30    | 44     | mA   |

| duty cycle (Note 1 applies)                                                                               | IEE    |       | 50    | 70     | mA   |

|                                                                                                           | ICC    |       | 237   | 540    | mA   |

| Supply Current transmitting at 1 MHz into 35Ω load at point A of Fig.3 - 25% duty cycle (Note 2 applies)  | IDD25  | -     | 85    | 120    | mA   |

| Supply Current transmitting at 1 MHz into 35Ω load at point A of Fig.3 - 100% duty cycle (Note 2 applies) | 1DD100 | -     | 240   | 315    | mA   |

| Power dissipation of most critical device during continuous transmission (Note 3 applies)                 | PC     | •     | 350   | 500    | mW   |

| Thermal Resistance of most critical device                                                                | θJC    | F -   | -     | 60     | °C/W |

| Operating Temperature Range(case)                                                                         | TOP    | -55   | -     | 125    | °C   |

| Storage Temperature Range                                                                                 | TST    | -65   |       | 150    | ç    |

| Power Dissipation at less than 1% duty cycle                                                              | P      | -     | 2.15  | 4.40   | W    |

| Power Dissipation at 25% duty cycle                                                                       | P25    | -     | 2.40  | 4.90   | W    |

| Power Dissipation at100% duty cycle                                                                       | P100   | -     | 3.06  | 7.20   | W    |

- 1. I<sub>CC</sub> and I<sub>EE</sub> limits do not change with duty cycle or mode of operation 2. Decreases linearly to applicable 'standby' value at zero duty cycle 3. Decreases linearly to zero at zero duty cycle

Table 6: Recommended Operating Conditions - MCT83103-3, MCT83911-3

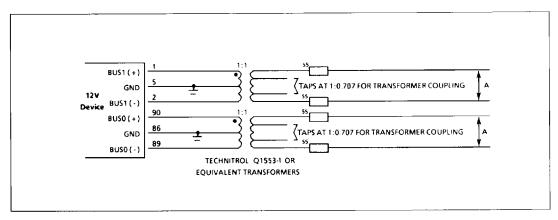

Figure 3: Bus Connections for 12V Devices

## 3.5 MCT83105, MCT83912 +5V Devices

| Parameter/Condition                                                                                      | Symbol | Min_ | Тур  | Max          | Unit |

|----------------------------------------------------------------------------------------------------------|--------|------|------|--------------|------|

| Power supply voltages                                                                                    | VDD    | 4.5  | 50   | 55           | ٧    |

|                                                                                                          | VCC    | 4.5  | 5.0  | 5.5          | ٧    |

| Supply Current - Standby mode(ie. less than 1%                                                           | IDD    | •    | 100  | 1 <u>5</u> 0 | mΑ   |

| duty cycle (Note 1 applies)                                                                              | ICC    |      | 137  | 390          | mA   |

| Supply Current transmitting at 1 MHz into 35Ω load at point A of Fig.4 - 25% duty cycle (Note 2 applies) | IDD25  | •    | 230  | 293          | mA   |

| Supply Current transmitting at 1MHz into 35Ω load at point A of Fig.4 - 100% duty cycle (Note2 applies)  | IDD100 | -    | 620  | 720          | mA   |

| Power dissipation of most critical device during continuous transmission (Note 3 applies)                | PC     | -    | 260  | 320          | mW   |

| Thermal Resistance of most critical device                                                               | θJC    | -    | -    | 60           | °C/W |

| Operating Temperature Range(case)                                                                        | TOP    | -55  |      | 125          | °C   |

| Storage Temperature Range                                                                                | TST _  | -65  | •    | 150          | °C   |

| Power Dissipation at less than 1%duty cycle                                                              | Р      |      | 1.19 | 2.97         | W    |

| Power Dissipation at 25% duty cycle                                                                      | P25    |      | 1.45 | 3.28         | W    |

| Power Dissipation at 100% duty cycle                                                                     | P100   |      | 2.24 | 4.50         | W    |

#### Notes

- 1. I<sub>CC</sub> limits do not change with duty cycle

- 2. Decreases linearly to applicable 'standby' value at zero duty cycle

- 3. Decreases linearly to zero at zero duty cycle

Table 7: Recommended Operating Conditions - MCT83105, MCT83912

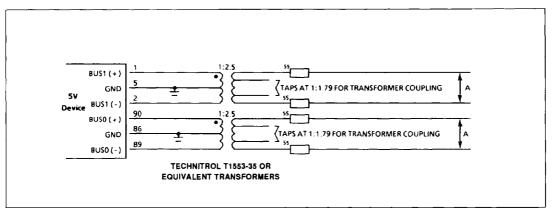

Figure 4: Bus Connections for +5V Device

## **GUIDELINES FOR USE**

## A) Decoupling

Decouple V<sub>DD</sub> to ground close to the hybrid.

A parallel capacitor combination of a 100nF ceramic and a  $10\mu$ F (or greater) tantalum is recommended. Note: The peak transmission current drawn from  $V_{DD}$  is of the order of 650mA.

## B) Board Layout

- Full PCB ground-planing is recommended.

- The connections between the Bus lines and the transformer should be balanced in terms of length, shape and area, and designed to:

- (i) Withstand peak transmission current at worst case operational duty cycle.

- (ii) Minimise added series inductance.

- (iii) Ensure that the input impedance of the hybrid with its associated transformer does not fall below the minimum requirements of MIL-STD-1553B.

## 4. ABSOLUTE MAXIMUM RATINGS

| Parameter                                                            | Device                                               | Limits          |

|----------------------------------------------------------------------|------------------------------------------------------|-----------------|

| Power Supply Voltage (V <sub>EE</sub> )                              | All except<br>MCT83105<br>MCT83912                   | +0.3V to -18V   |

| Power Supply Voltage (V <sub>CC</sub> )                              | All                                                  | -0.3V to +7V    |

| Power Supply Voltage (V <sub>DD</sub> )                              | MCT83102-3<br>MCT83103-3<br>MCT83910-3<br>MCT83911-3 | -0.3V to +18V   |

|                                                                      | MCT83105<br>MCT83912                                 | -0.3V to +7V    |

| Receiver Differential Input<br>Pin 1 or Pin 2, and Pin 90 or Pin 89  | Ail                                                  | ±20V (40V p-p)  |

| Receiver Input Voltage<br>Pin 1 or Pin 2, and Pin 90 or Pin 89       | All                                                  | ±15V            |

| Logic Input Voltages                                                 | All                                                  | -0.3V to +5.5V  |

| Transmitter Output Peak Current Pin 1 to Pin 2, and Pin 90 to Pin 89 | MCT83102<br>MCT83102-3<br>MCT83910<br>MCT83910-3     | 200mA           |

|                                                                      | MCT83103<br>MCT83103-3<br>MCT83911<br>MCT83911-3     | 300mA           |

|                                                                      | MCT83105<br>MCT83912                                 | 800mA           |

| Transmission Duty Cycle at T <sub>CASE</sub> = 125°C                 | All                                                  | 100%            |

| Operating Case Temperature Range (T <sub>OP</sub> )                  | All                                                  | -55°C to +125°C |

| Storage Temperature Range (T <sub>ST</sub> )                         | All                                                  | -65°C to +150°C |

Table 8: Absolute Maximum Ratings

## 5. ELECTRICAL CHARACTERISTICS

Note: All max/min values are for worst case operating conditions, where appropriate. at -55°C to +125°C

| Label | Description                          | Min | Тур | Max | Unit |

|-------|--------------------------------------|-----|-----|-----|------|

| VOH   | Output High Level Voltage(IOH=-1μA)  | 4.0 | •   | •   | V    |

| VOL   | Output Low Level Voltage (IOL = 4mA) | -   | -   | 0.4 | ٧    |

Table 9a: Output Type - C1

| Label | Description                           | Min | Тур | Max | Unit |

|-------|---------------------------------------|-----|-----|-----|------|

| VOH   | Output High Level Voltage(IOH≂ -20µA) | 4.0 |     |     | V    |

| VOL   | Output Low Level Voltage(IOL = 4mA)   | -   | -   | 0.4 | ٧    |

Table 9b: Output Type - T1

| Label | Description                            | Min | Тур | Max | Unit |

|-------|----------------------------------------|-----|-----|-----|------|

| VOH   | Output High Level Voltage (IOH = -4mA) | 2.4 |     |     | V    |

| VOL   | Output Low Level Voltage (IOL = 4mA)   |     | -   | 0.5 | ٧    |

Table 9c:0utput Type - RB

| Label | Description                            | Min | Тур | Max  | Unit     |

|-------|----------------------------------------|-----|-----|------|----------|

| VOH   | Output High Level Voltage (IOH = -4mA) | 2.4 |     | -    | V        |

| VOL   | Output Low Level Voltage (IOL = 4mA)   |     |     | 0.5  | V        |

| VIH   | Input High Level Voltage               | 2.2 | -   | •    | V        |

| VIL   | Input Low Level Voltage                | •   | •   | 0.7  | <b>V</b> |

| ILI   | Input Leakage Current                  |     | -   | 30.0 | μA       |

| ILO   | Output Leakage Current                 | · - |     | 30.0 | μA       |

Table 9d: Input/Output - RD

| Labei | Description              | Min | Тур | Max | Unit |

|-------|--------------------------|-----|-----|-----|------|

| VIH   | Input High Level Voltage | 2.0 | •   | VC  | V    |

| VIL   | Input Low Level Voltage  | •   | •   | 0.7 | ٧    |

| IIH   | Input High Level Current | •   | ,   | -20 | μA   |

| HL    | Input Low Level Current  | -   |     | 200 | μA   |

Table 9e: Input Type - C2 (CMOS I/P with 50kΩ pull up)

| Label | Description              |     | Тур | Max | Unit |

|-------|--------------------------|-----|-----|-----|------|

| VIH   | Input High Level Voltage | 2.0 | •   | VCC | V    |

| VIL   | Input Low Level Voltage  | •   | •   | 0.7 | V    |

| IIH   | Input High Level Current | •   |     | 100 | μА   |

| IIL   | Input Low Level Current  | •   | -   | 1.5 | mA   |

Table 9f: Input Type - T2 (CTTL I/P with 10KΩ)

| Label | Description              | min | Тур | max | unit       |

|-------|--------------------------|-----|-----|-----|------------|

|       | Input High Level Voltage | 2.0 | -   | VCC | V          |

|       | Input Low Level Voltage  | -   | •   | 0.7 | V          |

| 11.1  | Input Leakage Current    | -   |     | 20  | μ <b>A</b> |

Table 9g: Input Type - C3

| Label | Description              | Min | Тур | Max | Unit |

|-------|--------------------------|-----|-----|-----|------|

| VIH   | Input High Level Voltage | 2.0 |     | VCC | V    |

| VIL   | Input Low Level Voltage  | -   | •   | 0.7 | V    |

| 11.1  | Januat Lookaga Current   | -   | -   | 60  | μA   |

Table 9h: Input Type - RA

| Label | Description              | min | Тур | max | unit |

|-------|--------------------------|-----|-----|-----|------|

| VIH   | Input High Level Voltage | 2.0 |     | VCC |      |

| VIL   | Input Low Level voltage  | -   |     | 0.7 |      |

| 11.1  | Input Leakage Current    | -   |     | 40  | μA   |

Table 9i: Input Type - RW

| Parameter/Condition                                                                                                            |      | Symbol | Min  | Тур | Max    | Unit         |

|--------------------------------------------------------------------------------------------------------------------------------|------|--------|------|-----|--------|--------------|

| Differential input impedance DC to 1 MHz<br>(Transmitter Inhibited)                                                            |      | Zin    | 2K   | ,   | -<br>- | Ω            |

| Input differential voltage range                                                                                               |      | Vidr   | ±20  | •   | -      | Vpeak        |

| Input common mode voltage range up to 2MHz (line to ground)                                                                    |      | Vicr   | ±10  |     | -      | Vpeak        |

| Common mode rejection ratio                                                                                                    |      | CMRR   | 40   |     | -      | dB           |

| Threshold characteristics - sinewaye at 1MHz                                                                                   |      | Vth1   | 0.75 | 1.0 | 1.2    | Vp-p         |

| Filter characteristics                                                                                                         | 2MHz | Vth2   | 1.5_ |     | 8.0    | <b>V</b> p-р |

|                                                                                                                                | 3MHz | Vth3   | 5    |     | -      | Vp-р         |

| Differential output noise                                                                                                      |      | Vnoi   | -    |     | 10     | mVp-p        |

| Differential output level (e.g. at point A of Fig.2)                                                                           |      | Vo     | 6    | •   | 9      | Vp-р         |

| Rise and fall times (10-90%)                                                                                                   |      | Tr     | 100  | 160 | 300    | ns           |

| Output Offset at 2.5µs after mid-bit crossing of the parity bit of the last word of a 660µs message (e.g. at point A of Fig.2) |      | Vos    | -    | ±20 | ±75    | mVpk         |

Table 9j: Transceiver Characteristics - For Direct Coupled Operation

## 6. MEMORY ARCHITECTURE

The memory can be divided into eight distinct areas:-

- 1. Command Word Stack.

- 2. Receive Data Buffer.

- 3. Receive Mode Data Buffer.

- 4. Control and Status Area.

- 5. Transmit Data Buffers.

- 6. Transmit Mode Data Buffers.

- 7. Broadcast Receive Data Buffer.

- 8. Broadcast Mode Receive Data Buffer.

Figure 5: Memory Architecture

## 6.1 Command Word Stack

Locations 000 - 01F(hex) form the 32 word Command Word Stack. The device will store every valid, legal, logical command (except Transmit Status Word and Transmit Last Command Word mode commands) received in this circular stack. The bit allocation of the words on the Command Word Stack is listed on Table 10.

| Bit | Name   | Description                                                                                        |

|-----|--------|----------------------------------------------------------------------------------------------------|

| 0   | WC0    | Word Count bit 0                                                                                   |

| 1   | WC1    | Word Count bit 1                                                                                   |

| 2   | WC2    | Word Count bit 2                                                                                   |

| 3   | WC3    | Word Count bit 3                                                                                   |

| 4   | WC4    | Word Count bit 4                                                                                   |

| 5   | SA0    | Subaddress 0                                                                                       |

| 6   | SA1    | Subaddress 1                                                                                       |

| 7   | SA2    | Subaddress 2                                                                                       |

| 8   | SA3    | Subaddress 3                                                                                       |

| 9   | SA4    | Subaddress 4                                                                                       |

| 10  | T/R    | Transmit/Receive bit                                                                               |

| 11  | BCST   | Broadcast Command Detected -<br>Logic 1 indicates reception of a Broadcast<br>command              |

| 12  | ZERO   | Logic 0                                                                                            |

| 13  | ZERÔ   | Logic 0                                                                                            |

| 14  | ZERO   | Logic 0                                                                                            |

| 15  | NEWCMD | New Stack Command Word -<br>This bit may be cleared by the host CPU after<br>servicing the command |

Table 10: Stack Command Word

#### 6.2 Receive Data Buffers

Locations 020 - 3DF (hex) form the 30 Receive Data Buffers. Each buffer consists of 32 sixteen bit words and is allocated to each of the receive subaddress values excluding 00 and 1F (hex). Upon validation of a non-mode receive command and message the device will store the Data Words in the Receive Data Buffer indicated by the subaddress bits in the Command Word. The host CPU is able to delay this storing process by writing the appropriate subaddress value into the Receive Access Control Word (RACWd) in the Control and Status Area.

## 6.3 Receive Mode Data Buffer

Locations 3E0 - 3FF (hex) form the Receive Mode Data Buffer. This buffer is used to store the Data Words associated with receive mode commands irrespective of the subaddress bits being set to 00 or 1F (hex) e.g. Location 3F1 (hex) will contain the Data Word associated with a Synchronise with Data Word mode command.

## 6.4 Transmit Data Buffers

Locations 420-7DF (hex) form the Transmit Data Buffers. Each of these 30 buffers contains 32 sixteen bit words. As in the Receive Data Buffers each buffer is allocated a subaddress value. After the host CPU writes to either of the Transfer Control Words (TCWds) the gate array will transfer the indicated number of data words from the appropriate Transmit Data Buffer in the "Processor RAM" to the "1553 RAM". Upon reception of a non-mode transmit command the device will transmit the Data Words stored in the buffer indicated by the Command Word subaddress value.

## 6.5 Transmit Mode Data Buffers

Locations 7E0-7FF (hex) form the Transmit Mode Data Buffers. This buffer is used to store the Data Words associated with Transmit Mode Commands eg: Location 7F0 (hex) contains the 1553B Vector Word Location 7F3 (hex) contains the BITWd set up by the host CPU if bit 1 of the HIWd is set.

Note: Use of a TCWd is required to transfer these words from the "Processor RAM" to the "1553 RAM".

## 6.6 Broadcast Receive Data Buffer

Locations 820-BFF (hex) form the Broadcast Receive Data Buffers. These data buffers are used to store the Data Words associated with broadcast receive commands. As in the Receive Data Buffers each buffer is allocated a subaddress value.

# 6.7 Broadcast Receive Mode Data Buffer

Locations BE0-BFF (hex) form the Broadcast Receive Mode Data Buffers. This buffer is used to store the Data Words associated with broadcast mode receive commands irrespective of the subaddress bits being set to 00 or 1F (hex) eg: Location BF1 (hex) will contain the Data Word associated with a broadcast Synchronise with Data Word mode command.

## 6.8 Control and Status Area

Locations 400 - 41F form the Control and Status area. This area consists of ten words associated with the host CPU's monitoring and control of the device's operation.

## 6.8.1 Status Modifier Word

The Status Modifier Word (SMWd) is located at address 400 (hex), it allows the host CPU a high degree of control over the 1553B Status Word bits. In order to alter the state of the 1553B Status Word this word must be set to the appropriate, value then 0400 (hex) must be written into either of the Transfer Control Words. The bit allocation of the Status Modifier Word is listed in Table 11.

The 1553B Status Word Bits are set as a result of a logical 'OR' of the Status Modifier Word bits and the hardware status inputs (pins 76, 77, 78, 79, 80, 81).

In order to set a 1553B Status Word bit (eg Service Request) either set pin 77 to logic zero or write BFFF (hex) into address 400 (hex) then write 0400 (hex) into either of the Transfer Control Words.

| Bit | Name     | Description                                                                                                                           |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Not Used | Set to one                                                                                                                            |

| 1   | Not Used | Set to one                                                                                                                            |

| 2   | Not Used | Set to one                                                                                                                            |

| 3   | ALLÓW    | Allows reserved mode commands to be declared legal.                                                                                   |

| 4   | SETINST  | Sets the Instrumentation bit of the 1553B<br>Status Word                                                                              |

| 5   | SETRES5  | Sets bit 5 ot the 1553B Status Word                                                                                                   |

| 6   | SETRES6  | Sets bit 6 ot the 1553B Status Word                                                                                                   |

| 7   | SETRES7  | Sets bit 7 ot the 1553B Status Word                                                                                                   |

| 8   | SETDBCA  | Sets the Dynamic Bus Control Accept bit in<br>the 1553B Status Word transmitted in<br>response to Dynamic Bus Control mode<br>command |

| 9   | INHTF    | Inhibits the Terminal Flag bit in the 1553B<br>Status Word from being set.                                                            |

| 10  | INHSSF   | Inhibits the Subsystem Flag bit in the 1553B<br>Status Word from being set.                                                           |

| 11  | SETTF    | Sets the Terminal Flag bit in the 1553B Status<br>Word                                                                                |

| 12  | SETSSF   | Sets the Subsystem Flag bit in the 1553B<br>Staus Word                                                                                |

| 13  | SETBUSY  | Sets the Busy bit in the 1553B Status Word                                                                                            |

| 14  | SETSERV  | Sets the Service Request bit in the 1553B<br>Status Word                                                                              |

| 15  | SETME    | Sets the Message Error bit in the 1553B Staus<br>Word                                                                                 |

Note: All of the SMWd bits are active low.

Table 11: Status Modifier Word

## 6.8.2 Hybrid Initialise Word

The Hybrid Initialise Word (HIWd) is located at address 401 (hex), it allows the host CPU to configure the device for a particular application. An option to make this word 'hard-wired' is selectable by leaving the H/S input open circuit. In order to alter the state of the device Initialise Word the following sequence must be performed:

- 1. Set RTON bit in Hybrid Control Word to zero

- 2. Write 0403 into address 406/407

- 3. Set Hybrid Initialise Word to appropriate value

- 4. Write 0401 into address 406/407

- 5. Set RTON bit in Hybrid Control Word to one

- 6. Write 0403 into address 406/407

#### Notes:

- 1. All addresses and data in hex.

- 2. If H/S input is open circuit then 4. can be omitted.

- It is recommended that HIS be left open circuit and only the 'hard-wired' HIWd be used.

- The bit allocation of the Hybrid Initialise Word is listed in Table 12.

| Bit | Name      | Description                                                                                               |

|-----|-----------|-----------------------------------------------------------------------------------------------------------|

| 0   | Logic One | Set to one                                                                                                |

| 1   | ĀBR       | When low selects contents of 7F3 (hex) as<br>Data Word Associated with Transmit Bit<br>Word mode commands |

| 2   | TMO       | Timeout multiplier bit 0 (see note 1)                                                                     |

| 3   | TM1       | Timeout multiplier bit 1 (see note 1)                                                                     |

| 4   | Logic One | Set to one                                                                                                |

| 5   | Logic One | Set to one                                                                                                |

| 6   | Logic One | Set to one                                                                                                |

| 7   | FLAGOP    | Subsystem and Terminal Flag setting option (see note 2)                                                   |

| 8   | BCSTEN0   | When high enables the broadcast address on bus 0                                                          |

| 9   | BCSTEN1   | When high enables the broadcast address on bus 1                                                          |

| 10  | RTADPAR   | Remote Terminal address parity bit (see note 3)                                                           |

| 11  | RTAD0     | Remote Terminal address bit 0                                                                             |

| 12  | RTAD1     | Remote Terminal address bit 1                                                                             |

| 13  | RTAD2     | Remote Terminal address bit 2                                                                             |

| 14  | RTAD3     | Remote Terminal address bit 3                                                                             |

| 15  | RTAD4     | Remote Terminal address bit 4                                                                             |

| Notes  |   |

|--------|---|

| INDIES | ٠ |

| 1. | TM1 | TM0 | No Response<br>Timeout (µs) |

|----|-----|-----|-----------------------------|

|    | 1   | 1   | 14 " ′                      |

|    | 1   | 0   | 31                          |

|    | 0   | 1   | 47                          |

|    | 0   | 0   | 64                          |

FLAGOP = 1 if the TF or SSF bit is set, it will remain set until some positive action is taken to clear the setting condition, ie, mode command to reset or local resetting.

FLAGOP=0 if the TF or SSF bit is set, it will remain set until one status word has been transmitted with the bit set. The TF or SSF will then reset unless the fault condition is still present (ie, SETTF or SETSSF in the SMWd are still active or pins 79 or 81 still at logic 0).

RTADPAR. This pin must be set to a state such that bits 10-15 inclusive have an odd number of bits set to logic 1, ie, an odd parity.

Table 12: Hybrid Initialise Word

## 6.8.3 1553B Status Word

Location 402 (hex) contains a copy of the 1553B Status Word associated with the last Command Word received by the device.

| Bit | Name           |                  | Description                                                              |  |  |

|-----|----------------|------------------|--------------------------------------------------------------------------|--|--|

|     |                | Set by one       | Driving pin 81 to logic 0                                                |  |  |

|     |                | of the following | SMWd bit 9 high and SMWd bit 11 low                                      |  |  |

|     |                | Ì                | 1553 Protocol device(see note 1)                                         |  |  |

| 0   | TERMINALFLAG   |                  | Status word transmission if HIWd bit 7 low and Driving pin 81 to logic 1 |  |  |

|     |                | Reset by one     | Status word transmission if HIWd bit 7 low and SMWd bit 11 high          |  |  |

|     |                | of the following | Reset RT mode command and Driving pin 81 to logic 1                      |  |  |

|     |                |                  | Reset RT mode command and SMWd bit 11 high                               |  |  |

|     |                |                  | HCWd bit 0 low                                                           |  |  |

|     |                | Set by one       | Driving pin 80 to logic 0 and Reception of a valid DBCA mode command     |  |  |

|     |                | of the following | SMWd bit 8 low and Reception of a valid DBC A mode command               |  |  |

|     |                |                  | Driving pin 80 to logic 1 and Reception of any valid command except mode |  |  |

| 1   | Dynamic Bus    |                  | commands 02 or 12 (hex).                                                 |  |  |

|     | Control Accept | Reset by one     | SMWd bit 8 high and Reception of any valid command except                |  |  |

|     |                | of the following | mode commands 02 or 12 (hex).                                            |  |  |

|     |                |                  | Reception of any valid command except mode commands 00 or 02 or 12       |  |  |

|     |                |                  | (hex)                                                                    |  |  |

|     |                |                  | HCWd bit 0 low                                                           |  |  |

|     |                | Set by one       | Driving pin 79 to logic 0                                                |  |  |

|     |                | of the following | SMWd bit 9 high and SMWd bit 11 low                                      |  |  |

|     |                |                  | Status word transmission if HIWd bit 7 low and Driving pin 79 to logic 1 |  |  |

| 2   | Subsystem Flag | Reset by one     | Status word transmission if HIWd bit 7 low and SMWd bit 12 high          |  |  |

|     |                | of the following | Reset RT mode command and Driving pin 79 to logic 1                      |  |  |

|     |                |                  | Reset RT mode command and SMWd bit 12 high                               |  |  |

|     |                |                  | HCWd bit 0 low                                                           |  |  |

|     |                | Set by one       | Driving pin 78 to logic 0                                                |  |  |

|     |                | of the following | SMWd bit 13 low                                                          |  |  |

| 3   | BUSY           | Reset by         | Driving pin 78 to logic 1                                                |  |  |

|     |                | of the following | SMWd bit 13 high                                                         |  |  |

|     |                |                  | HCWd bit 0 low                                                           |  |  |

| 4   | BROADCAST      | Set by           | 1553 Protocol device (see note 2)                                        |  |  |

|     | COMMAND REC'VD | Reset by         | Reception of any valid command except mode commands 02 or 12 (hex)       |  |  |

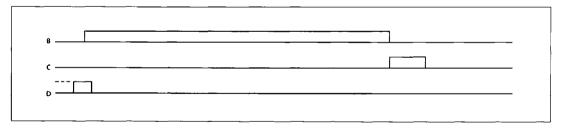

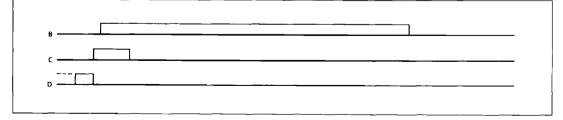

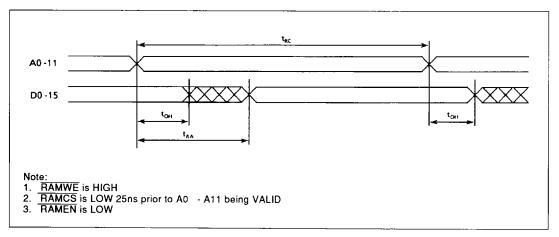

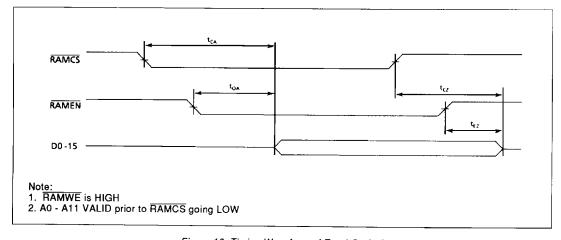

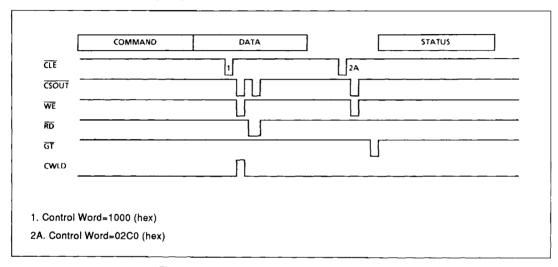

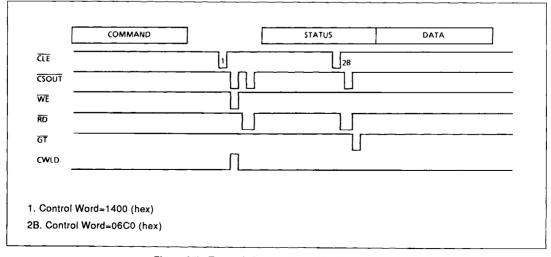

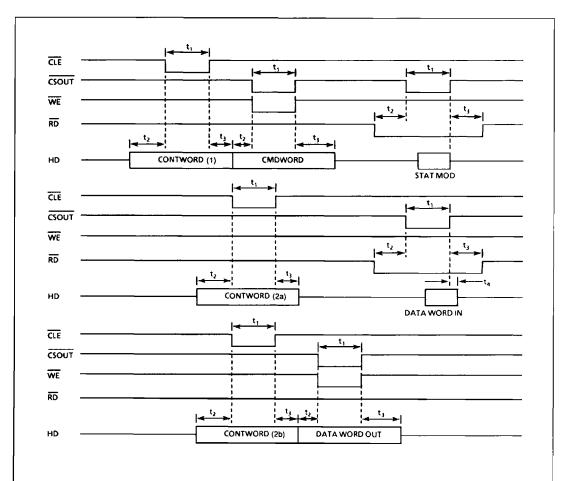

|     |                | Set by           | SMWd bit 5 low                                                           |  |  |