6.1

# **DAC8012**

# CMOS 12-Bit Multiplying DIGITAL-TO-ANALOG CONVERTER With Memory

## **FEATURES**

- DATA READBACK CAPABILITY

- FOUR-QUADRANT MULTIPLICATION

- LOW GAIN TC: 2PPM/°C typ

- MONOTONICITY GUARANTEED OVER TEMPERATURE

- SINGLE 5V TO 15V SUPPLY

- LOW OUTPUT LEAKAGE (10nA max)

- LOW OUTPUT CAPACITANCE (70pF max)

- DIRECT REPLACEMENT FOR PMI DAC8012

# **DESCRIPTION**

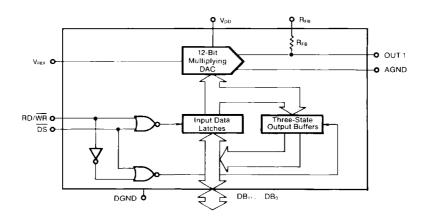

The DAC8012 is a CMOS, 12-bit, four-quadrant multiplying, digital-to-analog converter with input data latches and 3-state readback capabilities. The

input data is loaded into the DAC as a 12-bit data word. The data is loaded into the DAC from the bus when both the data strobe ( $\overline{DS}$ ) and the read/write (RD/ $\overline{WR}$ ) pins are held low. Data may be read back from the DAC by holding  $\overline{DS}$  low and (RD/ $\overline{WR}$ ) high. This readback feature enables the user to monitor the state of multiple DACs on a single bidirectional bus.

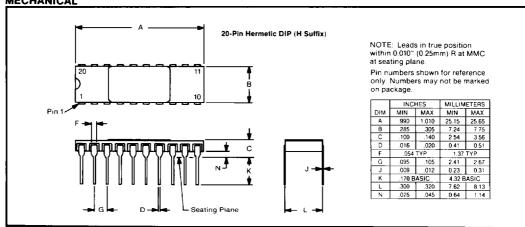

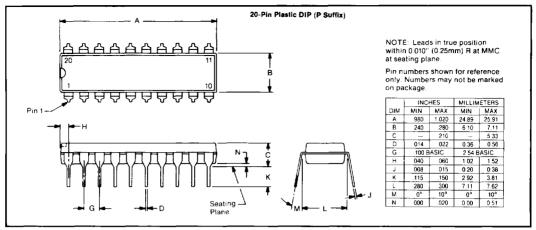

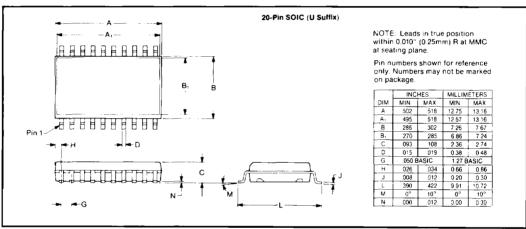

Laser-trimmed thin-film resistors and excellent CMOS voltage switches provide true 12-bit integral and differential linearity. The device operates on a single +5V to +15V supply and is available in 20-pin side-brazed DIP, 20-pin plastic DIP or a 20-lead plastic SOIC package. Devices are specified over the commercial, industrial, and military temperature ranges and are available with additional reliability screening.

International Airport Industrial Park - P.O. Box 11400 - Tucson, Arizona 85734 - Tel. (602) 746-1111 - Twx: 910-952-1111 - Cable: BBRCORP - Telex - 66-6491

# **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

$V_{REF} = +10V$ ,  $V_{OUT,1} = 0V$ , AGND = DGND = 0V unless otherwise noted.

|                                                                              |                                                                                | DA       | C8012B, K | , T <sup>(1)</sup> | DAC8012A, J, S <sup>(1)</sup> |         | , s'''    | _               |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------|-----------|--------------------|-------------------------------|---------|-----------|-----------------|

| PARAMETER                                                                    | CONDITIONS                                                                     | MIN      | TYP       | MAX                | MIN                           | TYP     | MAX       | UNITS           |

|                                                                              | V <sub>00</sub> = +5V or +15V                                                  |          | •         |                    |                               |         |           |                 |

| STATIC ACCURACY                                                              |                                                                                |          |           |                    |                               |         |           |                 |

| Resolution                                                                   |                                                                                | 12       |           |                    | 12                            |         |           | Bits            |

| Relative Accuracy                                                            | T <sub>A</sub> Full temperature range                                          |          |           | ±1/2               |                               |         | +1        | LSB             |

| Differential Nonlinearity <sup>(2)</sup><br>Gain Error <sup>(3)(4)</sup>     | T <sub>A</sub> Full temperature range<br>T <sub>A</sub> +25°C                  |          |           | +1                 |                               |         | ±1        | LSB             |

| Gain Error                                                                   | T <sub>A</sub> Full temperature Range                                          |          |           | ±1<br>+2           |                               |         | ±3        | LSB<br>LSB      |

| Gain Temperature Coefficient                                                 | TA Full temperature mange                                                      |          |           | 12                 |                               |         | .1.4      | LSB             |

| ΔGain/ΔTemperature <sup>(5)(6)</sup>                                         |                                                                                |          |           | ±5                 |                               |         | ±5        | ppm/°C          |

| DC Supply Rejection                                                          | $T_A = +25^{\circ}C (\Delta V_{DD} = \pm 5\%)$                                 |          |           | 0.002              |                               |         | 0.002     | %/%             |

| ΔGain/ΔV <sub>DD</sub> <sup>isi</sup>                                        | T <sub>A</sub> - Full temperature range                                        |          |           | ĺ.                 |                               |         |           |                 |

| Output Leakage Current at OUT 1                                              | $(\Delta V_{DD} = \pm 5\%)$<br>$T_A = +25^{\circ}C. RD/WR - DS = 0V.$          |          |           | 0.004              |                               |         | 0.004     | %/%             |

| Output Leakage Content at Out 1                                              | all digital inputs = 0V                                                        |          |           | 10                 |                               |         | 10        | n <b>A</b>      |

|                                                                              | T <sub>A</sub> Full temperature range                                          |          |           | "                  |                               |         | ,,,       | "               |

|                                                                              | S, T versions                                                                  |          |           | 200                |                               |         | 200       | n <b>A</b>      |

|                                                                              | J, K, A, B versions                                                            | 1        |           | 25                 | i                             |         | 25        | nA              |

| DYNAMIC PERFORMANCE                                                          |                                                                                |          |           |                    |                               |         |           |                 |

| Propagation Delay(5)(7)(8)                                                   | T <sub>A</sub> = +25°C                                                         |          |           |                    |                               |         |           |                 |

|                                                                              | (OUT 1 Load = 100Ω, C <sub>€xt</sub> = 13pF)                                   |          |           | 300                |                               |         | 300       | ns              |

| Current Settling Time <sup>(5)(8)</sup>                                      | T <sub>A</sub> = Full temperature range                                        |          |           |                    |                               | i       |           |                 |

| Glitch Energy <sup>(5)</sup> , V <sub>REF</sub> AGND                         | (to 1/2 LSB) lour, Load = 100Ω                                                 |          |           | 1                  |                               |         | 1         | μs              |

| Gitten Energy . VREF AGNU                                                    | T <sub>A</sub> = +25°C T <sub>A</sub> Full temperature range                   |          |           | 400                |                               |         | 400       | nVs             |

| AC Feedthrough at Iou1 1 (5811)                                              | T <sub>A</sub> = Full temperature range,                                       |          |           | 500                | 1                             |         | 500       | nVs             |

| The food in odgination of                                                    | V <sub>REF</sub> = ±10V, f = 10kHz                                             |          |           | 5                  |                               |         | 5         | mVp-p           |

| REFERENCE INPUT                                                              |                                                                                |          | -         | ļ -                |                               |         |           | титр-р          |

| Input Resistance                                                             |                                                                                |          |           |                    | l                             |         |           |                 |

| (Pin 19 to GND)(12)                                                          | T <sub>A</sub> Full temperature range                                          | 7        | 11        | 15                 | 7                             | 11      | 15        | kΩ              |

|                                                                              | V <sub>DD</sub> = +5V                                                          |          |           |                    |                               |         |           |                 |

| ANALOG OUTPUTS                                                               | T <sub>A</sub> : Full temperature range                                        |          |           |                    | _                             |         |           |                 |

| Output Capacitance <sup>(5)</sup>                                            | $V_{DD} = +5V \text{ or } +15V$                                                |          |           |                    |                               |         |           |                 |

| Cout 2                                                                       | DB <sub>0</sub> -DB <sub>11</sub> = 0V, RD/WR = DS = 0V                        |          |           | 70                 |                               |         | 70        | pF              |

| Cour :                                                                       | $DB_0-DB_{11} = V_{DD}$ . $RD/WR = DS = 0V$                                    |          |           | 150                |                               |         | 150       | pF              |

| DIGITAL INPUTS                                                               |                                                                                |          |           |                    |                               |         |           |                 |

| Input High Voltage                                                           | T <sub>A</sub> : Full temperature range                                        | 2.4      |           |                    | 2.4                           |         |           | l v             |

| Input Low Voltage                                                            | T <sub>A</sub> = Full temperature range                                        |          |           | 0.8                |                               |         | 0.8       | ľ               |

| Input Current <sup>(9)</sup>                                                 | T <sub>A</sub> = +25°C                                                         |          |           | 1                  |                               |         | 1         | μΑ              |

| I + C                                                                        | T <sub>A</sub> = Full temperature range                                        |          |           | 10                 |                               |         | 10        | μA              |

| Input Capacitance <sup>(5)</sup> DB <sub>0</sub> -DB <sub>11</sub> RD/WR, DS | T <sub>A</sub> Full temperature range<br>T <sub>A</sub> Full temperature range |          |           | 12                 |                               |         | 12        | pF              |

|                                                                              | TA Turremperature range                                                        |          |           | 6                  |                               |         | 6         | ρF              |

| DIGITAL OUTPUTS Output High Voltage                                          | I <sub>0</sub> = 400μA                                                         | 4.0      |           |                    |                               |         |           |                 |

| Output Low Voltage                                                           | lo = -1.6mA                                                                    | 4.0      |           | 0.4                | 4.0                           |         |           | V               |

| Three-State Output Leakage Current                                           | 1                                                                              |          |           | 10                 |                               |         | 0.4<br>10 | V<br>μ <b>A</b> |

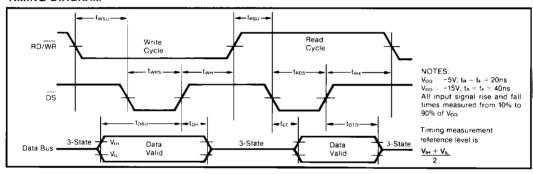

| SWITCHING CHARACTERISTICS(10)                                                | See timing diagram                                                             |          |           | <u> </u>           |                               | <b></b> |           | μ^              |

| Write to Data Stobe Setup Time                                               | T <sub>A</sub> = +25°C                                                         | 0        |           |                    | 0                             |         |           | <u></u>         |

| ·                                                                            | T <sub>A</sub> =Full temperature range                                         | ō        |           | 1                  | 0                             |         |           | ns<br>ns        |

| Data Strobe to Write Hold Time                                               | T <sub>A</sub> = +25°C                                                         | 0        |           | ,                  | 0                             |         |           | ns              |

| Bond to Date Direction 2 : The                                               | T <sub>A</sub> ≕ Full temperature range                                        | 0        |           |                    | 0                             |         |           | ns              |

| Read to Data Strobe Setup Time                                               | T <sub>A</sub> = +25°C<br>T <sub>A</sub> =: Full temperature range             | 0        |           |                    | 0                             |         |           | ns              |

| Data Strobe to Read Hold Time                                                |                                                                                | 0        |           |                    | 0                             |         |           | ns              |

| Data Strobe to Head Hold Titlle                                              | $T_A = +25^{\circ}C$ $T_A = Full temperature range$                            | 0        |           |                    | 0                             |         |           | ns              |

| Write Mode Data Strobe Width                                                 | T <sub>A</sub> = -25°C                                                         | 180      |           |                    | 0<br>180                      |         |           | ns              |

|                                                                              | T <sub>A</sub> = Full temperature range                                        | 250      |           |                    | 250                           |         |           | ns<br>ns        |

| Read Mode Data Strobe Width                                                  | T <sub>A</sub> = -25°C                                                         | 220      |           |                    | 220                           |         |           | ns              |

| Data Setup Time                                                              | T <sub>A</sub> == Full temperature range                                       | 290      | l i       |                    | 290                           |         |           | ns              |

| Data Setup Time                                                              | $I_A = +25$ °C<br>$I_A = Full temperature range$                               | 210      |           |                    | 210                           |         |           | ns              |

| Data Hold Time                                                               | $T_A = +000$ temperature range $T_A = +25$ °C                                  | 250<br>0 |           |                    | 250<br>0                      |         |           | ns              |

|                                                                              | T <sub>A</sub> =: Full temperature range                                       | ő        |           |                    | 0                             |         |           | ns<br>ns        |

| Data Strobe to Output Valid Time <sup>(5)</sup>                              | T <sub>A</sub> = +25°C                                                         |          |           | 300                |                               |         | 300       | ns              |

| Output Active Time from Deselection <sup>(5)</sup>                           | T <sub>A</sub> :- Full temperature range                                       |          |           | 400                |                               |         | 400       | ns              |

| Output Active Time from Deselection                                          | T <sub>A</sub> = +25°C                                                         | 1        |           | 315                |                               |         | 0.7       |                 |

|                                                                              |                                                                                |          |           | 215                |                               |         | 215       | ns              |

|                                                                              | T <sub>A</sub> : Full temperature range                                        | I        |           | 375                |                               |         | 375       |                 |

| POWER SUPPLY                                                                 |                                                                                |          |           | 375                |                               |         | 375       | ns              |

| POWER SUPPLY                                                                 | T <sub>A</sub> Full temperature range                                          |          |           | -                  |                               |         |           |                 |

| POWER SUPPLY Supply Current                                                  |                                                                                |          |           | 2                  |                               |         | 375<br>2  | mA              |

|                                                          |                                                            |      | DAC8012B, K, T <sup>(1)</sup> |     | DAC8012A, J, S <sup>(1)</sup> |     | ļ   |         |

|----------------------------------------------------------|------------------------------------------------------------|------|-------------------------------|-----|-------------------------------|-----|-----|---------|

| PARAMETER                                                | CONDITIONS                                                 | MIN  | TYP                           | MAX | MIN                           | TYP | MAX | UNITS   |

|                                                          | V <sub>DO</sub> = +15V                                     |      |                               |     |                               |     |     | _       |

| DIGITAL INPUTS                                           |                                                            |      |                               |     |                               |     |     |         |

| Input High Voltage                                       | T <sub>A</sub> = Full temperature range                    | 13.5 |                               |     | 13.5                          |     |     | V       |

| Input Low Voltage                                        | T <sub>A</sub> = Full temperature range                    | 1    |                               | 1.5 |                               |     | 1.5 | V       |

| Input Current <sup>(9)</sup>                             | T <sub>A</sub> = +25°C                                     |      |                               | 1   |                               |     | 1   | μΑ      |

|                                                          | T <sub>A</sub> = Full temperature range                    | l I  |                               | 10  |                               |     | 10  | $\mu A$ |

| Input Capacitance 151: DB <sub>0</sub> -DB <sub>11</sub> | T <sub>A</sub> = Full temperature range                    |      |                               | 12  |                               |     | 12  | pF      |

| RD/WR. DS                                                | T <sub>A</sub> Full temperature range                      |      |                               | 10  |                               |     | 10  | pF      |

|                                                          | Tan temperature range                                      | +    |                               |     |                               |     |     |         |

| DIGITAL OUTPUTS                                          | lo ≕ 3mA                                                   | 13.5 |                               |     | 13.5                          |     |     | v       |

| Output High Voltage                                      | Io · · · · 3mA                                             | 13.3 | İ                             | 1.5 | 10.0                          |     | 1.5 | ľ       |

| Output Low Voltage                                       | 10 - 3MA                                                   | 1    |                               | 10  |                               |     | 10  | μΑ      |

| Three-State Output Leakage Current                       |                                                            |      |                               | 10  |                               |     | 10  | μA      |

| SWITCHING CHARACTERISTICS101                             | See Timing Diagram                                         |      |                               |     |                               |     |     |         |

| Write to Data Strobe Setup Time                          | T <sub>A</sub> = +25°C                                     | 0    | l                             |     | 0                             |     |     | ns      |

|                                                          | T <sub>A</sub> : Full temperature range                    | 0    |                               |     | 0                             |     |     | ns      |

| Data Strobe to Write Hold Time                           | T <sub>A</sub> - +25°C                                     | 0    | 1                             |     | 0                             |     |     | ns      |

|                                                          | T <sub>A</sub> = Full temperature range                    | 0    |                               |     | 0                             |     |     | ns      |

| Read to Data Strobe Setup Time                           | T <sub>A</sub> = +25°C                                     | 0    |                               |     | 0                             |     |     | ns      |

|                                                          | T <sub>A</sub> = Full temperature range                    | 0    |                               | i   | 0                             |     |     | ns      |

| Data Strobe to Read Hold Time                            | T <sub>A</sub> - +25°C                                     | 0    |                               |     | lo                            |     |     | ns      |

|                                                          | T <sub>A</sub> Full temperature range                      | l 0  |                               | l   | 0                             |     |     | ns      |

| Write Mode Data Strobe Width                             | T <sub>A</sub> = +25°C                                     | 100  |                               | ľ   | 100                           |     |     | ns      |

| Time mode balla circulation                              | T <sub>A</sub> = Full temperature range                    | 120  |                               |     | 120                           |     |     | ns      |

| Read Mode Data Strobe Width                              | T <sub>4</sub> = +25°C                                     | 110  |                               |     | 110                           | ĺ   |     | ns      |

| ricas moso para onoso man                                | T <sub>A</sub> = Full temperature range                    | 150  |                               |     | 150                           | l   |     | ns      |

| Data Setup Time                                          | T <sub>A</sub> = +25°C                                     | 90   |                               |     | 90                            | l   |     | ns      |

| Data Setop Time                                          | T <sub>A</sub> = Full temperature range                    | 120  |                               | •   | 120                           | 1   |     | ns      |

| Data Hold Time                                           | T <sub>A</sub> = +25°C                                     | 0    | L                             | 1   | 0                             |     |     | ns      |

| Data Flord Tillie                                        | T <sub>A</sub> = Full temperature range                    | ا م  | l                             |     | ا م                           |     |     | ns      |

| Data Strobe to Output Valid Time                         | T <sub>A</sub> = +25°C                                     | ľ    | l                             | 180 | 1                             |     | 180 | ns      |

| Data Strobe to Output valid Time                         | T <sub>A</sub> = Full temperature range                    | 1    | l                             | 220 |                               |     | 220 | ns      |

| Output Active Time for Deselection                       | T <sub>A</sub> = +25°C                                     |      | l                             | 180 |                               |     | 180 | ns      |

| Output Active Time for Deselection                       | T <sub>A</sub> = Full temperature range                    |      |                               | 250 |                               |     | 250 | ns      |

| POWER SUPPLY                                             |                                                            | 1    |                               |     |                               |     |     |         |

|                                                          | T <sub>A</sub> = Full temperature range                    |      | 1                             |     |                               |     |     |         |

| Supply Current                                           |                                                            |      | I                             | 2   |                               |     | ,   |         |

|                                                          | (all digital inputs V <sub>INL</sub> or V <sub>INH</sub> ) |      | !                             | 2   |                               | l   | 2   | mA      |

|                                                          | T <sub>A</sub> = Full temperature range                    |      | ٠.                            | 400 |                               | ۱   |     | Ι.      |

|                                                          | (all digital inputs 0V or V <sub>DD</sub> )                | 1    | 10                            | 100 | I                             | 10  | 100 | μΑ      |

NOTES: (1)  $T_A = -55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for S, T grades.  $T_A = -25^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  for A, B grades.  $T_A = 0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  for J, K grades. (2) 12-bit monotonic over full forms and the second s temperature range. (3) Includes the effects of 5ppm max gain TC. (4) Using internal Res. DAC register loaded with 1111 1111. (5) Guaranteed but not tested. (6) Typical value is 2ppm/°C for V<sub>DD</sub> = +5V. (7) From digital input change to 90% of final analog output. (8) All digital inputs = 0V to V<sub>DD</sub>; or Voo to 0V. (9) Logic inputs are MOS gates, typical input current (at +25°C) is less than 1nA. (10) Sample tested at +25°C to ensure compliance. (11) Feedthrough can further be reduced by connecting the metal lid on the sidebraze package (Suffix H) to DGND. (12) Resistor T.C. = +100ppm/°C max

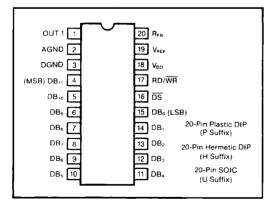

#### PIN DESIGNATIONS

#### **ABSOLUTE MAXIMUM RATINGS**

| ABSOLUTE MAXIMUM HATINGS                                               |

|------------------------------------------------------------------------|

| (T <sub>A</sub> = +25°C, unless otherwise noted.)                      |

| V <sub>0D</sub> to DGND                                                |

| Digital Input Voltage to DGND                                          |

| AGND to DGND                                                           |

| V <sub>RFB</sub> , V <sub>REF</sub> to DGND                            |

| V <sub>PIN 1</sub> to DGND                                             |

| Power Dissipation (any package) to +75°C 450mW                         |

| Derates Above +75°C by 6mW/°C                                          |

| Operating Temperature Range                                            |

| Military Grades: S, T                                                  |

| Industrial Grades: A, B25°C to +85°C                                   |

| Commercial Grades: J, K                                                |

| Storage Temperature                                                    |

| Lead Temperature (soldering, 10s)+300°C                                |

| CAUTION                                                                |

| Stresses above those listed under "Absolute Maximum Ratings"           |

| may cause permanent damage to the device. This is a stress rating      |

| only and functional operation at or above this specification is not    |

| implied. Exposure to above maximum rating conditions for extended      |

| periods may affect device reliability.                                 |

| 2. Do not apply voltages higher than Von or less than GND potential on |

| any terminal except V <sub>REF</sub> .                                 |

| 3. The digital inputs are zener protected, however, permanent damage   |

| may occur on unprotected units from high-energy electrostatic          |

| fields. Keep units in conductive foam at all times until ready to use. |

| Use proper antistatic handling procedures.                             |

|                                                                        |

4. Remove power before inserting or removing units from their sockets.

#### ORDERING INFORMATION

| Model     | Package                 | Temperature<br>Range | Relative<br>Accuracy (LSB) | Gain Error (LSB) |

|-----------|-------------------------|----------------------|----------------------------|------------------|

| DAC8012JP | Plastic DIP             | 0°C to +70°C         | ±1                         | ±3               |

| DAC8012KP | Plastic DIP             | 0°C to +70°C         | ±1/2                       | ±1               |

| DAC8012JU | Plastic SOIC            | 0°C to +70°C         | ±1                         | ±3               |

| DAC8012KU | Plastic SOIC            | 0°C to +70°C         | ±1/2                       | ±1               |

| DAC8012AH | Side-brazed ceramic DIP | -25°C to +85°C       | ±1                         | ±3               |

| DAC8012BH | Side-brazed ceramic DIP | -25°C to +85°C       | ±1/2                       | ±1               |

| DAC8012SH | Side-brazed ceramic DIP | -55°C to +125°C      | ±1                         | ±3               |

| DAC8012TH | Side-brazed ceramic DIP | -55°C to +125°C      | ±1/2                       | ±1               |

#### **BURN-IN SCREENING OPTION**

See text for details.

| Model        | Package                 | Temperature<br>Range | Relative<br>Accuracy (LSB) | Burn-In Temp.<br>(160 Hours) <sup>111</sup> |

|--------------|-------------------------|----------------------|----------------------------|---------------------------------------------|

| DAC8012JP-BI | Plastic DIP             | 0°C to +70°C         | ±1                         | +85°C                                       |

| DAC8012KP-BI | Plastic DIP             | 0°C to +70°C         | ±1/2                       | +85° C                                      |

| DAC8012JU-BI | Plastic SOIC            | 0°C to +70°C         | ±1                         | +85°C                                       |

| DAC8012KU-BI | Plastic SOIC            | 0°C to +70°C         | ±1/2                       | +85° C                                      |

| DAC8012AH-BI | Side-brazed ceramic DIP | -25°C to +85°C       | ±1                         | +125°C                                      |

| DAC8012BH-BI | Side-brazed ceramic DIP | -25°C to +85°C       | ±1/2                       | +125°C                                      |

| DAC8012SH-BI | Side-brazed ceramic DIP | 55°C to +125°C       | ±1                         | +125°C                                      |

| DAC8012TH-BI | Side-brazed ceramic DIP | 55°C to +125°C       | ±1/2                       | +125°C                                      |

NOTE: (1) Or equivalent combination of time and temperature.

#### TIMING DIAGRAM

#### **BURN-IN SCREENING**

Burn-in screening is an option available for the models indicated in the Ordering Information table. Burn-in duration is 160 hours at the maximum specified grade operating temperature (or equivalent combination of time and temperature).

All units are tested after burn-in to ensure that grade specifications are met. To order burn-in, add "-BI" to the base model number.

#### **ESD PROTECTION**

The design of the DAC8012 includes ESD protection circuitry for the digital inputs. High voltage static charges are shunted to the supply and ground rails. However, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. When not in use, devices must be stored in conductive foam or rails. The foam or rails should be discharged to the destination socket before devices are removed.

# DISCUSSION OF SPECIFICATIONS

#### **Relative Accuracy**

This term (also known as end point linearity) describes the transfer function of analog output to digital input code. Relative accuracy describes the deviation from a straight line after zero and full scale have been adjusted.

#### **Differential Nonlinearity**

Differential nonlinearity is the deviation from an ideal ILSB change in the output, for adjacent input code changes. A differential nonlinearity specification of ILSB guarantees monotonicity.

#### **Gain Error**

Gain error is the difference in measure of full-scale output versus the ideal DAC output. The ideal output for the DAC8012 is -(4095/4096) ( $V_{\rm REF}$ ). Gain error may be adjusted to zero using external trims as shown in the applications section.

#### **Output Leakage Current**

The current which appears at OUT<sub>1</sub> with the DAC loaded with all zeros.

#### Multiplying Feedthrough Error

The AC output error due to capacitive feedthrough from  $V_{REF}$  to  $OUT_1$  with the DAC loaded with all zeros. This test is performed using a 10kHz sine wave.

#### **Output Current Settling Time**

The time required for the output to settle within  $\pm 1/2$ LSB of final value from a change in code of all zeros to all ones, or all ones to all zeros.

#### **Propagation Delay**

The delay of the internal circuitry is measured as the time from a digital code change to the point at which the output reaches 90% of final value.

#### Digital-To-Analog Glitch Impulse

The area of the glitch energy measured in nanovolt-seconds. Key contributions to glitch energy are internal circuitry timing differences and charge injected from digital logic. The measurement is performed with  $V_{\rm REF} = {\rm GND}$ .

#### Monotonicity

Monotonicity assures that the analog output will increase or stay the same for increasing digital input codes. The DAC8012 is guaranteed monotonic to 12 bits.

#### **Power Supply Rejection**

Power supply rejection is the measure of the sensitivity of the output (full scale) to a change in the power supply voltage.

# CIRCUIT DESCRIPTION

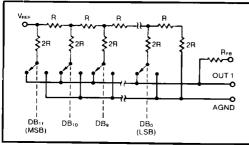

#### **DIGITAL-TO-ANALOG SECTION**

Figure 1 shows a simplified schematic of the digital-to-analog portion of the DAC8012. The current from the  $V_{\rm REF}$  pin is switched from  $I_{\rm OUT-1}$  to AGND by the FET switch for that bit. This circuit architecture keeps the resistance at the reference pin constant and equal to  $R_{\rm LDR}$ , so the reference could be provided by

FIGURE 1. Simplified Circuit of the DAC8012.

either a voltage or current, AC or DC, positive or negative polarity, and have a voltage range up to  $\pm 20V$  even with  $V_{\rm DD}=5V$ . The  $R_{\rm LDR}$  is equal to "R" and is typically  $11k\Omega$ .

The output capacitance of the DAC8012 is code dependent and varies from a minimum value (70pF) at code 000<sub>H</sub> to a maximum (200pF) at code FFF<sub>H</sub>.

#### DIGITAL SECTION

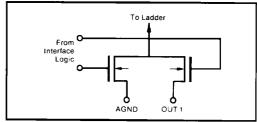

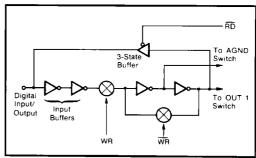

Figure 2 shows the basic current switch. Figure 3 shows the schematic of the input/output buffers. When the  $\overline{DS}$  and the  $RD/\overline{WR}$  are held low, the latches are transparent and pass data from the data bus to the DAC. When the  $\overline{DS}$  is held low and the  $RD/\overline{WR}$  line is held high, the three-state buffer becomes active and the data at the DAC is presented to the digital input/output lines for data readback.

FIGURE 2. N-Channel Current Steering Switch.

FIGURE 3. Digital Input/Output Structure.

The input buffers are CMOS inverters, designed so that when the DAC8012 is operated from a 5V supply ( $V_{\rm DD}$ ), the logic threshold is TTL compatible. Being simple CMOS inverters, there is a range of operations where the inverters operate in the linear region and thus draw more supply current than normal. Minimizing the transition time through the linear region and insuring that the digital inputs are operated as close to the rails as possible will minimize the supply drain current.

# **APPLICATIONS**

#### UNIPOLAR OPERATION

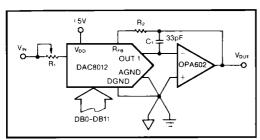

Figure 4 shows the DAC8012 connected for unipolar operation. The high-grade DAC8012 is specified for a 1LSB gain error, so gain adjust is typically not needed.

6.1

However, the resistors shown are for adjusting full-scale errors. The value of  $R_1$  should be minimized to reduce the effects of mismatching temperature coefficients between the internal and external resistors. A range of adjustment of 1.5 times the desired range will be adequate. For example, for a DAC8012JP, the gain error is specified to be  $\pm 3 \text{LSB}$ . A range of adjustment of  $\pm 4.5 \text{LSB}$  will be adequate. The equation shows a minimum value of  $33\Omega$  for the potentiometer.

$$R_1 = (R_{LADDER} / 4096) \times (3 \times Gain Error)$$

The addition of  $R_1$  will cause a negative gain error. To compensate for this error,  $R_2$  must be added. The value of  $R_2$  should be one-third the value of  $R_1$ .

FIGURE 4. Unipolar Binary Operation.

The capacitor across the feedback resistor is used to compensate for the phase shift due to stray capacitances of the circuit board, the DAC output capacitance, and op amp input capacitance. Eliminating this capacitor will result in excessive ringing and an increase in glitch energy in higher speed applications. This capacitor should be as small as possible to minimize settling time.

The circuit of Figure 4 may be used with input voltages up to  $\pm 20$ V as long as the output amplifier is biased to handle the excursions. Table I represents the analog output for four codes into the DAC for Figure 4.

TABLE 1. Unipolar Output Code for Figure 4.

| Binary Code    |         | Analog Output                        |

|----------------|---------|--------------------------------------|

| MSBI           | I LSB   |                                      |

| 1111 11        | 11 1111 | V <sub>IN</sub> (4095/4096)          |

| 1000 0000 0000 |         | $-V_{IN}$ (2048/4096) = $-1/2V_{IN}$ |

| 0000 0000 0001 |         | V <sub>IN</sub> (1/4096)             |

| 0000 00        | 00 0000 | 0 Volts                              |

#### **BIPOLAR FOUR-QUADRANT OPERATION**

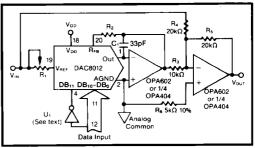

Figure 5 and Table II illustrate the recommended circuit and code relationship for bipolar operation. The D/A function itself uses offset binary code. The inverter  $U_1$  on the MSB line converts twos complement input code to offset binary code. The inverter  $U_1$  may be omitted if the inversion is done in software.

$R_3$ ,  $R_4$ , and  $R_5$  must match within 0.01% and should be the same type of resistors (preferably wire-wound or metal foil), so that their temperature coefficients match. Mismatch of  $R_3$  value to  $R_4$  causes both offset and full-scale error. Mismatch of  $R_5$  to  $R_4$  and  $R_3$  causes full-scale error.

FIGURE 5. Bipolar Operation (Twos Complement Code).

TABLE II. Twos Complement Code Table for Circuit of Figure 5.

| Г | Data Input     |         | Analog Output                |

|---|----------------|---------|------------------------------|

| Γ | MSB↓           | I LSB   |                              |

| L | 0111 11        | 11 1111 | +V <sub>IN</sub> (2047/2048) |

| 1 | 0000 0000 0001 |         | +V <sub>IN</sub> (1/2048)    |

| П | 0000 000       | 0000    | 0 Volts                      |

| П | 1111 1111 1111 |         | −V <sub>IN</sub> (1/2048)    |

| L | 1000 000       | 0000    | V <sub>IN</sub> (2048/2048)  |

#### DIGITALLY CONTROLLED GAIN BLOCK

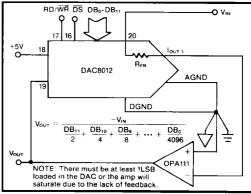

Figure 6 shows a circuit for a digitally controlled gain block. The feedback for the op amp is made up of the FET switch and the R-2R ladder. The input resistor to the gain block is the R+B of the DAC8012. Since the FET switch is in the feedback loop, a "zero code" into the DAC will result in the op amp having no feedback and a saturated op amp output. The DAC8012 readback feature makes the DAC8012 especially good for this configuration when an automatic gain or automatic calibration routine is used. If the logic were set up to calibrate a value via logic external to the processor (successive approximation register), then when the calibration is done, the processor could read the DAC8012 to store away the calibration code.

FIGURE 6. Digitally Controlled Gain Block.

### APPLICATIONS HINTS

CMOS DACs such as the DAC8012 exhibit a codedependent output resistance. The effect of this is a codedependent differential nonlinearity at the amplifier output which depends on the offset voltage Vos of the amplifier. Thus linearity depends upon the potential of low and AGND being exactly equal to each other. Usually the DAC is connected to an external op amp with its noninverting input connected to AGND. The op amp selected should have a low input bias current and low Vos and Vos drift over temperature. The op amp offset voltage should be less than  $(25 \times 10^{-6})$  (V<sub>REF</sub>) over operating conditions. Suitable op amps are the Burr-Brown OPA37 and the OPA111 for fixed reference applications and low bandwidth requirements. The OPA37 has low Vos and will not require an offset trim. For wide bandwidth, high slew rate, or fast settling applications, the Burr-Brown OPA602, 1/4 OPA404, or OPA606 are recommended.

Unused digital inputs should be connected to  $V_{\rm DD}$  or to DGND. This prevents noise from triggering the high impedance digital input. It is suggested that the unused digital inputs also be given a path to ground or  $V_{\rm DD}$  through a IM $\Omega$  resistor to prevent the accumulation of static charge if the PC card is unplugged from the system. In addition, in systems where the AGND to DGND connection is on a backplane, it is recommended that two diodes be connected in inverse parallel between AGND and DGND.

# INTERFACING TO MICROPROCESSORS

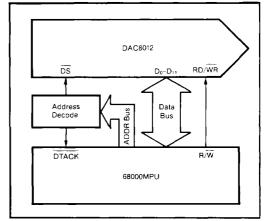

Figure 7 shows the DAC8012 interfaced to a 16-bit microprocessor. The interface requires only address decoding to select the DAC to be written to or read from.

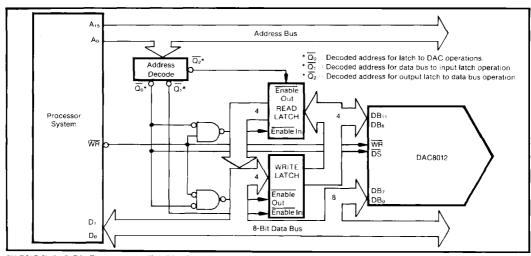

Figure 8 shows an interface scheme for using the DAC8012 with an 8-bit microprocessor. The data for the first 4 bits are written and latched into the external write latch and the next 8 bits are presented on the bus. The DAC8012 is then instructed to pass the data through the internal DAC latch ( $\overline{WR} + \overline{DS}$ ) and all 8 bits are transferred into the DAC. Reading data back is done in the same manner.

FIGURE 7. 16-Bit Microprocessor to DAC8012 Interface

FIGURE 8. 8-Bit Processor to DAC8012 Interface.