# **FEATURES**

tors

|   | Pin Compatible With TC7662/ICL7663 | 2/\$17661 |

|---|------------------------------------|-----------|

|   | High Output Current                | 80 mA     |

|   | No External Diodes Required        |           |

|   | Wide Operating Range               | 3V to 18V |

|   | Low Output Impedance               | 28Ω Typ   |

|   | No Low Voltage Terminal Required   | ,,        |

| - | Application Zener On Chin          |           |

**Doubling Pin Option for Smaller Output Capaci-**

# **GENERAL DESCRIPTION**

The TC962 is an advanced version of the industry-standard 7662 high-voltage DC-to-DC converter. Using improved design techniques and CMOS construction, the TC962 can source as much as 80 mA versus the 7662's 20 mA capability.

As an inverter, the TC962 can put out voltages as high as 18V and as low as 3V without the need for external diodes. The output impedance of the device is a low  $28\Omega$  (with the proper capacitors), voltage conversion efficiency is 99.9%, and power conversion efficiency is 97%.

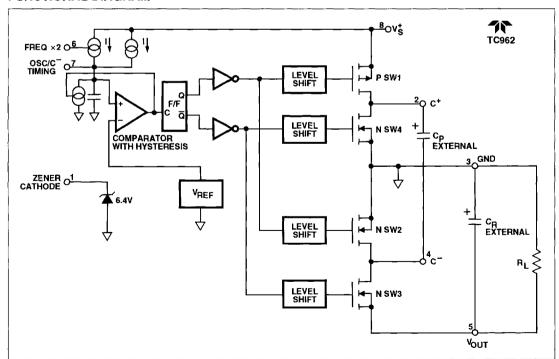

# **FUNCTIONAL DIAGRAM**

#### **TC962**

The low voltage terminal (pin 6) required in some 7662 applications has been eliminated. Grounding this terminal will double the oscillator frequency from 12 kHz to 24 kHz. This will allow the use of smaller capacitors for the same output current and ripple, in most applications. Only two external capacitors are required for inverter applications. In the event an external clock is needed to drive the TC962 (such as paralleling), driving this pin directly will cause the internal oscillator to sync to the external clock.

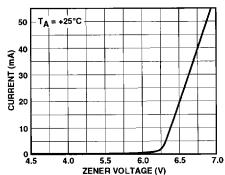

Pin 1, which is used as a test pin on the 7662, is a voltage reference zener on the TC962. This zener (6.4V at 5 mA) has a dynamic impedance of 12W and is intended for use where the TC962 is supplying current to external regulator circuitry and a reference is needed for the regulator circuit. (See applications section.)

The TC962 is compatible with the LTC1044, SI7661, and ICL7662. It should be used in designs that require greater power and/or less input to output voltage drop. It offers superior performance over the ICL7660S.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (Vs to GND)+18                              | ٧  |

|------------------------------------------------------------|----|

| Input Voltage (Any Pin)( $V_S^+ + 0.3$ ) to ( $V_S^ 0.3$ ) | 3) |

| Current Into Any Pin10 m/                                  | Α  |

| ESD Protection±2000                                        | ٧  |

| Output Short CircuitContinuous (at 5.5V Input              | t) |

| Storage Temperature Range65°C to +150°C                    | Ċ  |

| Lead Temperature (Soldering, 10 sec)+300°0                 | С  |

| Operating Temperature Range                                |    |

| CPA, COE0°C to +70°C                                       | С  |

| IJA–25°C to +85°C                                          | Ç  |

| EOE, EPA40°C to +85°C                                      | С  |

| MJA55°C to +125°C                                          | С  |

| Max Dissipation                                            |    |

| COE, CPA, EOE, EPA375 mV                                   | Ν  |

| IJA, MJA500 mV                                             | Ν  |

| Package Thermal Resistance                                 |    |

| CerDIP, R <sub>qJ-A</sub> 90°C/V                           | Ν  |

| PDIP, R <sub>qJ-A</sub> 140°C/V                            | N  |

Static-sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

#### ORDERING INFORMATION

| Part No. | Package           | Temperature<br>Range |

|----------|-------------------|----------------------|

| TC962CPA | 8-Pin Plastic DIP | 0°C to +70°C         |

| TC962IJA | 8-Pin CerDIP      | -25°C to +85°C       |

| TC962EPA | 8-Pin Plastic DIP | -40°C to +85°C       |

| TC962MJA | 8-Pin CerDIP      | -55°C to +125°C      |

| TC962COE | 16-Pin SO         | 0 to +70°C           |

| TC962EOE | 16-Pin SO         | -40°C to +85°C       |

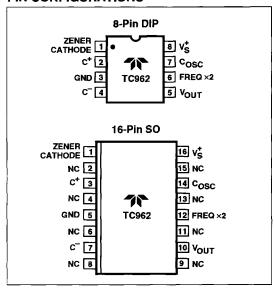

#### PIN CONFIGURATIONS

# ELECTRICAL CHARACTERISTICS: V<sub>S</sub> = 15V, T<sub>A</sub> = +25°C (See Test Circuit)

| Symbol           | Parameter            | Test Conditions                           | Min | Тур  | Max | Unit |

|------------------|----------------------|-------------------------------------------|-----|------|-----|------|

| V <sub>S</sub> * | Supply Voltage       |                                           | 3   |      | 18  | V    |

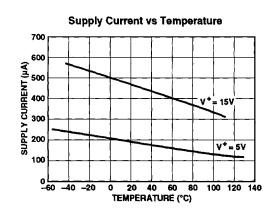

| Is               | Supply Current       | R <sub>L</sub> = ∞                        |     |      |     |      |

|                  | V <sub>S</sub> = 15V | T <sub>A</sub> = +25°C                    | 1   | 510  | 700 | μA   |

|                  |                      | 0 ≤ T <sub>A</sub> ≤ +70°C                |     | 560  |     | μA   |

|                  |                      | ~55 ≤ T <sub>A</sub> ≤ +125°C             | (   | 650  |     | μA   |

|                  | $V_{S}^{+} = 5V$     | T <sub>A</sub> = +25°C                    | 1   | 190  |     | μA   |

|                  |                      | $0 \le T_A < +70^{\circ}C$                | )   | 210  |     | μА   |

|                  |                      | -55 ≤ T <sub>A</sub> ≤ +125°C             | 1   | 210  |     | μA   |

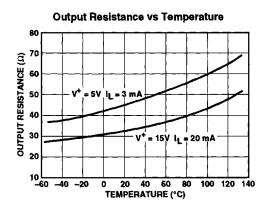

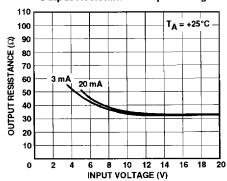

| Ro               | Output Source        | $I_1 = 20 \text{ mA}, V_S^+ = 15V$        |     | 28   | 32  | Ω    |

| •                | Resistance           | $I_1 = 80 \text{ mA}, V_8^+ = 15V$        | 1   | 30   | 35  | Ω    |

|                  |                      | $I_L = 3 \text{ mA}, V_S^{\dagger} = 5V$  |     |      | 46  | Ω    |

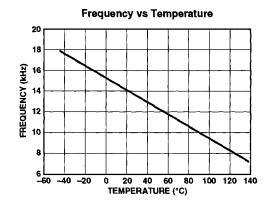

| Cosc             | Oscillator Frequency | Pin 6 Open                                |     | 12   |     | kHz  |

|                  |                      | Pin 6 GND                                 | 1   | 24   |     | kHz  |

| PEFF             | Power Efficiency     | V <sub>S</sub> <sup>+</sup> = 15V         | 93  | 97   |     | %    |

|                  |                      | $R_L = 2 k\Omega$                         | )   |      |     | 1    |

| V <sub>DEF</sub> | Voltage Efficiency   | V <sub>S</sub> <sup>+</sup> = 15V         | 99  | 99.9 |     | %    |

| <del></del> -    |                      | R <sub>L</sub> = ∞                        |     |      |     |      |

|                  |                      | Over Temperature Range                    | 96  | -    |     | %    |

| Vz               | Zener Voltage        | $I_Z = 5 \text{ mA}$                      | 6.2 | 6.4  | 6.6 | V    |

| Z <sub>ZT</sub>  | Zener Impedance      | $I_L = 2.5 \text{ mA to } 7.5 \text{ mA}$ |     | 12   |     | Ω    |

# APPLICATIONS INFORMATION Theory of Operation

The TC962 is a capacitive pump (sometimes called a switched capacitor circuit), where four MOSFET switches control the charge and discharge of a capacitor.

The functional diagram (page 1) shows how the switching action works. SW1 and SW2 are turned on simultaneously, charging  $C_P$  to the supply voltage,  $V_{\text{IN}}$ . This assumes that the on resistance of the MOSFETs in series with the capacitor results in a charging time (3 time constants) that is less than the on time provided by the oscillator frequency as shown:

In the next cycle, SW1 and SW2 are turned off and after a very short interval of all switches being off (this prevents large currents from occurring due to cross conduction), SW3 and SW4 are turned on. The charge in  $C_P$  is then transferred to  $C_R$ , BUT WITH THE POLARITY INVERTED. In this way, a negative voltage is now derived.

Page 1 shows a functional diagram of the TC962. An oscillator supplies pulses to a flip-flop that is then fed to a set of level shifters. These level shifters then drive each set of switches at one-half the oscillator frequency.

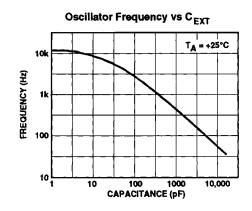

The oscillator has two pins that control the frequency of oscillation. Pin 7 can have a capacitor added that is run to ground. This will lower the frequency of the oscillator by adding capacitance to the timing capacitor internal to the TC962. Grounding pin 6 will turn on a current source and double the frequency. This will double the charge current going into the internal capacitor, as well as any capacitor added to pin 7.

A zener diode has been added to the TC962 for use as a reference in building external regulators. This zener runs from pin 1 to ground.

# **TC962**

## Capacitors

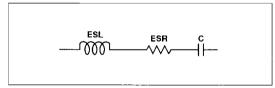

In early charge pump converters, the capacitors were not considered critical due to the high  $R_{DS(ON)}$  of the MOS-FET switches. In order to understand this, let's look at a model of a typical electrolytic capacitor (Figure 1).

Note that one of its characteristics is ESR (equivalent series resistance). This parasitic resistance winds up in series with the load. Thus, both voltage conversion efficiency and power conversion efficiency are compromised if a low ESR capacitor is not used.

In the test circuit, for example, just changing two capacitors,  $C_P$  and  $C_R$ , from capacitors with unspecified ESR to low ESR-type output, impedance changes from  $36\Omega$  to  $28\Omega$ , an improvement of 23%!

This applies to all types of capacitors, including film types (polyester, polycarbonate, etc.).

Some applications information suggest that the capacitor is not critical and attribute the limiting factor of the capacitor to its reactive value. Let's examine this:

$$X_C = \frac{1}{2\pi f C}$$

and  $Z_C = \frac{X_C}{DS}$ ,

where DS (duty cycle) = 50%.

Thus,  $Z_C \approx 2.6\Omega$  at f = 12 kHz, where C = 10  $\mu$ F.

Figure 1 Typical Electrolytic Capacitor

For the TC962, f = 12,000 Hz, and a typical value of C would be 10  $\mu$ F. This is a reactive impedance of <sup>a</sup> 2.6W. If the ESR is as great as 5W, the reactive value is not as critical as it would first appear, as the ESR would predominate. The 5W value is typical of a general-purpose electrolytic capacitor.

#### Latch Up

All CMOS structures contain a parasitic SCR. Care must be taken to prevent any input from going above or below the supply rail, or latch up will occur. The result of latch up is an effective short between  $V^+{}_S$  and  $V^-{}_S$ . Unless the power supply input has a current limit, this latch-up phenomena will result in damage to the device. (See Application Note 31 for additional information.)

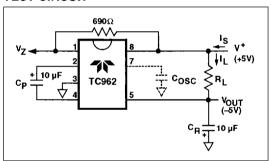

#### **TEST CIRCUIT**

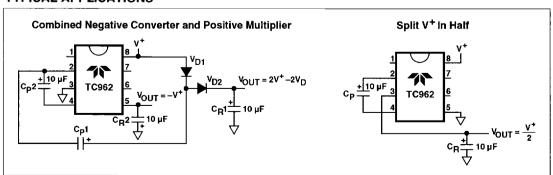

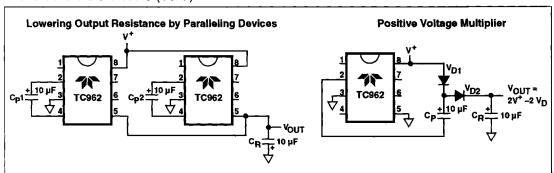

#### TYPICAL APPLICATIONS

# **TYPICAL APPLICATIONS (Cont.)**

# **TYPICAL CHARACTERISTICS CURVES**

# **TC962**

# TYPICAL CHARACTERISTICS CURVES (Cont.)

# Current vs Zener Voltage

#

24 32 40 48 56 LOAD CURRENT (mA)

# **Output Resistance vs Input Voltage**

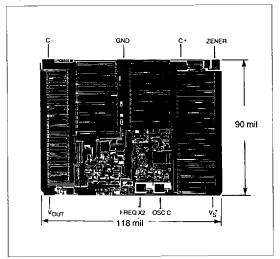

# **BONDING DIAGRAM**

0