# **User's Manual**

# V850ES/SG2

# 32-Bit Single-Chip Microcontroller

# **Hardware**

| μ <b>PD703260</b>                                                                | μ <b>PD703270</b>                                                                | μ <b>PD703280</b>                                                                |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| μ <b>PD703260Y</b>                                                               | μ <b>PD703270Y</b>                                                               | μ <b>PD703280</b> Υ                                                              |

| μ <b>PD703261</b>                                                                | μ <b>PD703271</b>                                                                | μ <b>PD703281</b>                                                                |

| μ <b>PD703261Y</b>                                                               | μ <b>PD703271Y</b>                                                               | μ <b>PD703281Y</b>                                                               |

| μ <b>PD703262</b>                                                                | μ <b>PD703272</b>                                                                | μ <b>PD703282</b>                                                                |

| μ <b>PD703262Y</b>                                                               | μ <b>PD703272Y</b>                                                               | μ <b>PD703282Y</b>                                                               |

| μ <b>PD703263</b>                                                                | μ <b>PD703273</b>                                                                | μ <b>PD703283</b>                                                                |

| μ <b>PD703263Y</b>                                                               | μ <b>PD703273Y</b>                                                               | μ <b>PD703283Y</b>                                                               |

| μ <b>PD70F3261</b>                                                               | μ <b>PD70F3271</b>                                                               | μ <b>PD70F3281</b>                                                               |

| μ <b>PD70F3261Y</b>                                                              | μ <b>PD70F3271Y</b>                                                              | μ <b>PD70F3281Y</b>                                                              |

| μ <b>PD70F3263</b>                                                               | μ <b>PD70F3273</b>                                                               | μ <b>PD70F3283</b>                                                               |

| μ <b>PD70F3263Y</b>                                                              | μ <b>PD70F3273Y</b>                                                              | μ <b>PD70F3283Y</b>                                                              |

| μPD703262Y<br>μPD703263<br>μPD703263Y<br>μPD70F3261<br>μPD70F3261Y<br>μPD70F3263 | μPD703272Υ<br>μPD703273<br>μPD703273Υ<br>μPD70F3271<br>μPD70F3271Υ<br>μPD70F3273 | μPD703282Y<br>μPD703283<br>μPD703283Y<br>μPD70F3281<br>μPD70F3281Y<br>μPD70F3283 |

Document No. U16541EJ4V0UD00 (4th edition)

Date Published July 2005 N CP(K)

# [MEMO]

#### NOTES FOR CMOS DEVICES —

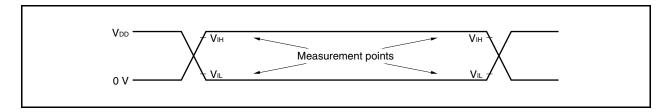

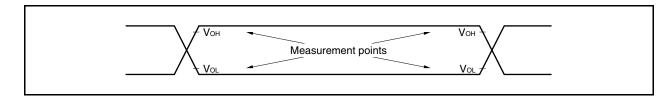

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

# (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

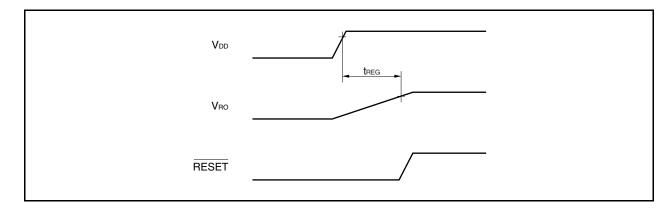

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### 6 INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

IEBus, Inter Equipment Bus, and IECUBE are trademarks of NEC Electronics Corporation.

Windows and Windows NT are either registered trademarks or a trademarks of Microsoft Corporation in the United States and/or other countries.

PC/AT is a trademark of International Business Machines Corporation.

SPARCstation is a trademark of SPARC International, Inc.

Solaris and SunOS are trademarks of Sun Microsystems, Inc.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of March, 2005. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may

appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative

purposes in semiconductor product operation and application examples. The incorporation of these

circuits, software and information in the design of a customer's equipment shall be done under the full

responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by

customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and

"Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

#### (Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- · Ordering information

- Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT]

http://www.necel.com/en/support/support.html

# NEC Electronics America, Inc. (U.S.) NEC Electronics (Europe) GmbH NEC Electronics Hong Kong Ltd.

Santa Clara, California Tel: 408-588-6000 800-366-9782

Duesseldorf, Germany Tel: 0211-65030

#### • Sucursal en España Madrid, Spain

Tel: 091-504 27 87

# • Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-675800

#### • Filiale Italiana

Milano, Italy Tel: 02-66 75 41

#### Branch The Netherlands

Eindhoven. The Netherlands Tel: 040-2654010

#### • Tyskland Filial

Taeby, Sweden Tel: 08-63 87 200

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133

Hong Kong Tel: 2886-9318

# **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-558-3737

### **NEC Electronics Shanghai Ltd.**

Shanghai, P.R. China Tel: 021-5888-5400

### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377

# **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore

Tel: 6253-8311

J05.6

#### **PREFACE**

Readers

This manual is intended for users who wish to understand the functions of the V850ES/SG2 and design application systems using these products.

**Purpose**

This manual is intended to give users an understanding of the hardware functions of the V850ES/SG2 shown in the **Organization** below.

Organization

This manual is divided into two parts: Hardware (this manual) and Architecture (V850ES Architecture User's Manual).

#### Hardware

- Pin functions

- CPU function

- On-chip peripheral functions

- Flash memory programming

- Electrical specifications

#### Architecture

- Data types

- Register set

- Instruction format and instruction set

- Interrupts and exceptions

- Pipeline operation

#### How to Read This Manual

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To understand the overall functions of the V850ES/SG2

→ Read this manual according to the **CONTENTS**.

To find the details of a register where the name is known

→Use APPENDIX B REGISTER INDEX.

To know the electrical specifications of the V850ES/SG2

→ See CHAPTER 32 ELECTRICAL SPECIFICATIONS.

To understand the details of an instruction function

→ Refer to the **V850ES Architecture User's Manual** available separately.

# Register format

→The name of the bit whose number is in angle brackets (<>) in the figure of the register format of each register is defined as a reserved word in the device file.

The "yyy bit of the xxx register" is described as the "xxx.yyy bit" in this manual. Note with caution that if "xxx.yyy" is described as is in a program, however, the compiler/assembler cannot recognize it correctly.

The mark ★ shows major revised points.

**Conventions** Data significance: Higher digits of

nce: Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

Memory map address: Higher addresses on the top and lower addresses on

the bottom

**Note:** Footnote for item marked with **Note** in the text

Caution: Information requiring particular attention

**Remark:** Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory

capacity):  $K \text{ (kilo): } 2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$ G (giga):  $2^{30} = 1,024^3$

# **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

# Documents related to V850ES/SG2

| Document Name                     | Document No. |

|-----------------------------------|--------------|

| V850ES Architecture User's Manual | U15943E      |

| V850ES/SG2 Hardware User's Manual | This manual  |

# Documents related to development tools

| Document Name                                                   | Document No.                                    |                |

|-----------------------------------------------------------------|-------------------------------------------------|----------------|

| IE-V850ES-G1 (In-Circuit Emulator)                              | U16313E                                         |                |

| IE-703288-G1-EM1 (In-Circuit Emulator Option                    | n Board)                                        | To be prepared |

| IE-V850E1-CD-NW (PCMCIA Card Type On-C                          | Chip Debug Emulator)                            | U16647E        |

| QB-V850ESSX2 (In-Circuit Emulator)                              |                                                 | U17091E        |

| CA850 Ver. 3.00 C Compiler Package                              | Operation                                       | U17293E        |

|                                                                 | C Language                                      | U17291E        |

|                                                                 | Assembly Language                               | U17292E        |

|                                                                 | Link Directive                                  | U17294E        |

| PM+ Ver. 6.00 Project Manager                                   |                                                 | U17178E        |

| ID850 Ver. 3.00 Integrated Debugger                             | Operation                                       | U17358E        |

| ID850QB Ver. 2.80 Integrated Debugger                           | Operation                                       | U16973E        |

| SM850 Ver. 2.50 System Simulator                                | SM850 Ver. 2.50 System Simulator Operation      |                |

| SM850 Ver. 2.00 or Later System Simulator                       | External Part User Open Interface Specification | U14873E        |

| SM+ System Simulation                                           | Operation                                       | U17246E        |

|                                                                 | User Open Interface                             | U17247E        |

| RX850 Ver. 3.13 or Later Real-Time OS                           | Basics                                          | U13430E        |

|                                                                 | Installation                                    | U13410E        |

|                                                                 | Technical                                       | U13431E        |

| RX850 Pro Ver. 3.15 Real-Time OS                                | Basics                                          | U13773E        |

|                                                                 | Installation                                    | U13774E        |

| Technical                                                       |                                                 | U13772E        |

| RD850 Ver. 3.01 Task Debugger RD850 Pro Ver. 3.01 Task Debugger |                                                 | U13737E        |

|                                                                 |                                                 | U13916E        |

| AZ850 Ver. 3.20 System Performance Analyzer                     |                                                 | U14410E        |

| PG-FP4 Flash Memory Programmer                                  | U15260E                                         |                |

# **CONTENTS**

| CHAPTER      | 1 INTRODUCTION                                                                  | 22  |

|--------------|---------------------------------------------------------------------------------|-----|

| 1.1          | General                                                                         | 22  |

| 1.2          | Features                                                                        |     |

| 1.3          | Application Fields                                                              |     |

| 1.4          | Ordering Information                                                            |     |

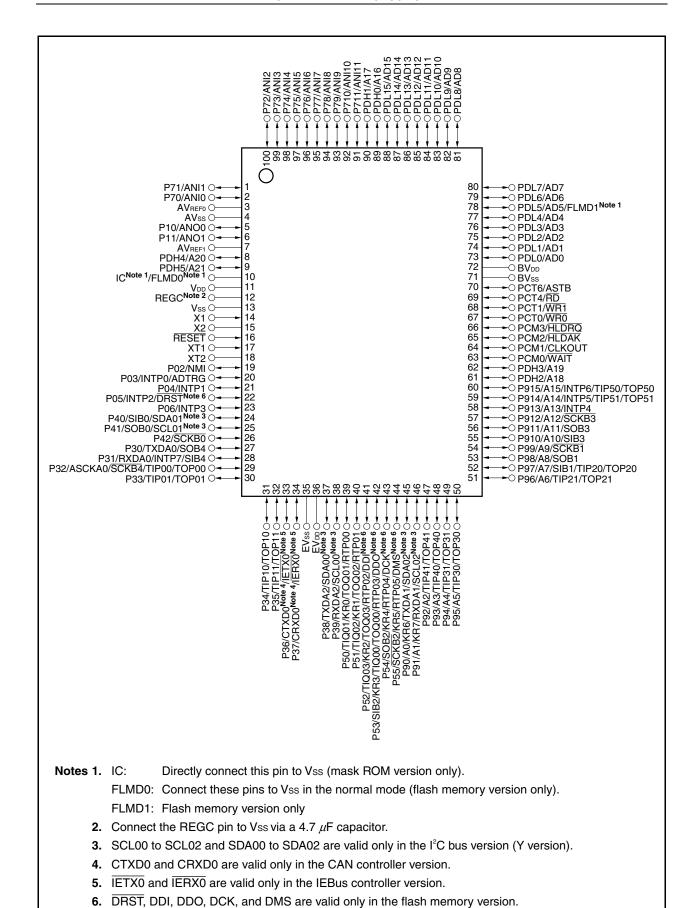

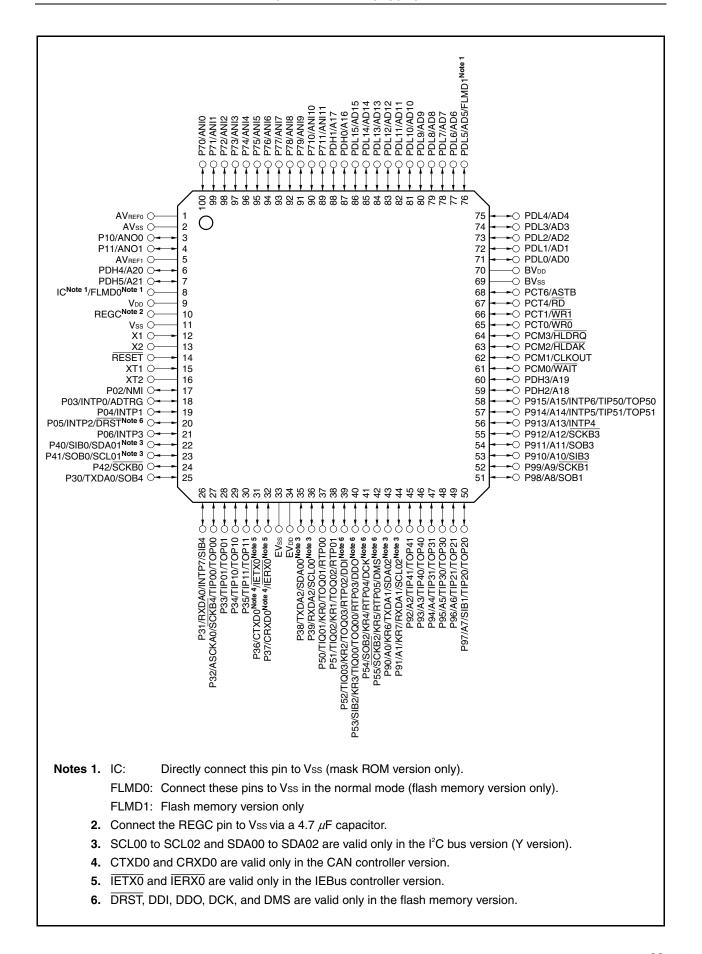

| 1.5          | Pin Configuration (Top View)                                                    |     |

| 1.6          | Function Block Configuration                                                    |     |

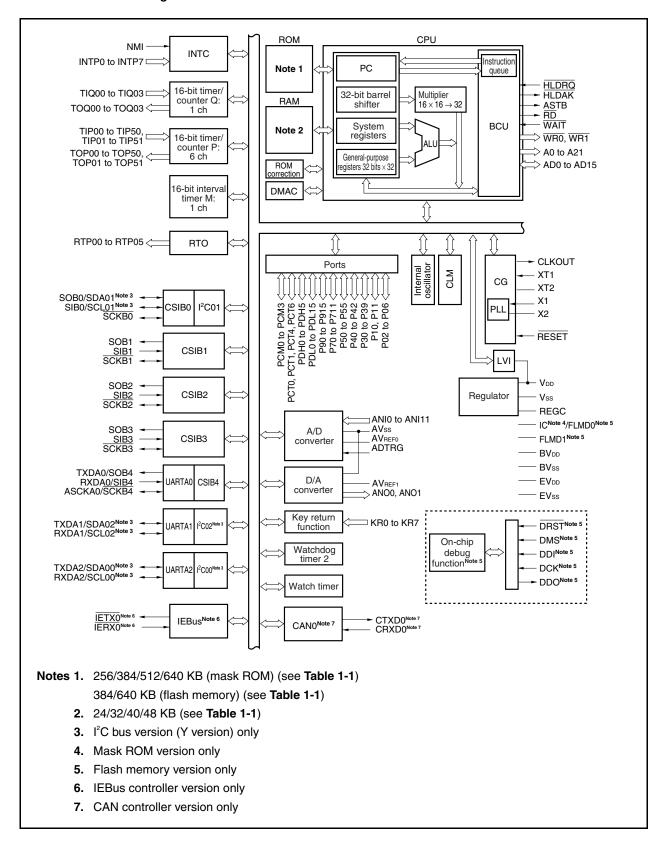

|              | 1.6.1 Internal block diagram                                                    |     |

|              | 1.6.2 Internal units                                                            |     |

| CHAPTER      | 2 PIN FUNCTIONS                                                                 | 39  |

| 2.1          | List of Pin Functions                                                           | 39  |

| 2.2          | Pin States                                                                      | 49  |

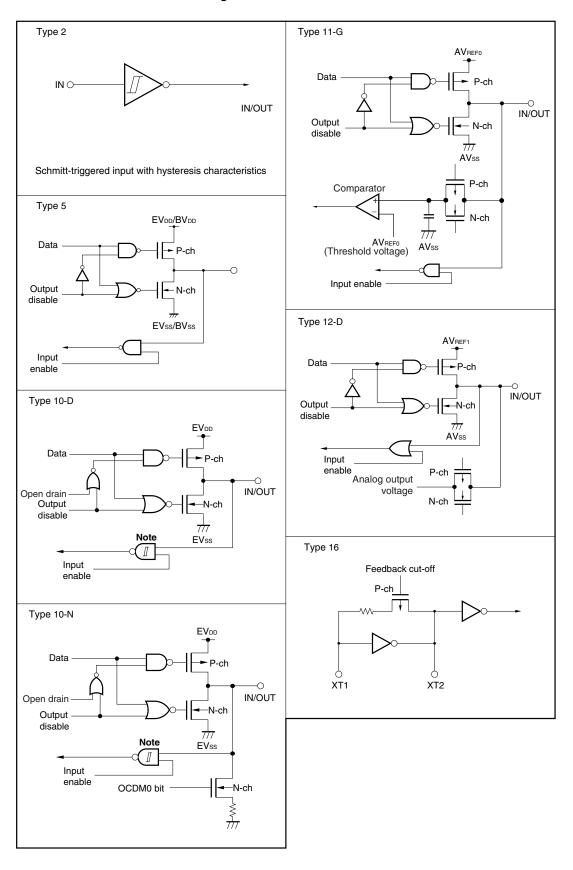

| 2.3          | Pin I/O Circuit Types, I/O Buffer Power Supplies, and Connection of Unused Pins | 50  |

| <b>★</b> 2.4 | Cautions                                                                        | 54  |

| CHAPTER      | 3 CPU FUNCTION                                                                  | 55  |

| 3.1          | Features                                                                        | 55  |

| 3.2          | CPU Register Set                                                                |     |

|              | 3.2.1 Program register set                                                      | 57  |

|              | 3.2.2 System register set                                                       |     |

| 3.3          | Operation Modes                                                                 |     |

|              | 3.3.1 Specifying operation mode                                                 | 64  |

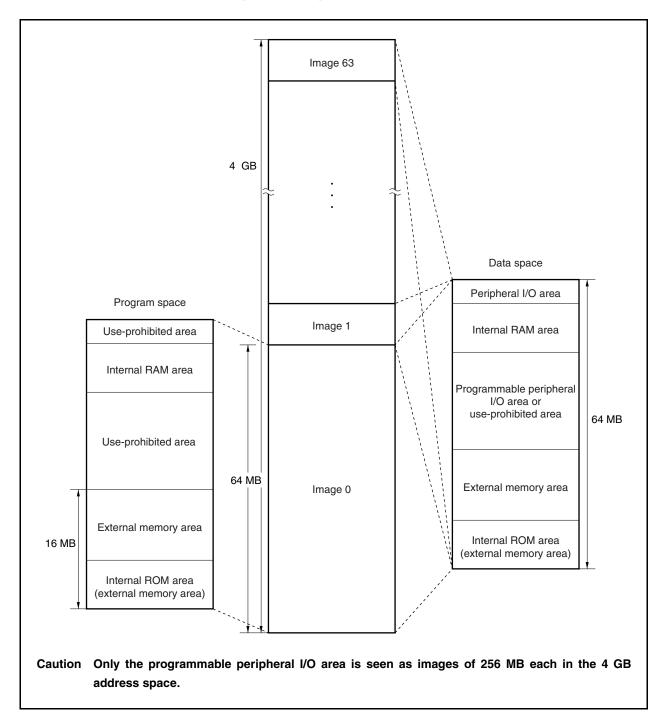

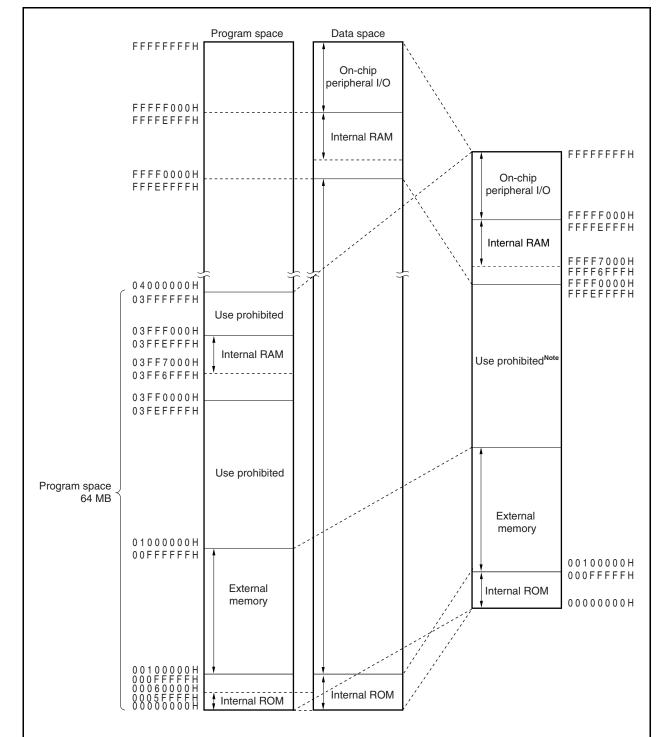

| 3.4          | Address Space                                                                   | 65  |

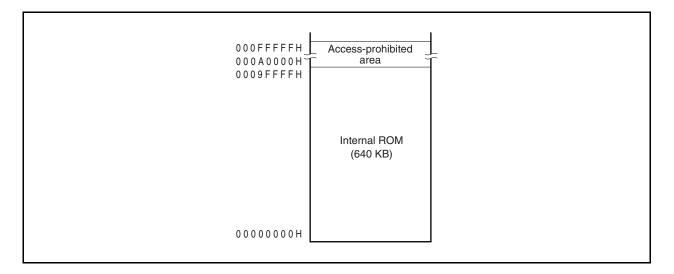

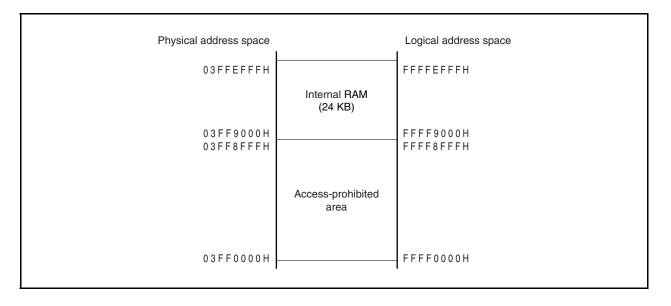

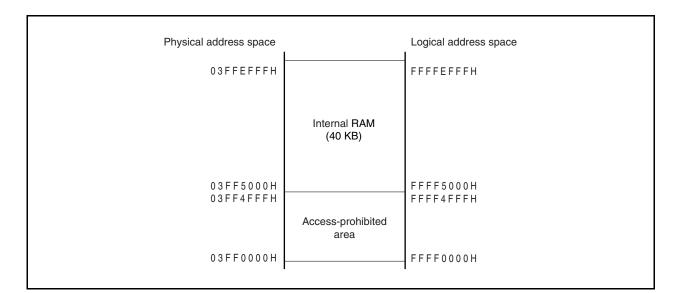

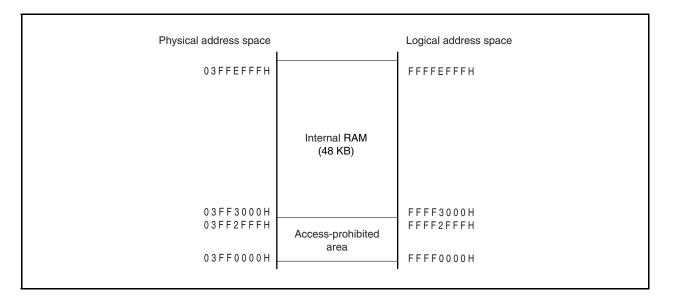

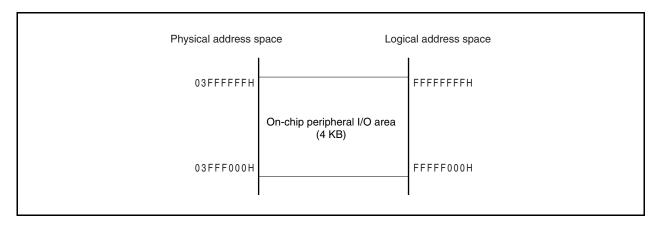

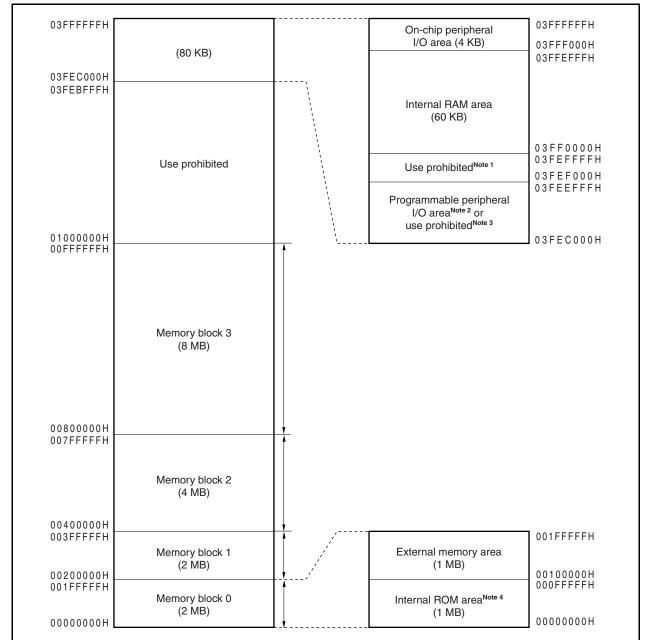

|              | 3.4.1 CPU address space                                                         | 65  |

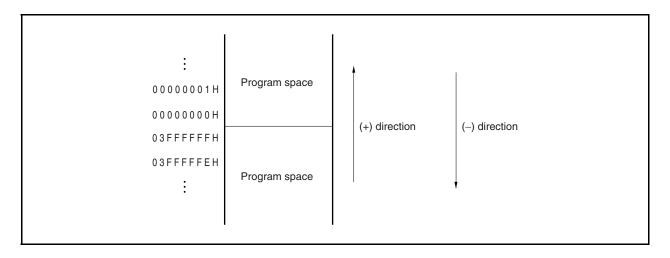

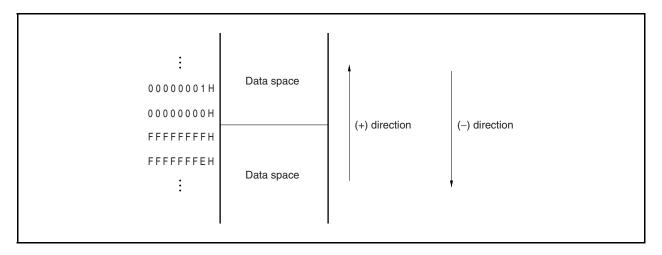

|              | 3.4.2 Wraparound of CPU address space                                           | 66  |

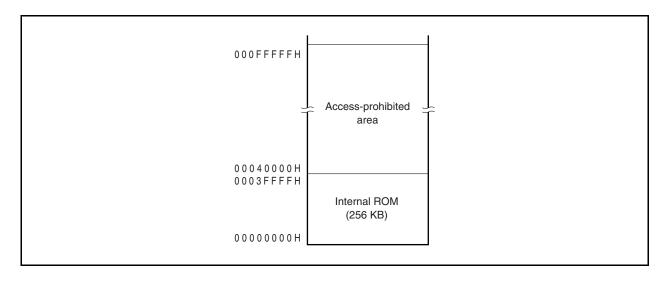

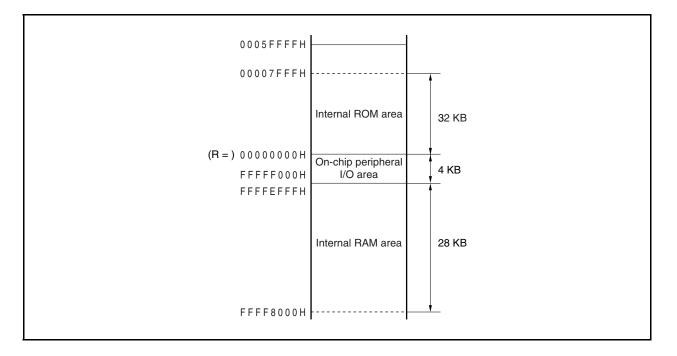

|              | 3.4.3 Memory map                                                                | 67  |

|              | 3.4.4 Areas                                                                     | 69  |

|              | 3.4.5 Recommended use of address space                                          | 77  |

|              | 3.4.6 Peripheral I/O registers                                                  | 80  |

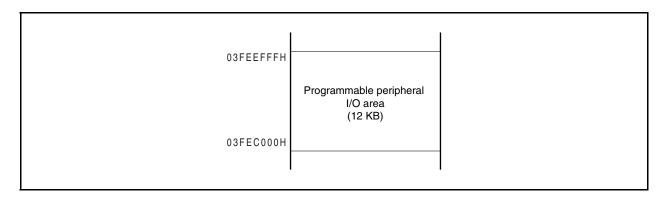

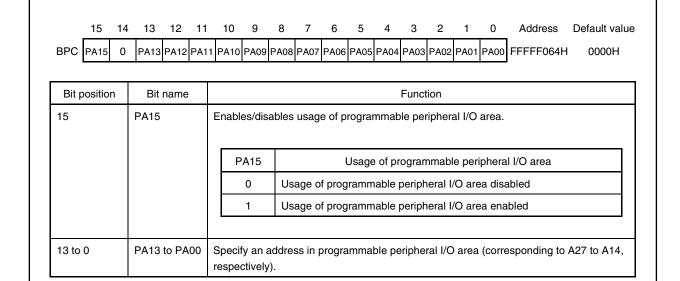

|              | 3.4.7 Programmable peripheral I/O registers                                     | 91  |

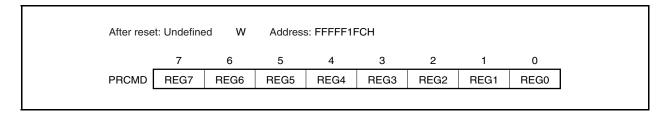

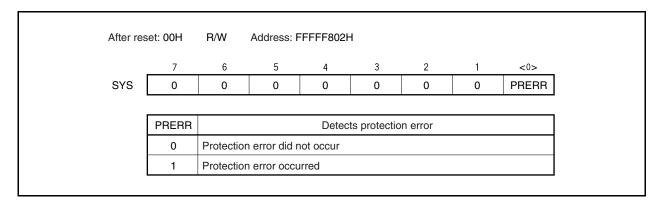

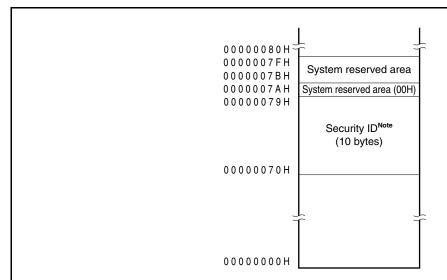

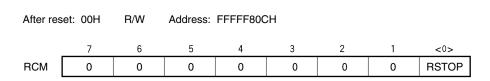

|              | 3.4.8 Special registers                                                         | 92  |

|              | 3.4.9 Cautions                                                                  | 96  |

| CHAPTER      | 4 PORT FUNCTIONS                                                                | 101 |

| 4.1          | Features                                                                        | 101 |

| 4.2          | Basic Port Configuration                                                        |     |

| 4.3          | Port Configuration                                                              |     |

|              | 4.3.1 Port 0                                                                    |     |

|              | 4.3.2 Port 1                                                                    |     |

|              | 4.3.3 Port 3                                                                    |     |

|              | 4.3.4 Port 4                                                                    |     |

|              | 4.3.5 Port 5                                                                    |     |

|              | 4.3.6 Port 7                                                                    | 125 |

|        | 4.3.7    | Port 9                                                                            | 127 |

|--------|----------|-----------------------------------------------------------------------------------|-----|

|        | 4.3.8    | Port CM                                                                           | 135 |

|        | 4.3.9    | Port CT                                                                           | 137 |

|        | 4.3.10   | Port DH                                                                           |     |

|        | 4.3.11   | Port DL                                                                           | 141 |

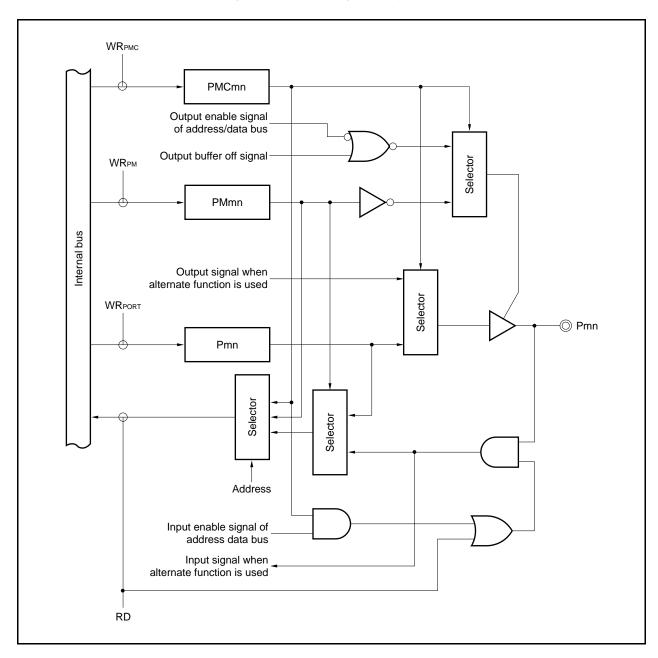

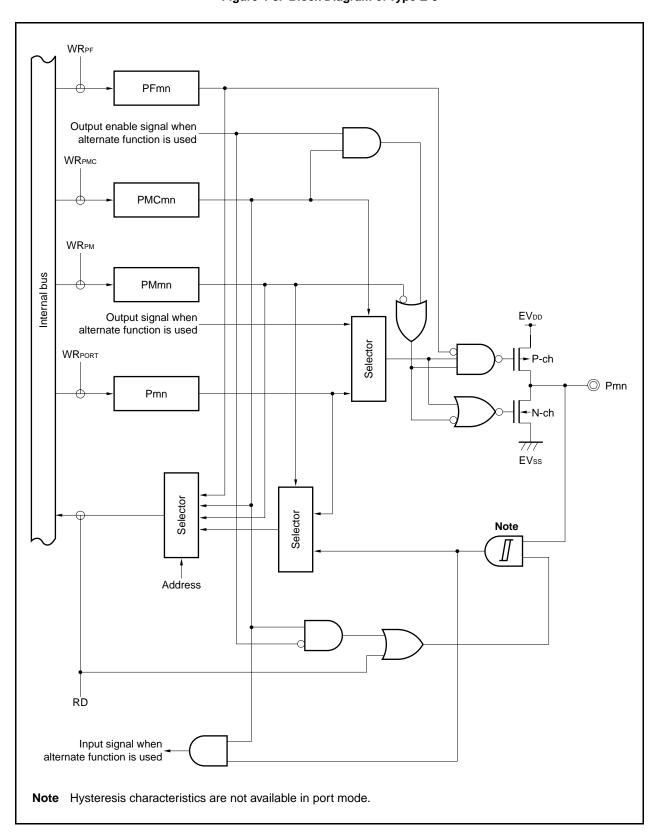

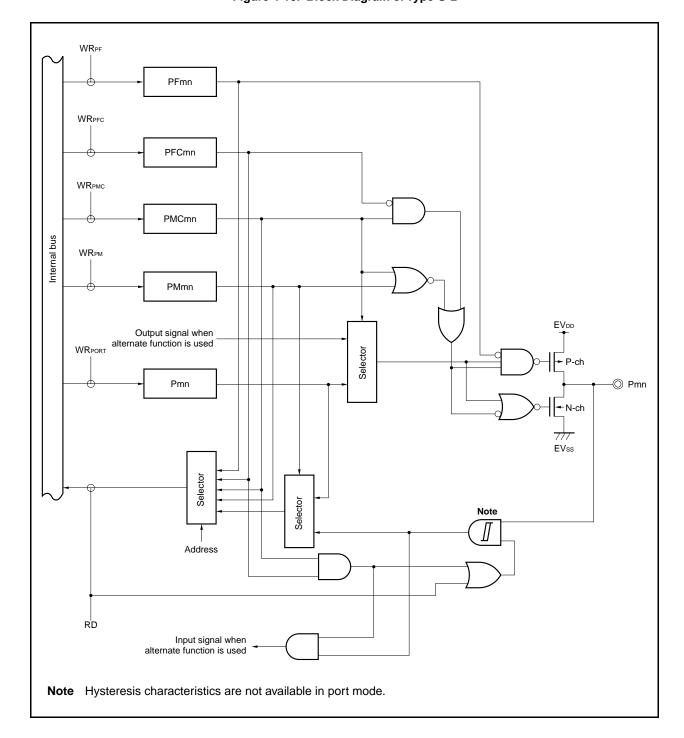

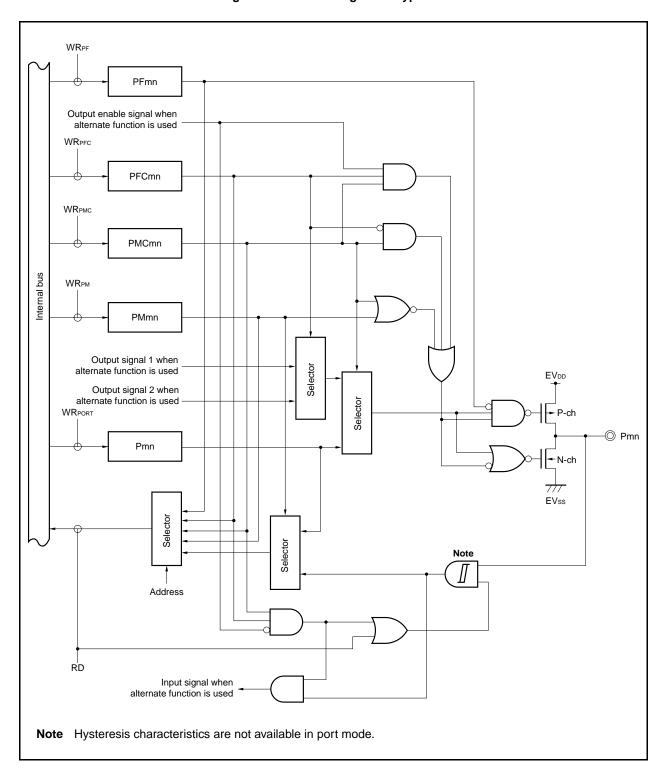

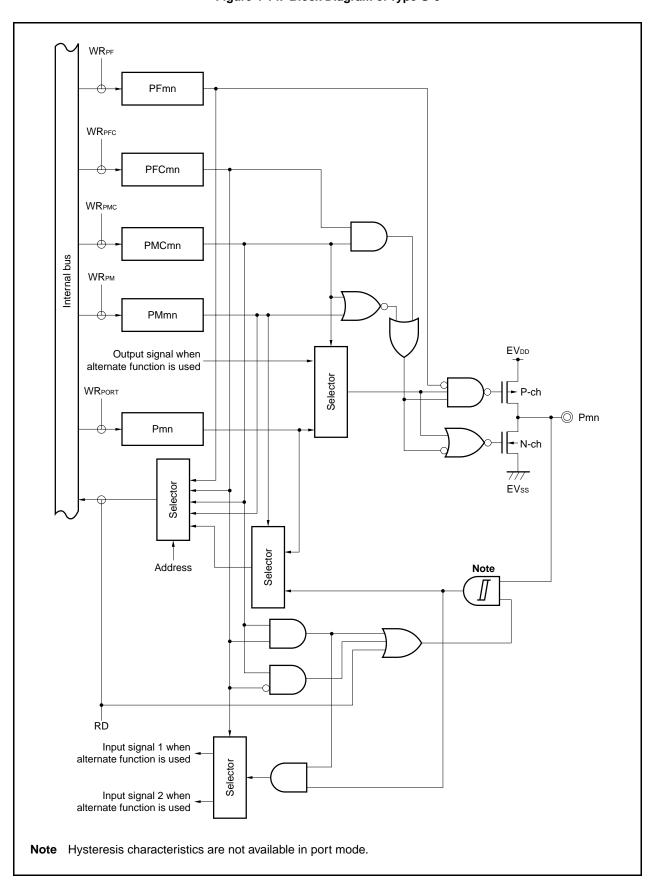

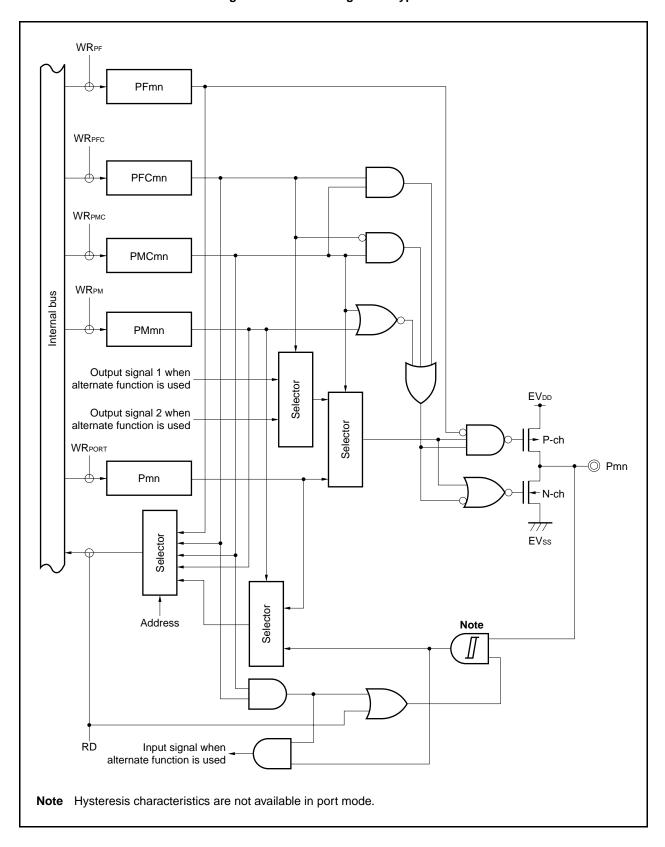

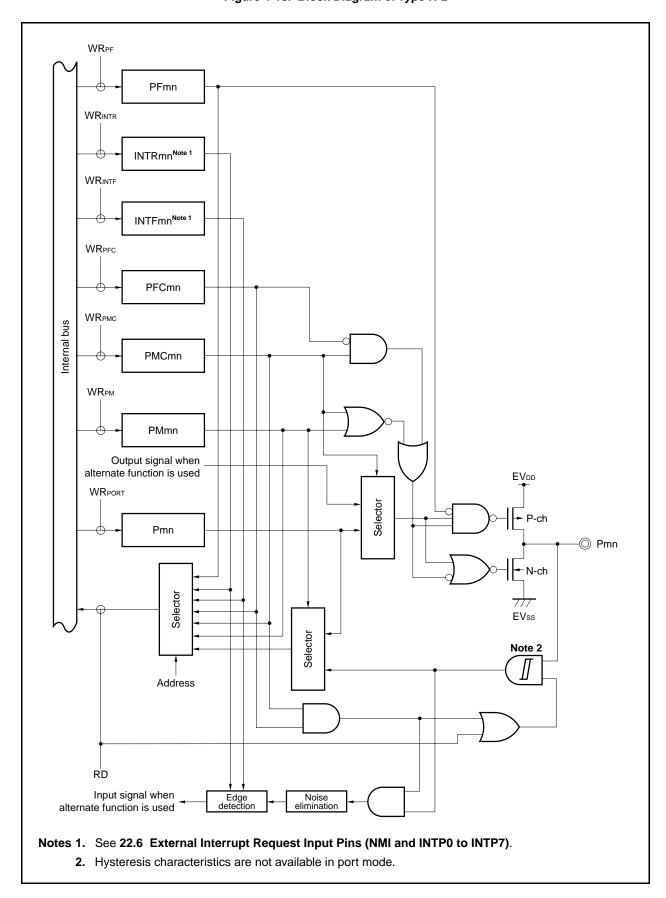

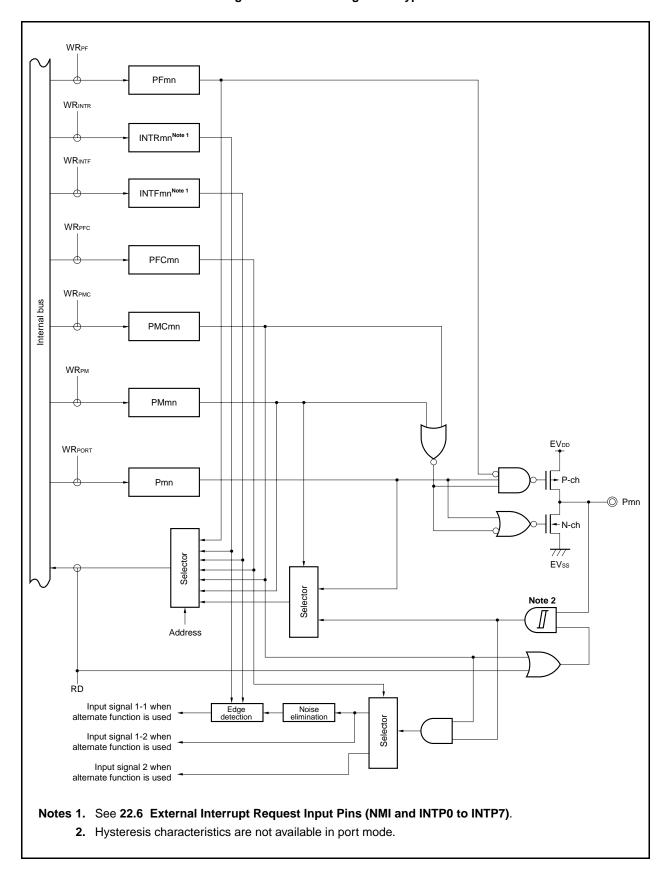

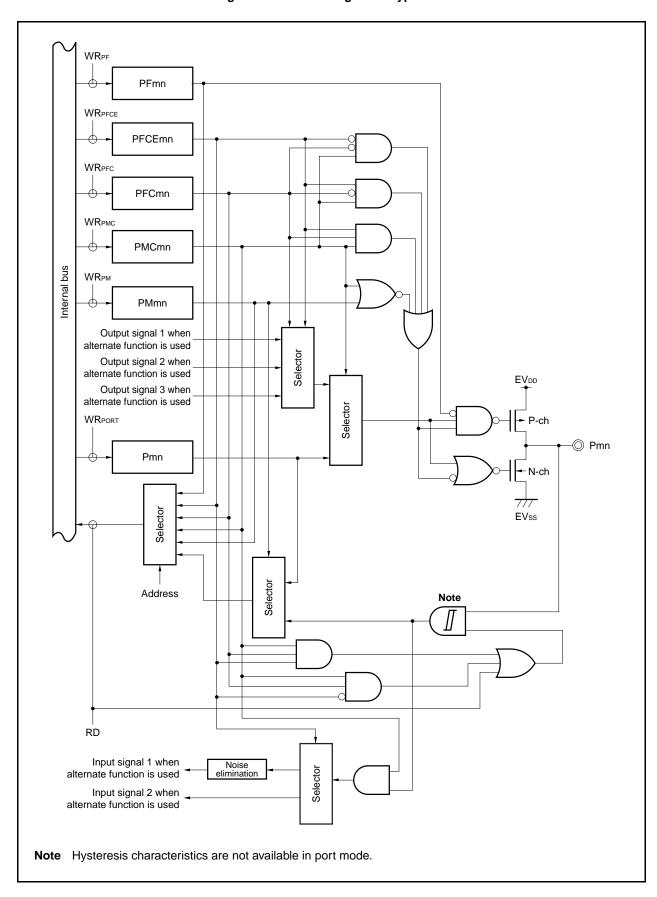

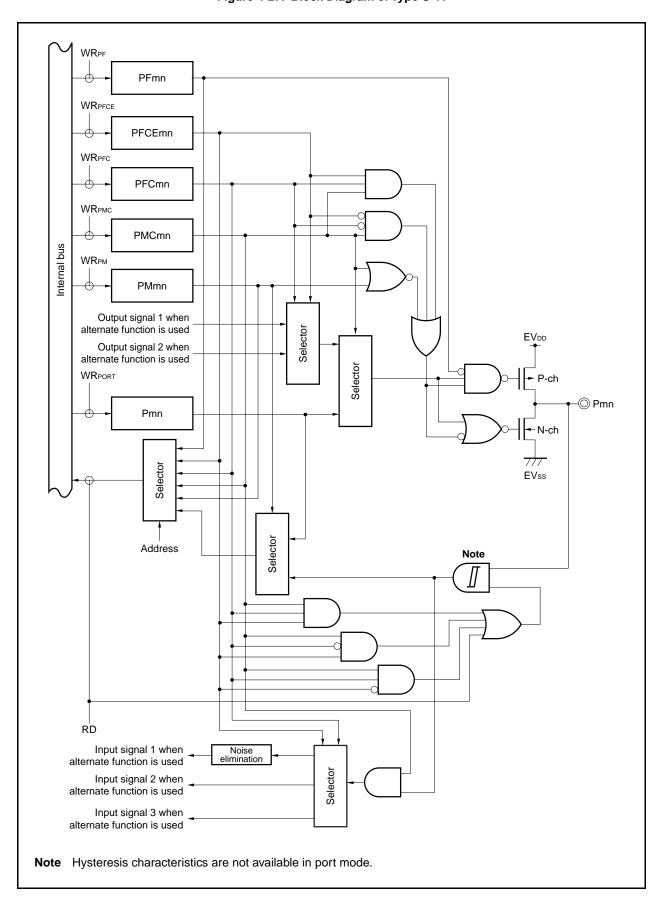

| 4.4    | Block I  | Diagrams                                                                          | 144 |

| 4.5    | Port Re  | egister Settings When Alternate Function Is Used                                  | 174 |

| 4.6    | Cautio   | ns                                                                                | 182 |

|        | 4.6.1    | Cautions on setting port pins                                                     | 182 |

|        | 4.6.2    | Cautions on bit manipulation instruction for port n register (Pn)                 | 185 |

|        | 4.6.3    | Cautions on on-chip debug pins                                                    | 186 |

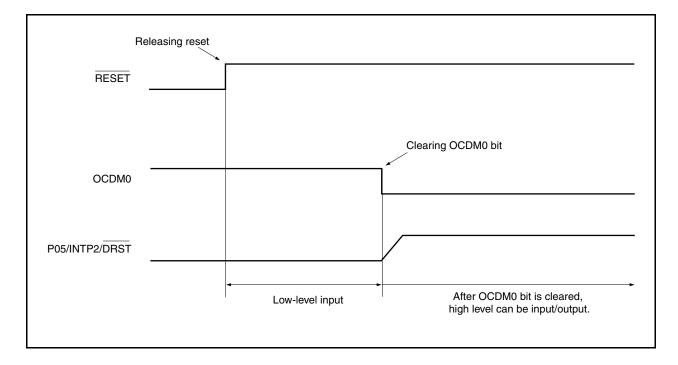

|        | 4.6.4    | Cautions on P05/INTP2/DRST pin                                                    | 186 |

|        | 4.6.5    | Cautions on P10, P11, and P53 pins when power is turned on                        | 186 |

|        | 4.6.6    | Hysteresis characteristics                                                        | 186 |

| CHAPTE | R 5 BUS  | S CONTROL FUNCTION                                                                | 187 |

| 5.1    | Feature  | es                                                                                | 187 |

| 5.2    |          | ontrol Pins                                                                       |     |

|        | 5.2.1    | Pin status when internal ROM, internal RAM, or on-chip peripheral I/O is accessed |     |

|        | 5.2.2    | Pin status in each operation mode                                                 |     |

| 5.3    |          | y Block Function                                                                  |     |

| 5.4    |          | al Bus Interface Mode Control Function                                            |     |

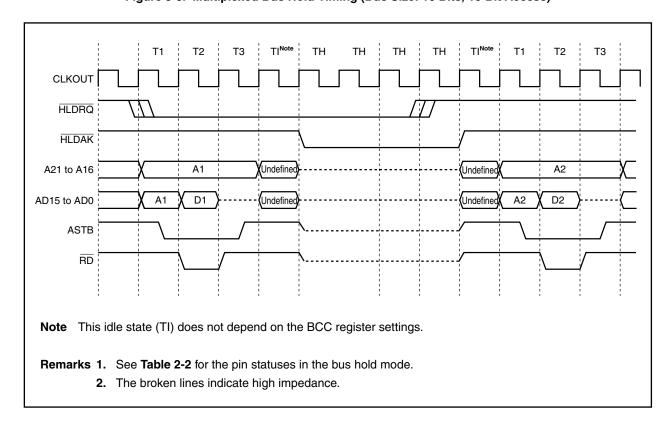

| 5.5    |          | ccess                                                                             |     |

|        | 5.5.1    | Number of clocks for access                                                       |     |

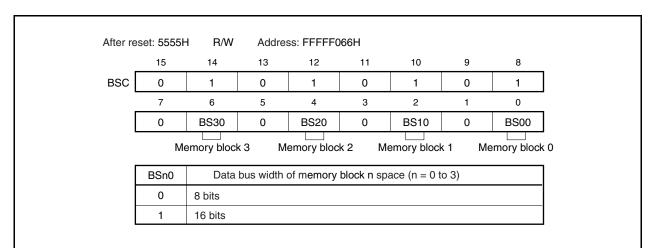

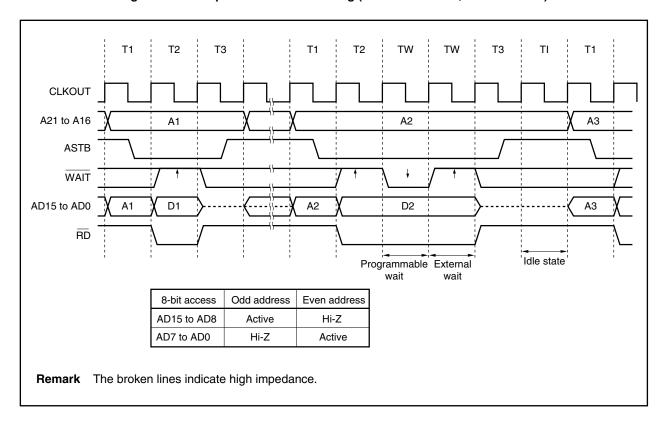

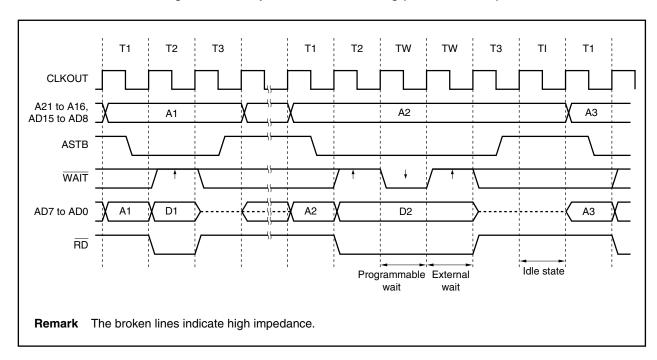

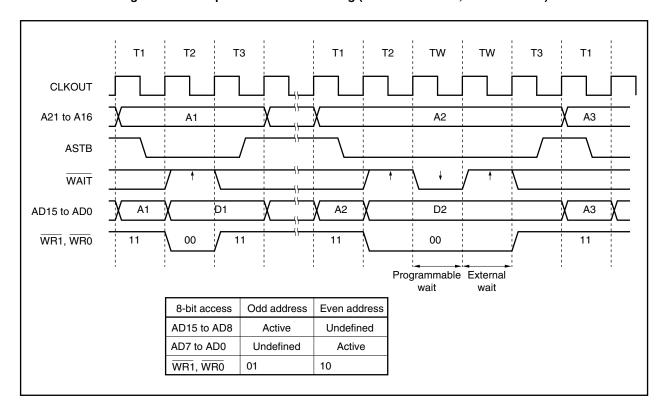

|        | 5.5.2    | Bus size setting function                                                         | 191 |

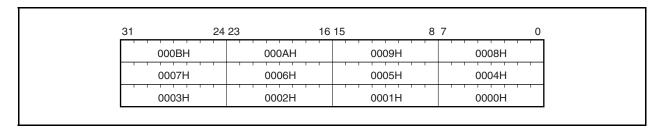

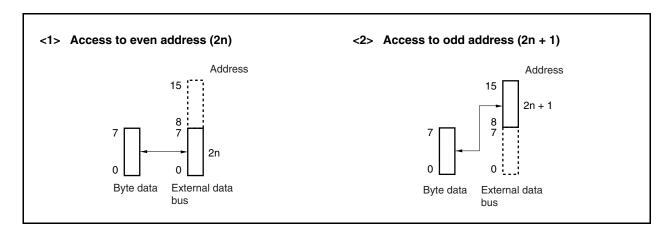

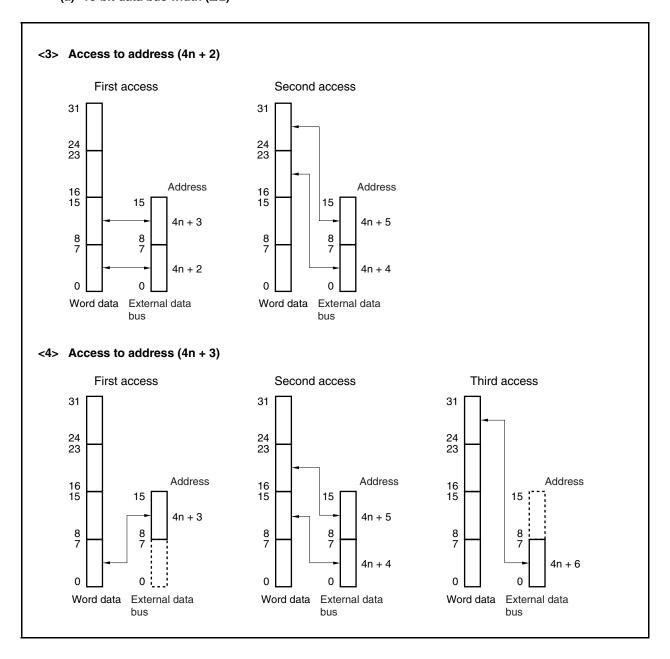

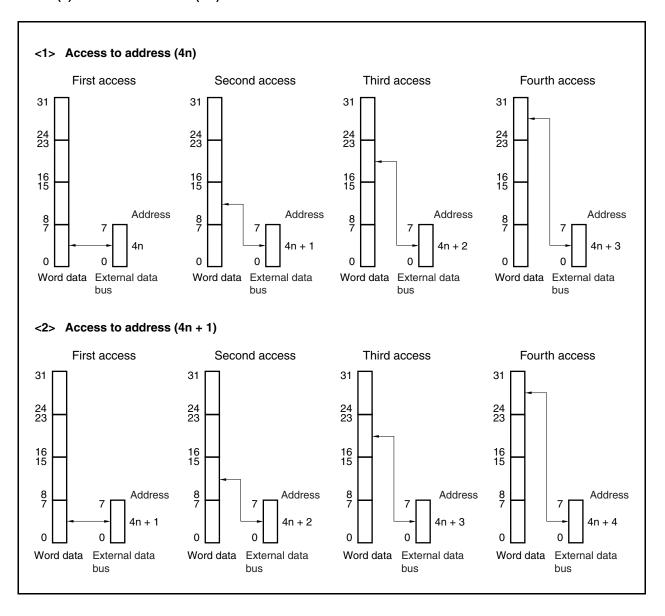

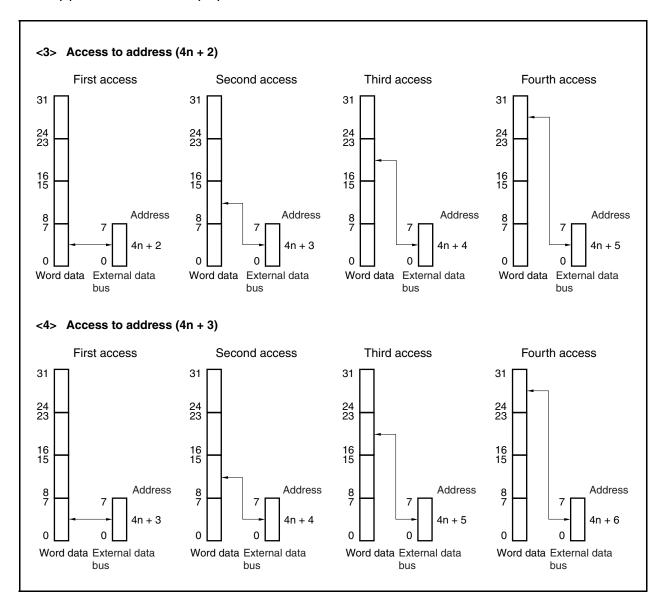

|        | 5.5.3    | Access by bus size                                                                |     |

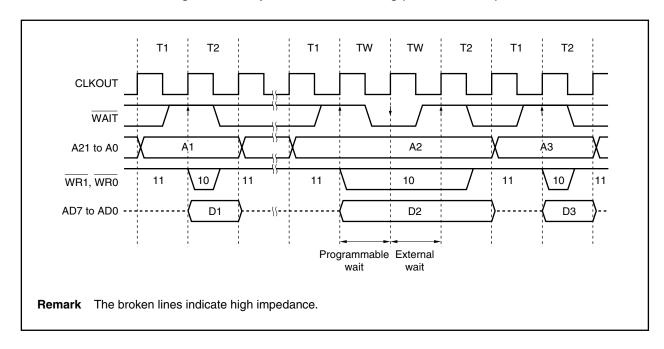

| 5.6    | Wait Fu  | unction                                                                           | 199 |

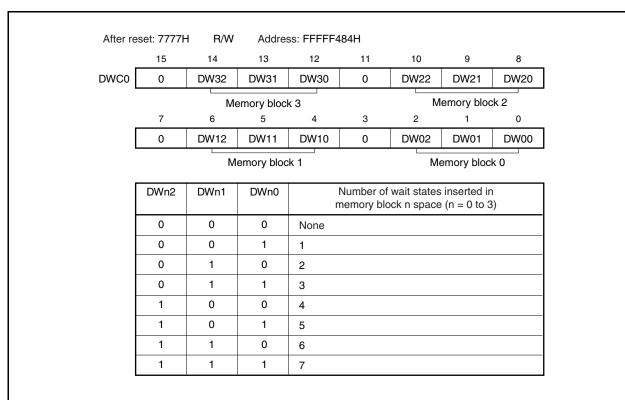

|        | 5.6.1    | Programmable wait function                                                        | 199 |

|        | 5.6.2    | External wait function                                                            | 200 |

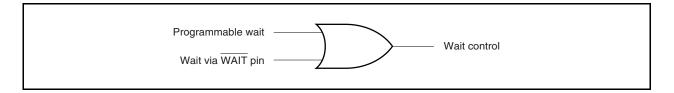

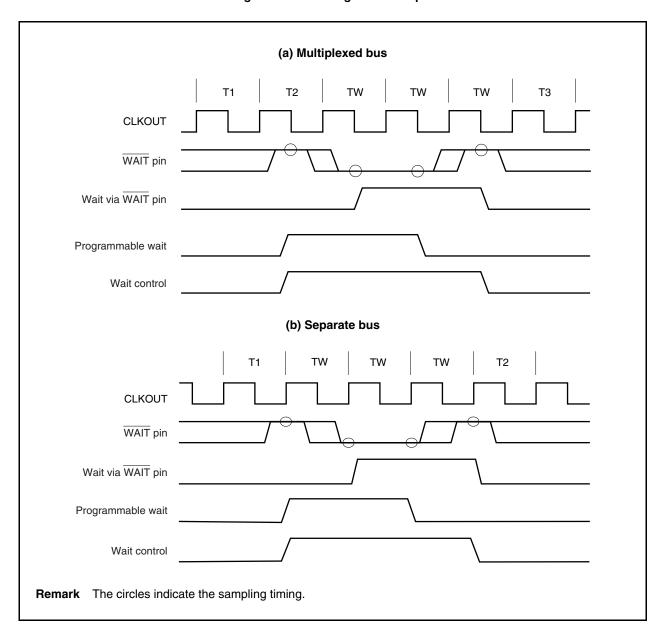

|        | 5.6.3    | Relationship between programmable wait and external wait                          | 201 |

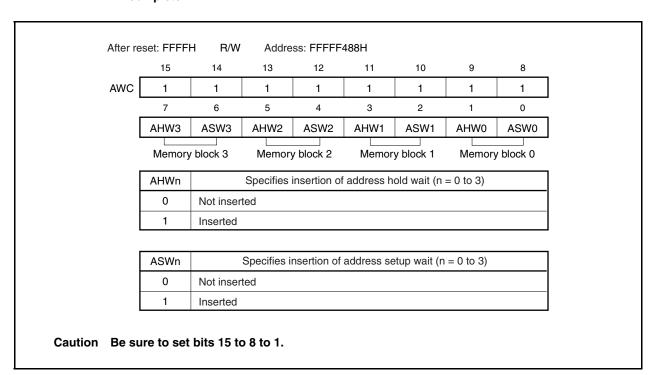

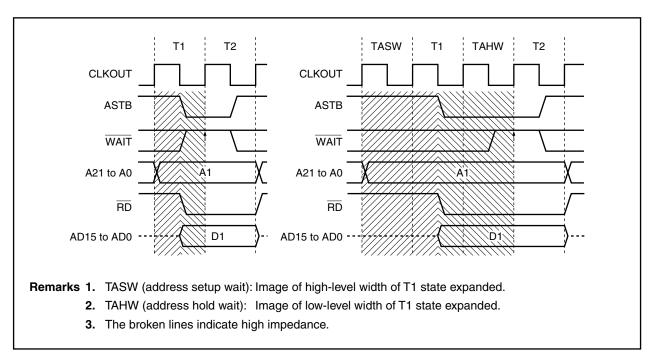

|        | 5.6.4    | Programmable address wait function                                                | 202 |

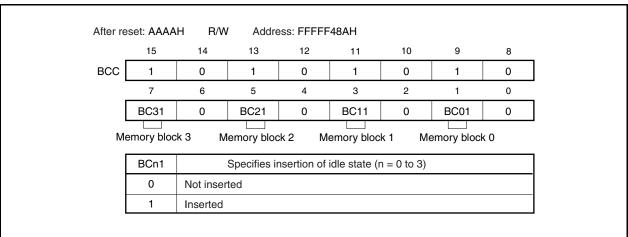

| 5.7    | Idle Sta | ate Insertion Function                                                            | 203 |

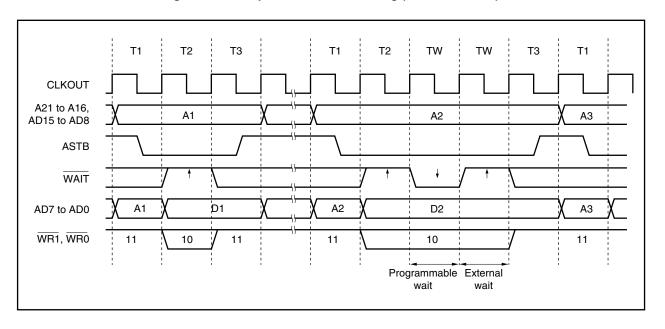

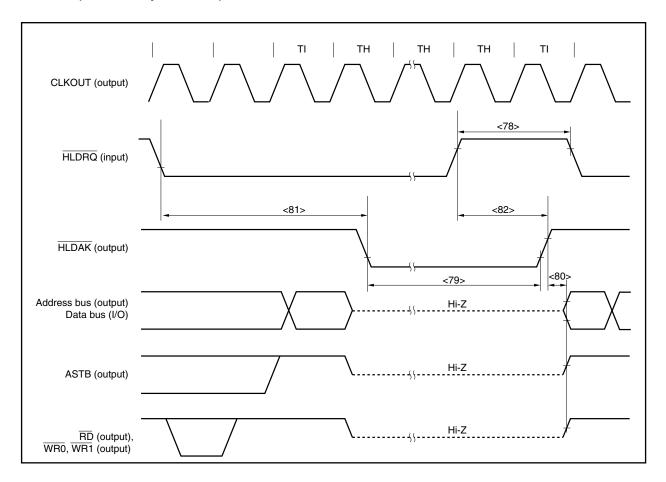

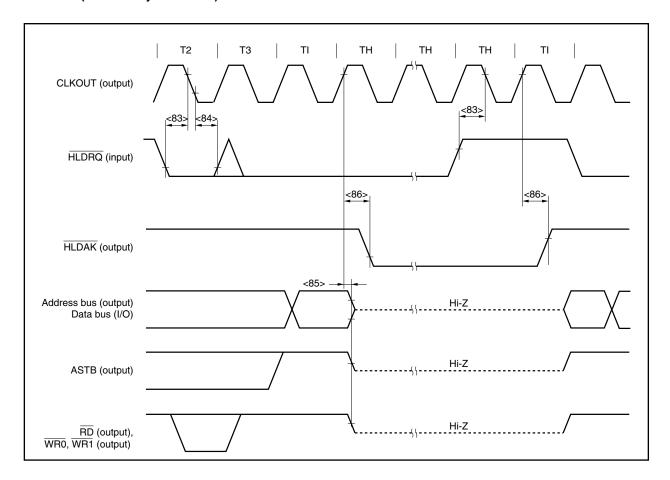

| 5.8    | Bus Ho   | old Function                                                                      | 204 |

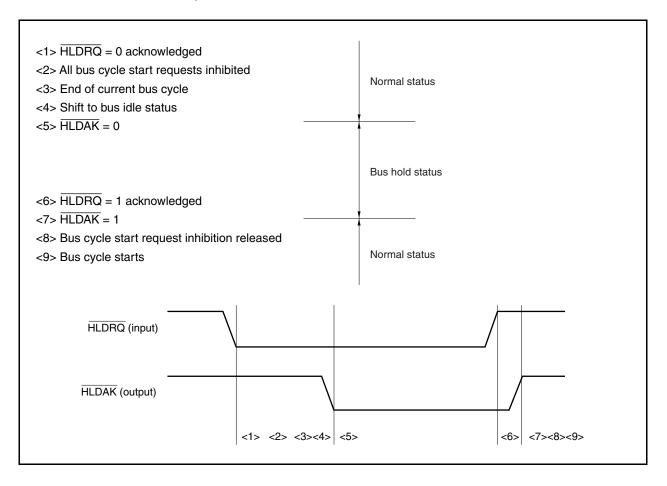

|        | 5.8.1    | Functional outline                                                                | 204 |

|        | 5.8.2    | Bus hold procedure                                                                | 205 |

|        | 5.8.3    | Operation in power save mode                                                      | 205 |

| 5.9    | Bus Pr   | iority                                                                            | 206 |

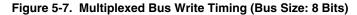

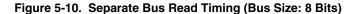

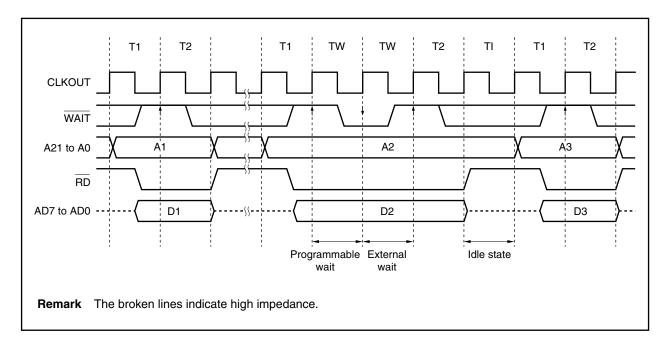

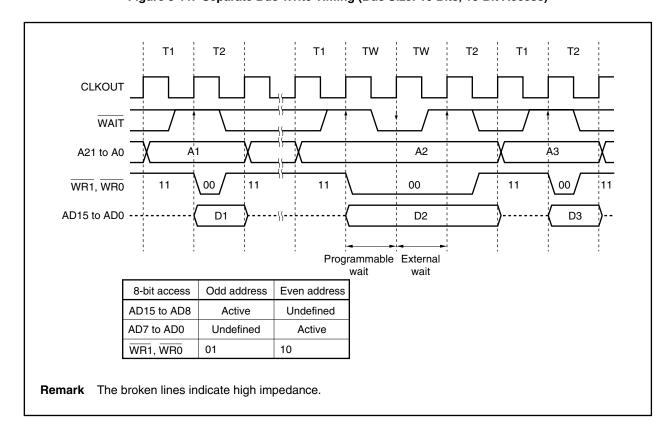

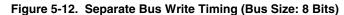

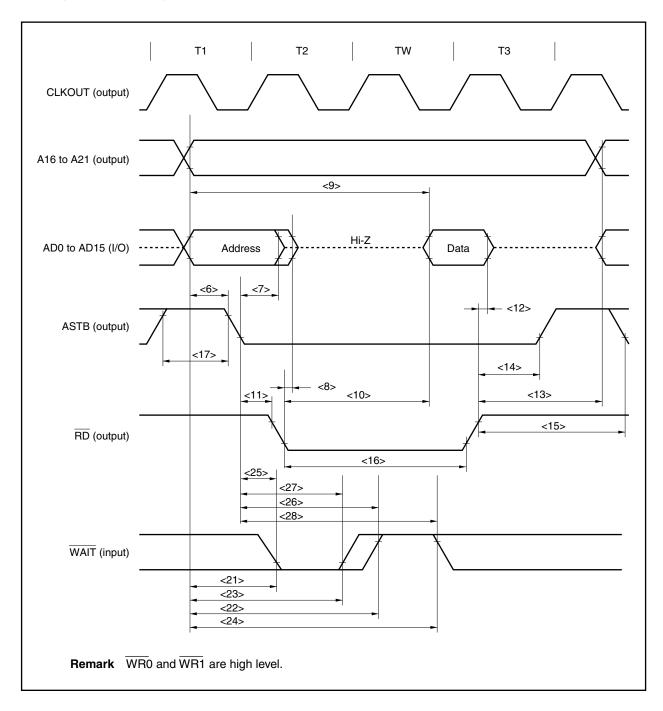

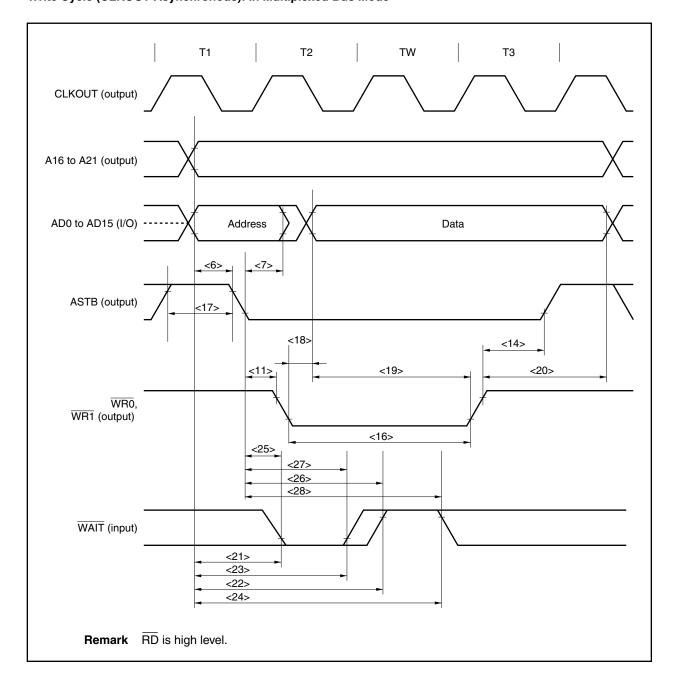

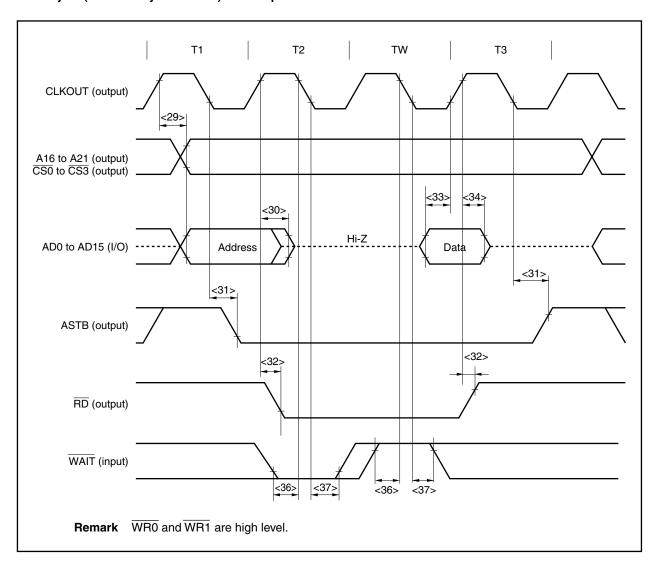

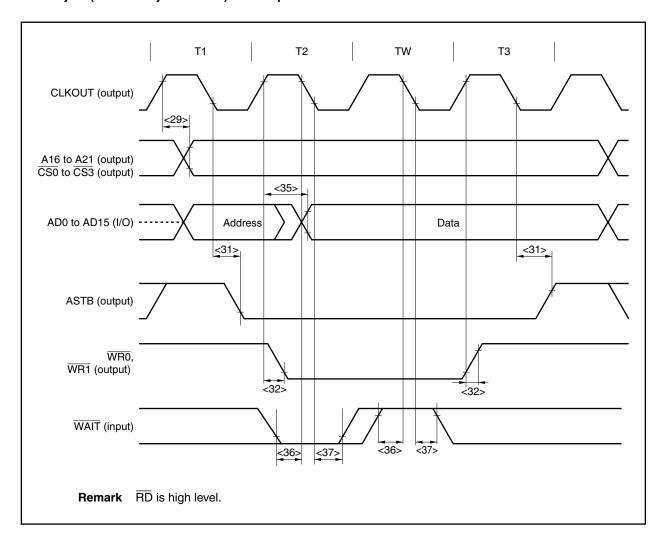

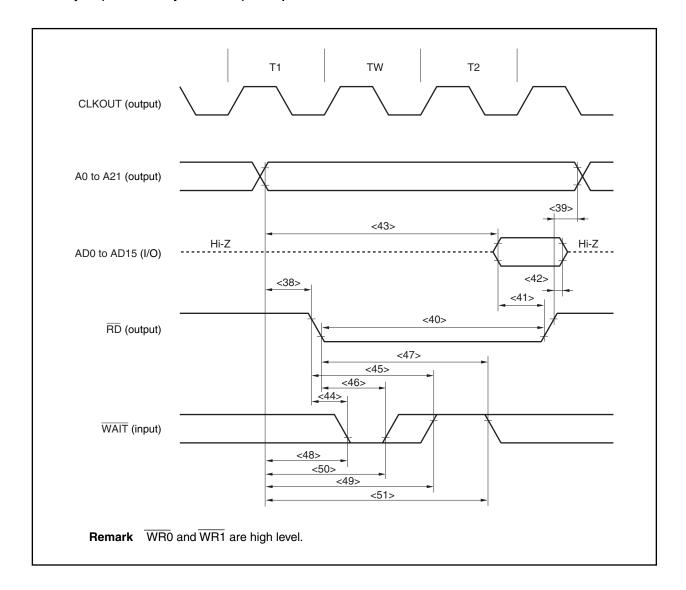

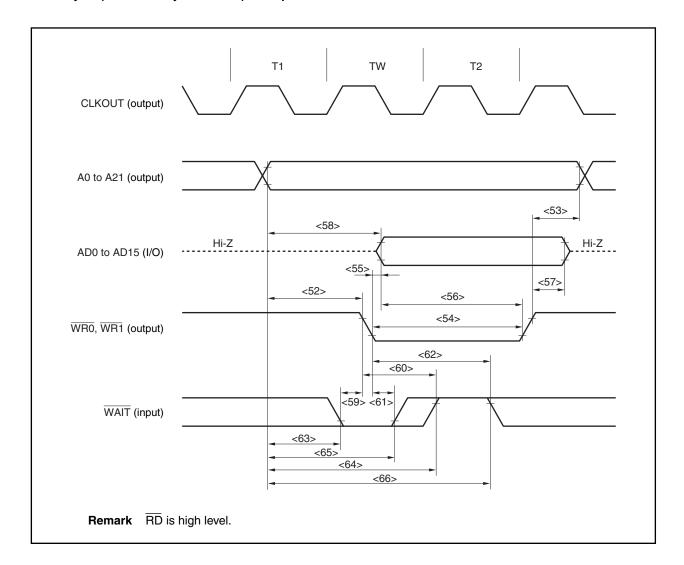

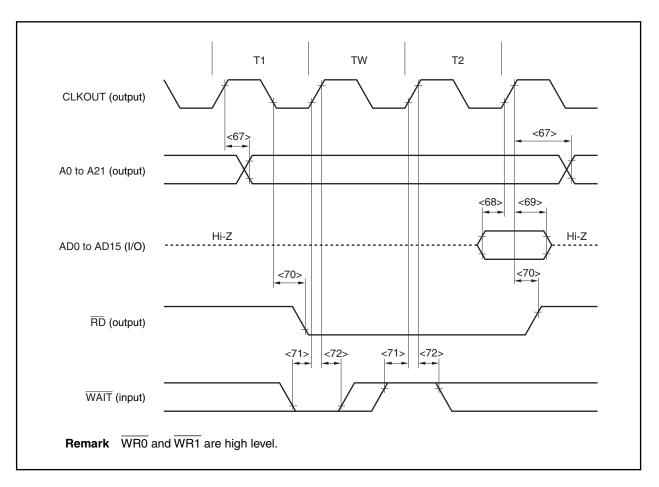

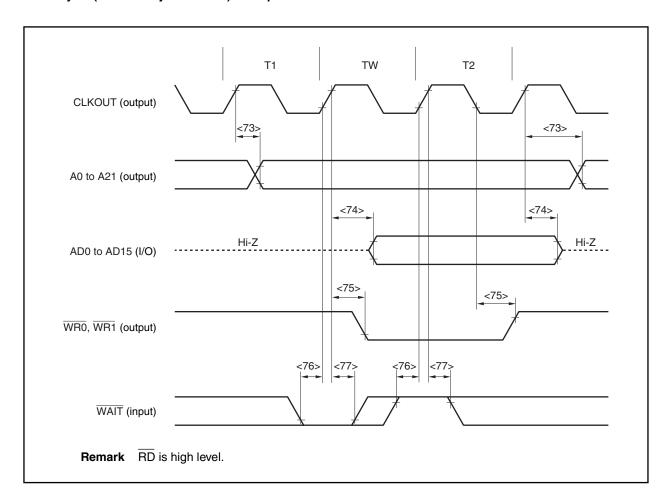

| 5.10   | Bus Ti   | ming                                                                              | 207 |

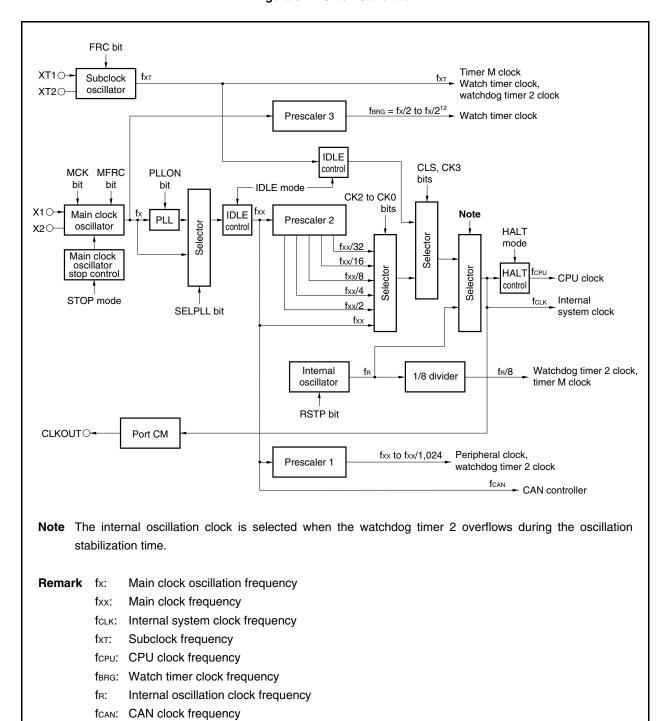

| CHAPTE | R 6 CLC  | OCK GENERATION FUNCTION                                                           | 213 |

| 6.1    |          | ew                                                                                |     |

| 6.2    | _        | urationuration                                                                    |     |

| 6.3    | •        | ers                                                                               |     |

| 6.4    | •        | ion                                                                               |     |

|        | 6.4.1    | Operation of each clock                                                           |     |

|        | 6.4.2    | Clock output function                                                             |     |

| 6.5    | PLL Fu   | ınction                                                                           |     |

|        | 6.5.1    | Overview                                                                          | 222 |

|       |            | 6.5.2          | Registers                                                                                                         | 222   |

|-------|------------|----------------|-------------------------------------------------------------------------------------------------------------------|-------|

|       |            | 6.5.3          | Usage                                                                                                             | 226   |

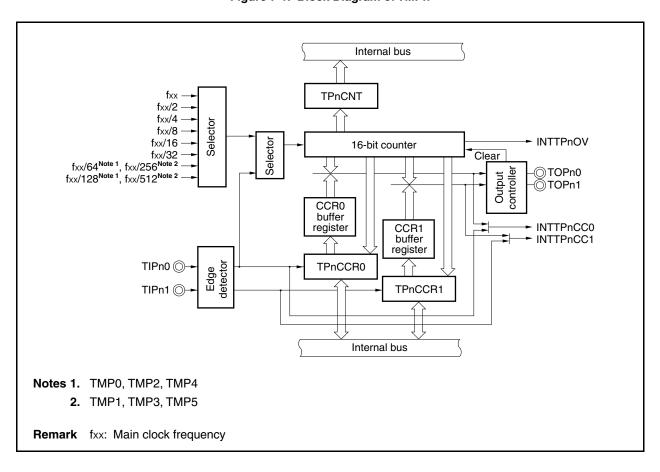

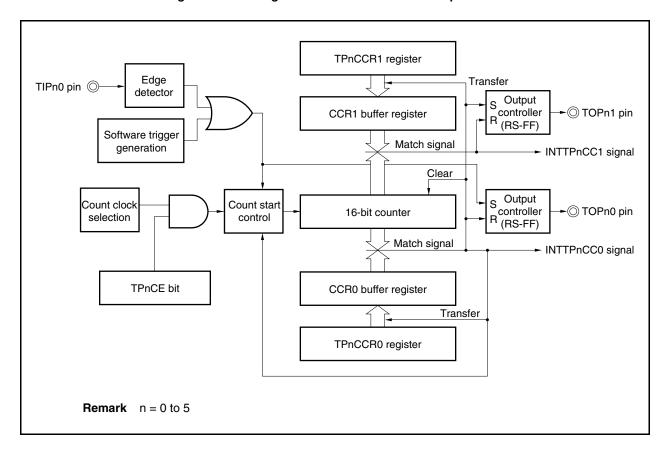

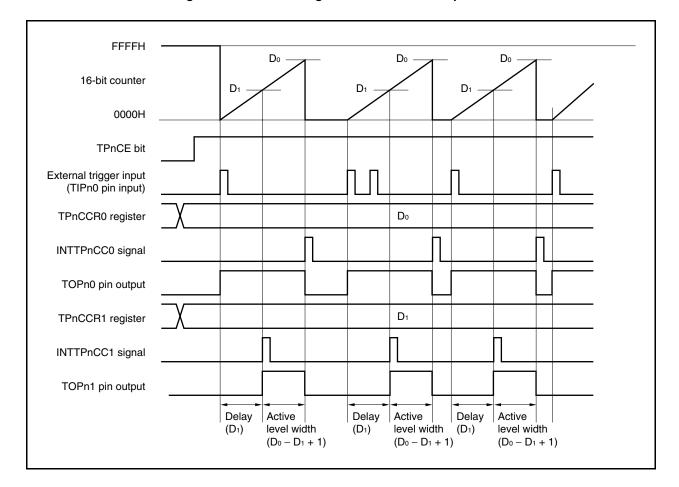

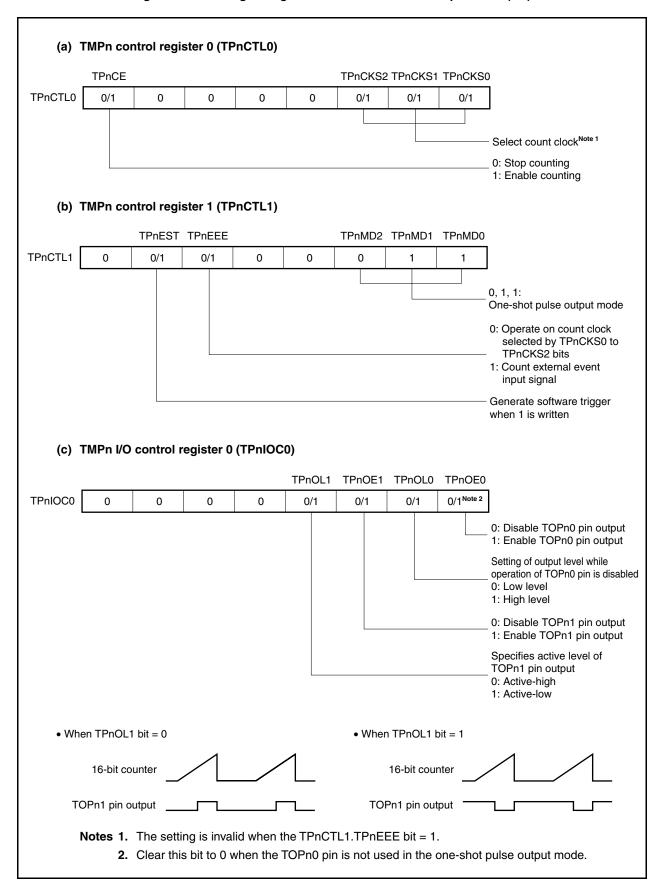

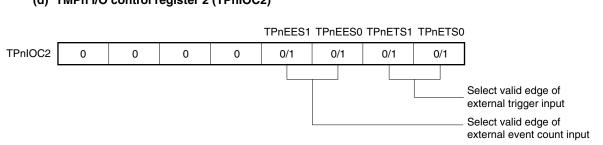

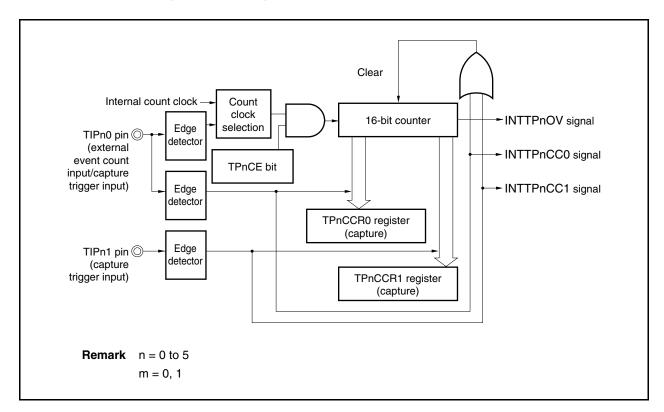

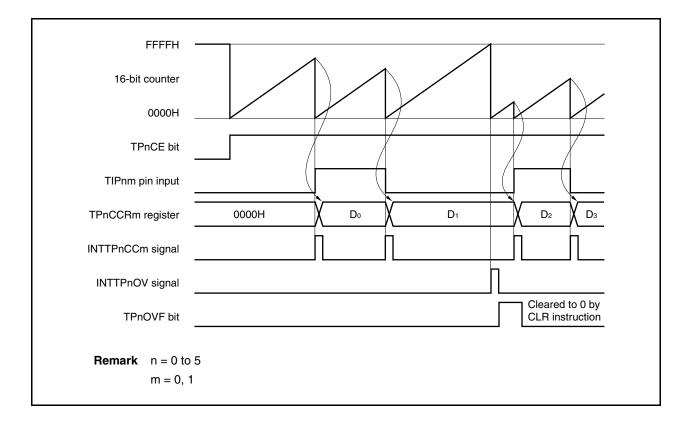

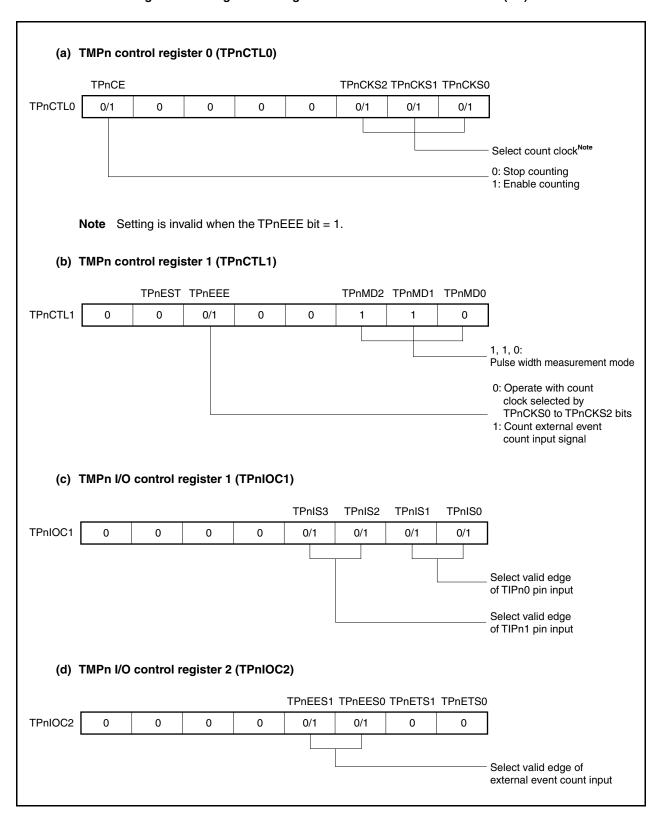

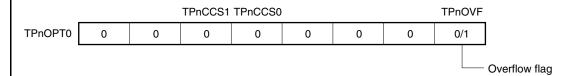

| CHAD  | TER        | 7 16-          | BIT TIMER/EVENT COUNTER P (TMP)                                                                                   | 227   |

|       | '.1        |                | ew                                                                                                                |       |

|       | . i<br>'.2 |                | ons                                                                                                               |       |

|       | .2<br>'.3  |                | uration                                                                                                           |       |

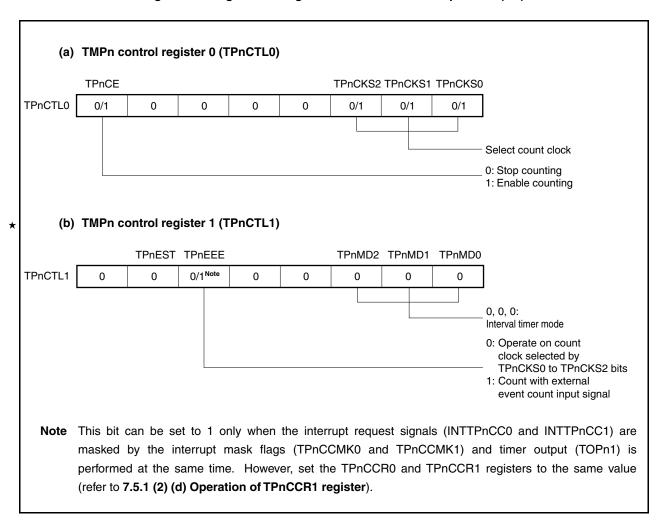

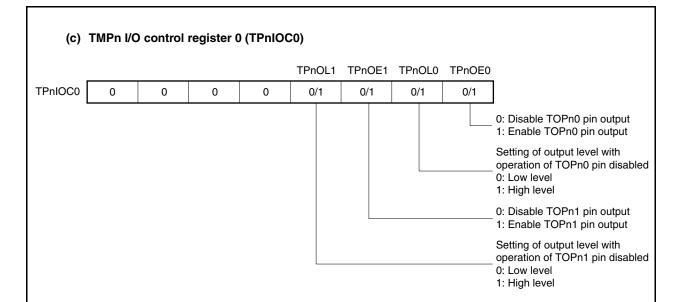

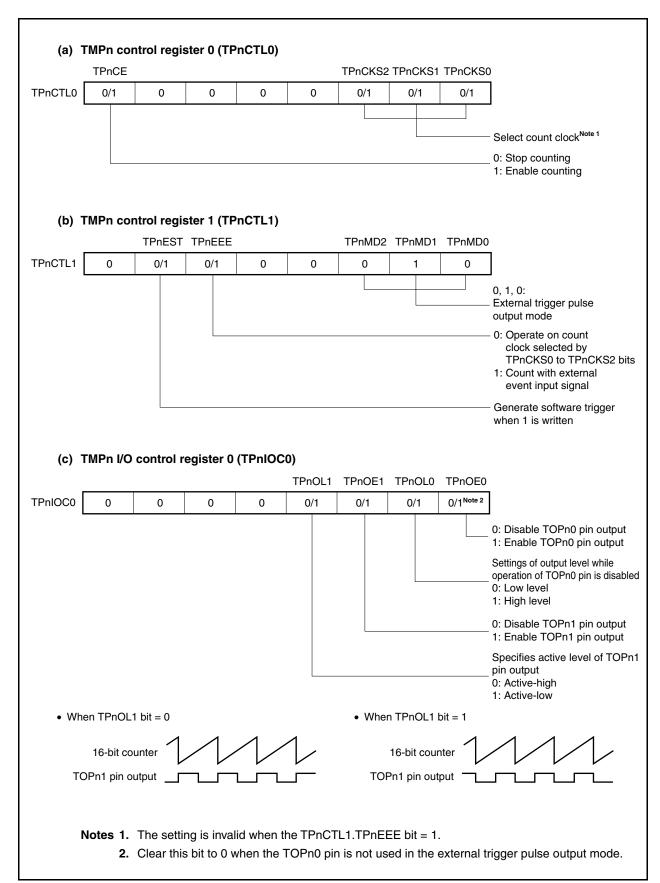

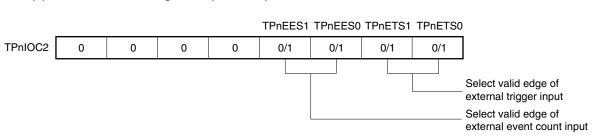

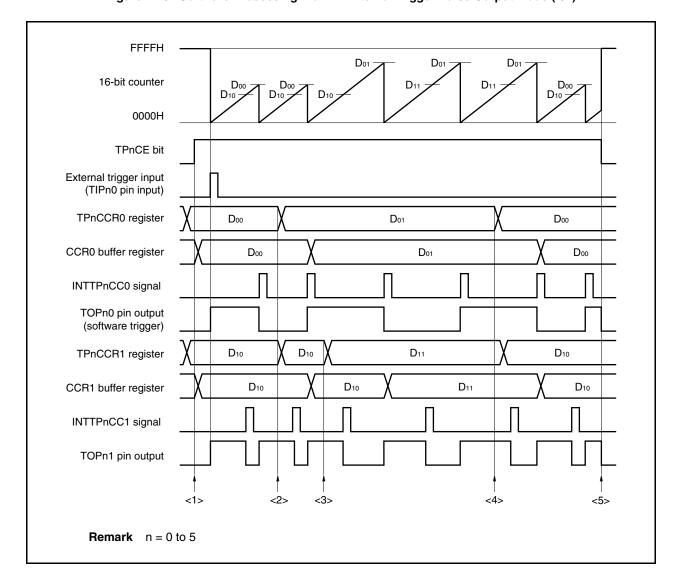

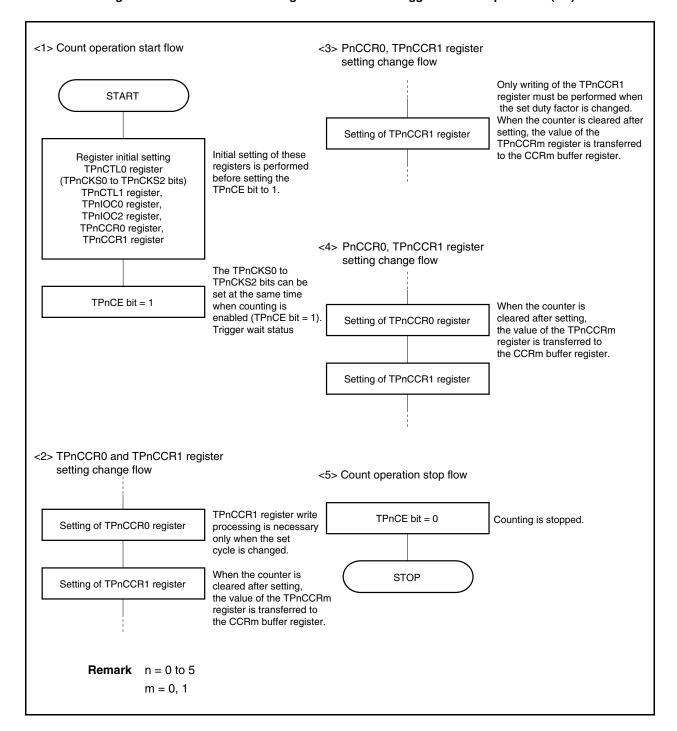

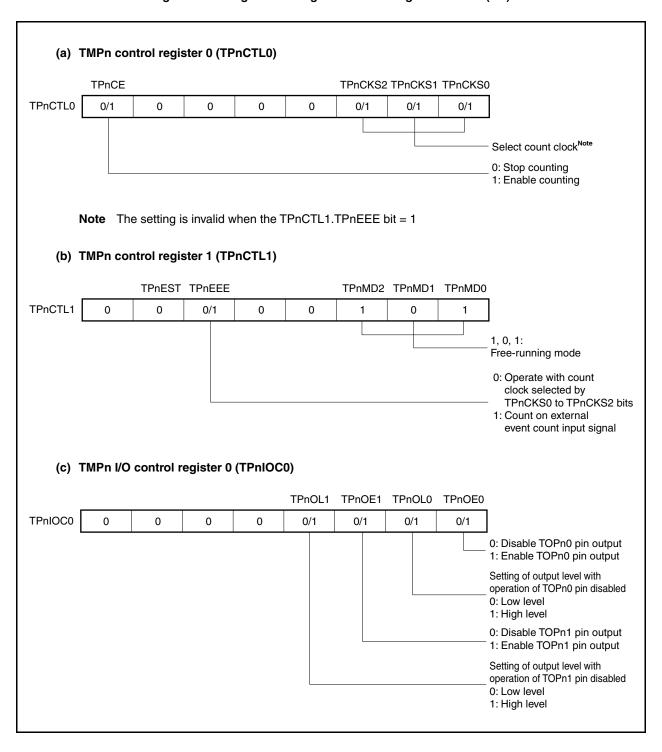

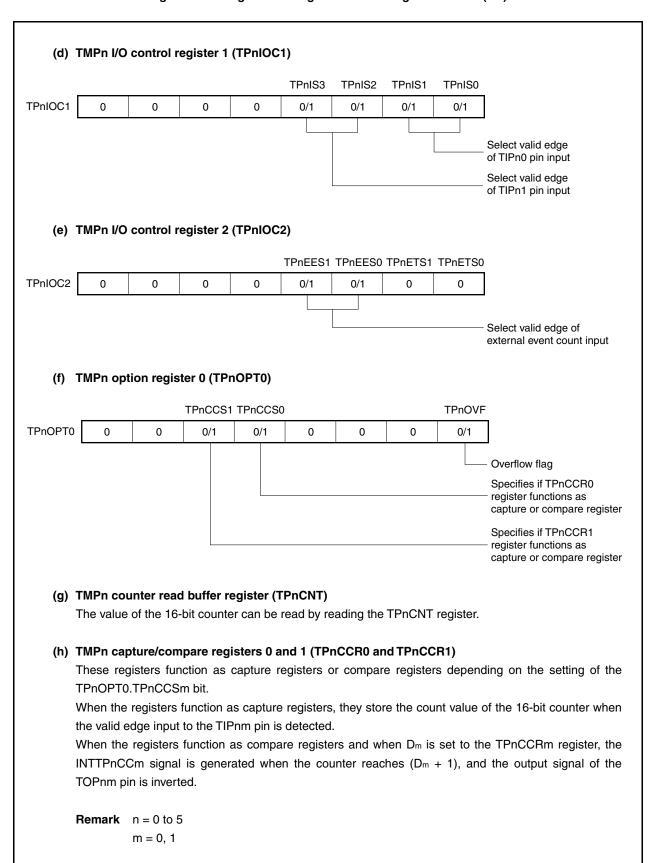

|       | .3<br>'.4  | _              | ers                                                                                                               |       |

|       | .5         | 9              | tion                                                                                                              |       |

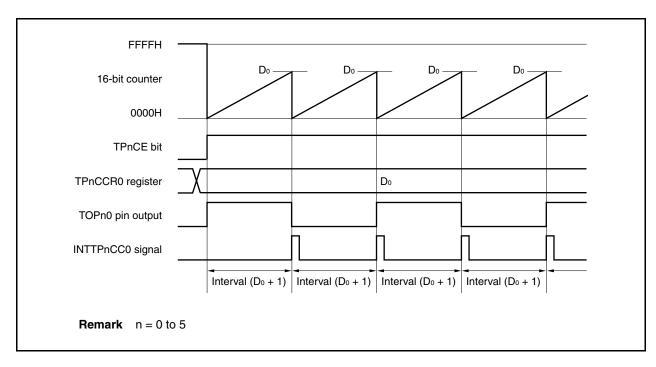

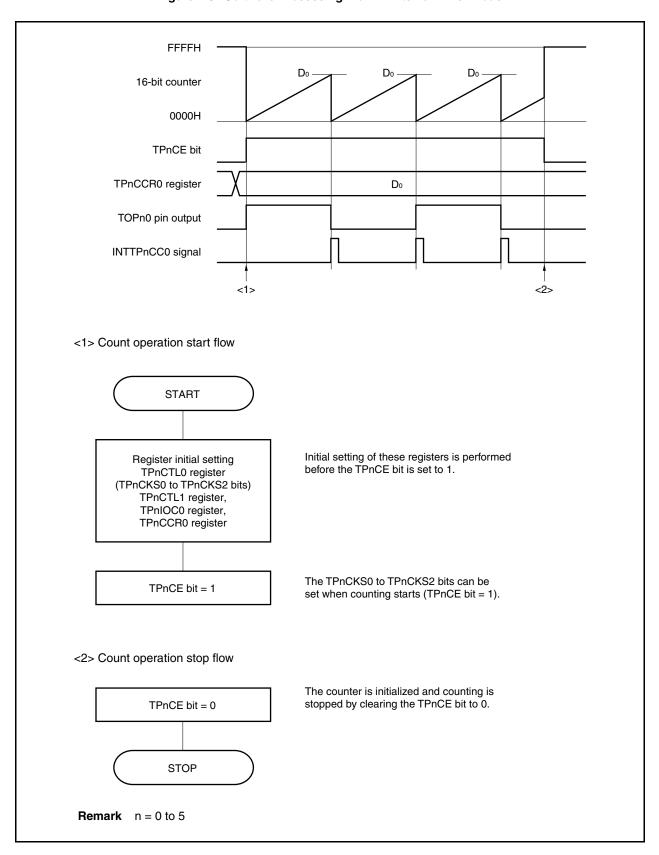

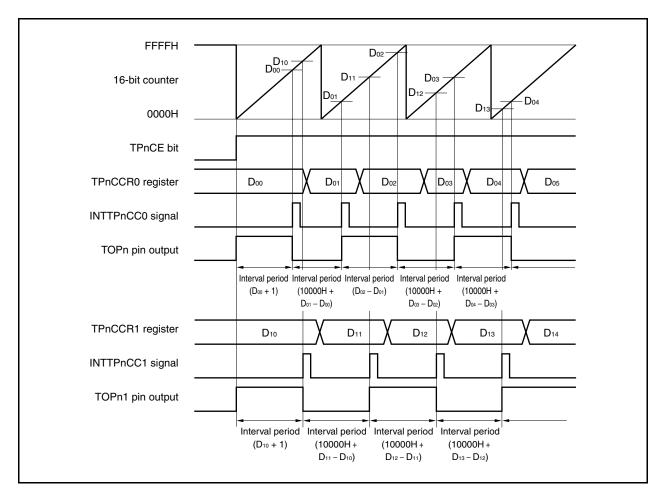

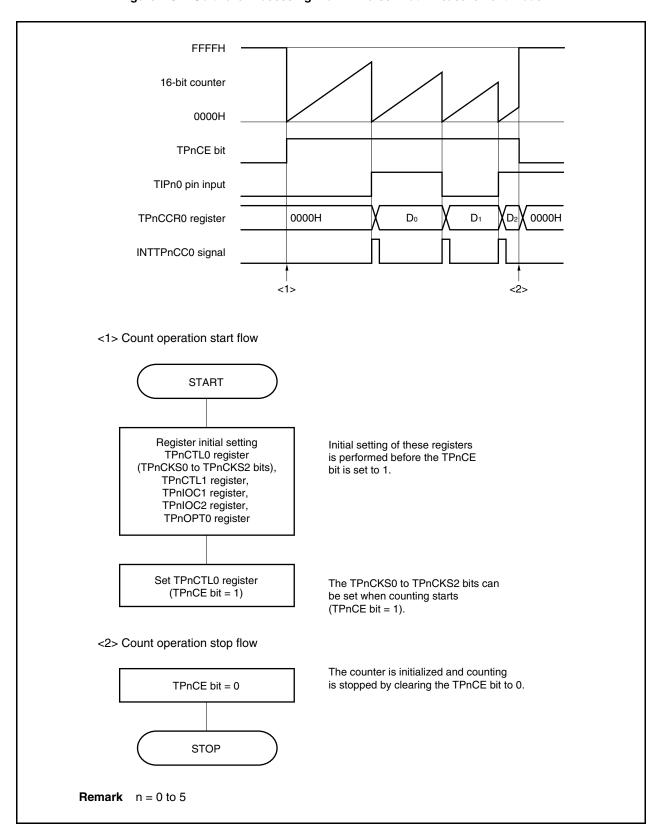

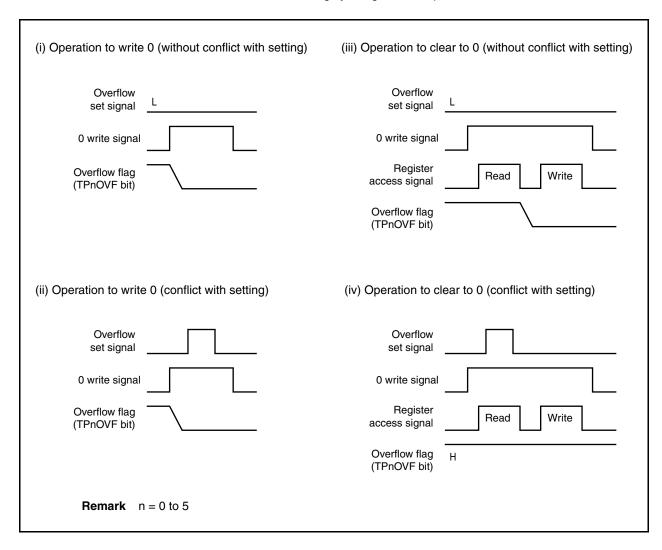

| •     | .0         | 7.5.1          | Interval timer mode (TPnMD2 to TPnMD0 bits = 000)                                                                 |       |

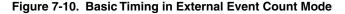

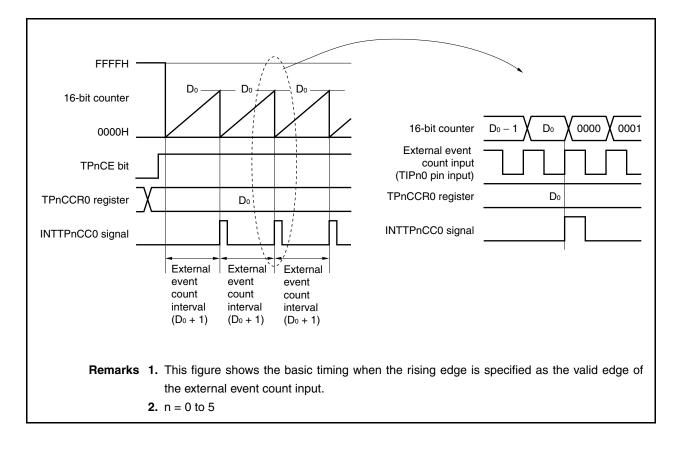

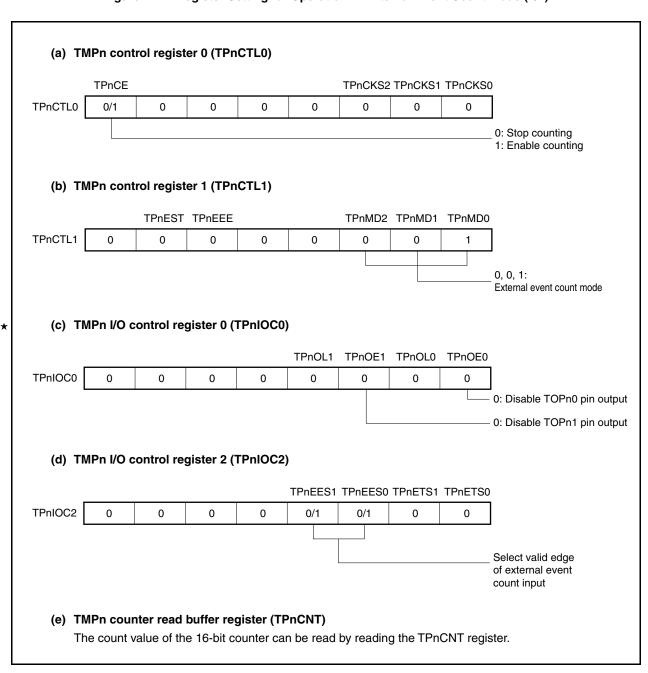

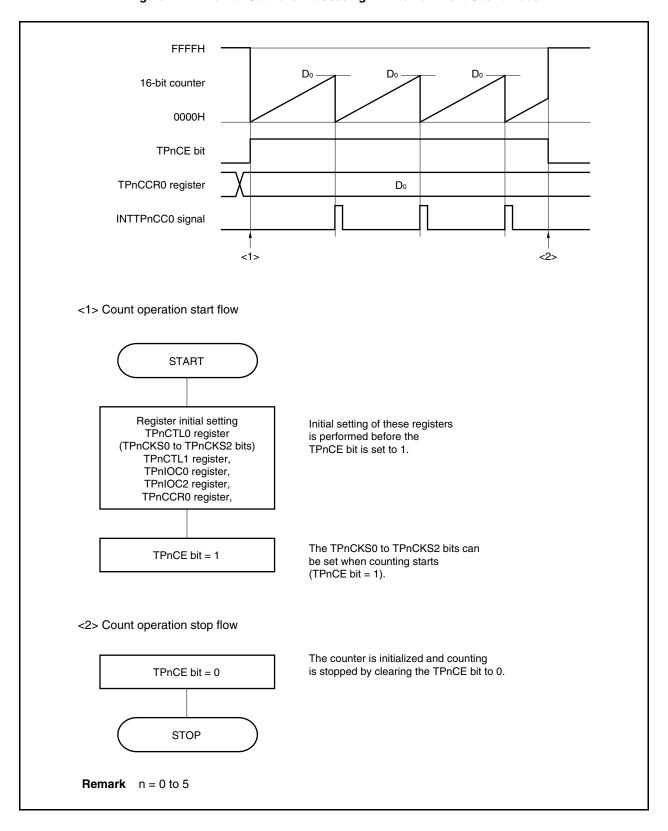

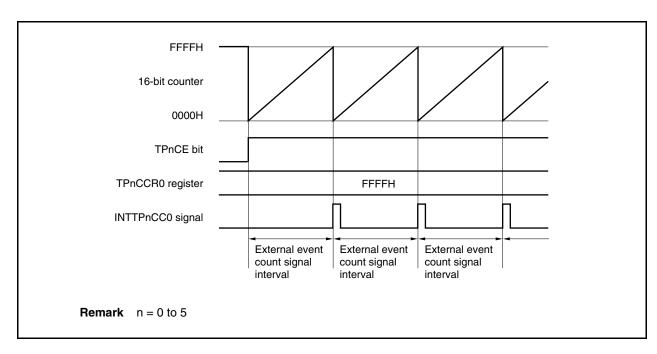

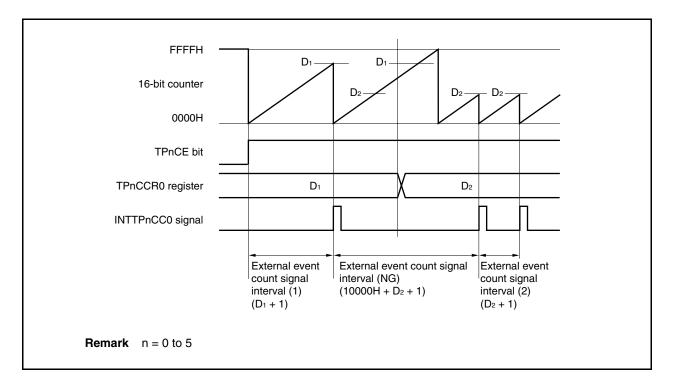

|       |            | 7.5.2          | External event count mode (TPnMD2 to TPnMD0 bits = 001)                                                           |       |

|       |            | 7.5.3          | External trigger pulse output mode (TPnMD2 to TPnMD0 bits = 010)                                                  |       |

|       |            | 7.5.4          | One-shot pulse output mode (TPnMD2 to TPnMD0 bits = 011)                                                          |       |

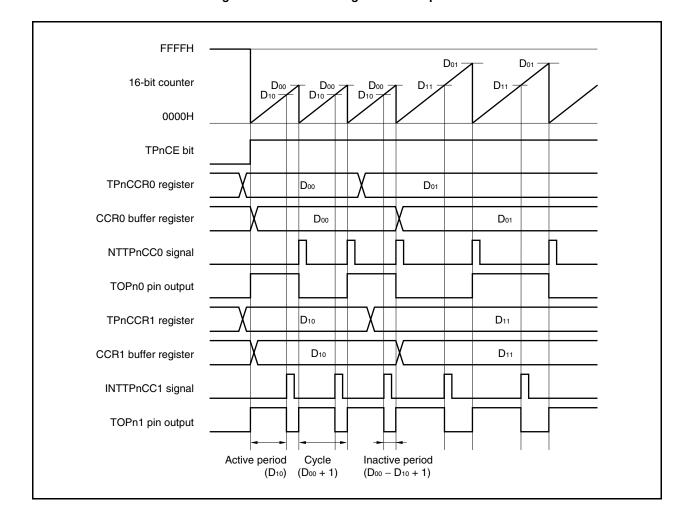

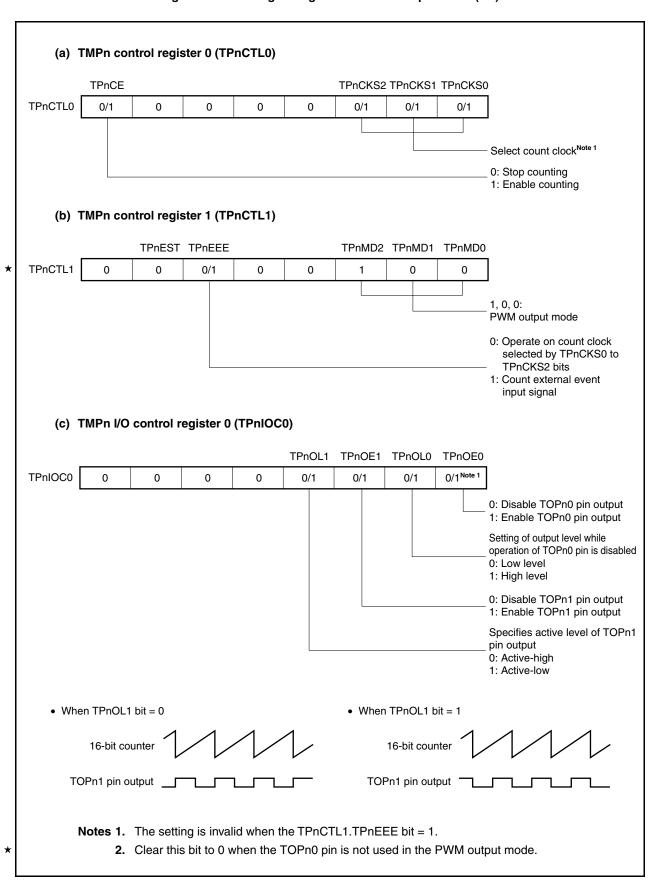

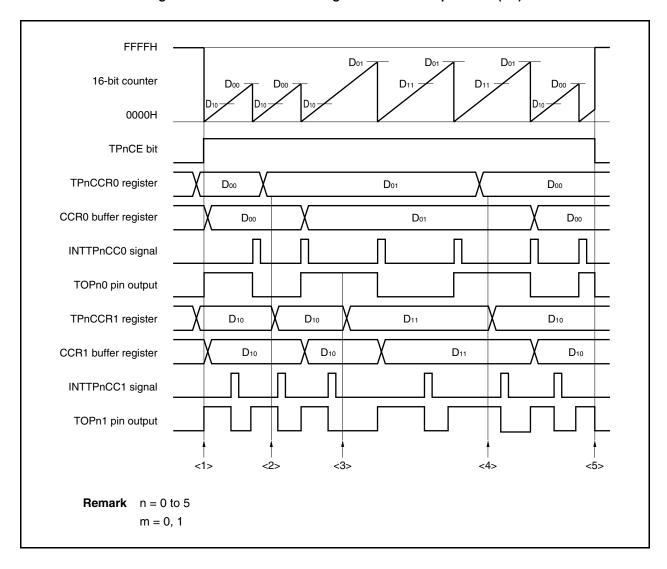

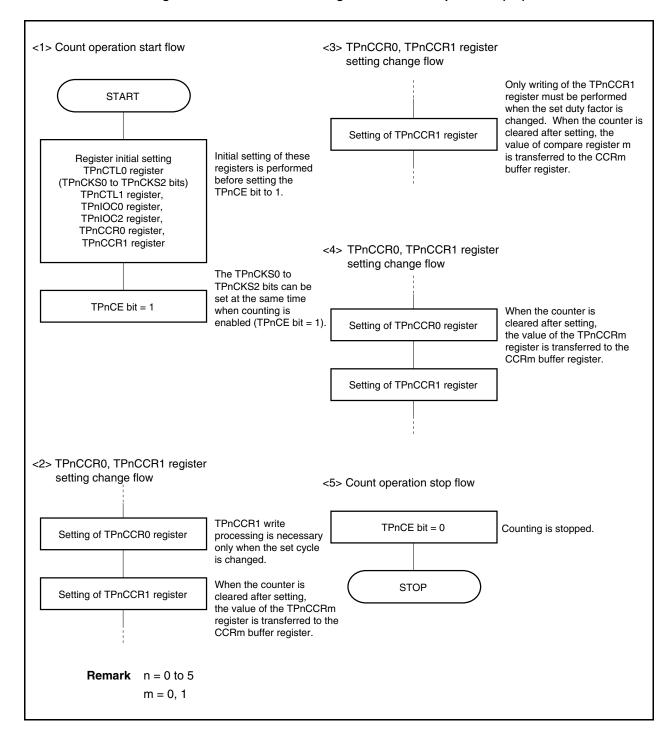

|       |            | 7.5.5          | PWM output mode (TPnMD2 to TPnMD0 bits = 100)                                                                     |       |

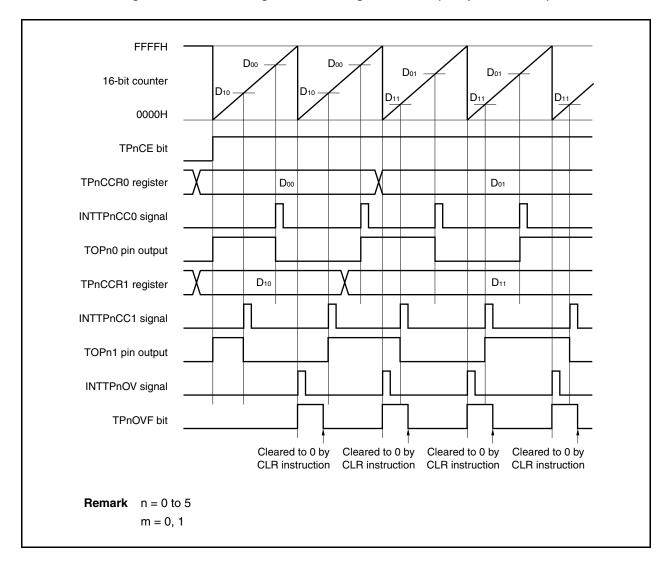

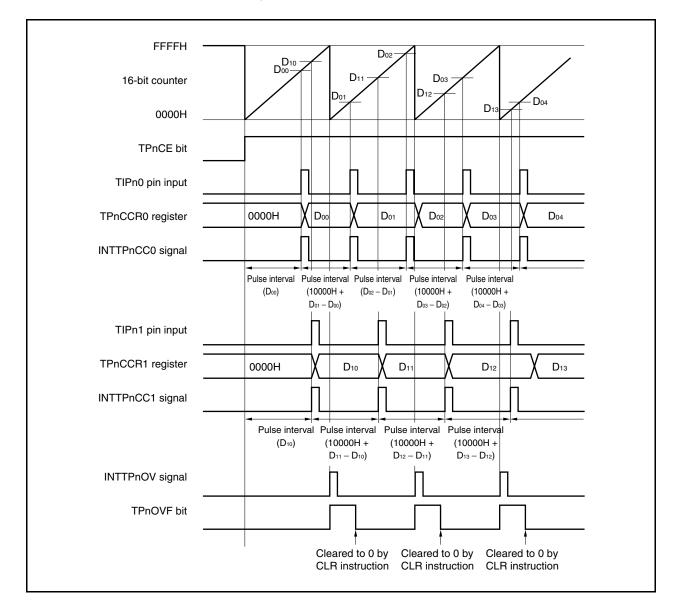

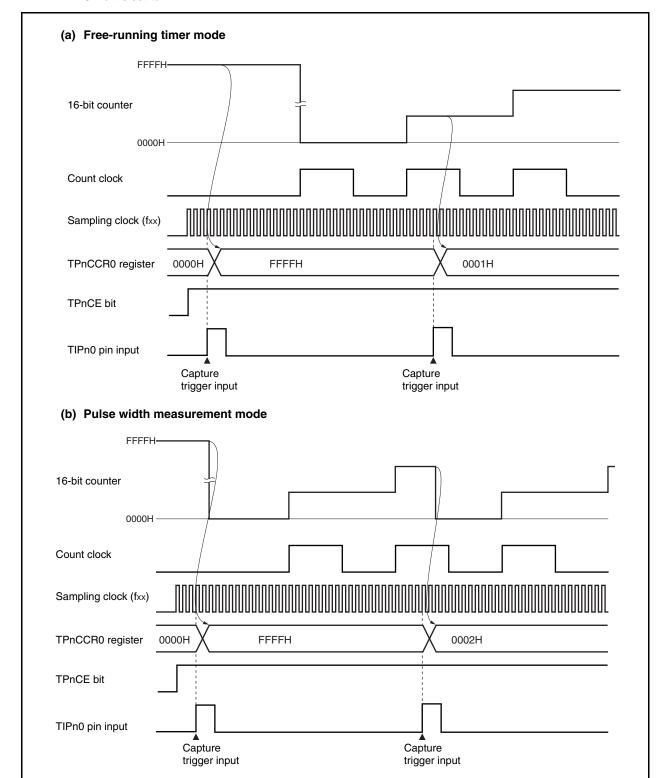

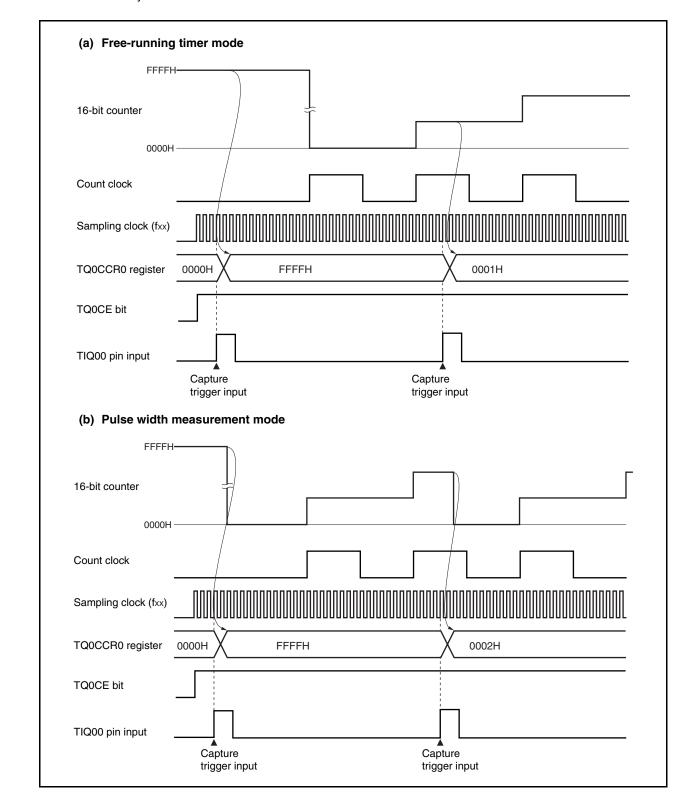

|       |            | 7.5.6          | Free-running timer mode (TPnMD2 to TPnMD0 bits = 101)                                                             |       |

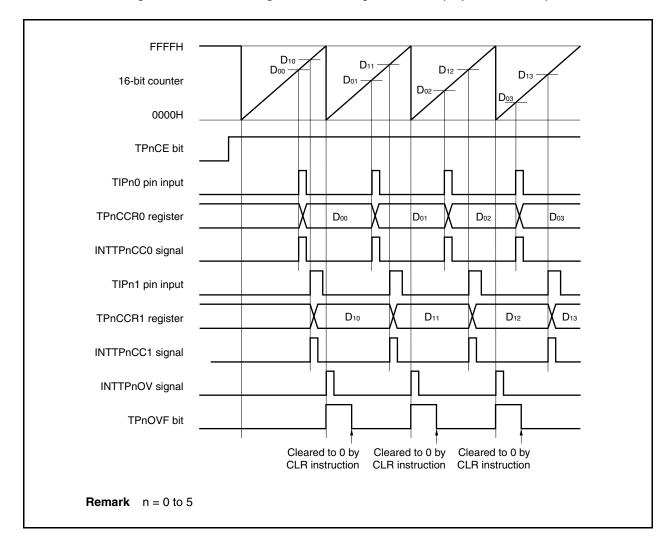

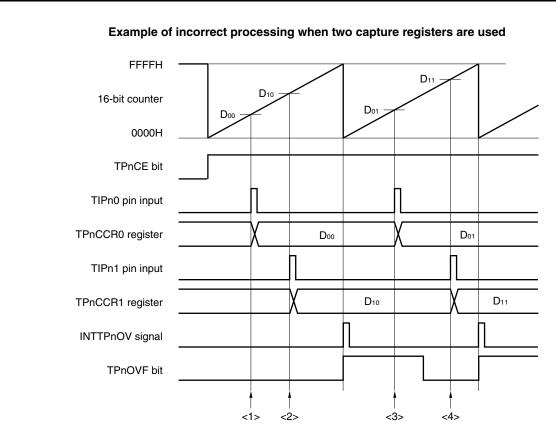

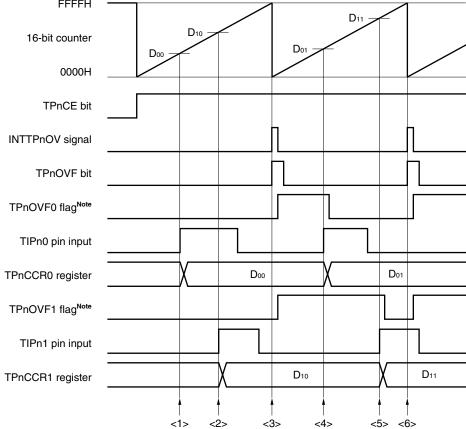

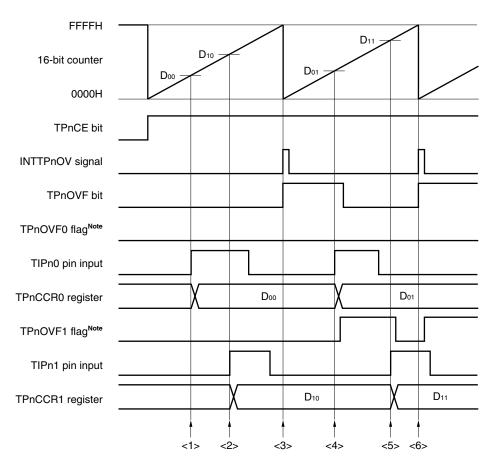

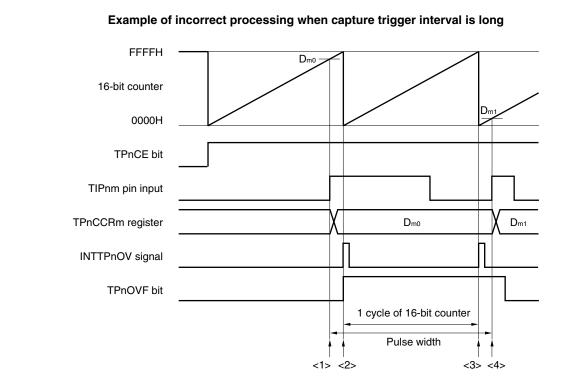

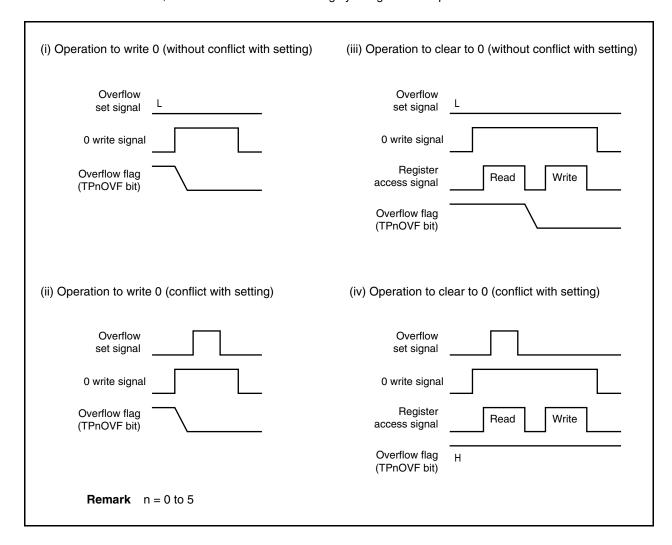

|       |            | 7.5.7          | Pulse width measurement mode (TPnMD2 to TPnMD0 bits = 110)                                                        |       |

|       |            | 7.5.8          | Timer output operations                                                                                           | 312   |

| 7     | .6         | Select         | or Function                                                                                                       | 313   |

| 7     | .7         | Cautio         | ns                                                                                                                | 315   |

| 01145 |            |                | DIT TIMED/EVENT COUNTED O (TMO)                                                                                   | 0.4.0 |

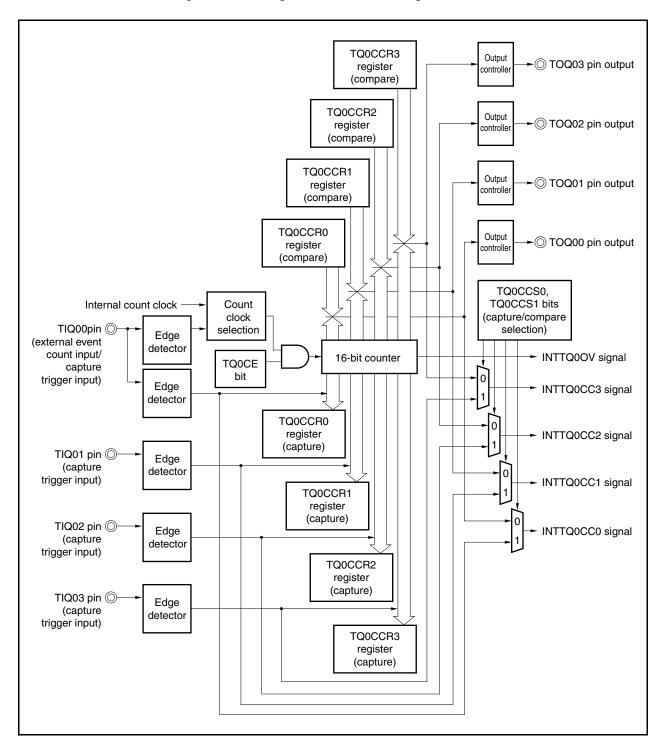

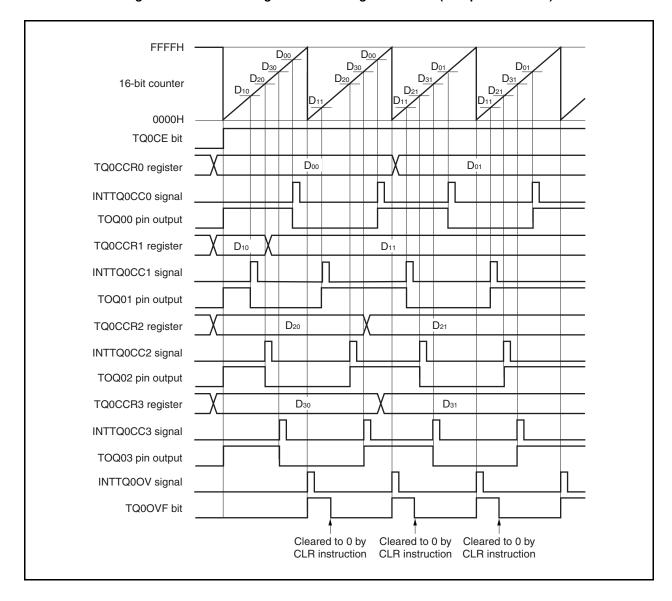

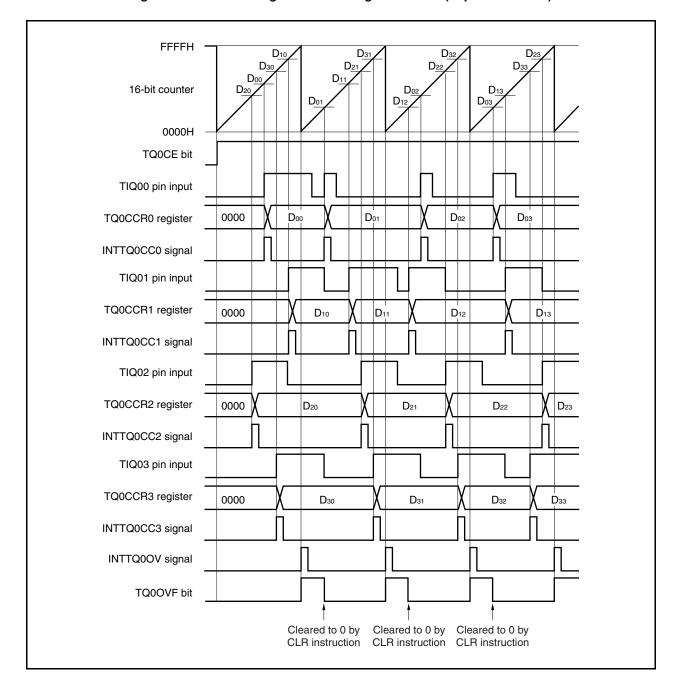

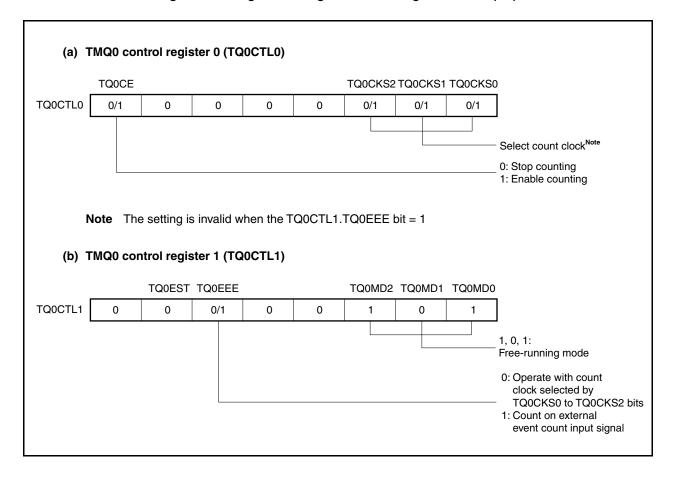

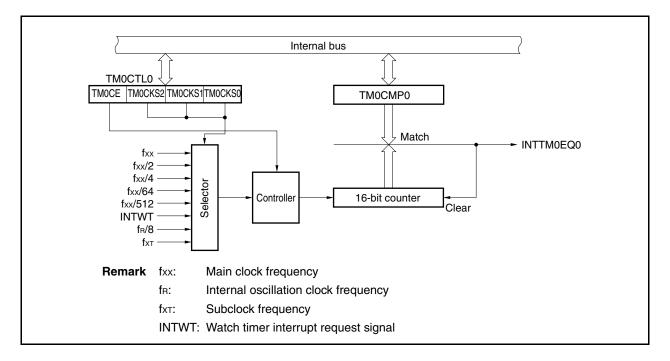

| CHAP  | TER        | 8 16-          | BIT TIMER/EVENT COUNTER Q (TMQ)                                                                                   | 316   |

| 8     | .1         |                | ew                                                                                                                |       |

| 8     | .2         |                | ons                                                                                                               |       |

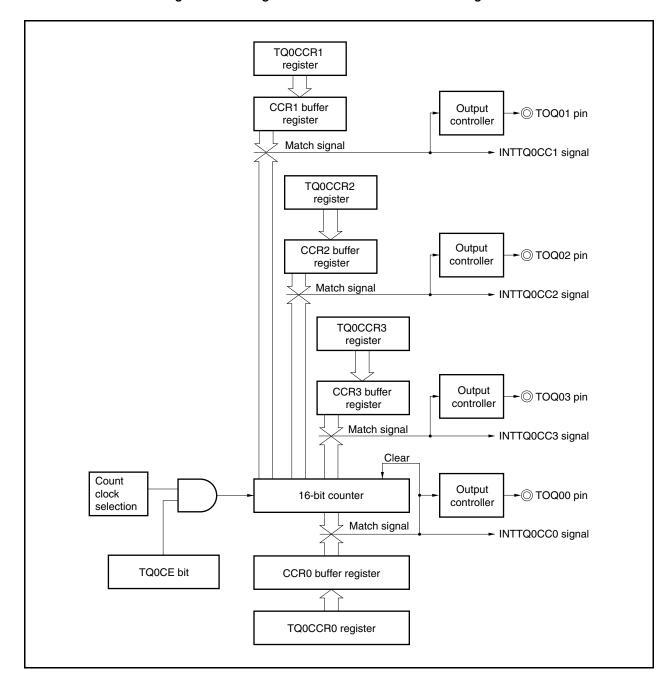

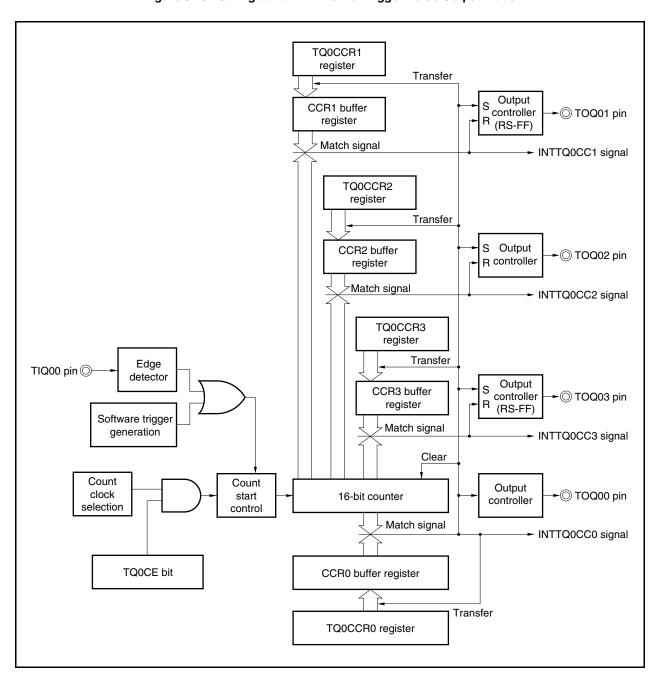

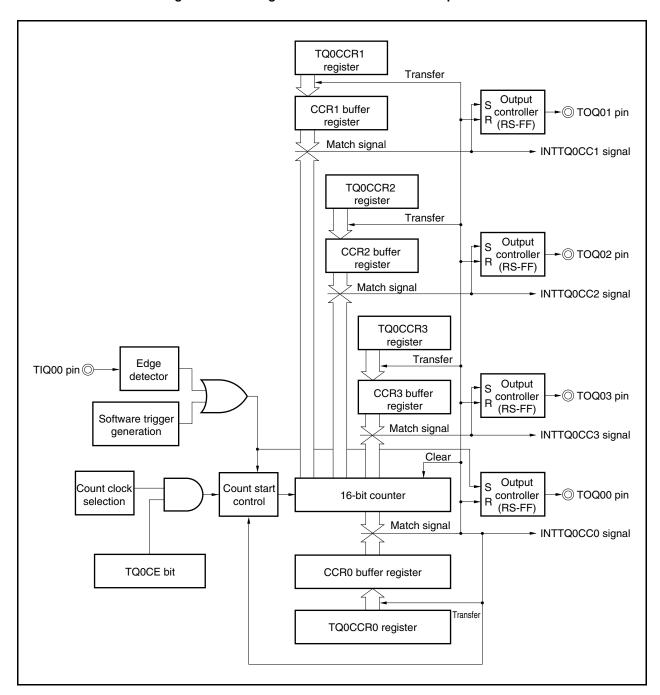

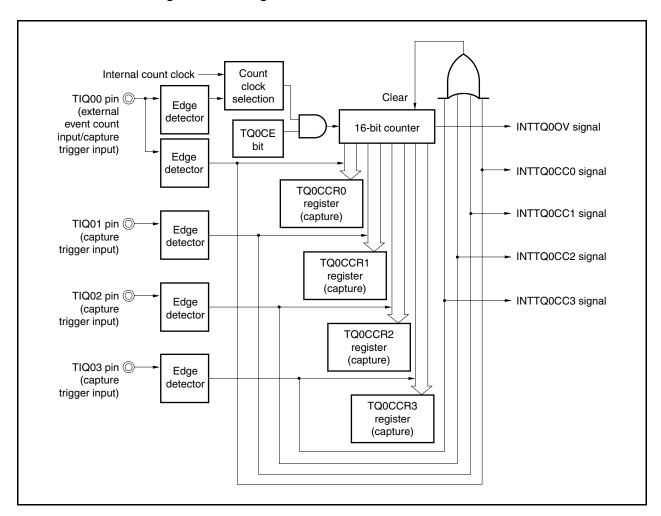

| 8     | .3         | _              | uration                                                                                                           |       |

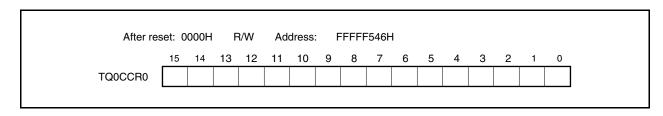

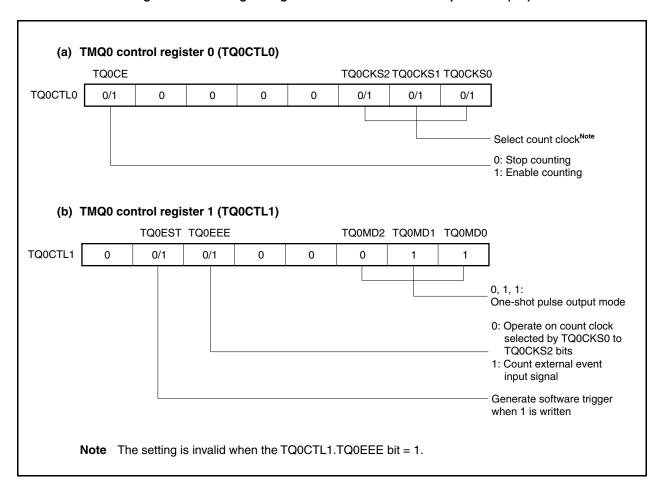

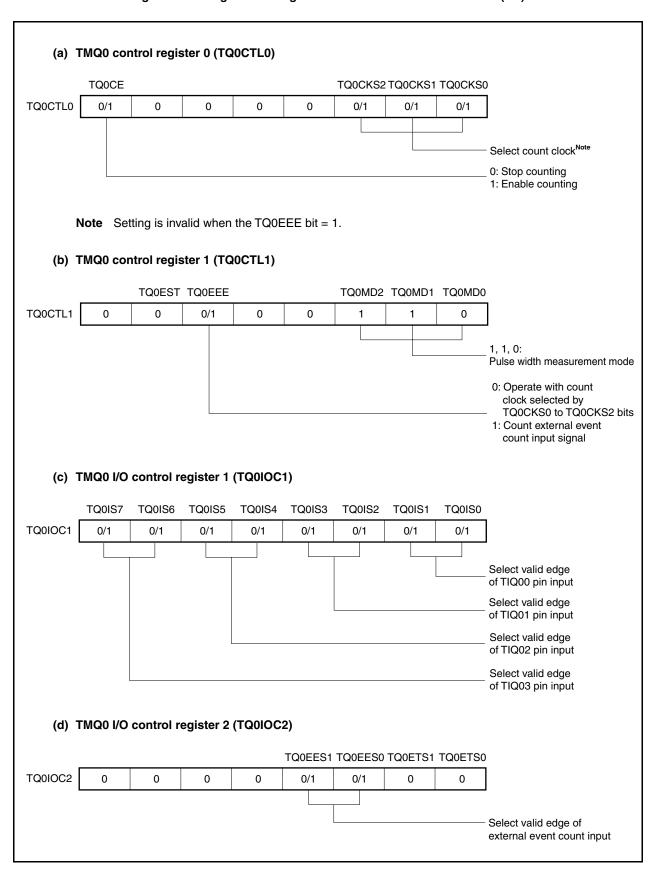

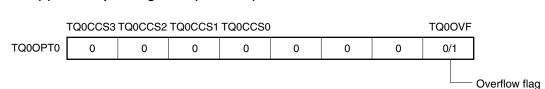

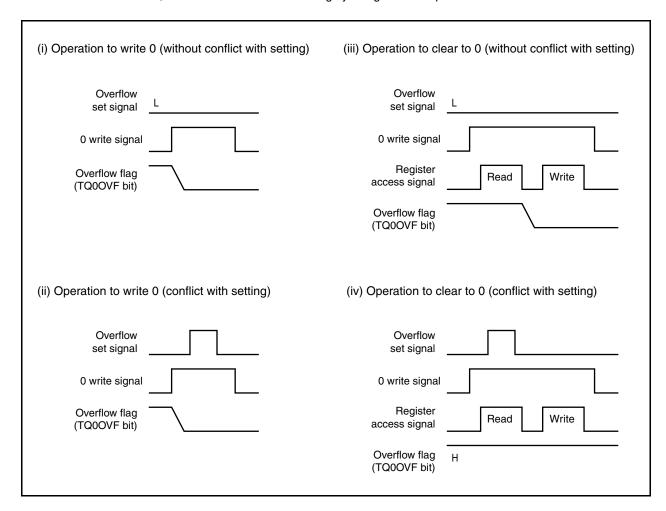

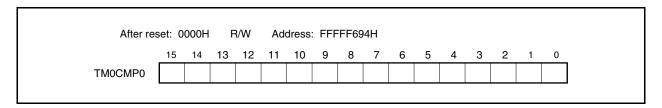

|       | .4         | •              | ers                                                                                                               |       |

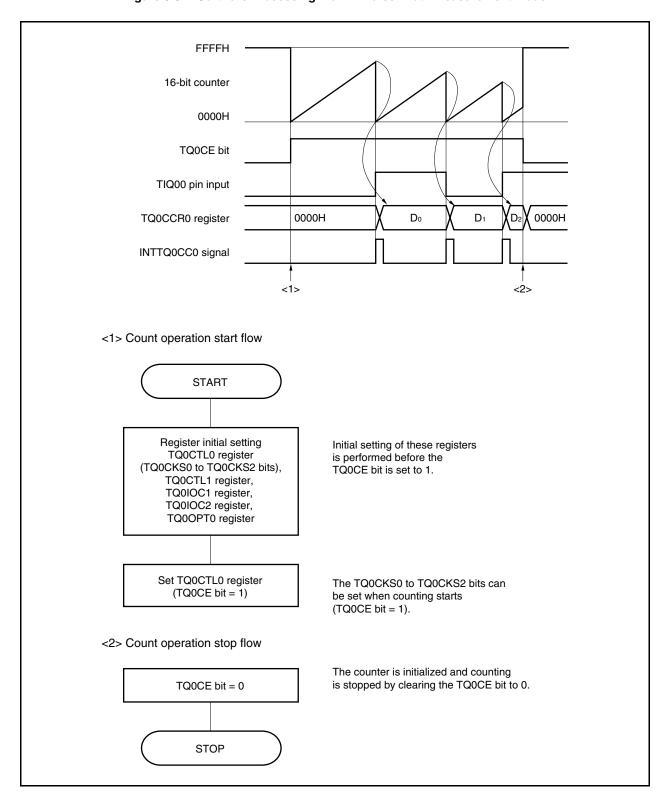

| 8     | .5         | •              | tion                                                                                                              |       |

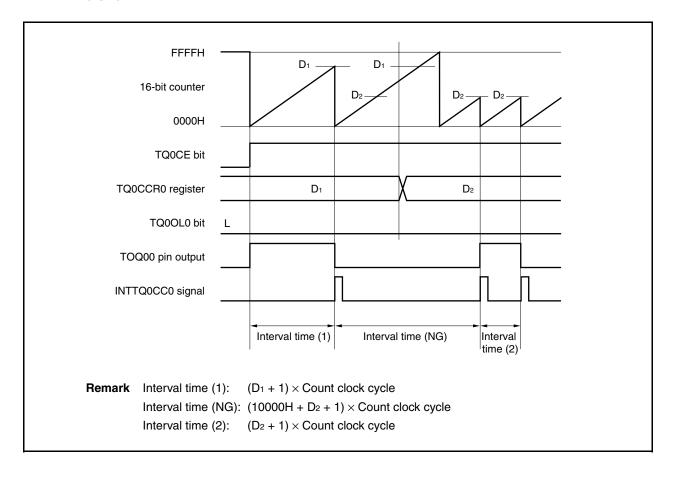

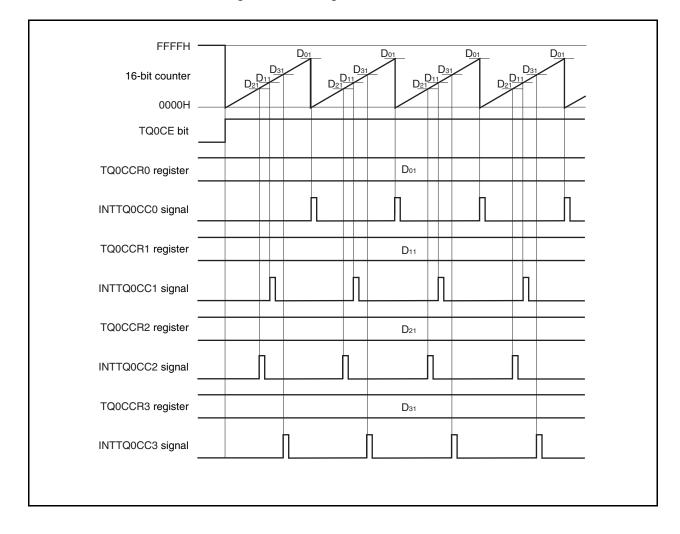

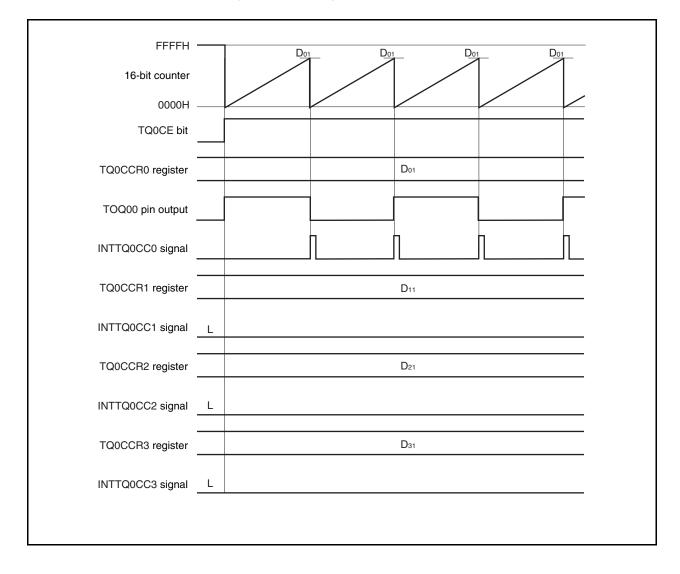

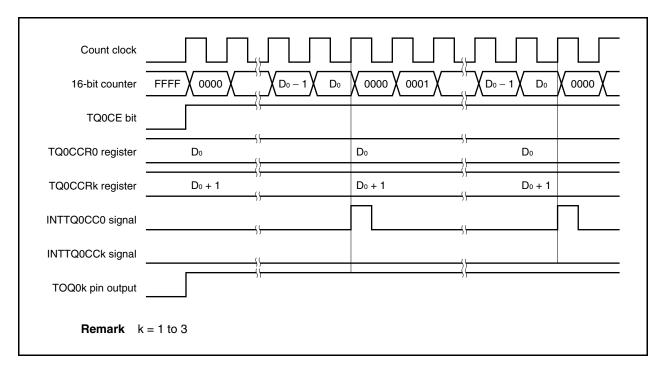

|       |            | 8.5.1          | Interval timer mode (TQ0MD2 to TQ0MD0 bits = 000)                                                                 |       |

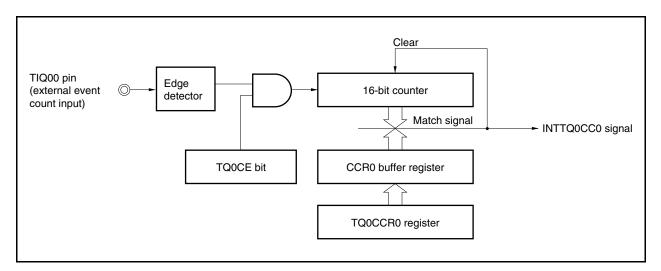

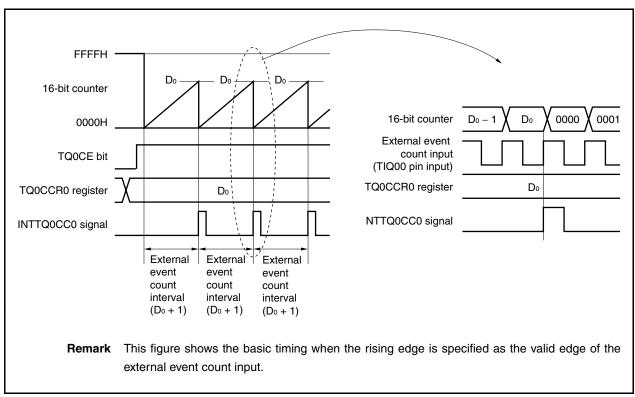

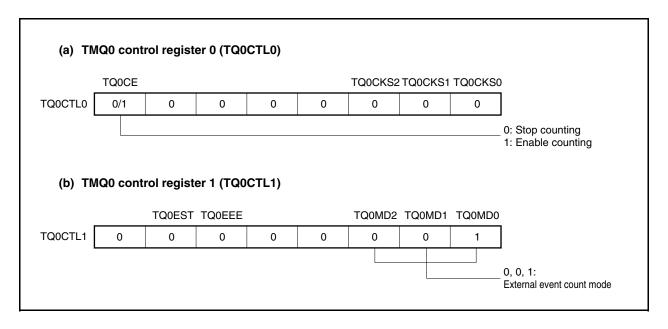

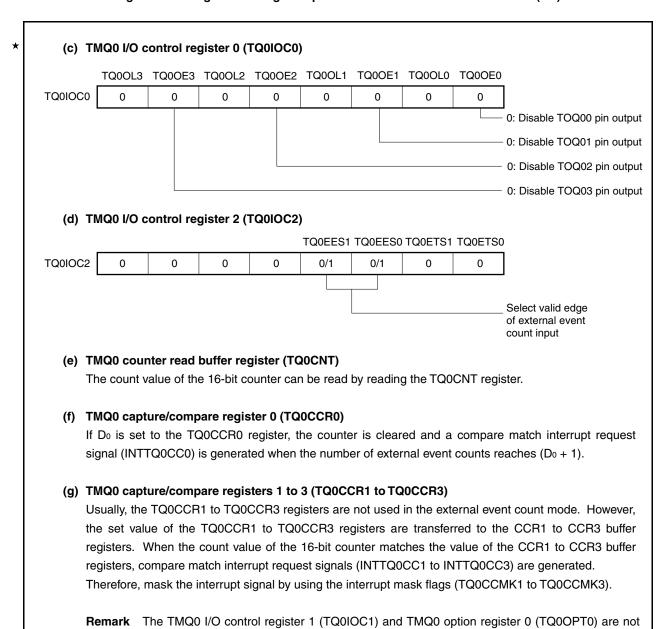

|       |            | 8.5.2          | External event count mode (TQ0MD2 to TQ0MD0 bits = 001)                                                           |       |

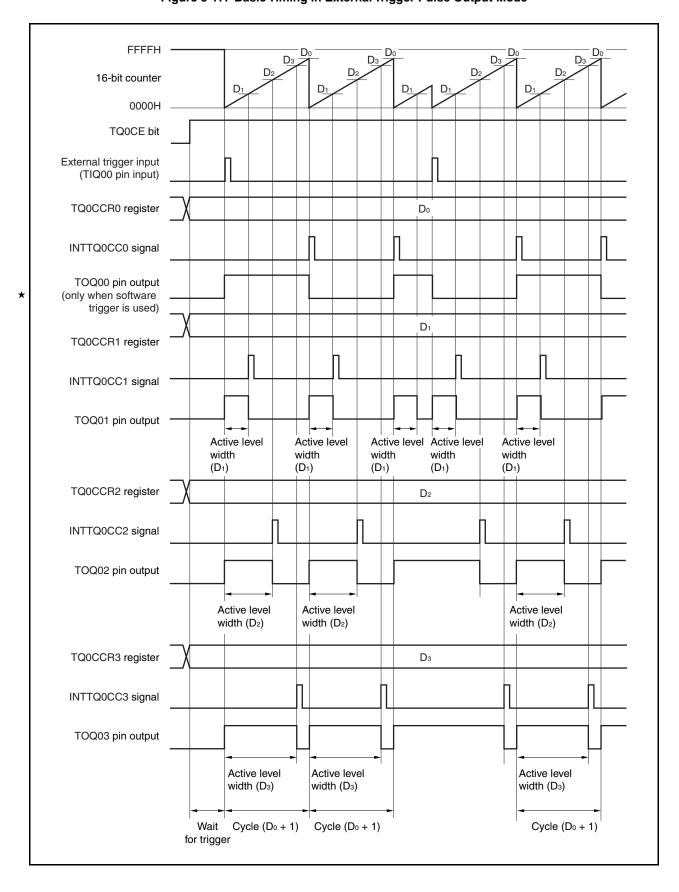

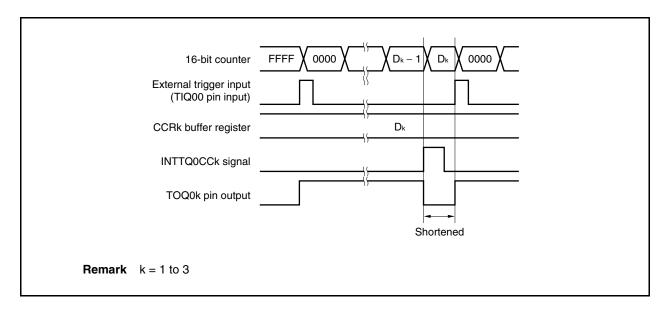

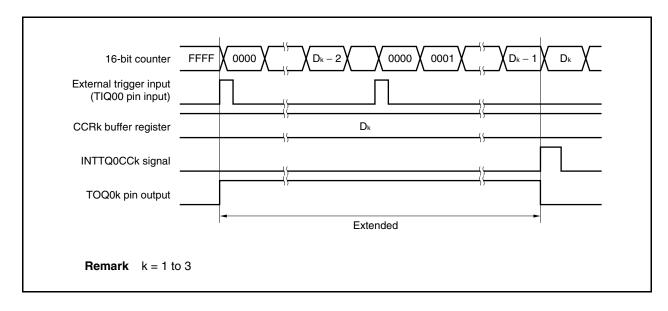

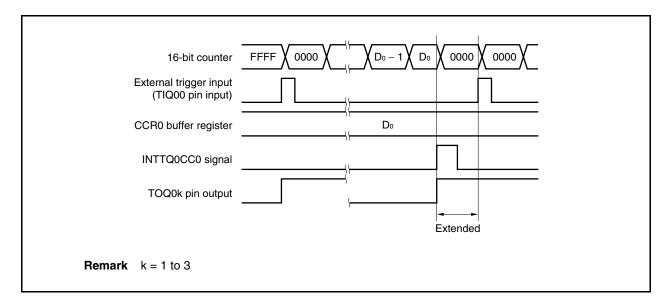

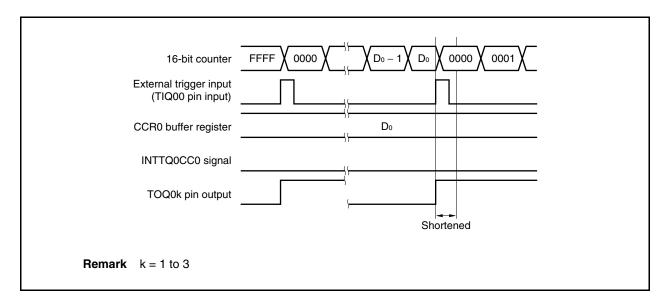

|       |            | 8.5.3          | External trigger pulse output mode (TQ0MD2 to TQ0MD0 bits = 010)                                                  |       |

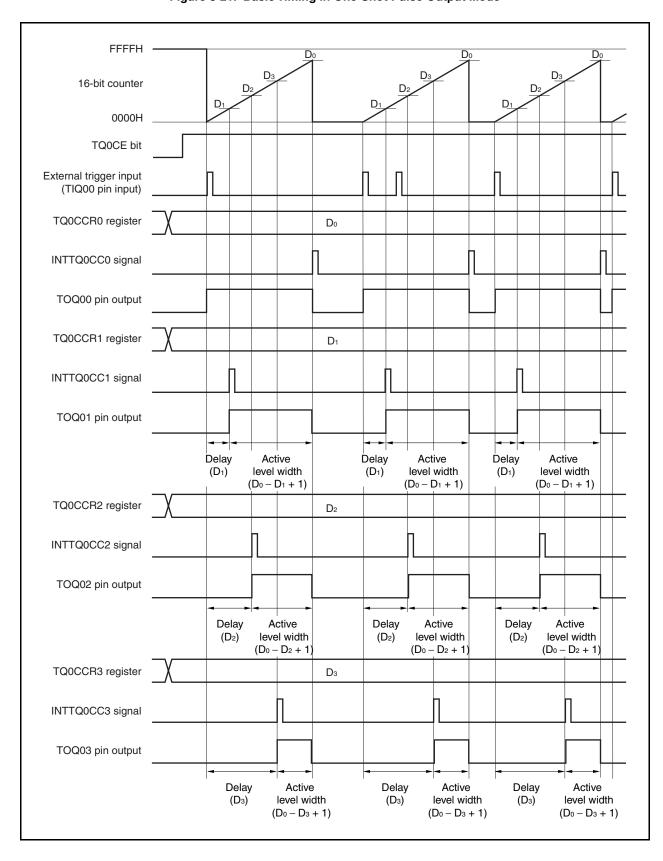

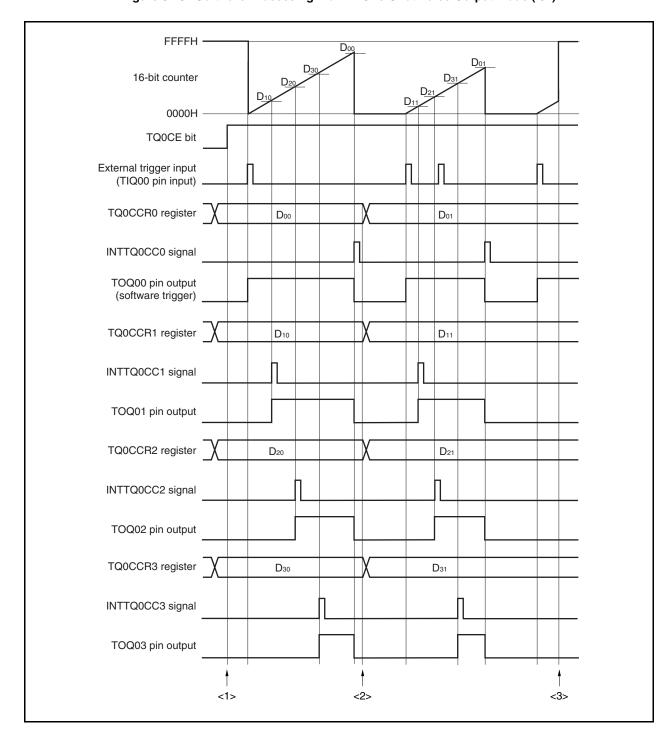

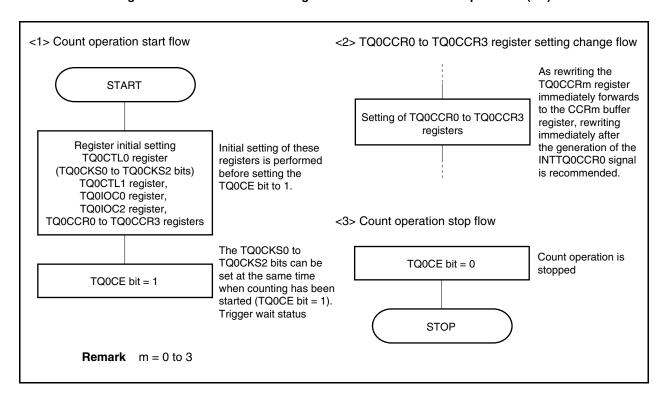

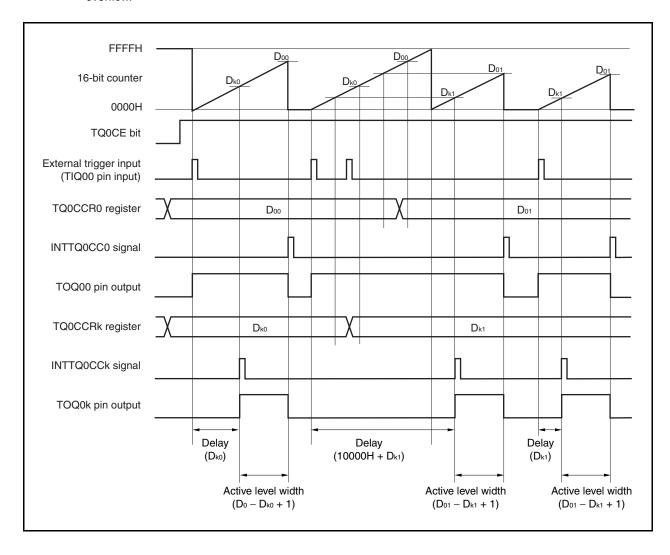

|       |            | 8.5.4          | One-shot pulse output mode (TQ0MD2 to TQ0MD0 bits = 011)                                                          |       |

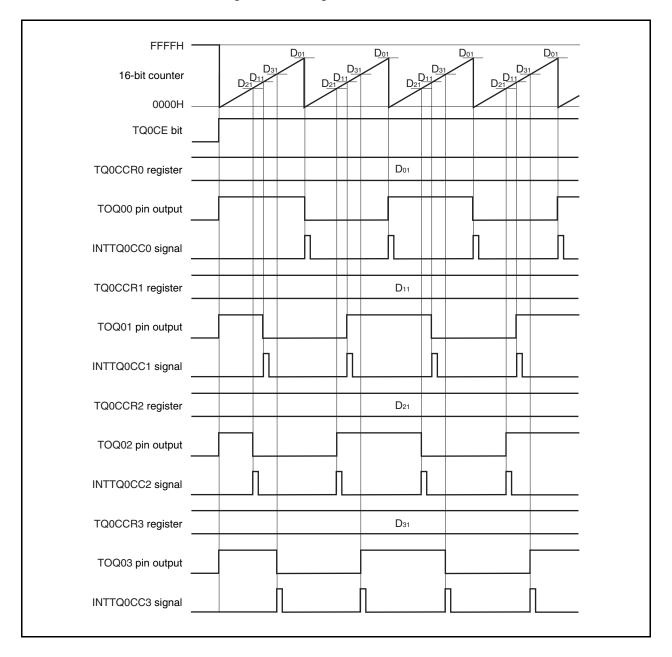

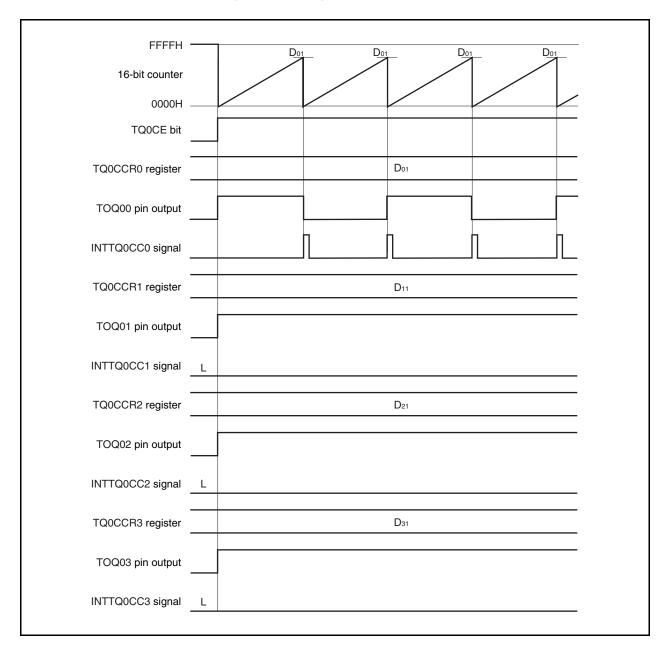

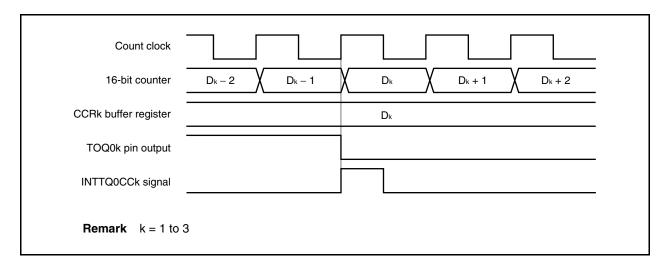

|       |            | 8.5.5          | PWM output mode (TQ0MD2 to TQ0MD0 bits = 100)                                                                     |       |

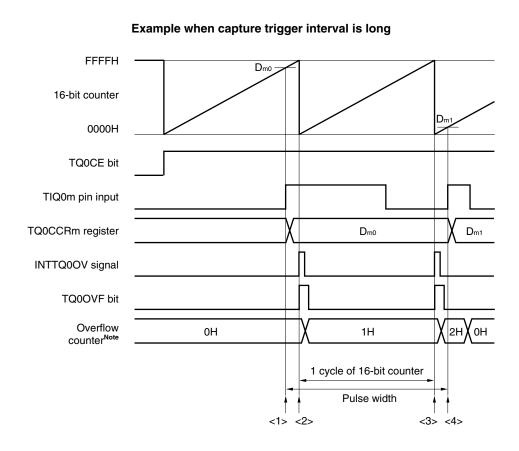

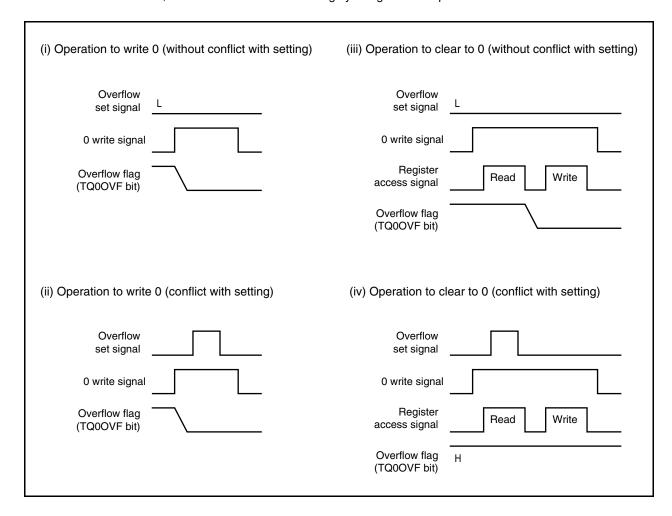

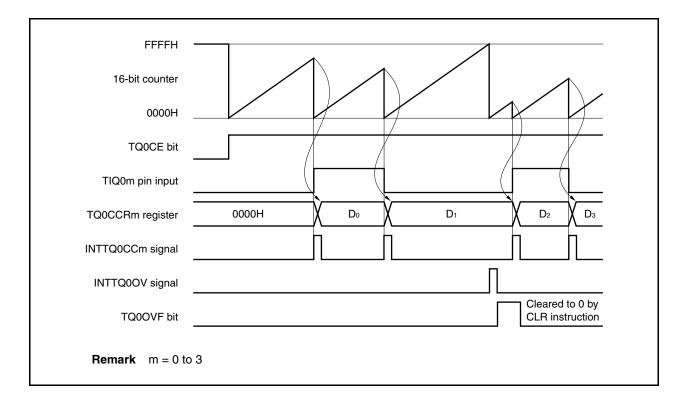

|       |            | 8.5.6<br>8.5.7 | Free-running timer mode (TQ0MD2 to TQ0MD0 bits = 101)  Pulse width measurement mode (TQ0MD2 to TQ0MD0 bits = 110) |       |

|       |            | 8.5.8          | Timer output operations                                                                                           |       |

| Ω     | .6         |                | or Function                                                                                                       |       |

|       | .7         |                | ns                                                                                                                |       |

|       |            |                |                                                                                                                   |       |

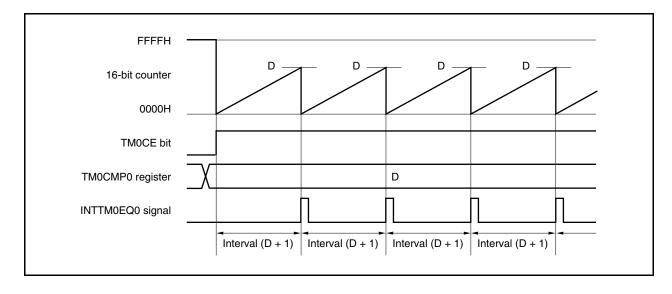

| CHAP  | PTER       | 9 16-          | BIT INTERVAL TIMER M (TMM)                                                                                        | 416   |

|       | .1         |                | ew                                                                                                                |       |

|       | .2         | _              | uration                                                                                                           |       |

|       | .3         | _              | er                                                                                                                |       |

| 9     | .4         | •              | tion                                                                                                              |       |

|       |            | 9.4.1          | Interval timer mode                                                                                               |       |

|       |            | 9.4.2          | Cautions                                                                                                          | 423   |

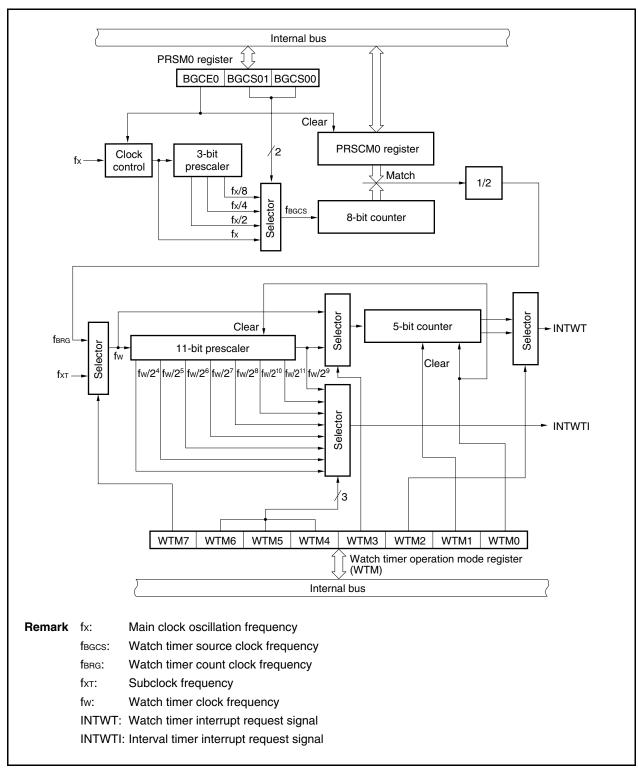

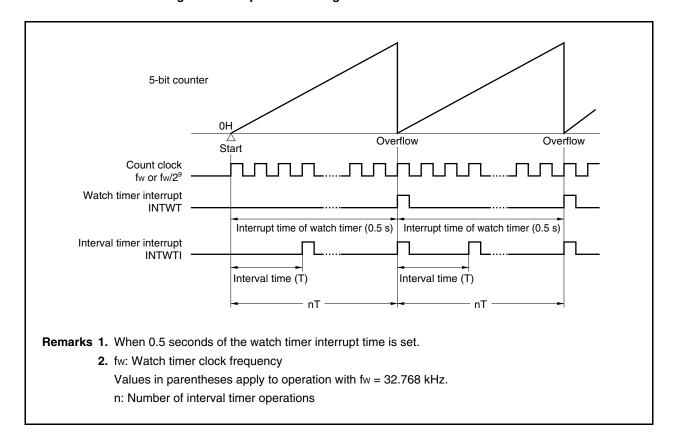

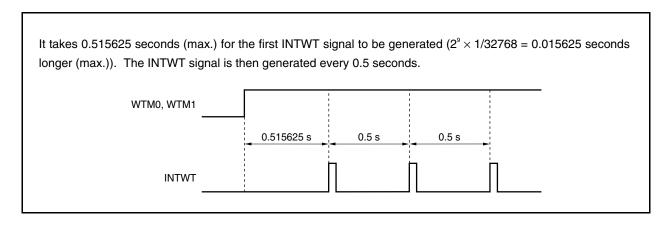

| CHAP  | TER        | 10 W           | ATCH TIMER FUNCTIONS                                                                                              | 424   |

| 1     | 0.1        | Functi         | ons                                                                                                               | 424   |

|       |            |                |                                                                                                                   |       |

| 10.2           | Configuration                                       | 425 |

|----------------|-----------------------------------------------------|-----|

| 10.3           | Control Registers                                   | 427 |

| 10.4           | Operation                                           | 431 |

|                | 10.4.1 Operation as watch timer                     | 431 |

|                | 10.4.2 Operation as interval timer                  |     |

|                | 10.4.3 Cautions                                     |     |

|                |                                                     |     |

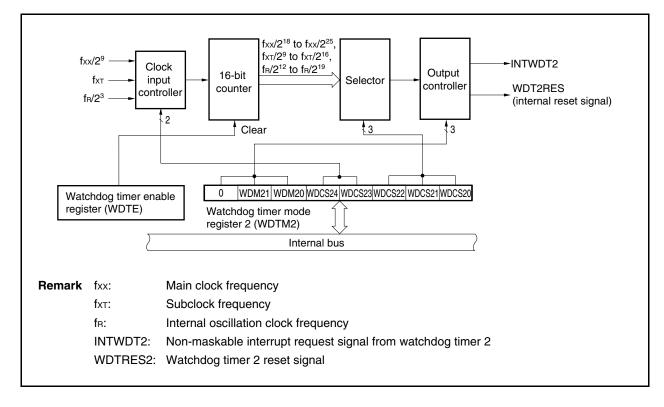

| <b>CHAPTER</b> | 11 FUNCTIONS OF WATCHDOG TIMER 2                    | 434 |

| 11.1           | Functions                                           | 121 |

| 11.1           | Configuration                                       |     |

| 11.2           | •                                                   |     |

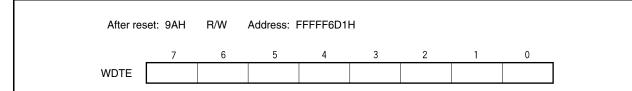

|                | Registers Operation                                 |     |

| 11.4           | Operation                                           | 439 |

| CHAPTER        | 12 REAL-TIME OUTPUT FUNCTION (RTO)                  | 440 |

|                |                                                     |     |

| 12.1           | Function                                            |     |

| 12.2           | Configuration                                       |     |

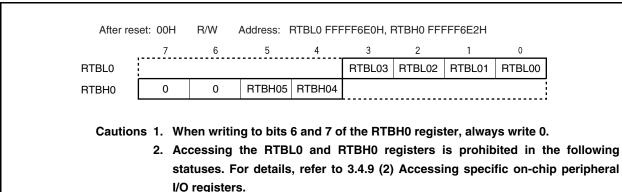

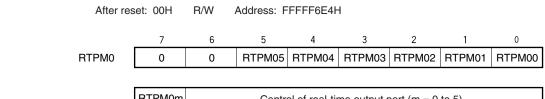

| 12.3           | Registers                                           |     |

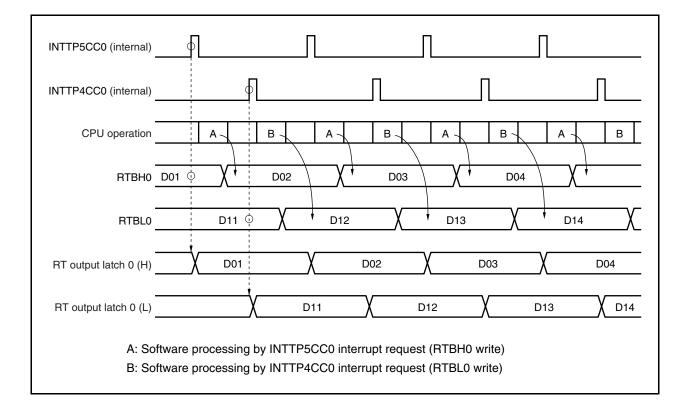

| 12.4           | Operation                                           | 445 |

| 12.5           | Usage                                               | 446 |

| 12.6           | Cautions                                            | 446 |

|                |                                                     |     |

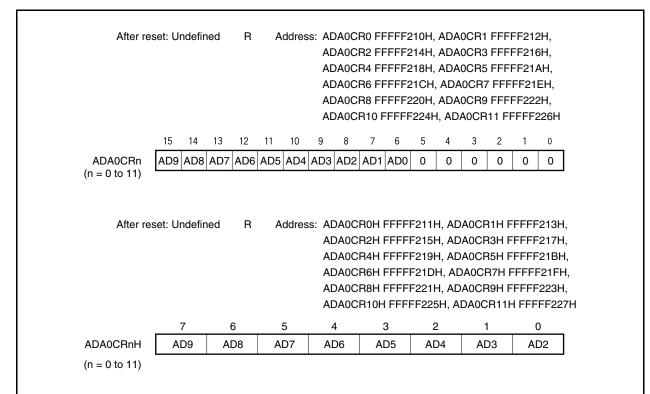

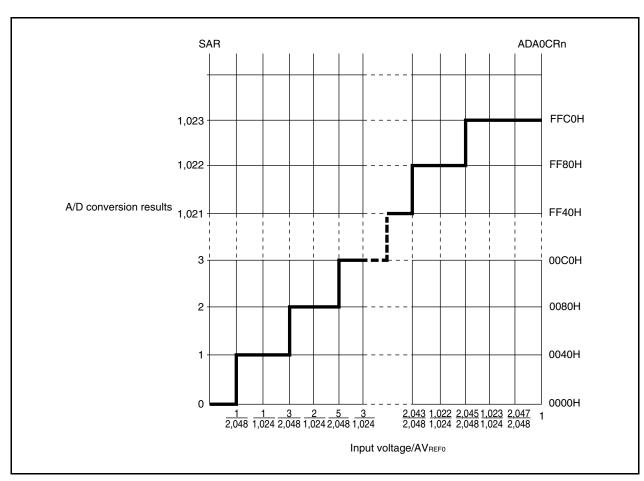

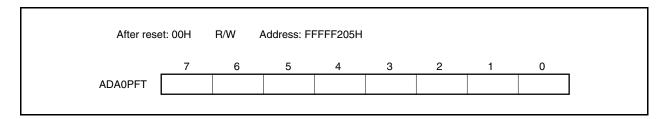

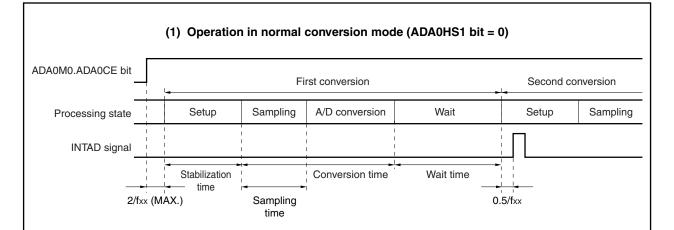

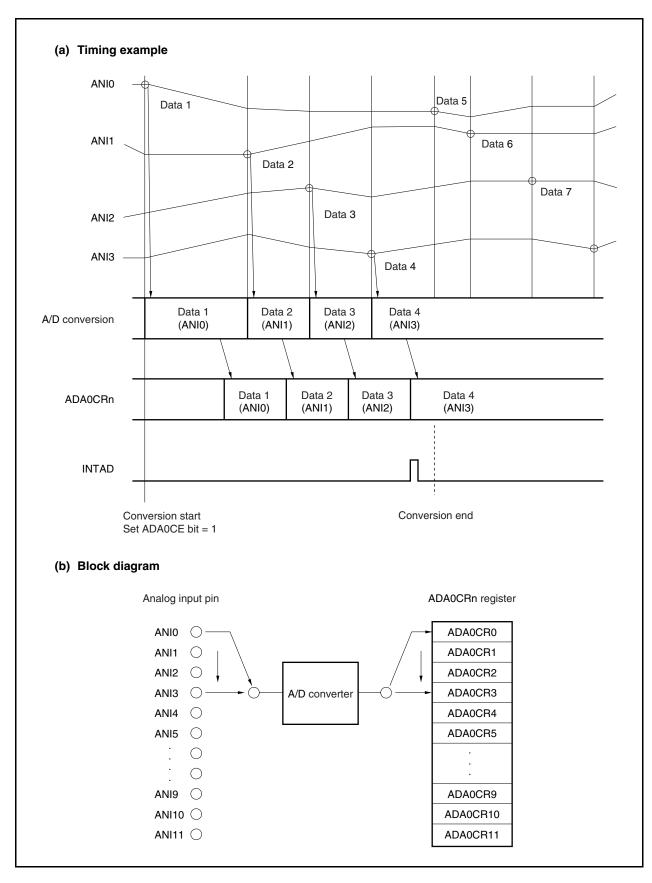

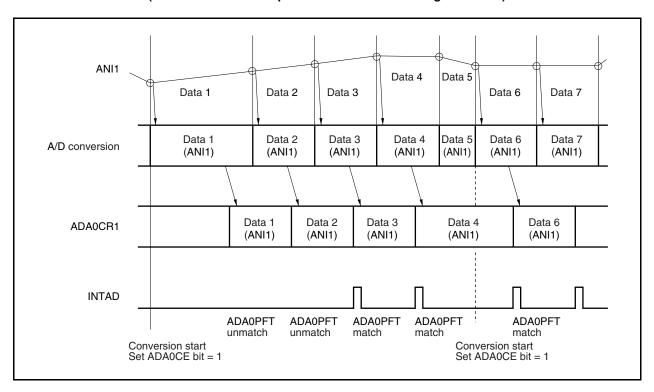

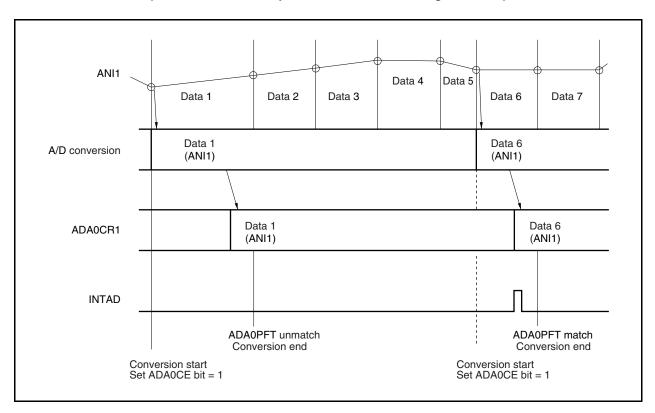

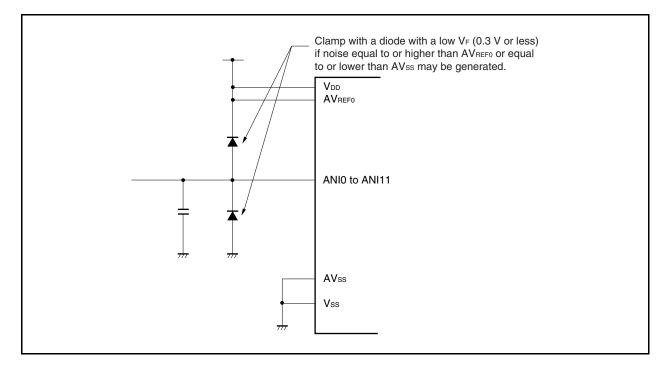

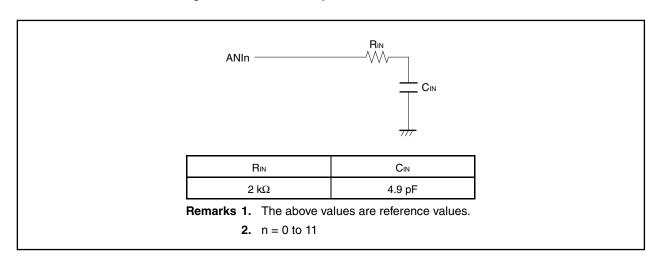

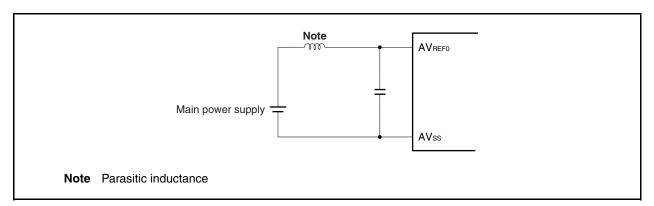

| CHAPTER        | 13 A/D CONVERTER                                    | 447 |

| 13.1           | Overview                                            | 447 |

| 13.2           | Functions                                           |     |

| 13.3           | Configuration                                       |     |

| 13.4           | Registers                                           |     |

| 13.5           | Operation                                           |     |

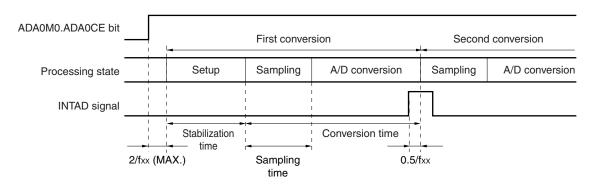

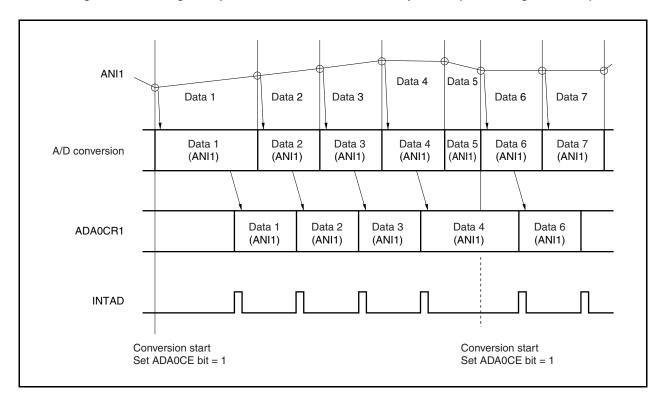

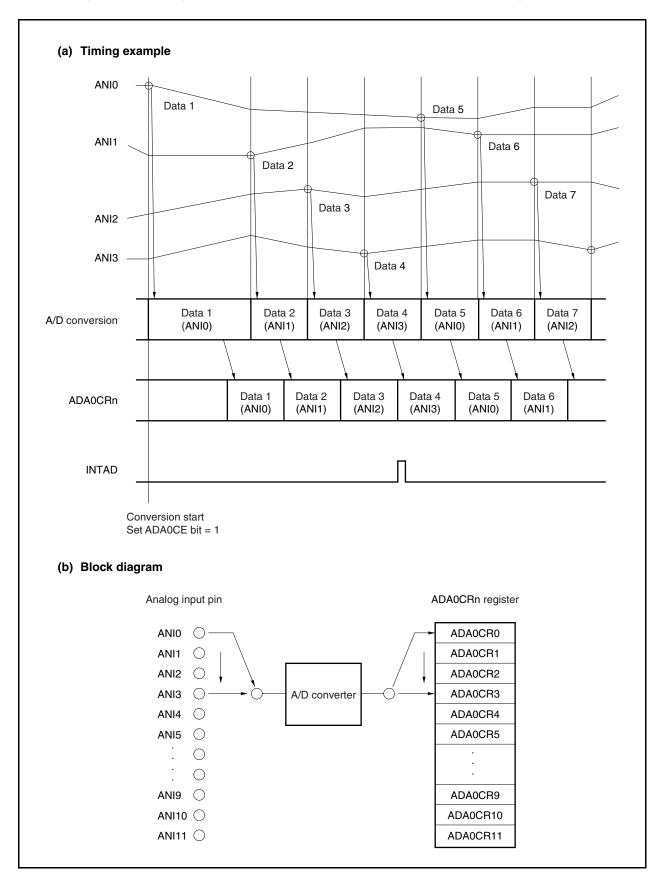

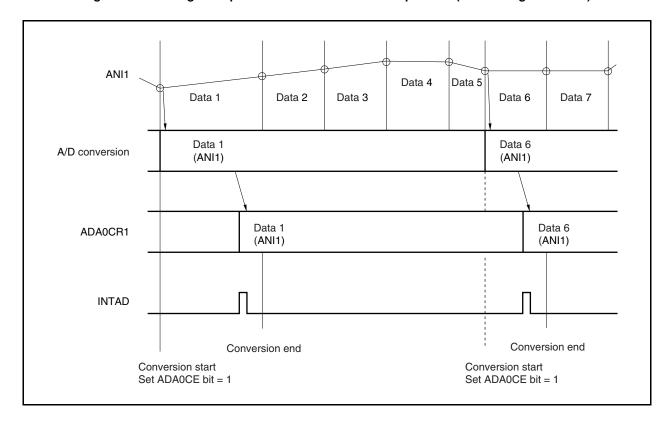

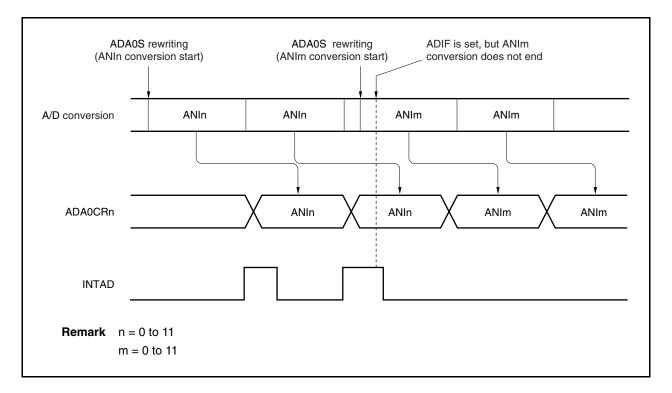

| 10.5           | 13.5.1 Basic operation                              |     |

|                | 13.5.2 Conversion operation timing                  |     |

|                | ·                                                   |     |

|                | 99-                                                 |     |

|                | 13.5.4 Operation mode                               |     |

| 400            | 13.5.5 Power-fail compare mode                      |     |

| 13.6           | Cautions                                            |     |

| 13.7           | How to Read A/D Converter Characteristics Table     | 478 |

| CHAPTER        | 14 D/A CONVERTER                                    | 482 |

|                |                                                     |     |

| 14.1           | Functions                                           |     |

| 14.2           | Configuration                                       |     |

| 14.3           | Registers                                           | 483 |

| 14.4           | Operation                                           | 485 |

|                | 14.4.1 Operation in normal mode                     | 485 |

|                | 14.4.2 Operation in real-time output mode           | 485 |

|                | 14.4.3 Cautions                                     | 486 |

|                |                                                     |     |

| CHAPTER        | 15 ASYNCHRONOUS SERIAL INTERFACE A (UARTA)          | 487 |

| 15.1           | Mode Switching of UARTA and Other Serial Interfaces | 487 |

|                | 15.1.1 CSIB4 and UARTA0 mode switching              |     |

|                |                                                     |     |

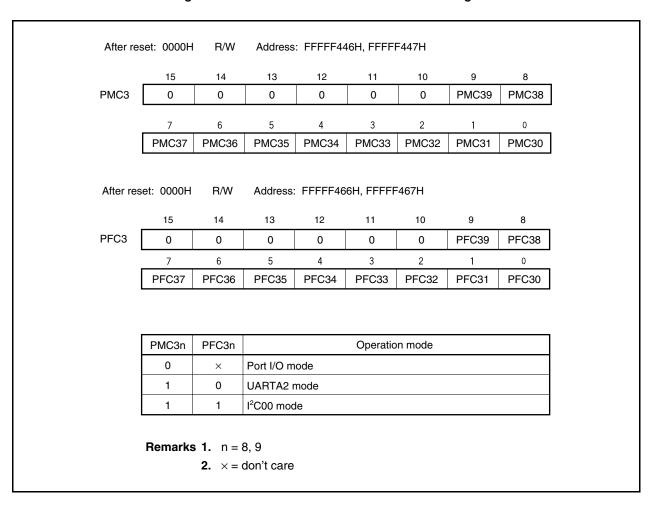

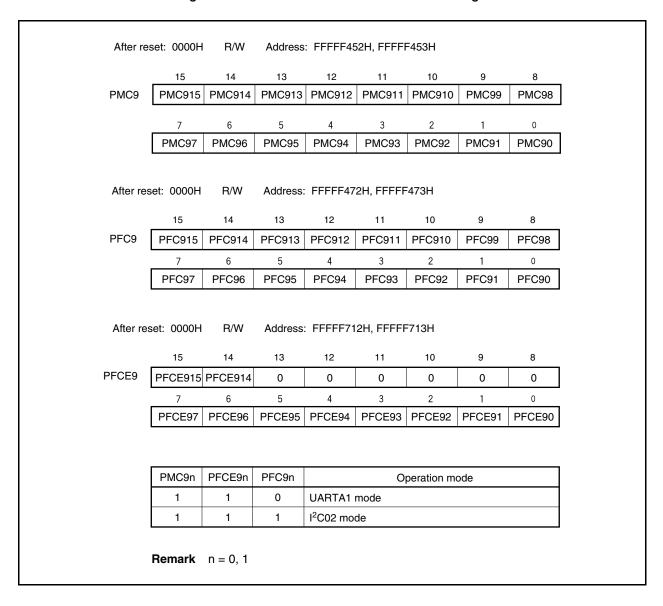

|         | 15.1.2 UARTA2 and I <sup>2</sup> C00 mode switching                    | 488 |

|---------|------------------------------------------------------------------------|-----|

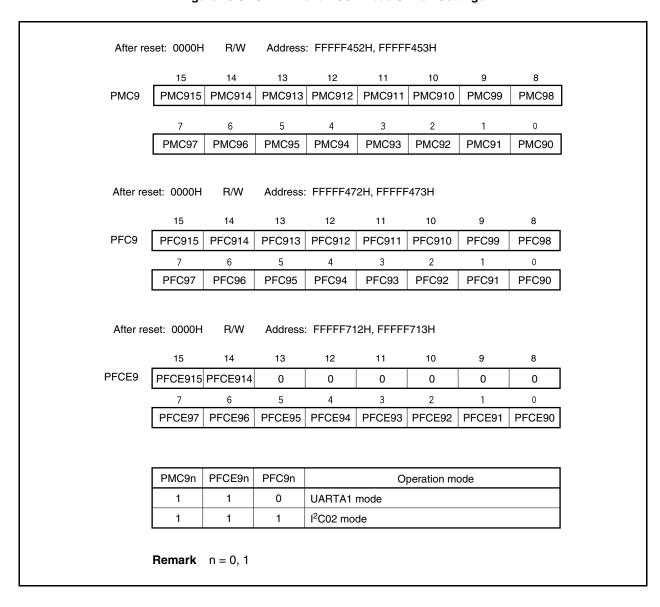

|         | 15.1.3 UARTA1 and I <sup>2</sup> C02 mode switching                    | 489 |

| 15.2    | Features                                                               | 490 |

| 15.3    | Configuration                                                          | 491 |

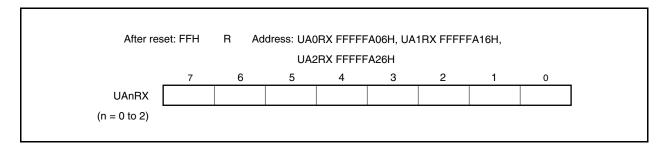

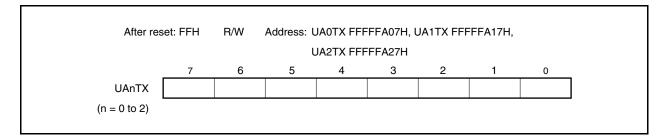

| 15.4    | Registers                                                              | 493 |

| 15.5    | Interrupt Request Signals                                              | 499 |

| 15.6    | Operation                                                              | 500 |

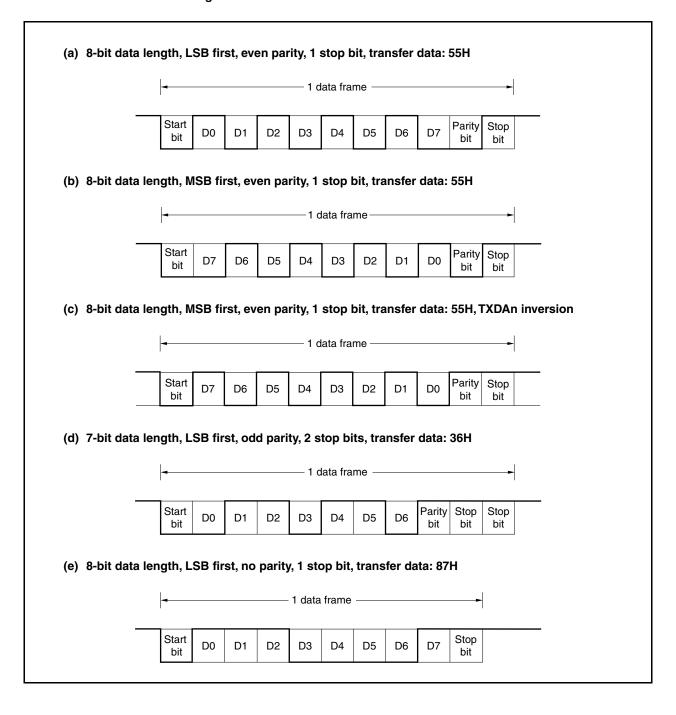

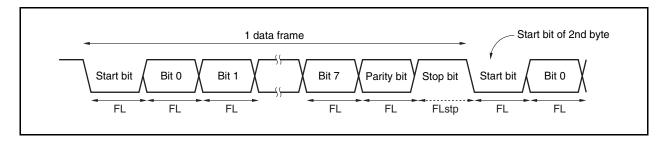

|         | 15.6.1 Data format                                                     | 500 |

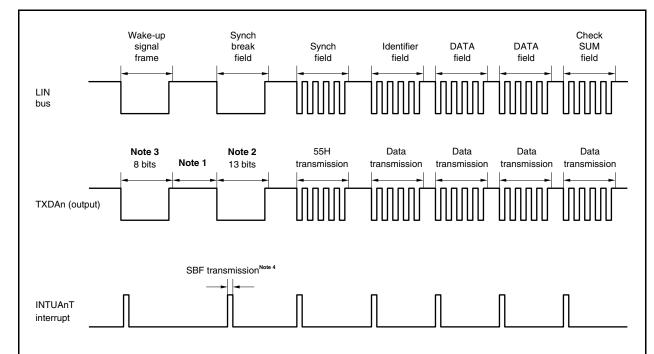

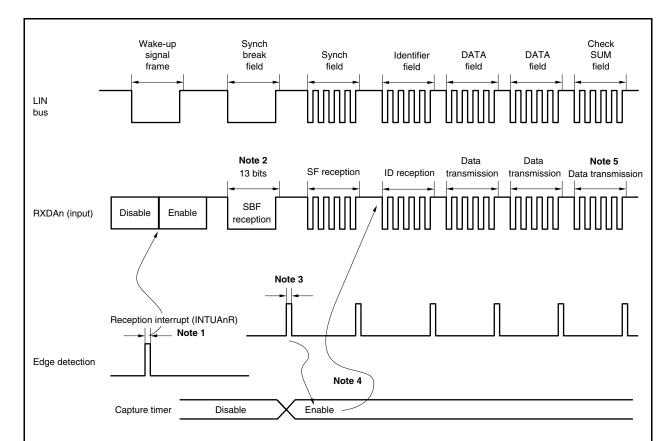

|         | 15.6.2 SBF transmission/reception format                               | 502 |

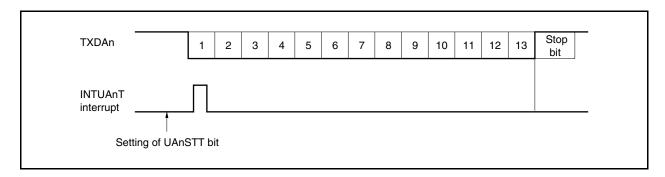

|         | 15.6.3 SBF transmission                                                | 504 |

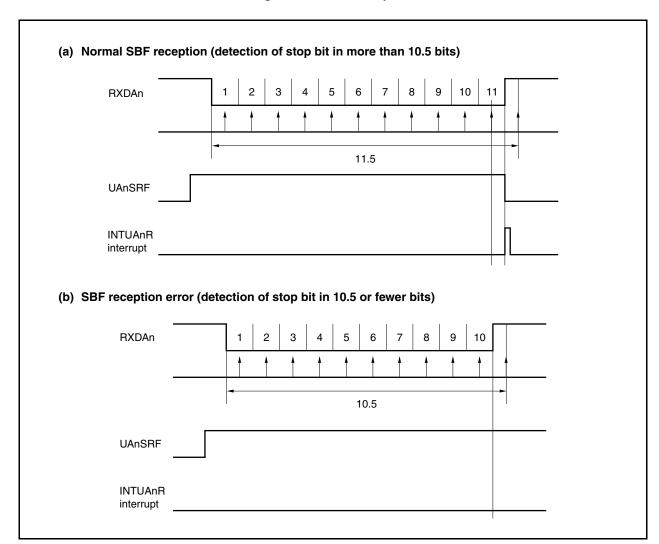

|         | 15.6.4 SBF reception                                                   | 505 |

|         | 15.6.5 UART transmission                                               | 506 |

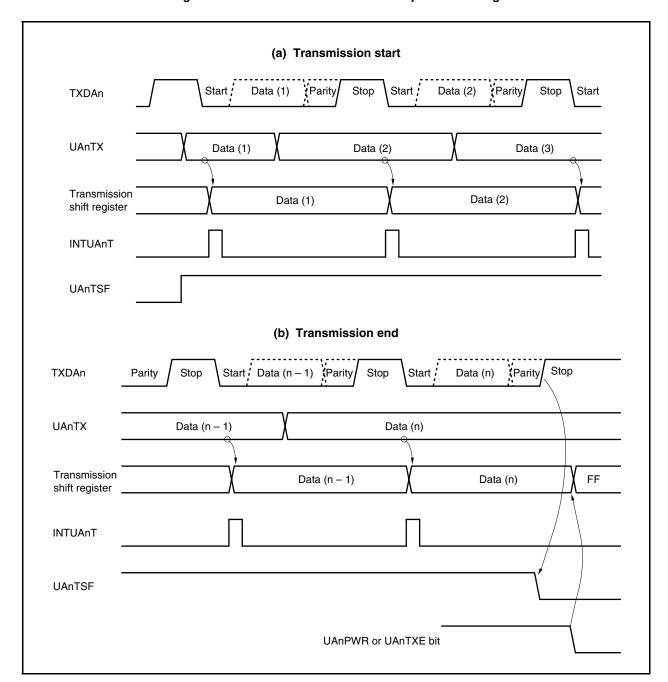

|         | 15.6.6 Continuous transmission procedure                               | 507 |

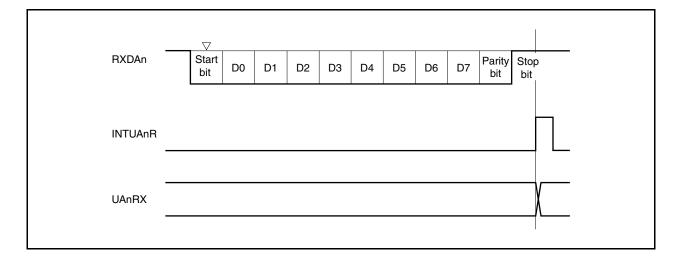

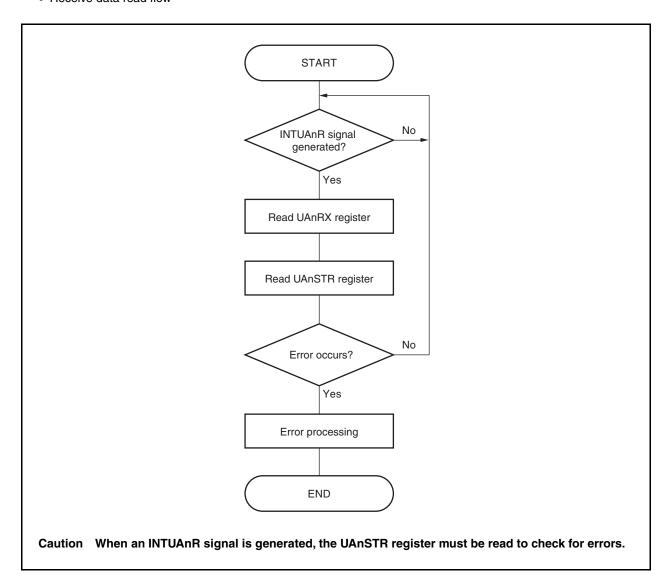

|         | 15.6.7 UART reception                                                  | 509 |

|         | 15.6.8 Reception errors                                                | 510 |

|         | 15.6.9 Parity types and operations                                     | 512 |

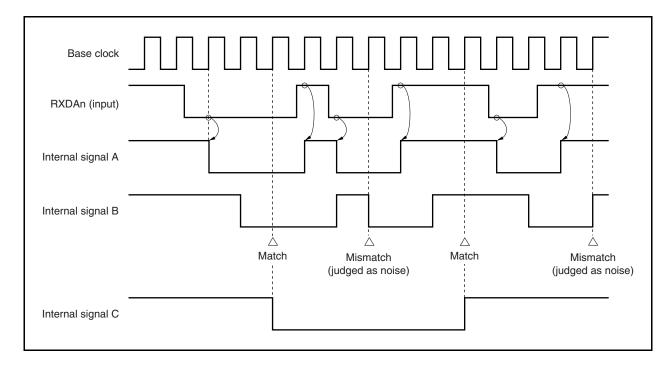

|         | 15.6.10 Receive data noise filter                                      | 513 |

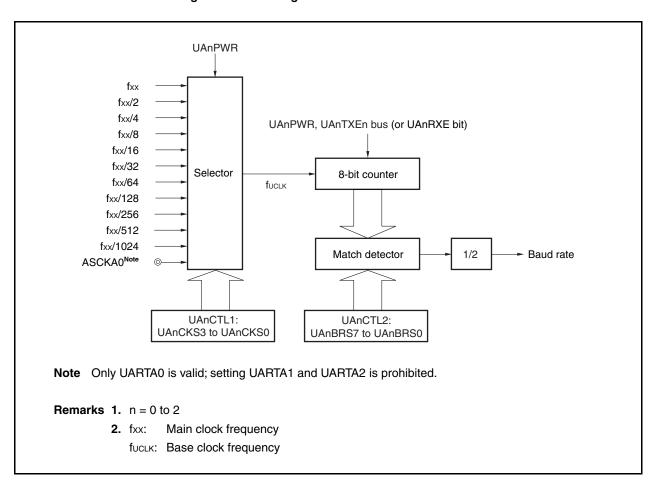

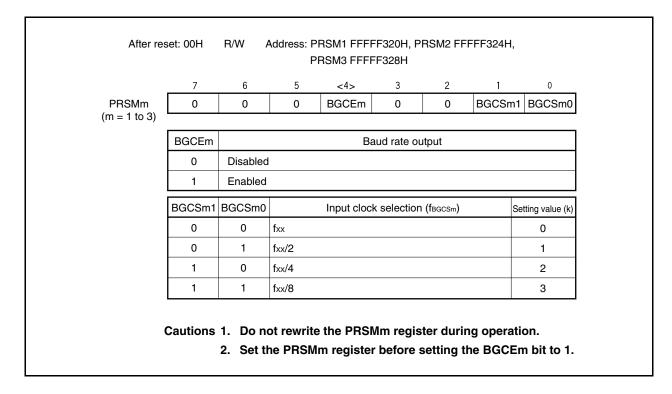

| 15.7    | Dedicated Baud Rate Generator                                          |     |

| 15.8    | Cautions                                                               | 522 |

|         |                                                                        |     |

| CHAPTER | R 16 3-WIRE VARIABLE-LENGTH SERIAL I/O (CSIB)                          | 523 |

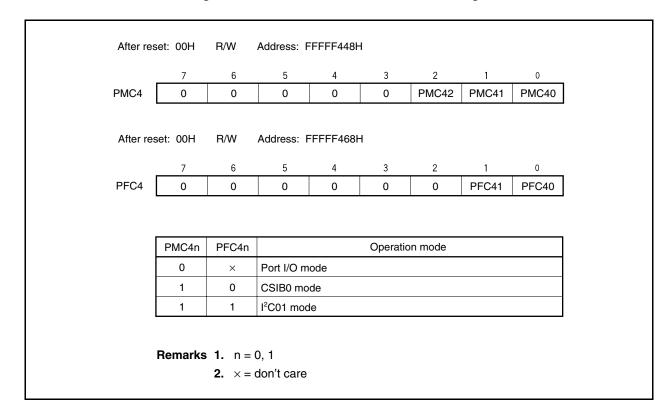

| 16.1    | Mode Switching of CSIB and Other Serial Interfaces                     | 523 |

|         | 16.1.1 CSIB4 and UARTA0 mode switching                                 | 523 |

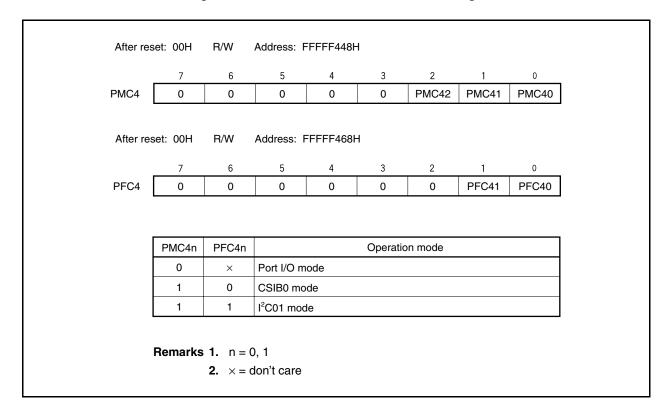

|         | 16.1.2 CSIB0 and I <sup>2</sup> C01 mode switching                     | 524 |

| 16.2    | Features                                                               | 525 |

| 16.3    | Configuration                                                          | 526 |

| 16.4    | Registers                                                              | 528 |

| 16.5    | Operation                                                              | 535 |

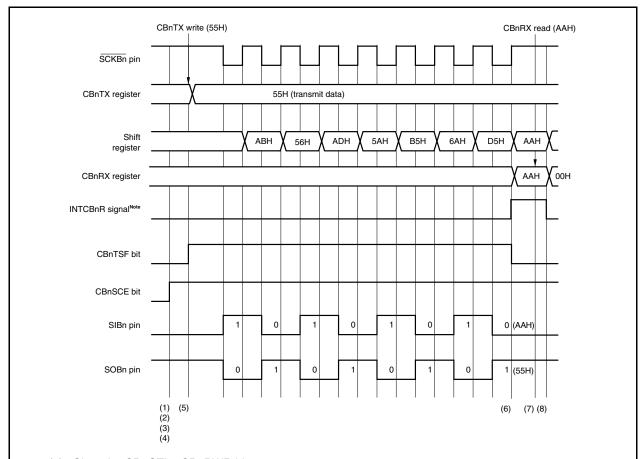

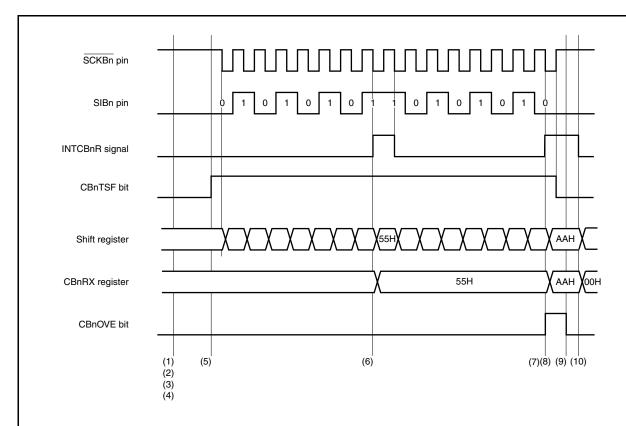

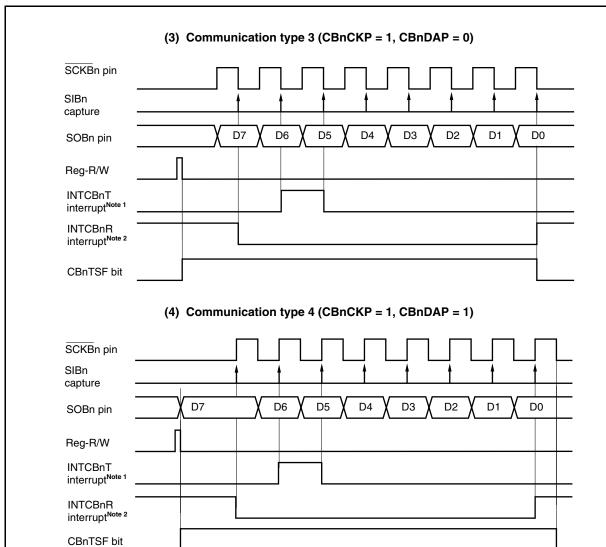

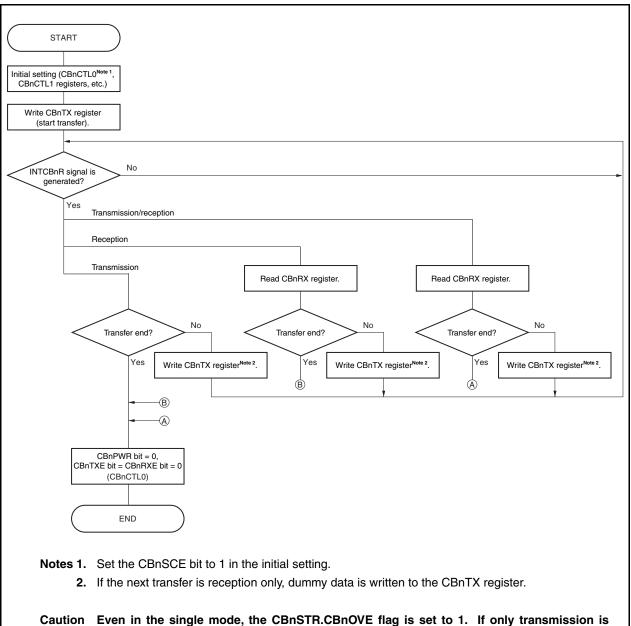

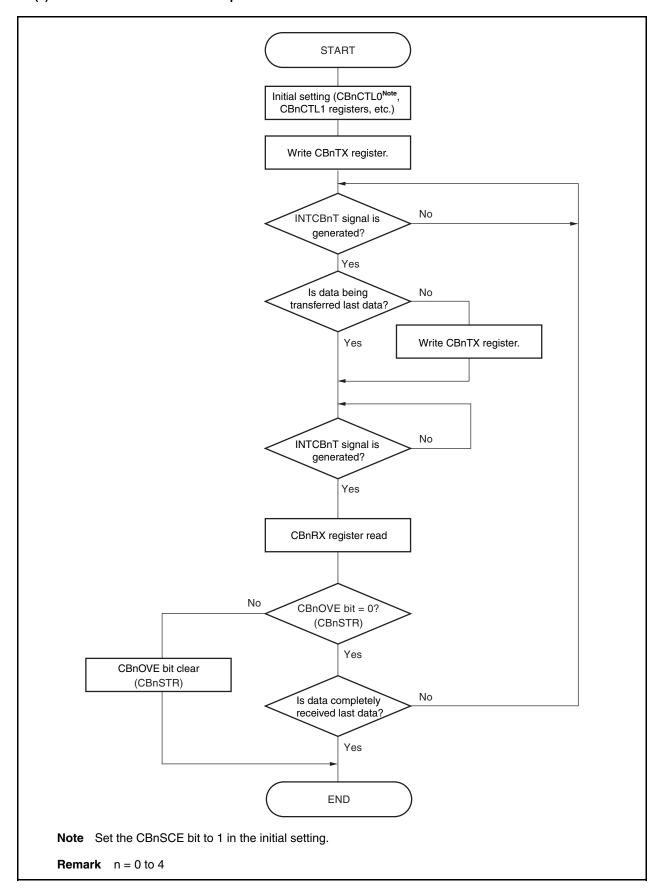

|         | 16.5.1 Single transfer mode (master mode, transmission/reception mode) | 535 |

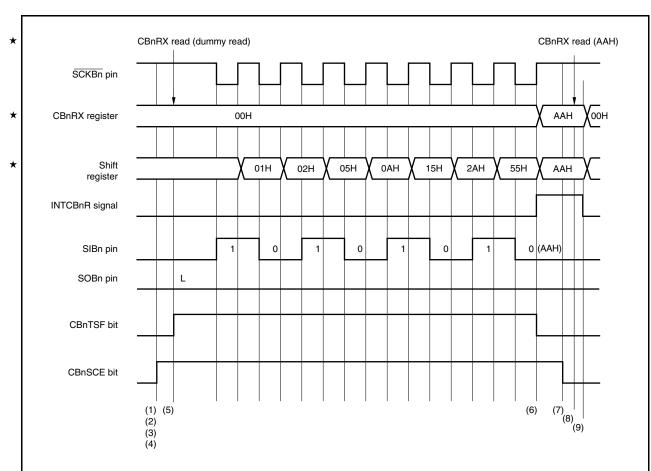

|         | 16.5.2 Single transfer mode (master mode, reception mode)              | 536 |

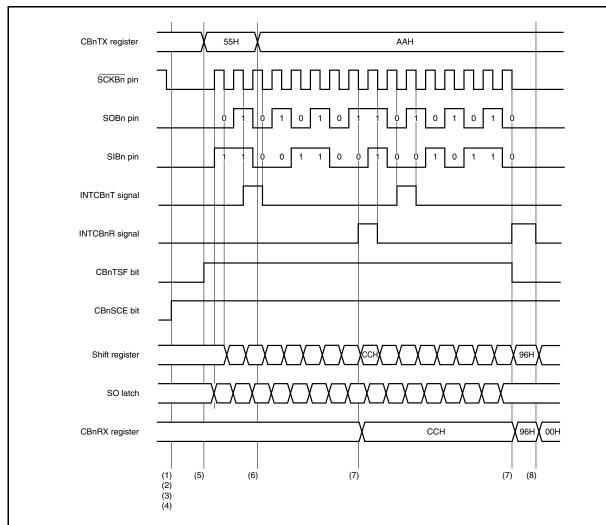

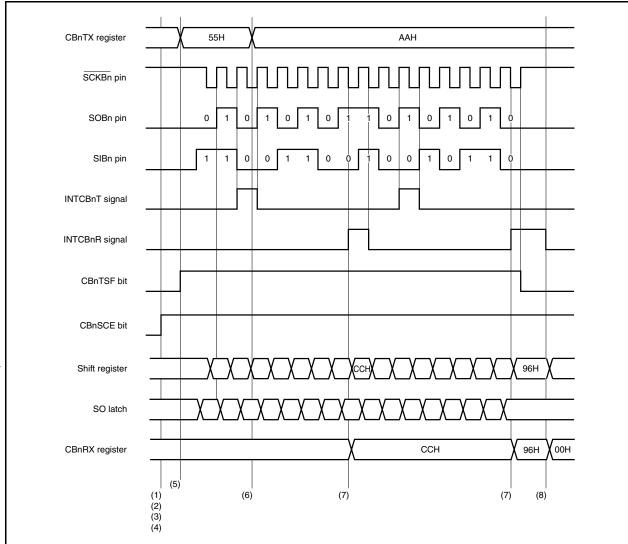

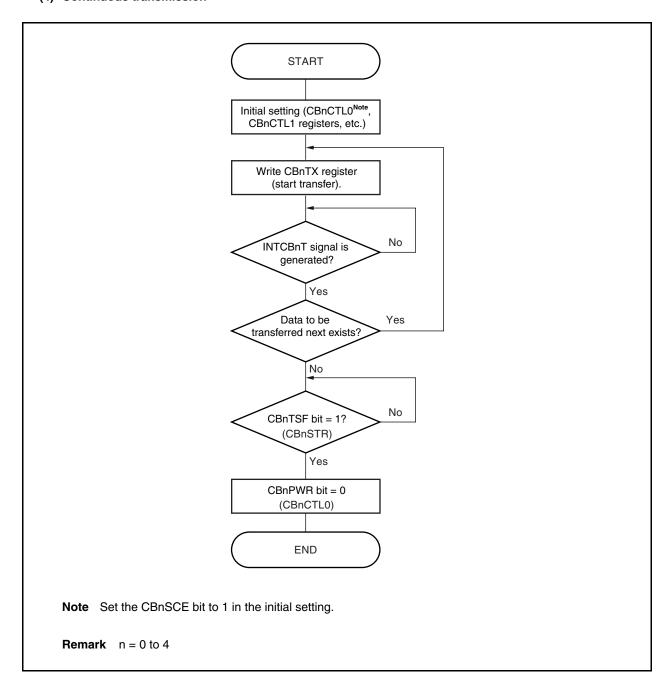

|         | 16.5.3 Continuous mode (master mode, transmission/reception mode)      | 537 |

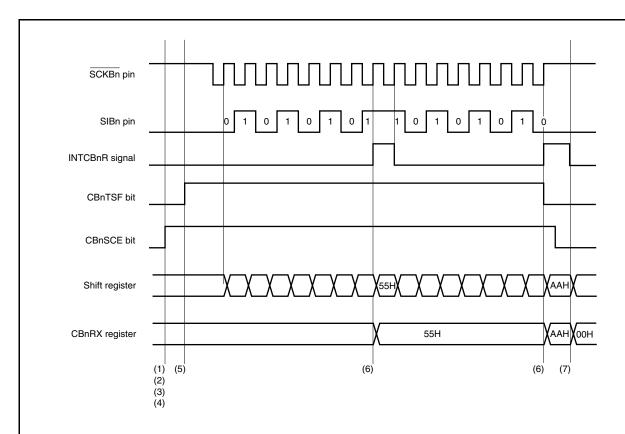

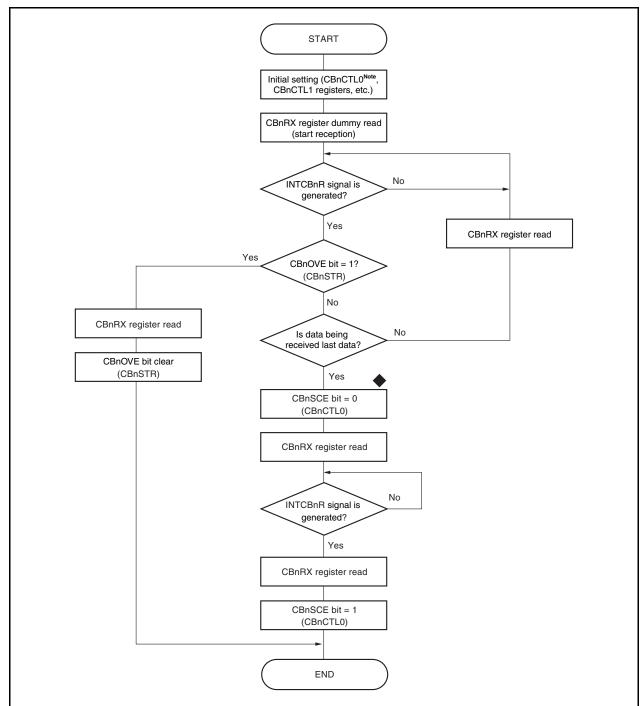

|         | 16.5.4 Continuous mode (master mode, reception mode)                   | 538 |

|         | 16.5.5 Continuous reception mode (error)                               | 539 |

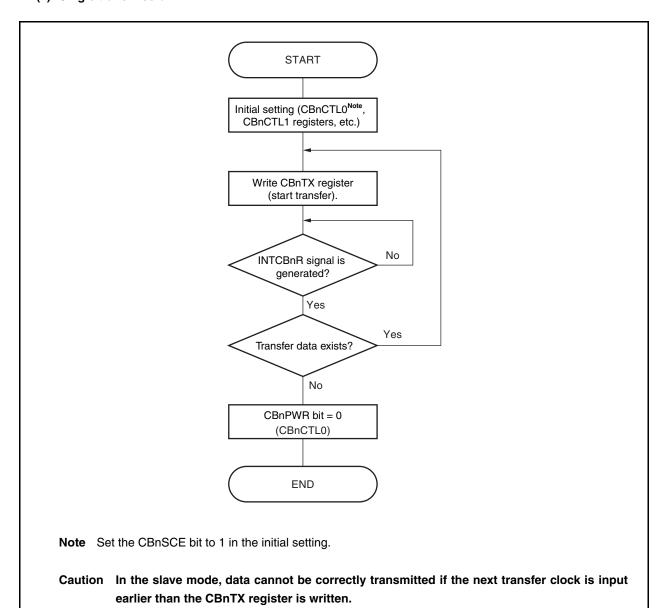

|         | 16.5.6 Continuous mode (slave mode, transmission/reception mode)       | 540 |

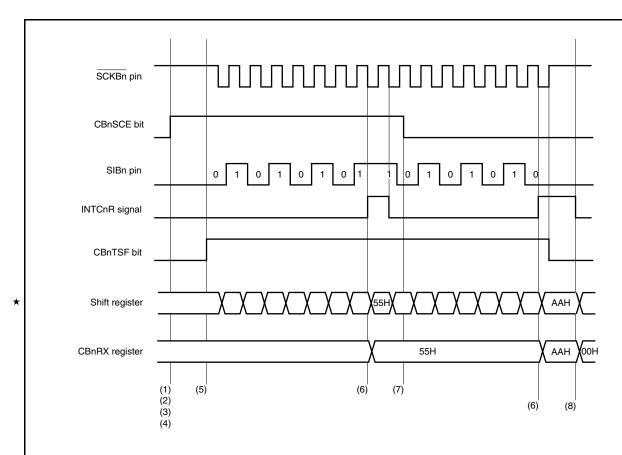

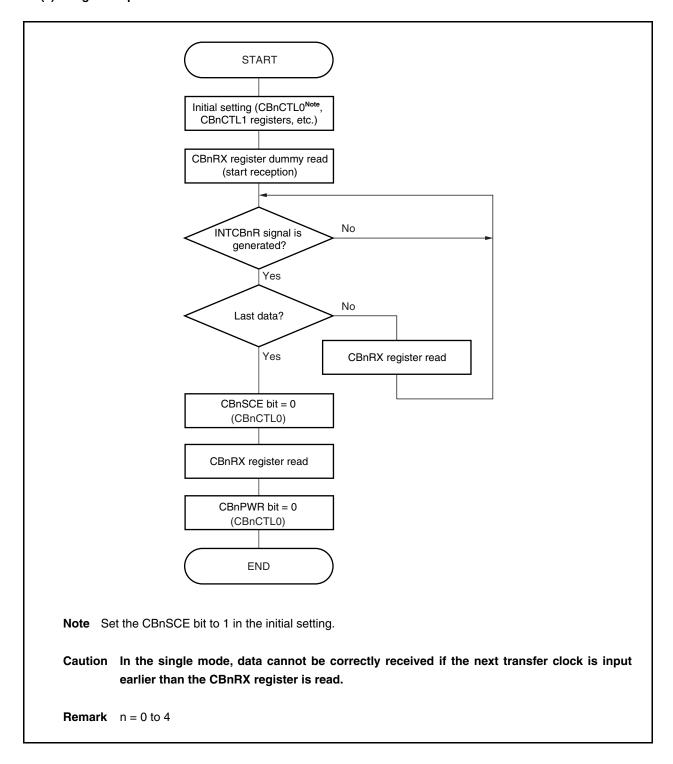

|         | 16.5.7 Continuous mode (slave mode, reception mode)                    | 541 |

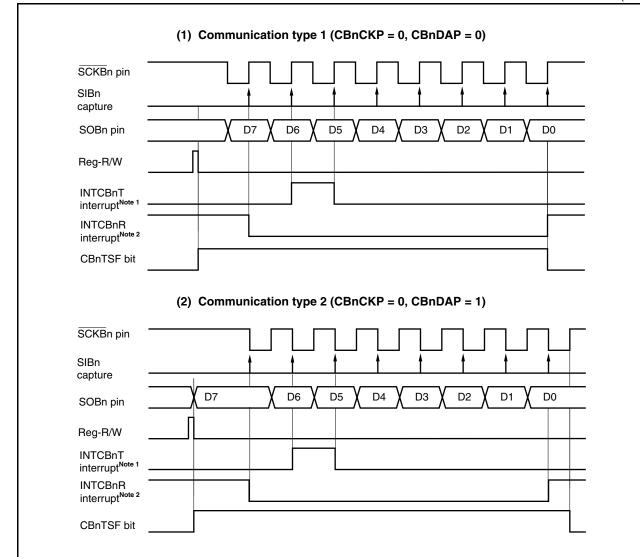

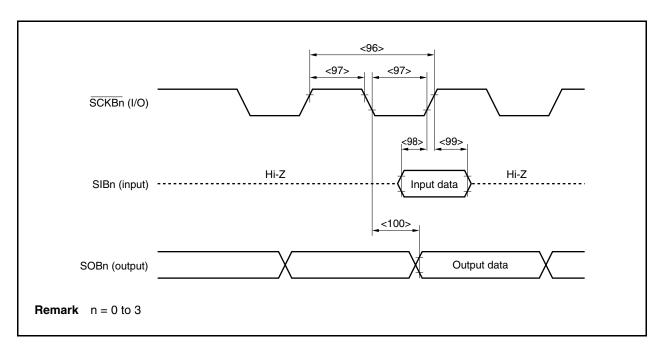

|         | 16.5.8 Clock timing                                                    | 542 |

| 16.6    | Output Pins                                                            | 544 |

| 16.7    | Operation Flow                                                         | 545 |

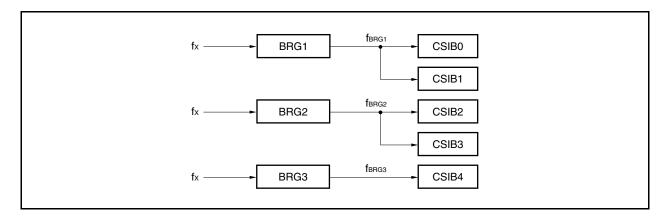

| 16.8    | Baud Rate Generator                                                    | 551 |

|         | 16.8.1 Baud rate generation                                            | 552 |

| 16.9    | Cautions                                                               | 553 |

|         |                                                                        |     |

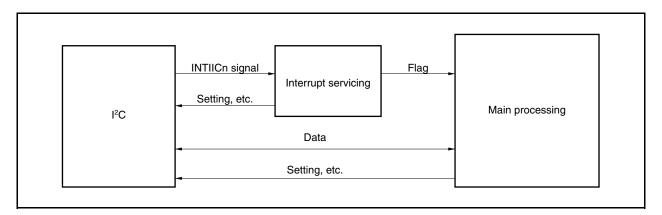

| CHAPTEF | R 17 I'C BUS                                                           | 554 |

| 17.1    | Mode Switching of I <sup>2</sup> C Bus and Other Serial Interfaces     | 554 |

|         | 17.1.1 UARTA2 and I <sup>2</sup> C00 mode switching                    |     |

|         | 17.1.2 CSIB0 and I <sup>2</sup> C01 mode switching                     |     |

|         | 17.1.3 UARTA1 and I <sup>2</sup> C02 mode switching                    |     |

| 17.2    | •                                                                      |     |

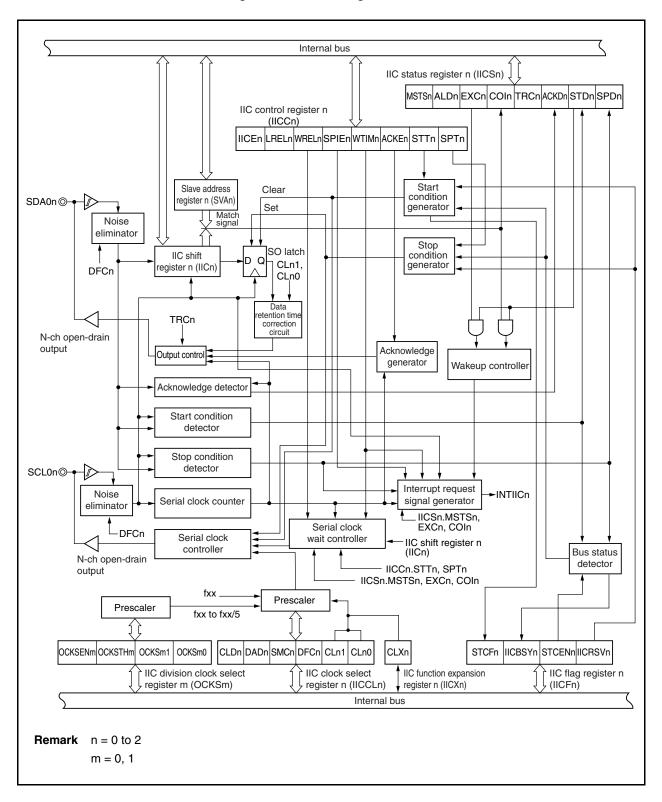

| 17.3    | Config                | uration                                                                          | 558 |

|---------|-----------------------|----------------------------------------------------------------------------------|-----|

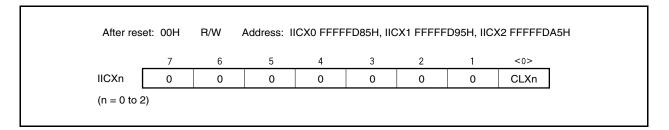

| 17.4    | Registe               | ers                                                                              | 562 |

| 17.5    | I <sup>2</sup> C Bus  | s Mode Functions                                                                 | 578 |

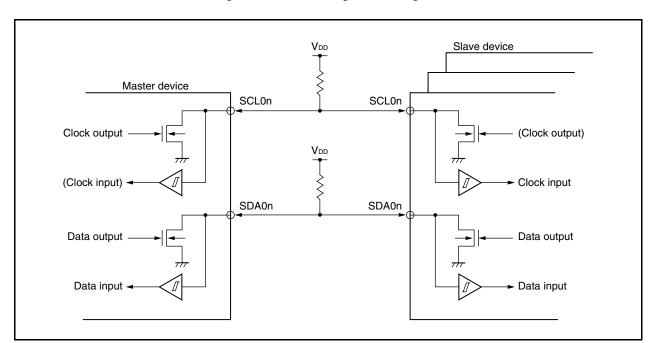

|         | 17.5.1                | Pin configuration                                                                | 578 |

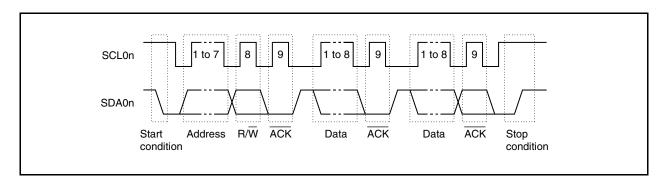

| 17.6    | I <sup>2</sup> C Bus  | Definitions and Control Methods                                                  | 579 |

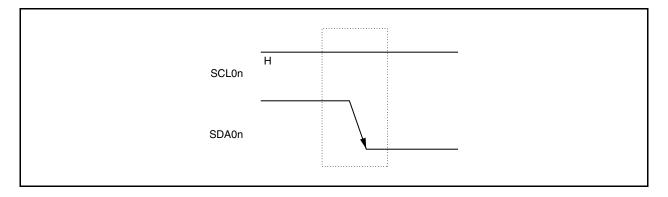

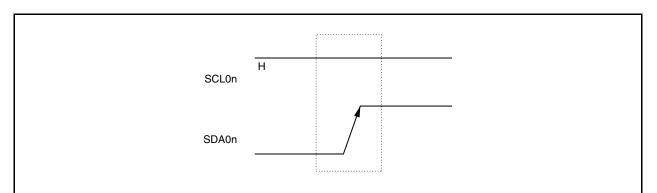

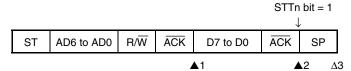

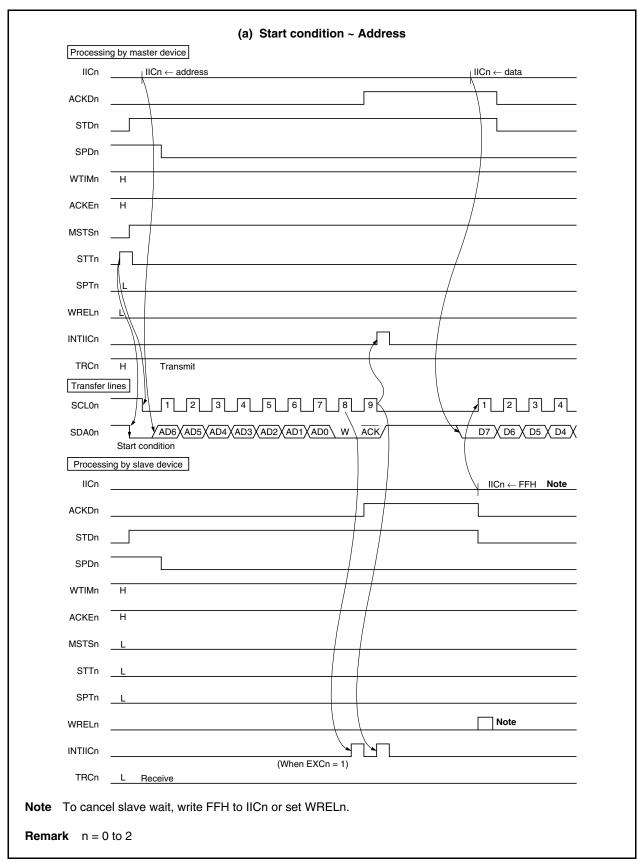

|         | 17.6.1                | Start condition                                                                  | 579 |

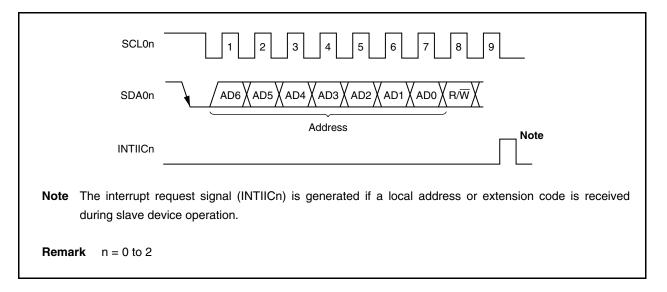

|         | 17.6.2                | Addresses                                                                        | 580 |

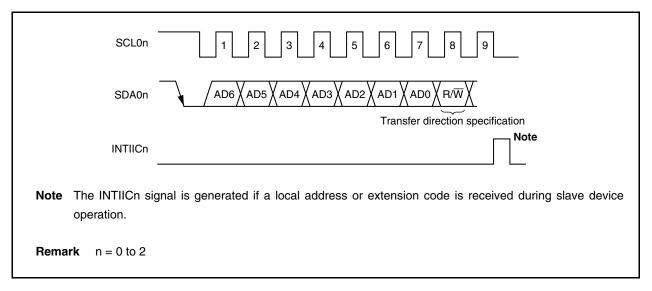

|         | 17.6.3                | Transfer direction specification                                                 | 581 |

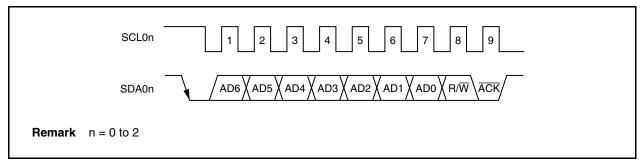

|         | 17.6.4                | ACK                                                                              | 582 |

|         | 17.6.5                | Stop condition                                                                   | 583 |

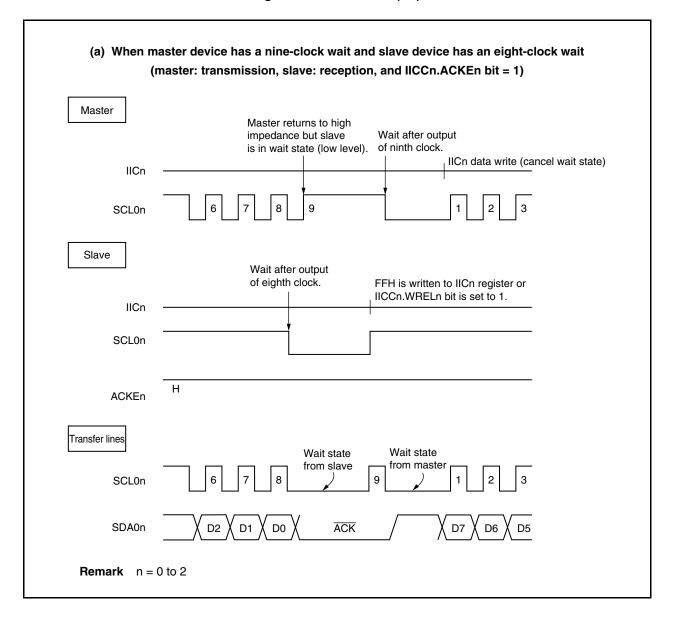

|         | 17.6.6                | Wait state                                                                       | 584 |

|         | 17.6.7                | Wait state cancellation method                                                   | 586 |

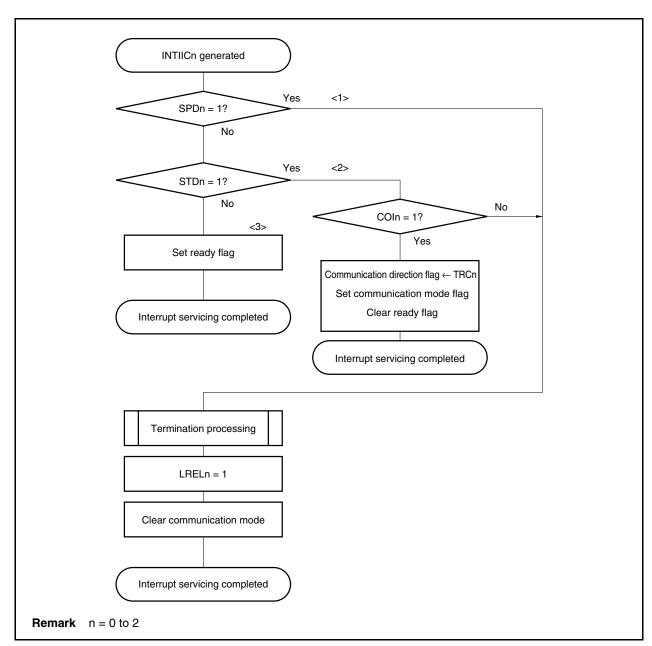

| 17.7    | I <sup>2</sup> C Inte | errupt Request Signals (INTIICn)                                                 | 587 |

|         | 17.7.1                | Master device operation                                                          | 587 |

|         | 17.7.2                | Slave device operation (when receiving slave address data (address match))       | 590 |

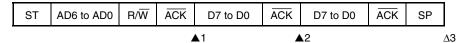

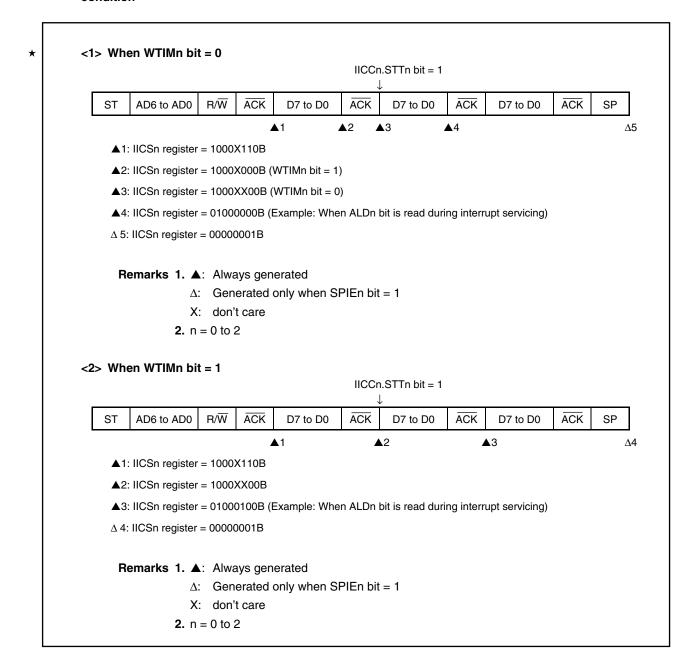

|         | 17.7.3                | Slave device operation (when receiving extension code)                           | 594 |

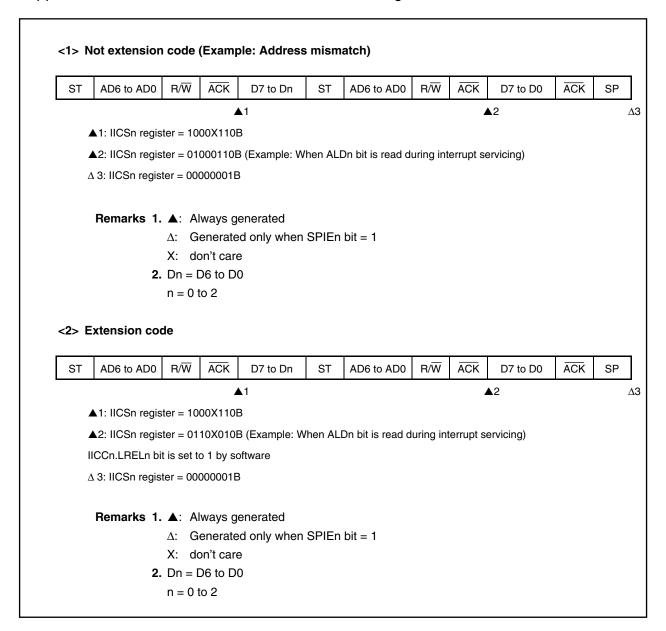

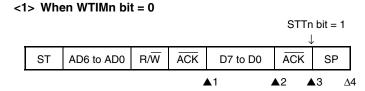

|         | 17.7.4                | Operation without communication                                                  | 598 |

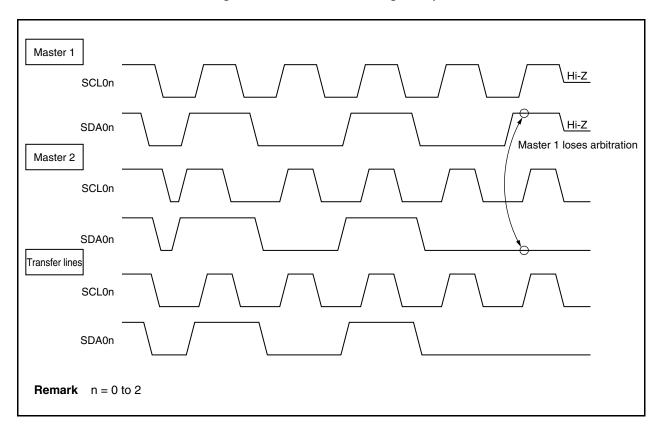

|         | 17.7.5                | Arbitration loss operation (operation as slave after arbitration loss)           | 598 |

|         | 17.7.6                | Operation when arbitration loss occurs (no communication after arbitration loss) | 600 |

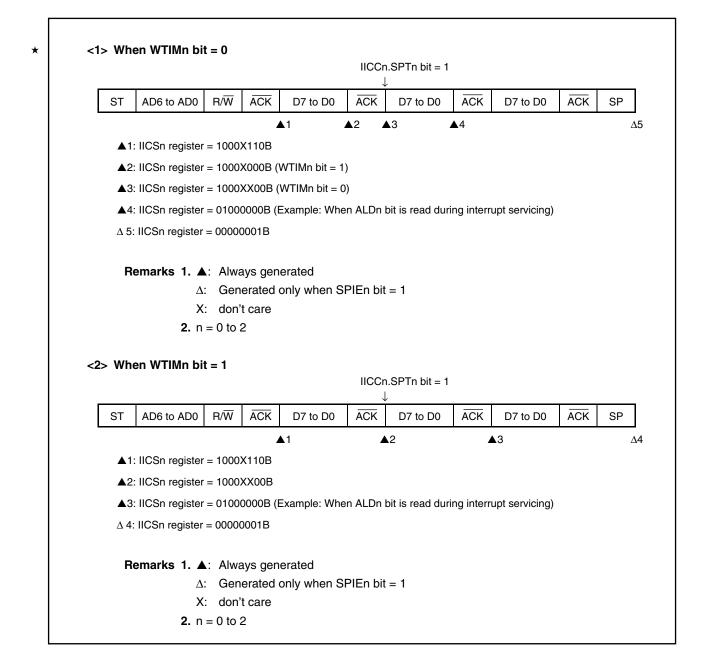

| 17.8    | Interru               | pt Request Signal (INTIICn) Generation Timing and Wait Control                   | 607 |

| 17.9    | Addres                | ss Match Detection Method                                                        | 609 |

| 17.10   | Error D               | Detection                                                                        | 609 |

| 17.11   | Extens                | ion Code                                                                         | 609 |

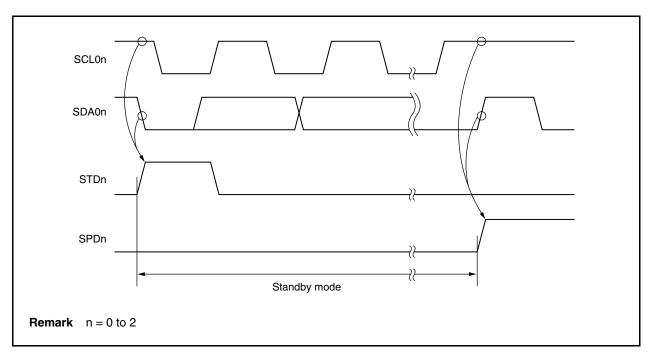

|         |                       | tion                                                                             |     |

|         |                       | p Function                                                                       |     |

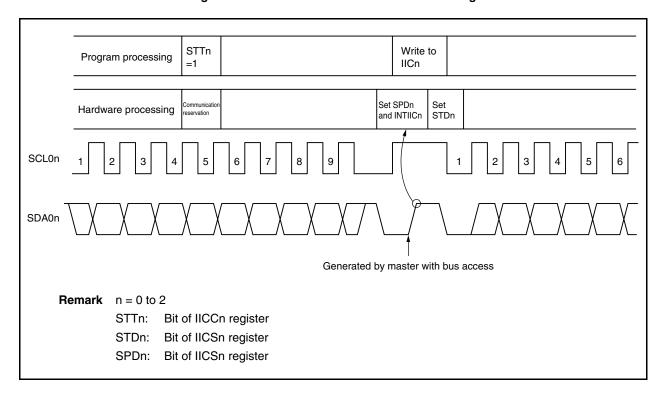

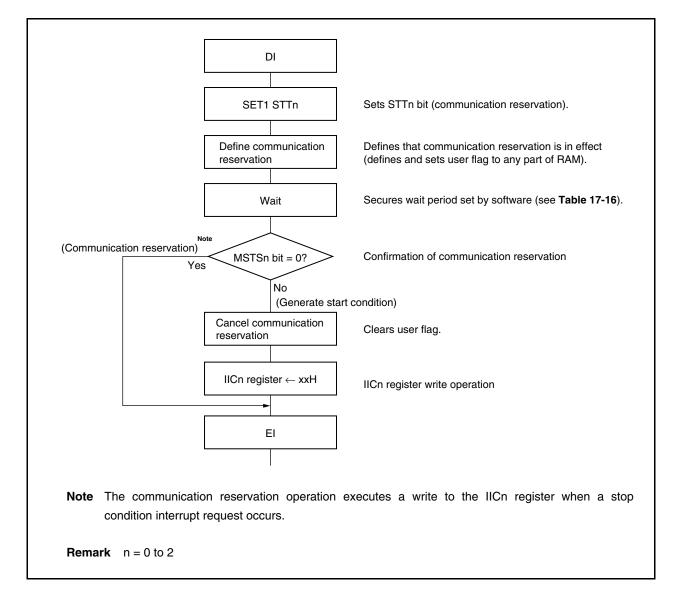

| 17.14   |                       | unication Reservation                                                            |     |

|         |                       | When communication reservation function is enabled (IICFn.IICRSVn bit = 0)       |     |

|         |                       | When communication reservation function is disabled (IICFn.IICRSVn bit = 1)      |     |

|         |                       | ns                                                                               |     |

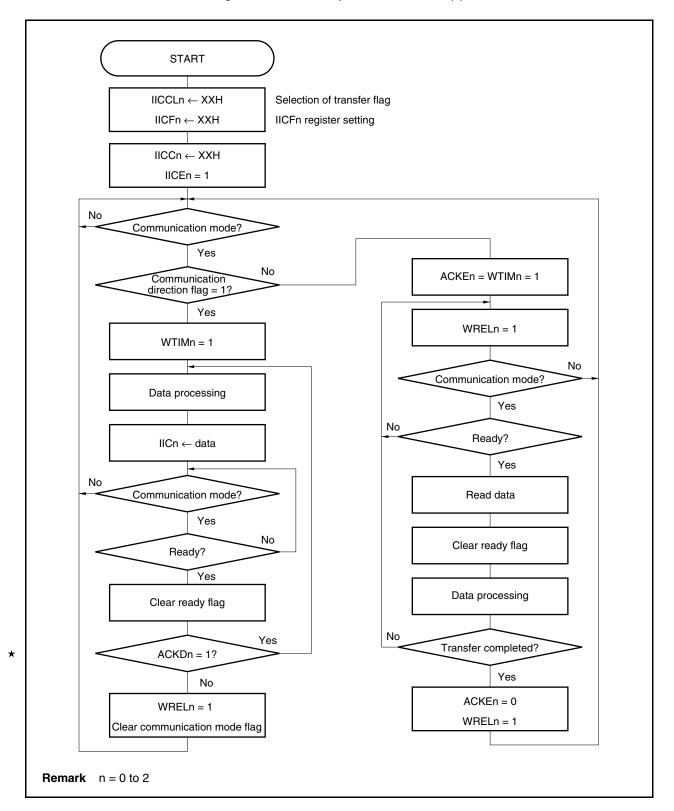

| 17.16   |                       | unication Operations                                                             |     |

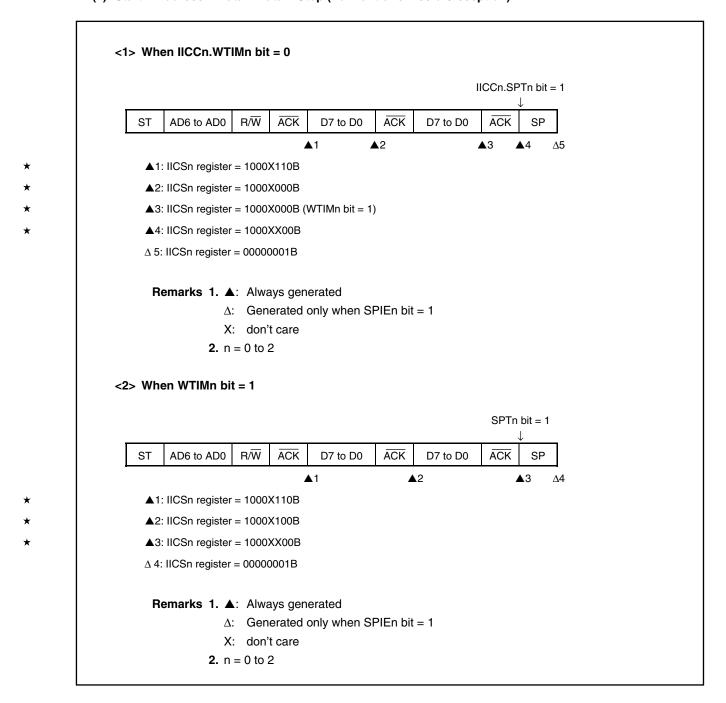

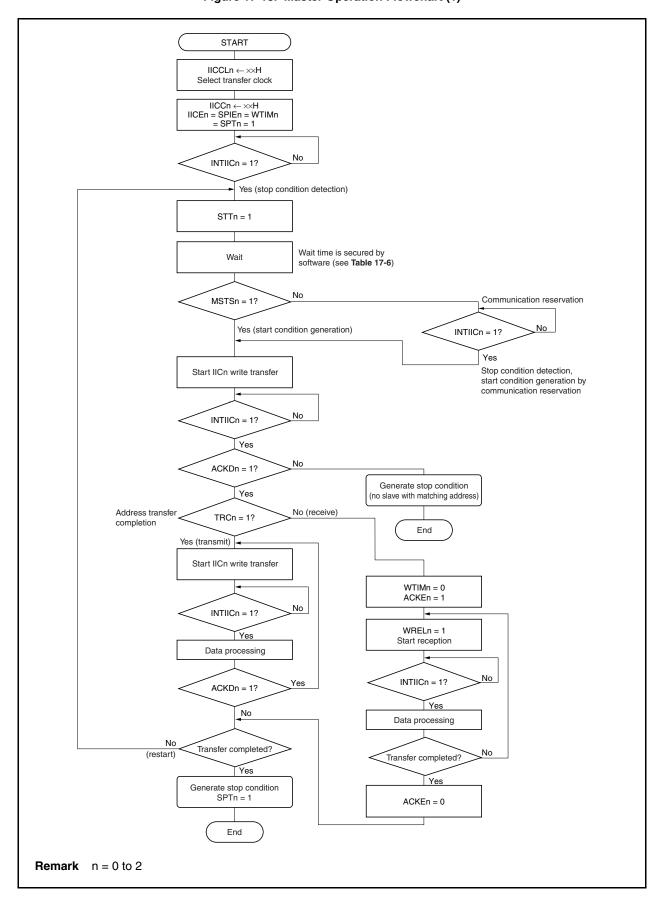

|         | 17.16.1               | Master operation 1                                                               | 618 |

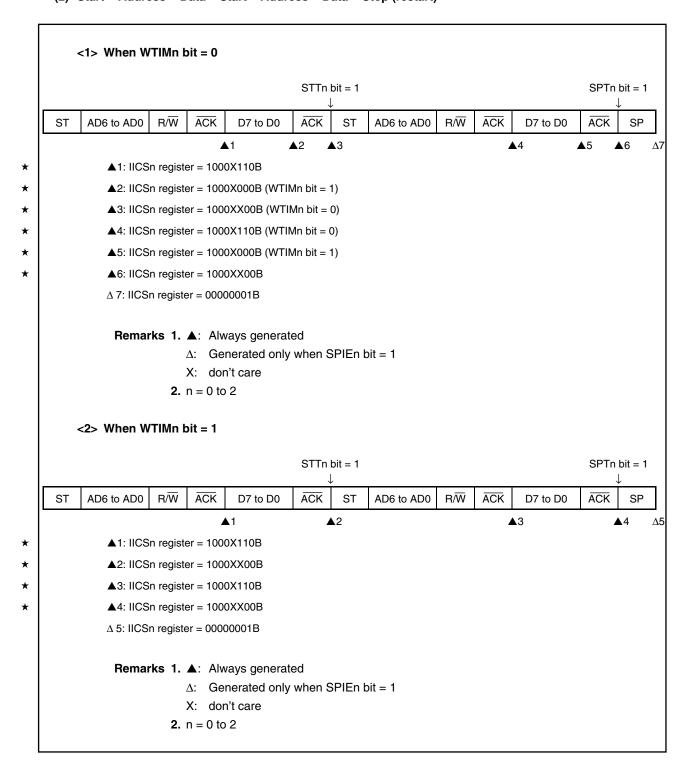

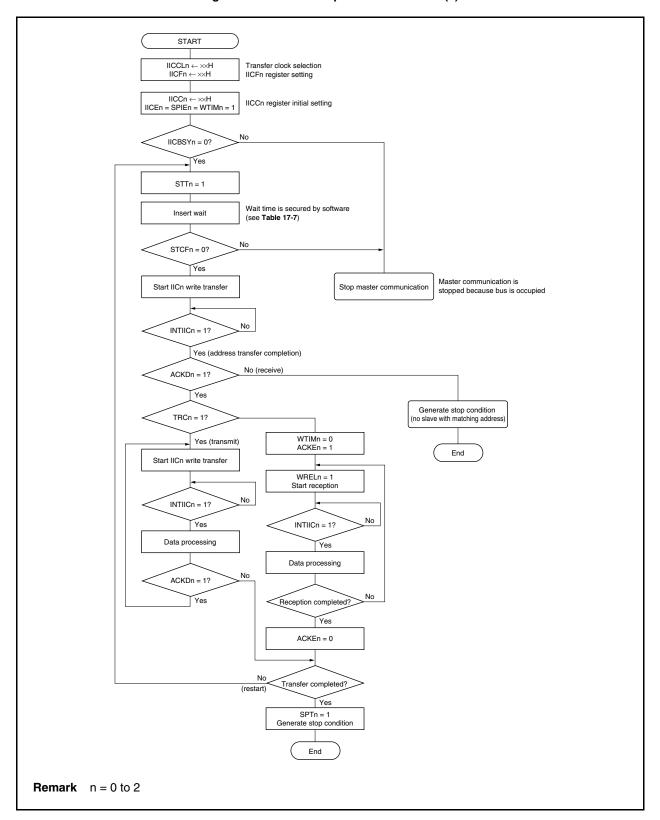

|         |                       | Master operation 2                                                               |     |

|         |                       | Slave operation                                                                  |     |

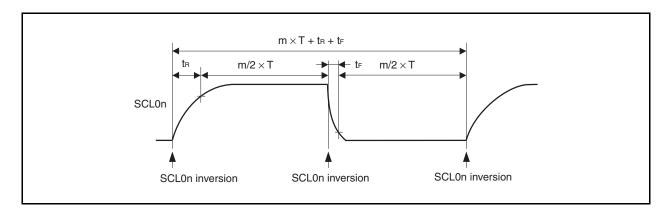

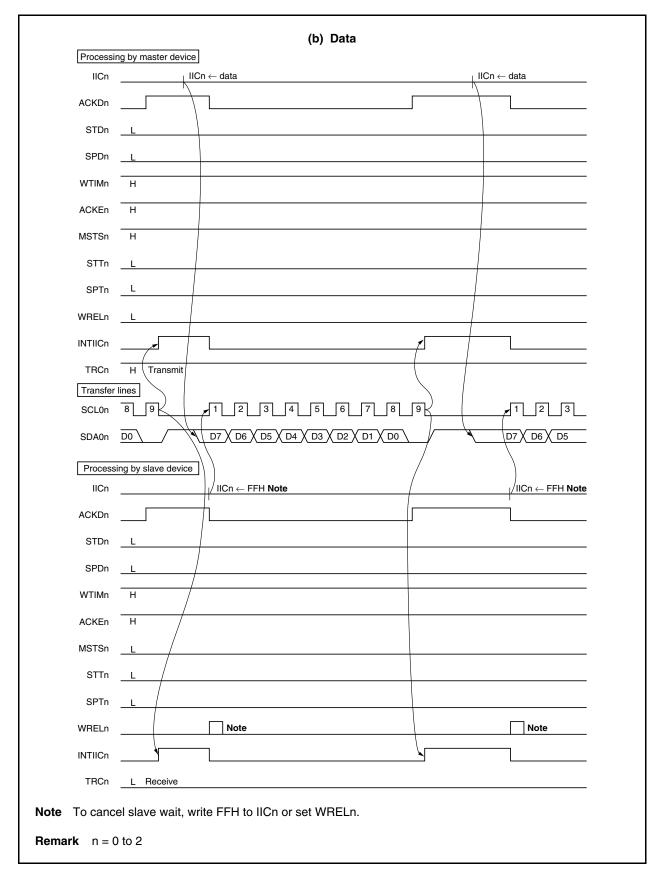

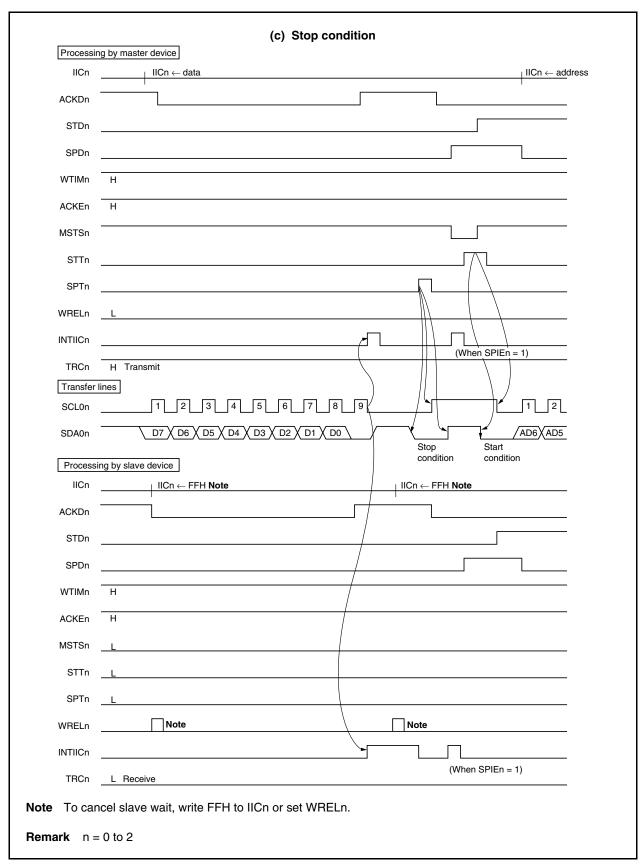

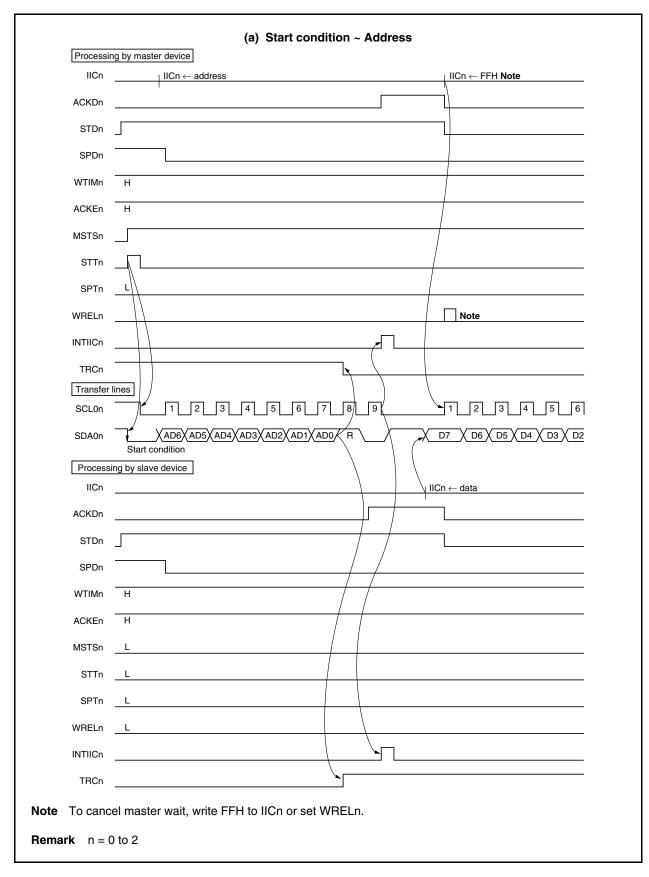

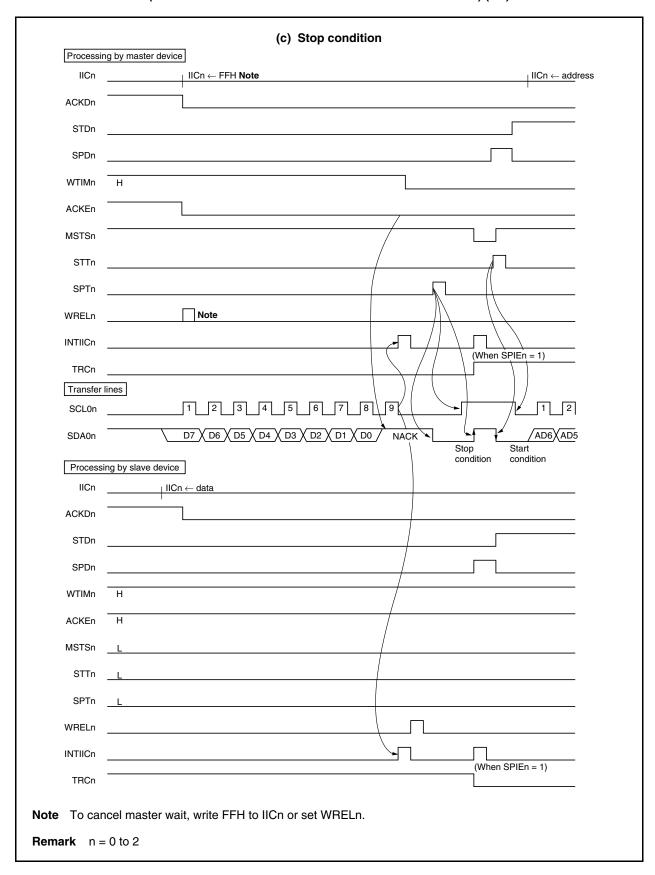

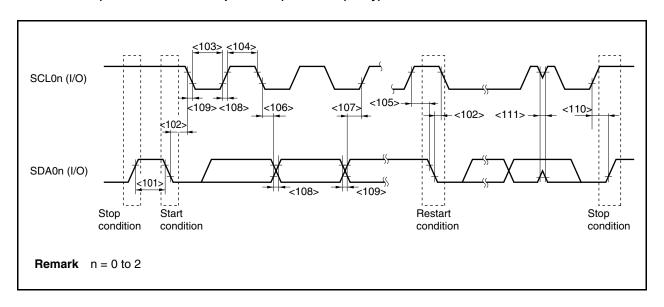

| 17.17   | Timing                | of Data Communication                                                            | 624 |

| CHAPTER | 18 IEI                | Bus CONTROLLER                                                                   | 631 |

| 18.1    | Function              | ons                                                                              | 631 |

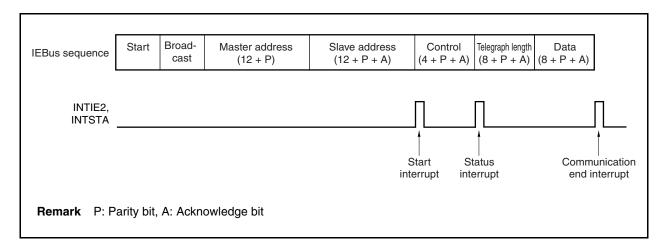

|         | 18.1.1                | Communication protocol of IEBus                                                  | 631 |

|         | 18.1.2                | Determination of bus mastership (arbitration)                                    | 632 |

|         | 18.1.3                | Communication mode                                                               | 632 |

|         | 18.1.4                | Communication address                                                            | 632 |

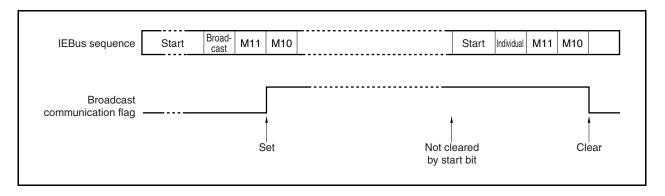

|         | 18.1.5                | Broadcast communication                                                          | 633 |

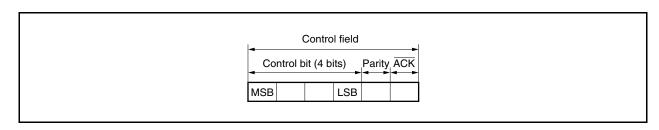

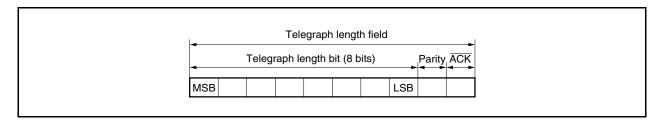

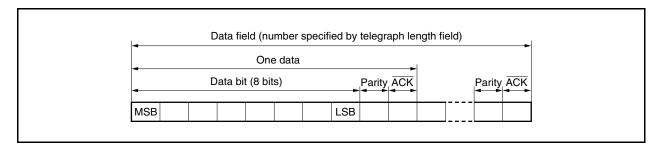

|         | 18.1.6                | Transfer format of IEBus                                                         | 633 |

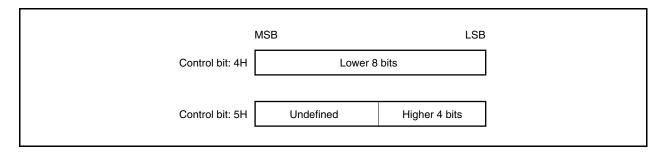

|         | 18.1.7                | Transfer data                                                                    | 643 |

|         | 18.1.8                | Bit format                                                                       | 645 |

| 18.2    | Config                | uration                                                                          | 646 |

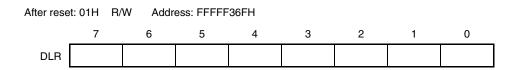

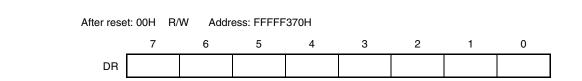

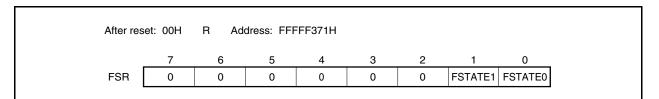

| 18.3    | Registe               | ers                                                                              | 648 |

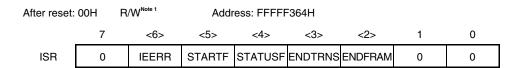

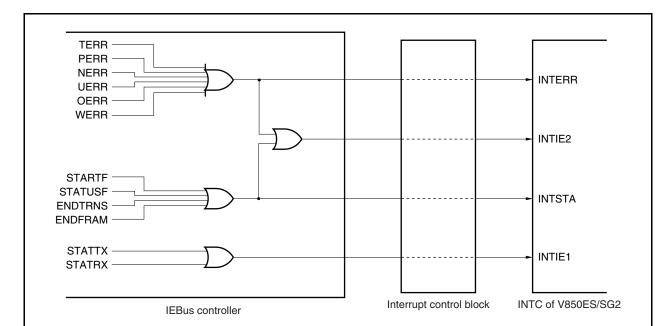

| 18.4    | Interru               | pt Operations of IEBus Controller                                                | 678 |

|    |       | 18.4.1           | Interrupt control block                                              | 678 |

|----|-------|------------------|----------------------------------------------------------------------|-----|

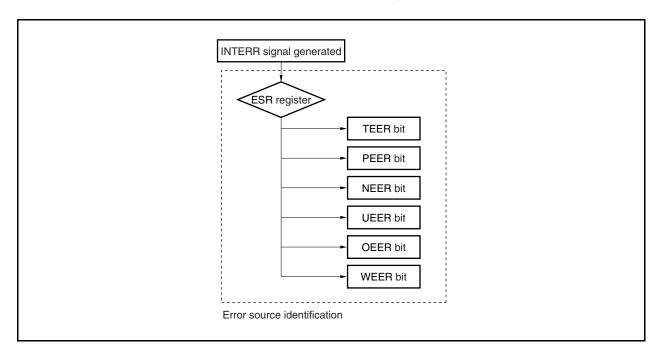

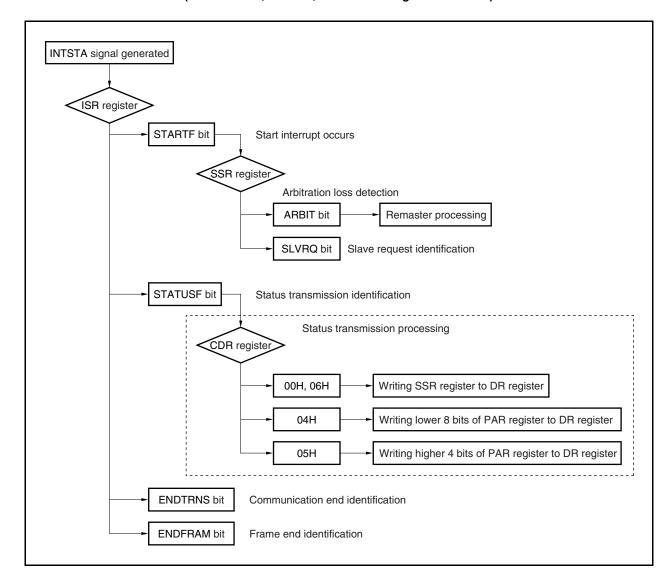

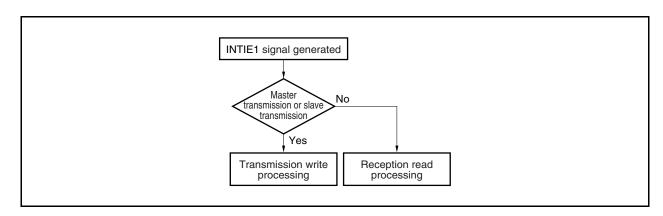

|    |       | 18.4.2           | Example of identifying interrupt                                     | 680 |

|    |       | 18.4.3           | Interrupt source list                                                | 683 |

|    |       | 18.4.4           | Communication error source processing list                           | 684 |

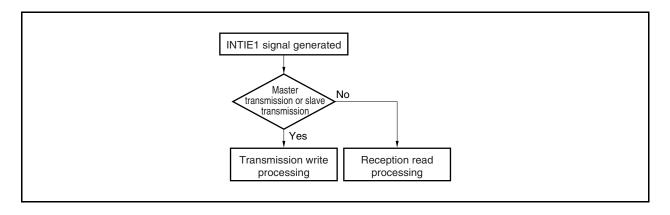

|    | 18.5  | Interru          | upt Request Signal Generation Timing and Main CPU Processing         | 686 |

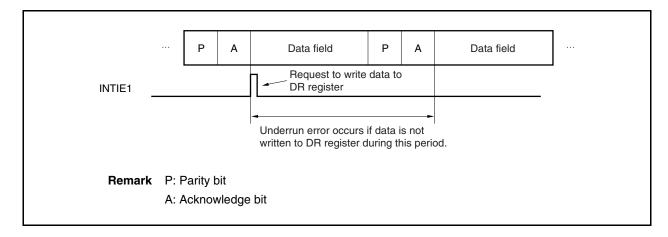

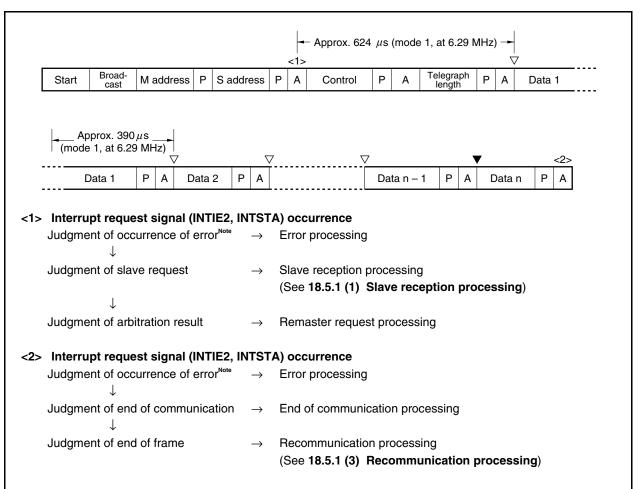

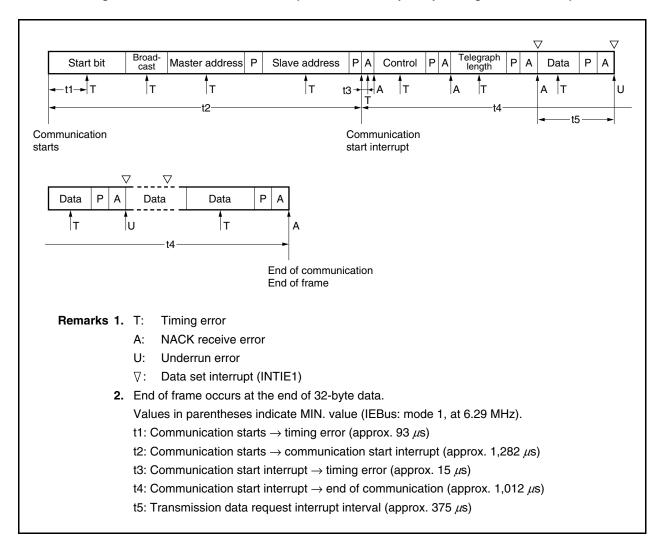

|    |       | 18.5.1           | Master transmission                                                  | 686 |

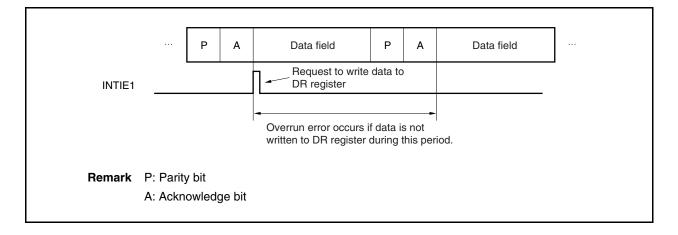

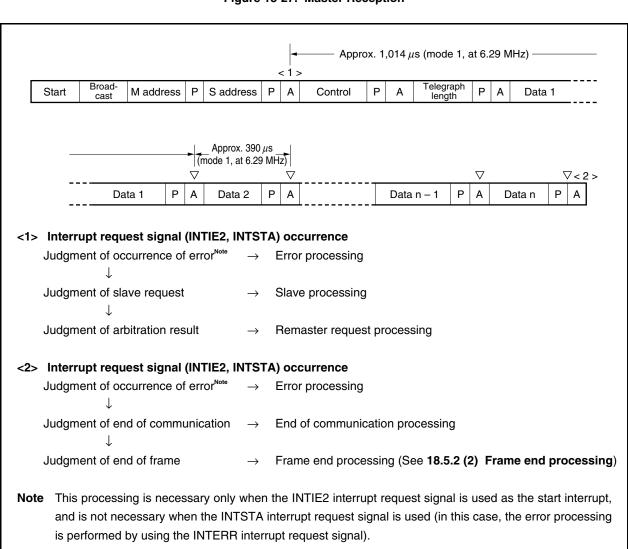

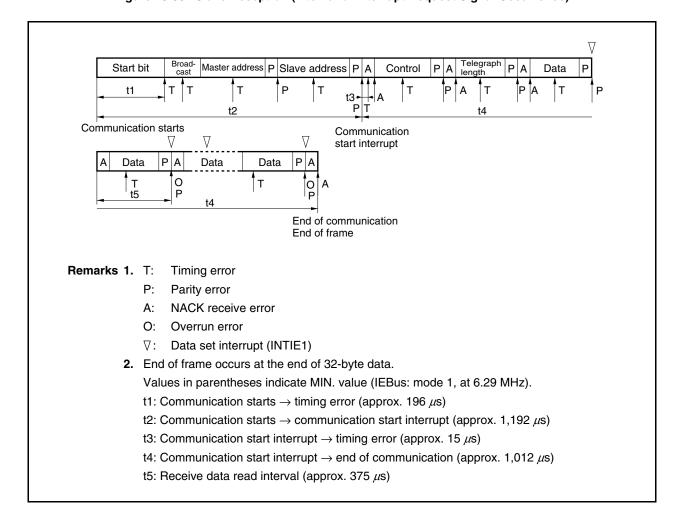

|    |       | 18.5.2           | Master reception                                                     | 688 |

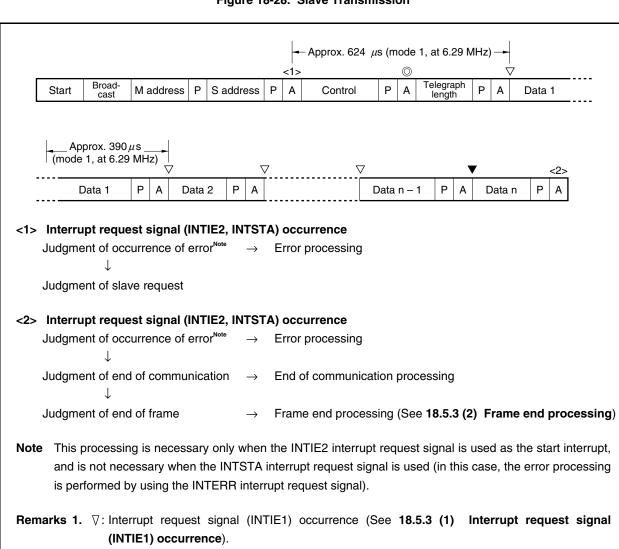

|    |       | 18.5.3           | Slave transmission                                                   | 690 |

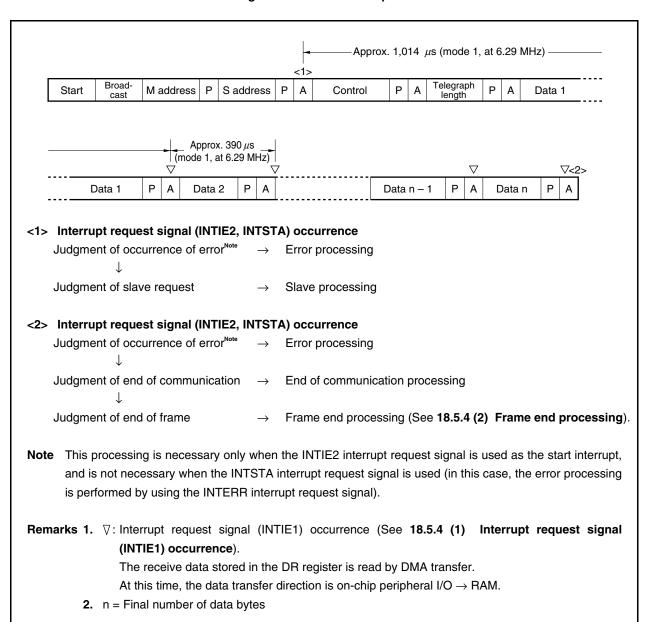

|    |       | 18.5.4           | Slave reception                                                      | 692 |

|    |       | 18.5.5           | Interval of occurrence of interrupt request signal for IEBus control | 694 |

| СН | APTER | 19 C             | AN CONTROLLER                                                        | 698 |

|    | 19.1  | Overvi           | iew                                                                  | 698 |

|    |       | 19.1.1           | Features                                                             | 698 |

|    |       | 19.1.2           | Overview of functions                                                | 699 |

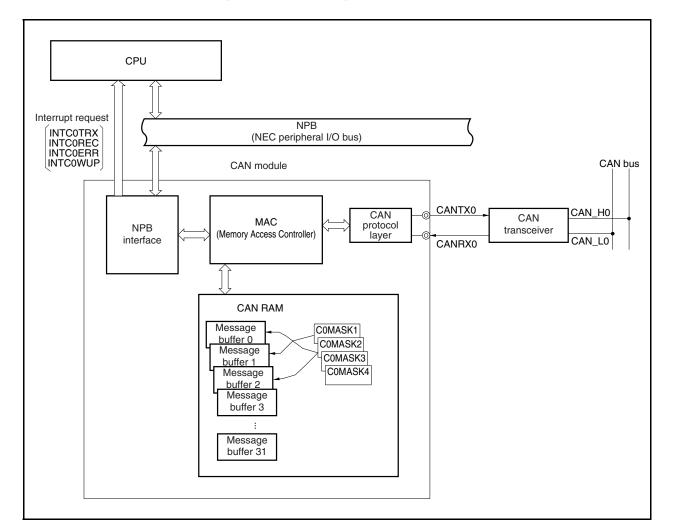

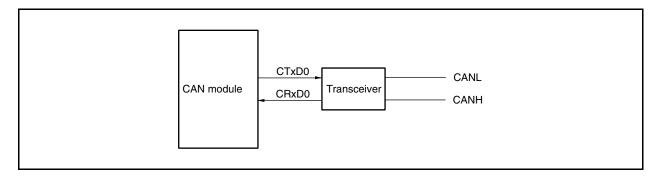

|    |       | 19.1.3           | Configuration                                                        | 700 |

|    | 19.2  | CAN P            | Protocol                                                             | 701 |

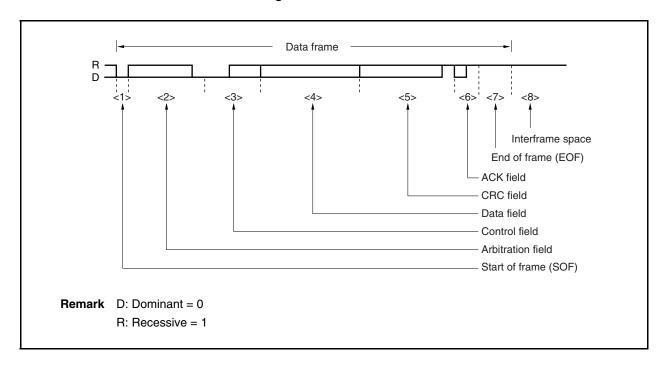

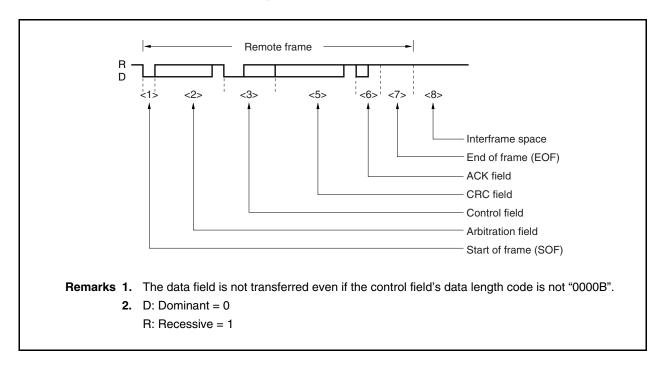

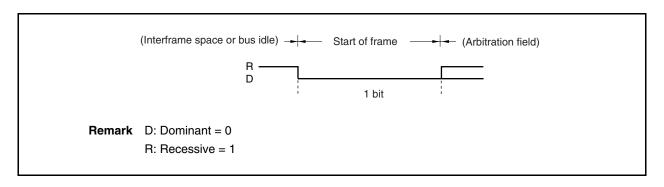

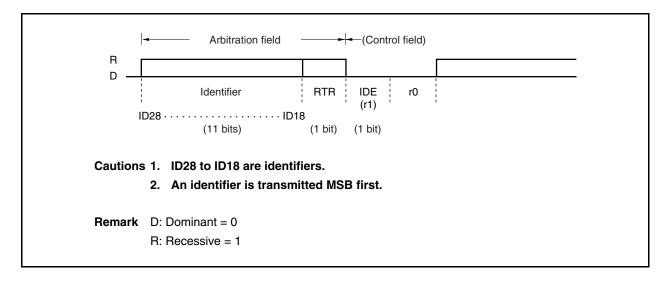

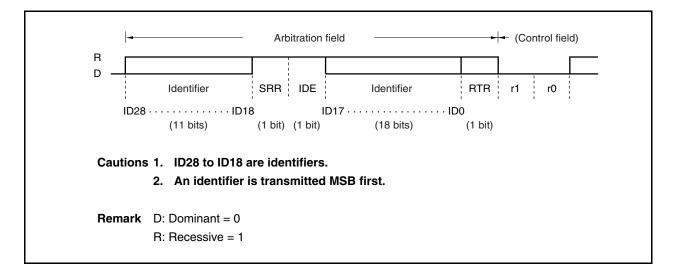

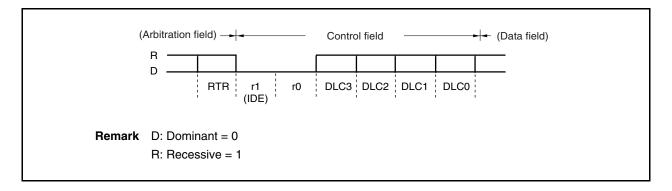

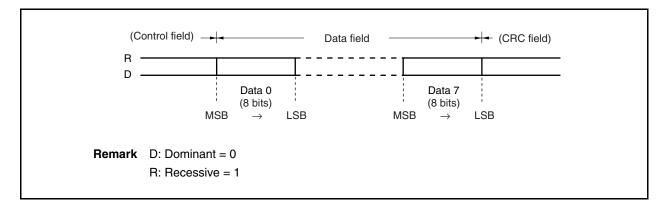

|    |       | 19.2.1           | Frame format                                                         | 701 |

|    |       | 19.2.2           | Frame types                                                          | 702 |

|    |       | 19.2.3           | Data frame and remote frame                                          | 702 |

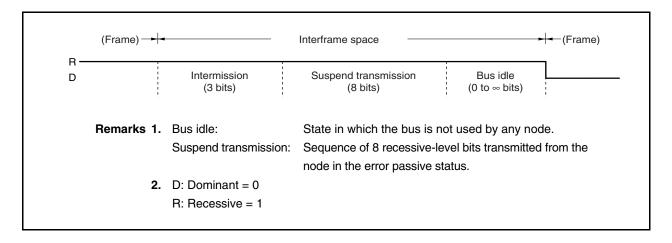

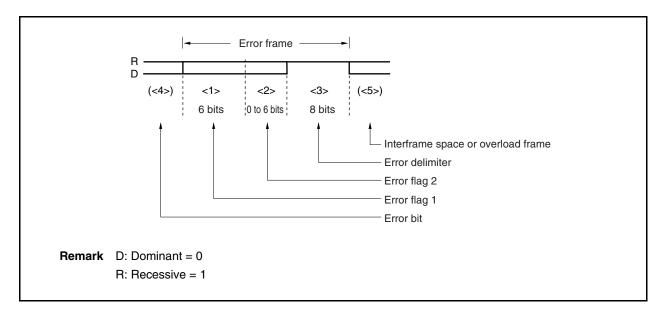

|    |       | 19.2.4           | Error frame                                                          | 710 |

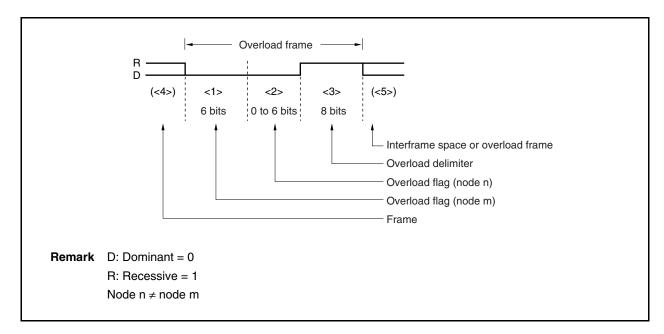

|    |       | 19.2.5           | Overload frame                                                       | 711 |

|    | 19.3  | Functi           | ions                                                                 | 712 |

|    |       | 19.3.1           | Determining bus priority                                             | 712 |

|    |       | 19.3.2           | Bit stuffing                                                         | 712 |

|    |       | 19.3.3           | Multi masters                                                        | 712 |

|    |       | 19.3.4           | Multi cast                                                           |     |

|    |       | 19.3.5           | CAN sleep mode/CAN stop mode function                                |     |

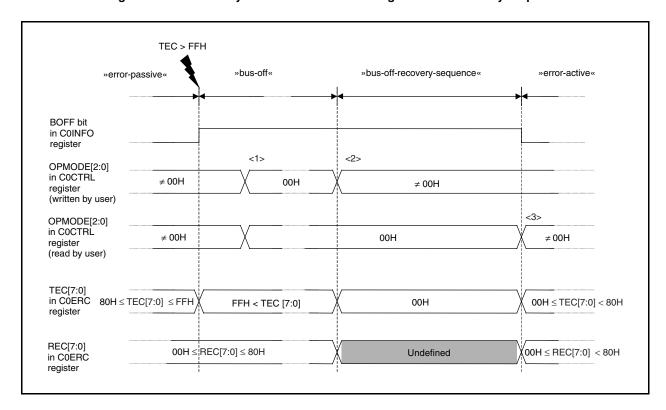

|    |       | 19.3.6           | Error control function                                               | 713 |

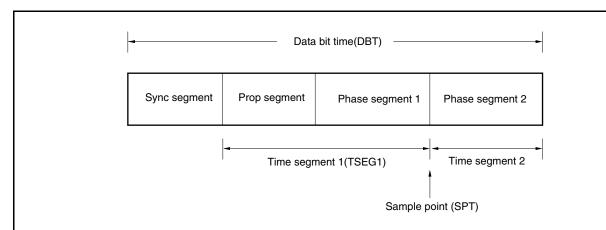

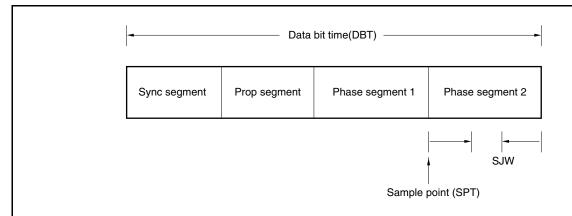

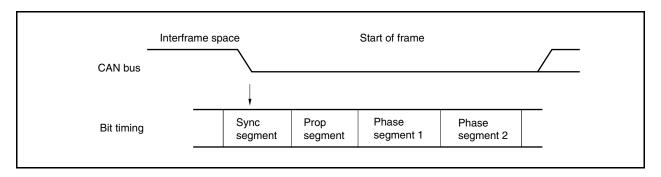

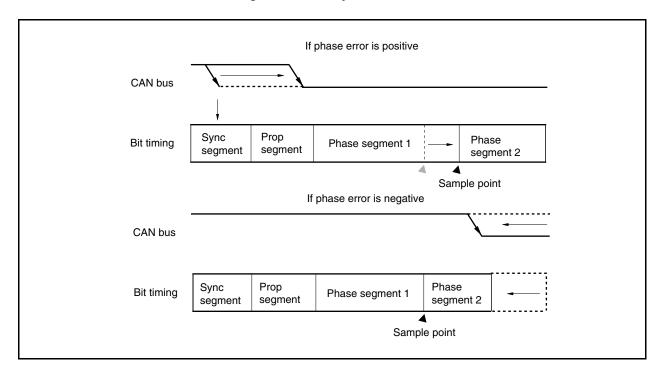

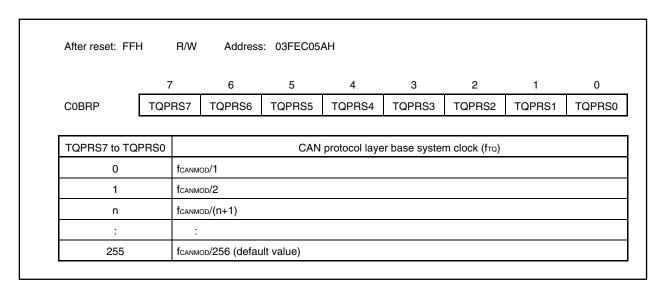

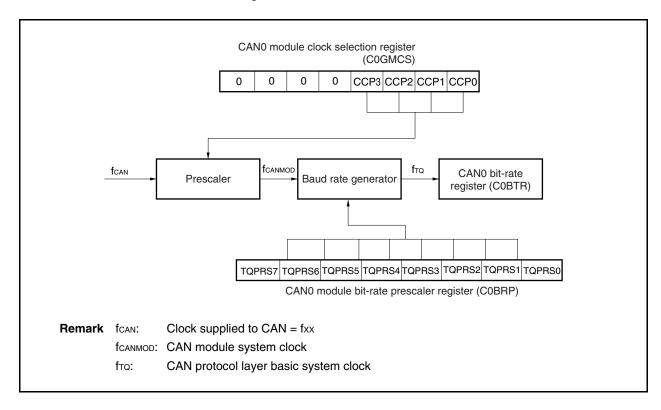

|    |       | 19.3.7           | Baud rate control function                                           |     |

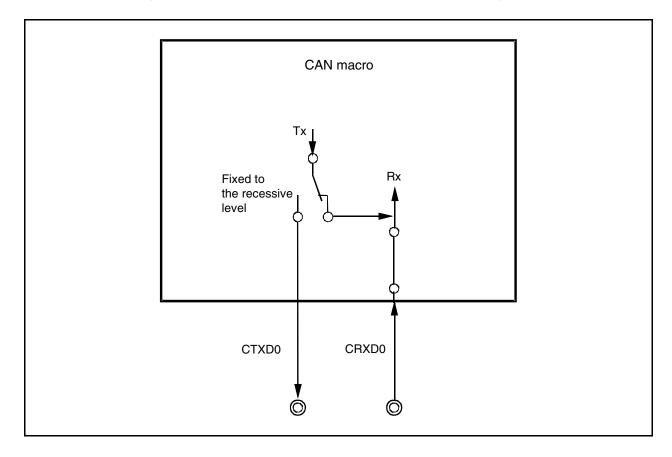

|    | 19.4  |                  | ection with Target System                                            |     |

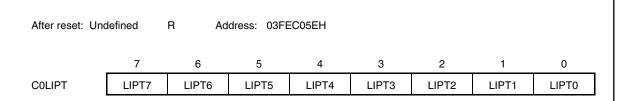

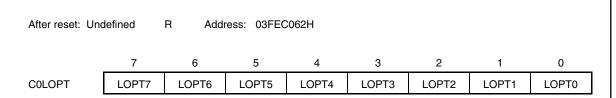

|    | 19.5  | Interna          | al Registers of CAN Controller                                       |     |

|    |       | 19.5.1           | CAN controller configuration                                         |     |

|    |       | 19.5.2           | Register access type                                                 |     |

|    |       | 19.5.3           | Register bit configuration                                           |     |

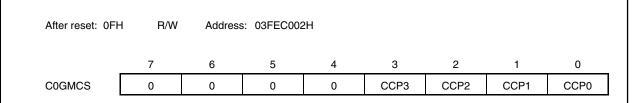

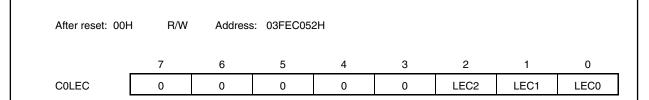

|    | 19.6  | _                | ters                                                                 |     |

|    | 19.7  |                  | t/Clear Function                                                     | _   |

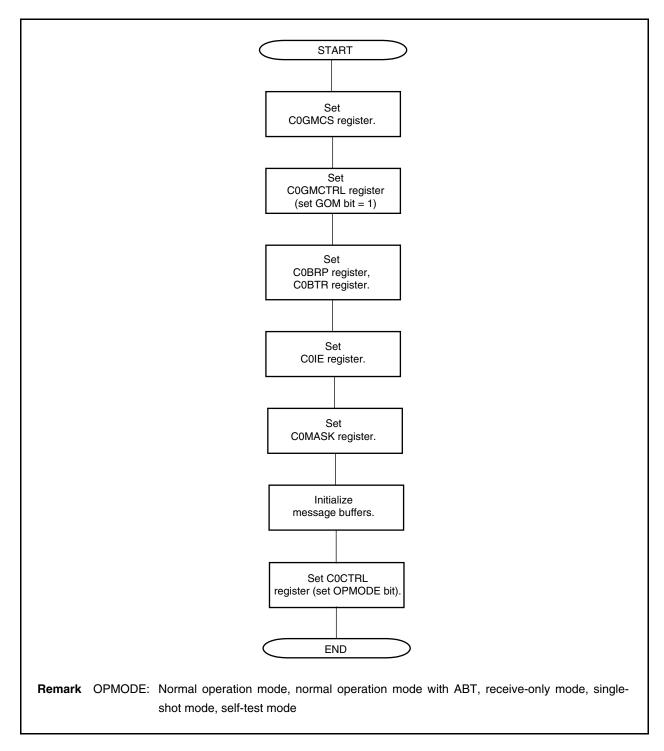

|    | 19.8  |                  | Controller Initialization                                            |     |

|    |       | 19.8.1           | Initialization of CAN module                                         |     |

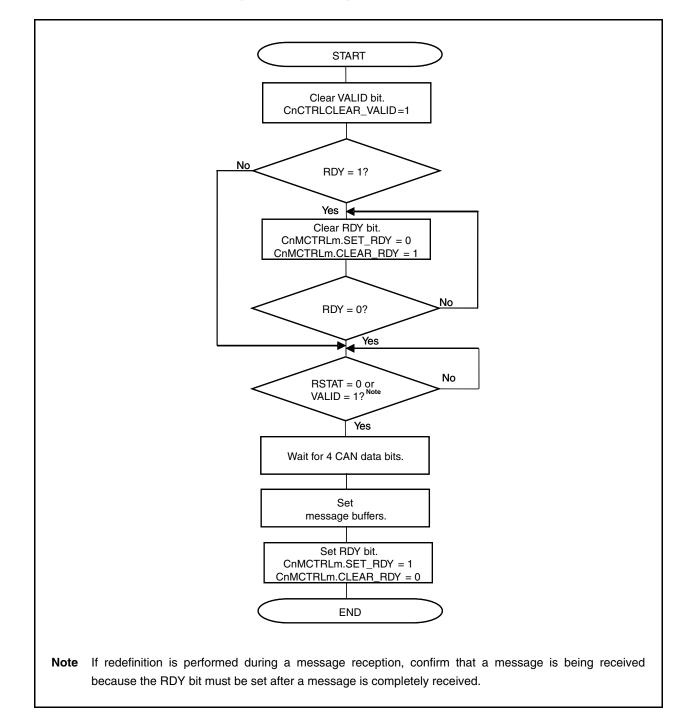

|    |       | 19.8.2           | Initialization of message buffer                                     |     |

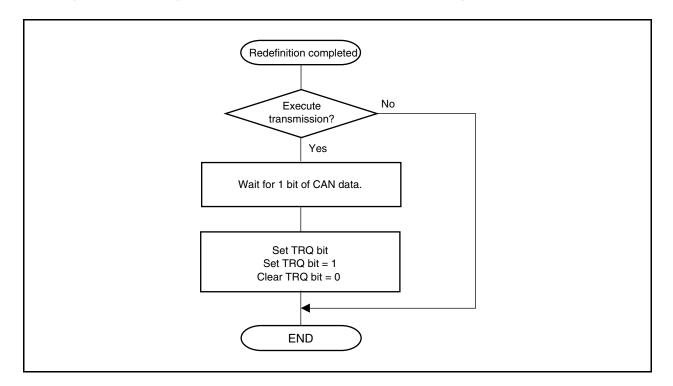

|    |       | 19.8.3           | Redefinition of message buffer                                       |     |

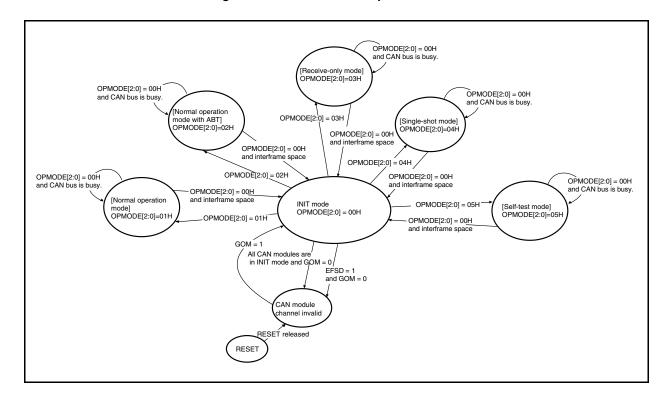

|    |       | 19.8.4           | Transition from initialization mode to operation mode                |     |

|    | 10.0  | 19.8.5           | Resetting error counter C0ERC of CAN module                          |     |

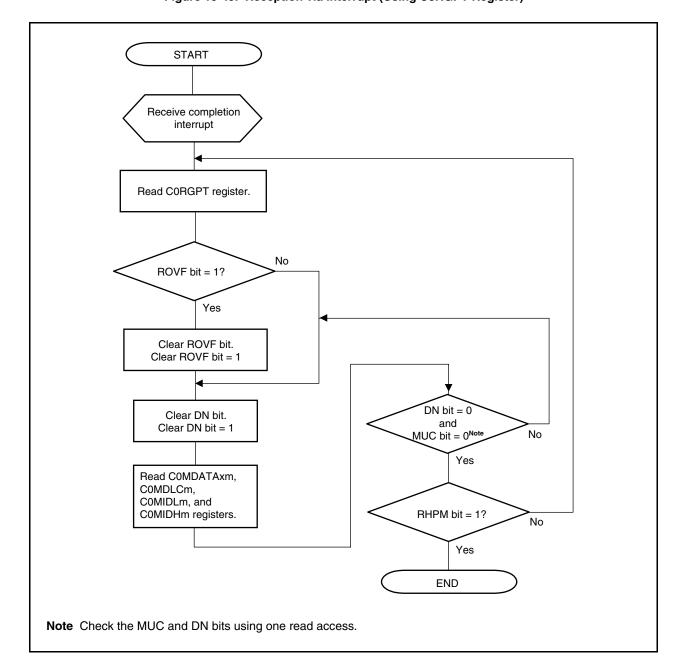

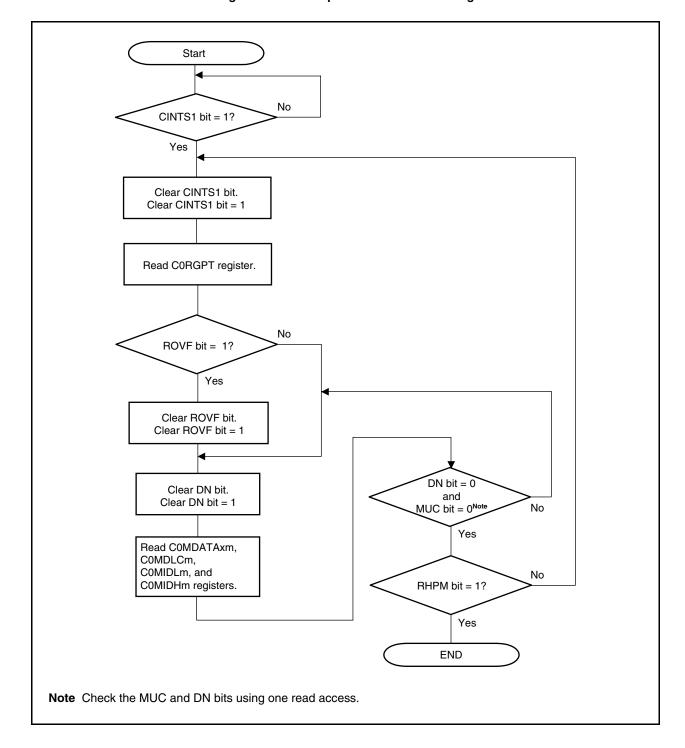

|    | 19.9  |                  | ge Reception                                                         |     |

|    |       | 19.9.1           | Message reception                                                    |     |

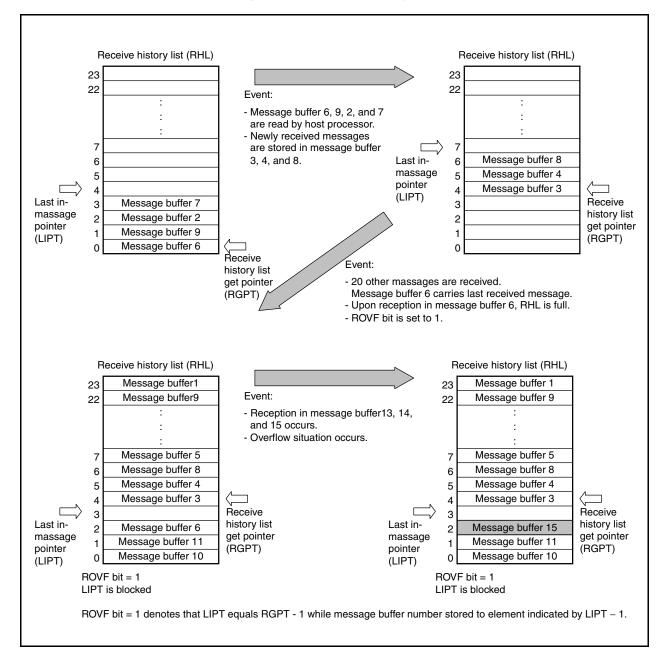

|    |       | 19.9.2           | Receive history list function                                        |     |

|    |       | 19.9.3<br>19.9.4 | Mask function                                                        |     |

|    |       | 13.3.4           | IVIUILI DUITEI TECEIVE DIOCK TULICIOTI                               | /09 |

|                                                                                                                                             | 19.9.5 Remote frame reception                                                                                                                                                                                                           |                   |

|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

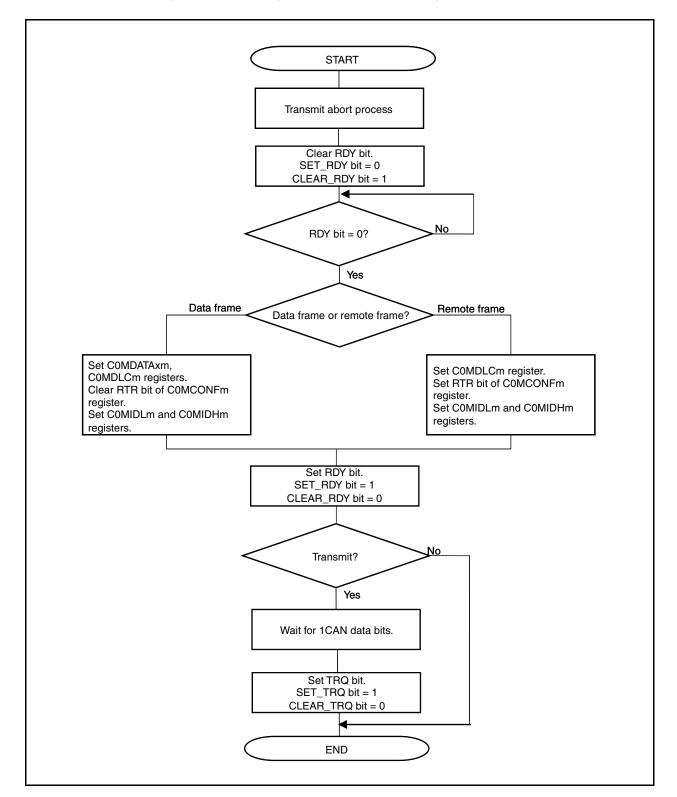

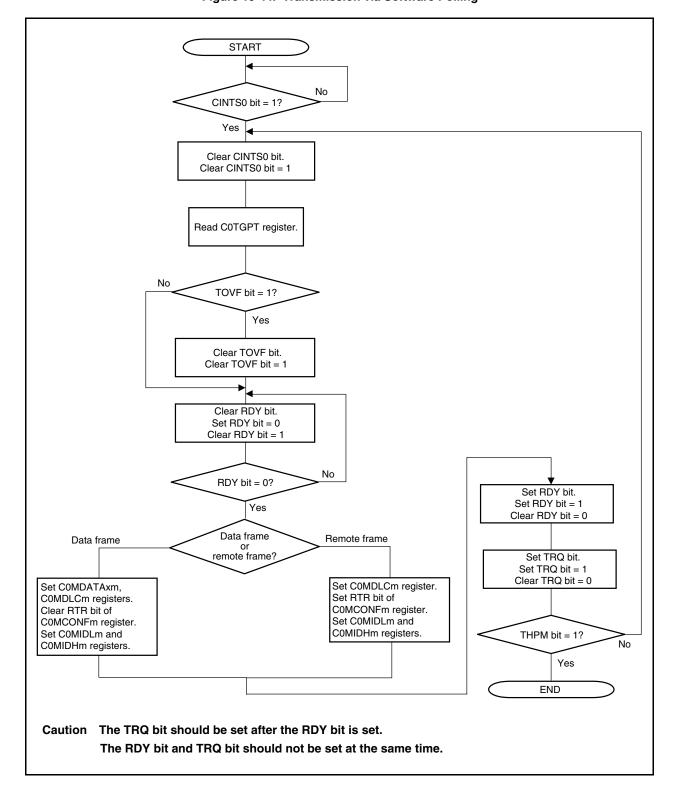

| 19.10                                                                                                                                       | Message Transmission                                                                                                                                                                                                                    | 791               |

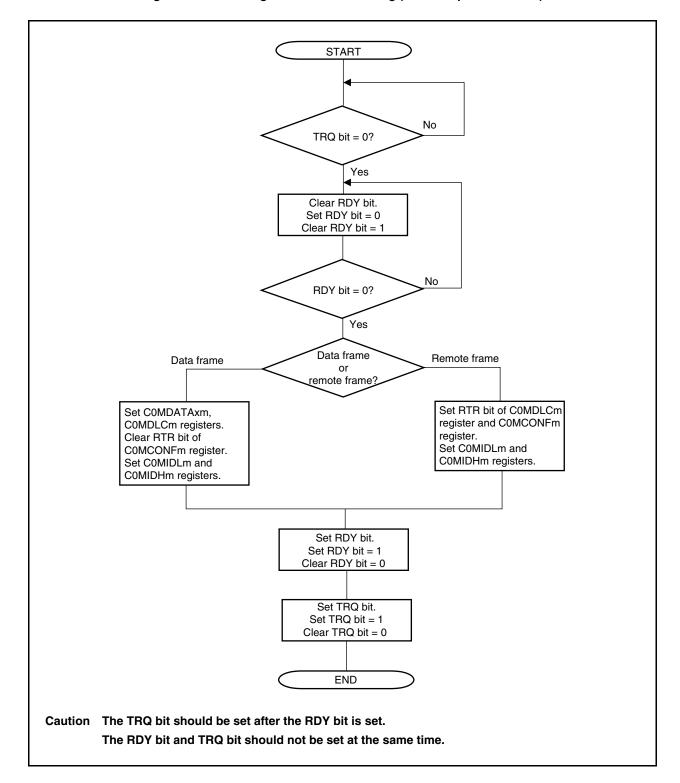

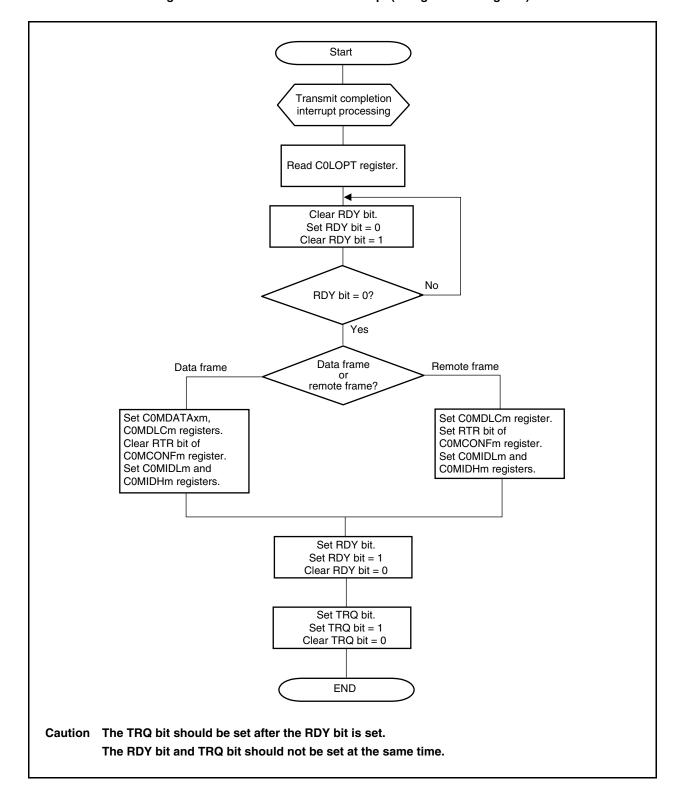

|                                                                                                                                             | 19.10.1 Message transmission                                                                                                                                                                                                            | 791               |

|                                                                                                                                             | 19.10.2 Transmit history list function                                                                                                                                                                                                  | 793               |

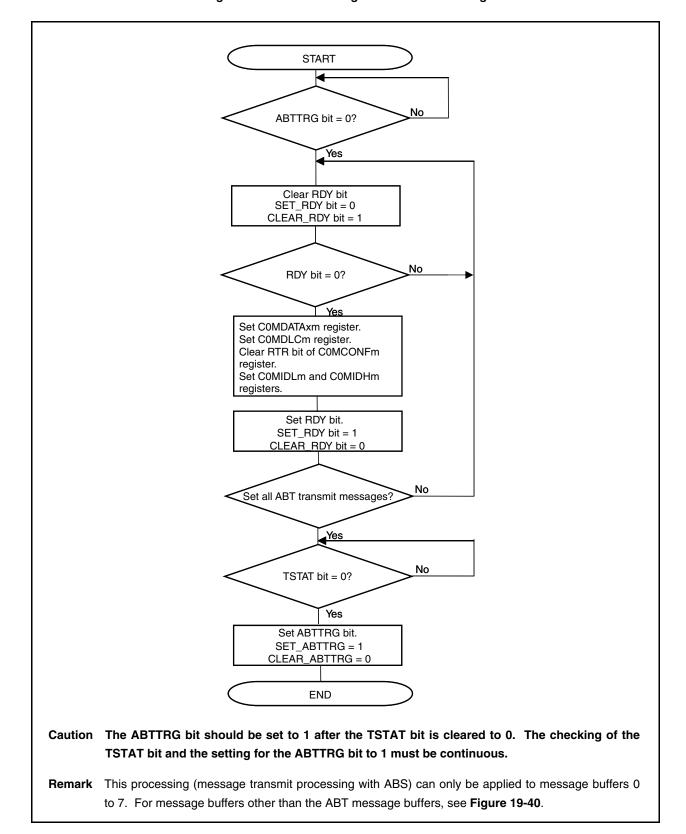

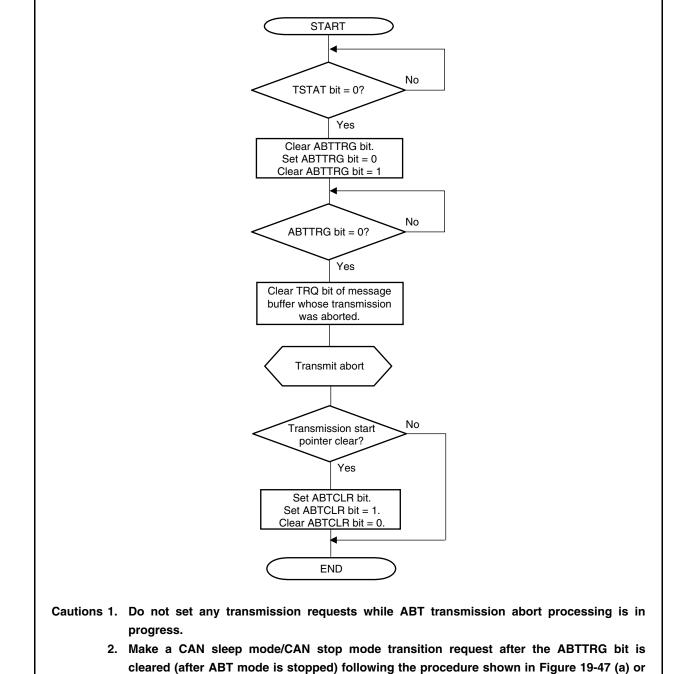

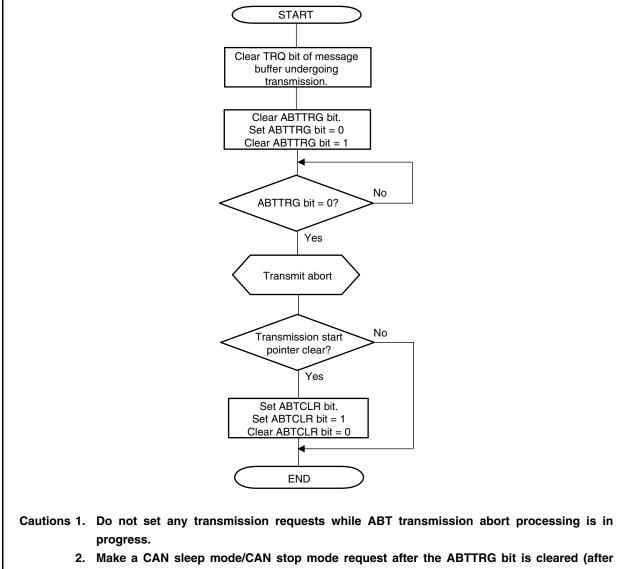

|                                                                                                                                             | 19.10.3 Automatic block transmission (ABT)                                                                                                                                                                                              | 795               |

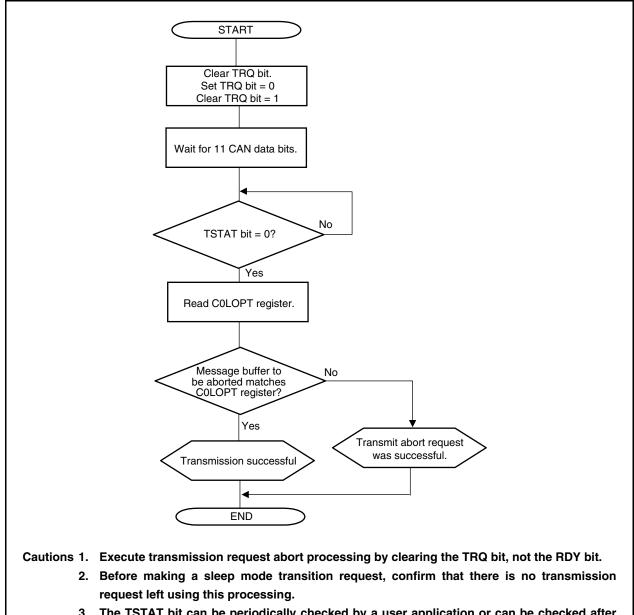

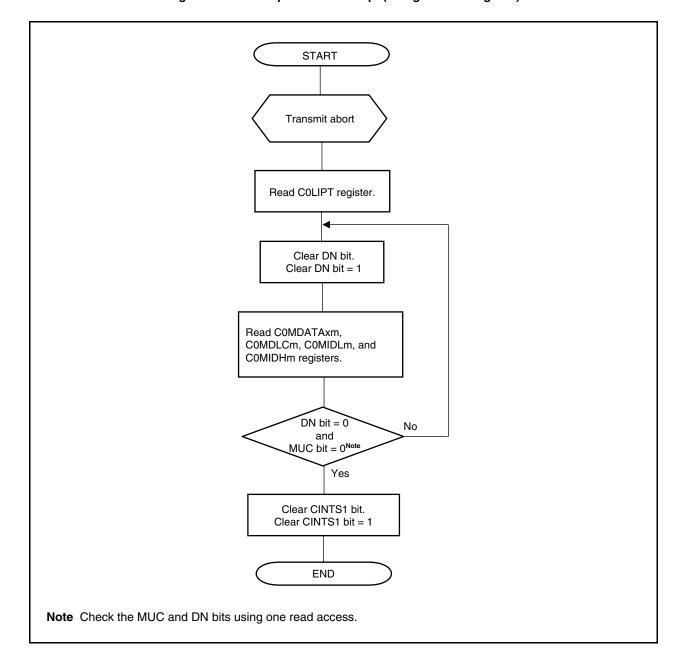

|                                                                                                                                             | 19.10.4 Transmission abort process                                                                                                                                                                                                      | 796               |

|                                                                                                                                             | 19.10.5 Remote frame transmission                                                                                                                                                                                                       | 797               |

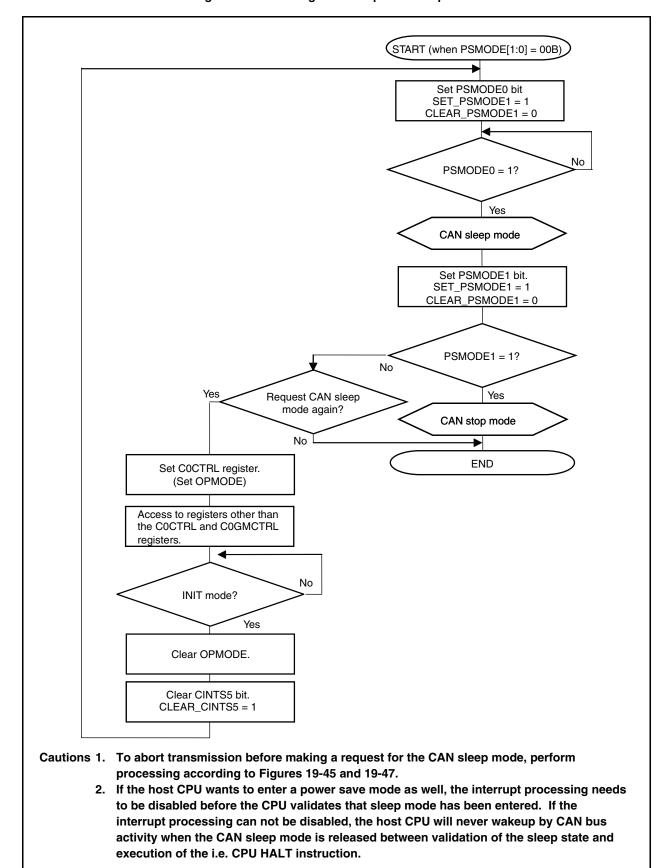

| 19.11                                                                                                                                       | Power Saving Modes                                                                                                                                                                                                                      | 798               |

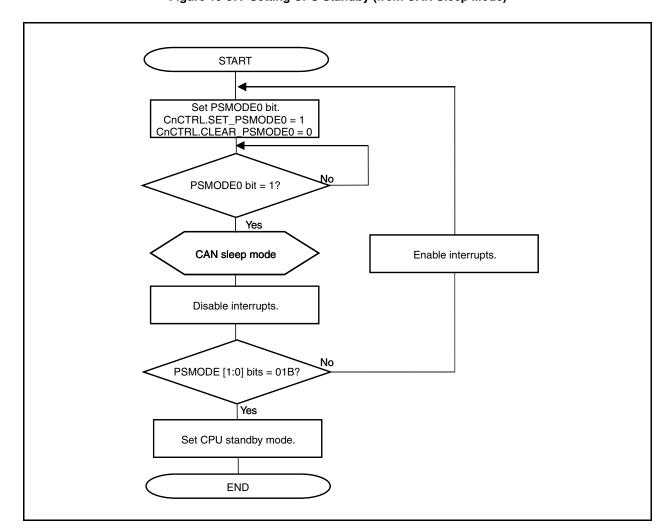

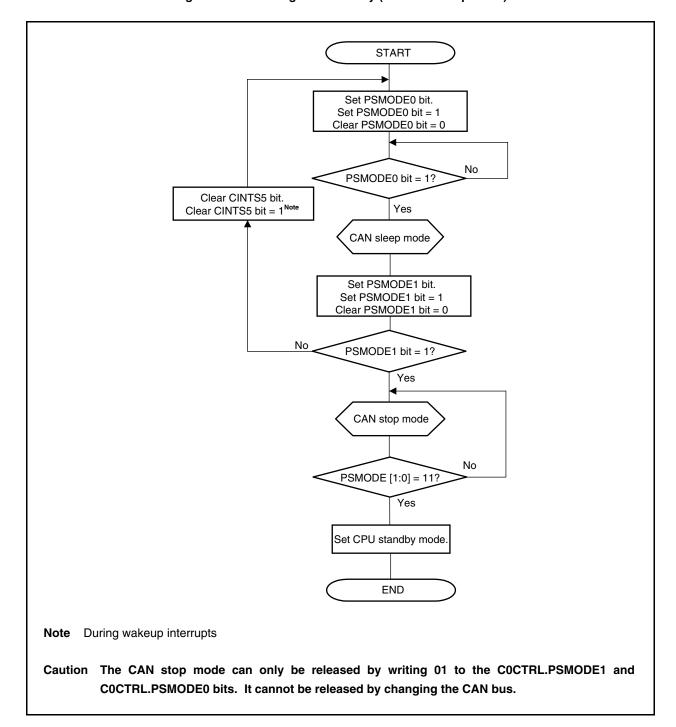

|                                                                                                                                             | 19.11.1 CAN sleep mode                                                                                                                                                                                                                  | 798               |

|                                                                                                                                             | 19.11.2 CAN stop mode                                                                                                                                                                                                                   | 800               |

|                                                                                                                                             | 19.11.3 Example of using power saving modes                                                                                                                                                                                             | 801               |

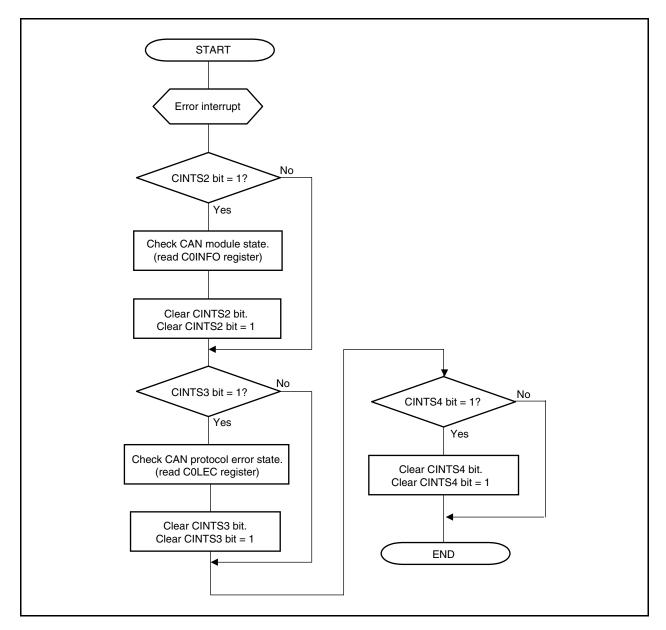

|                                                                                                                                             | Interrupt Function                                                                                                                                                                                                                      |                   |

| 19.13                                                                                                                                       | Diagnosis Functions and Special Operational Modes                                                                                                                                                                                       | 803               |

|                                                                                                                                             | 19.13.1 Receive-only mode                                                                                                                                                                                                               | 803               |

|                                                                                                                                             | 19.13.2 Single-shot mode                                                                                                                                                                                                                | 804               |

|                                                                                                                                             | 19.13.3 Self-test mode                                                                                                                                                                                                                  | 805               |

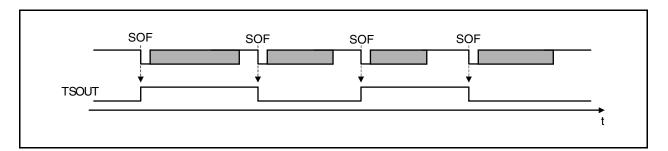

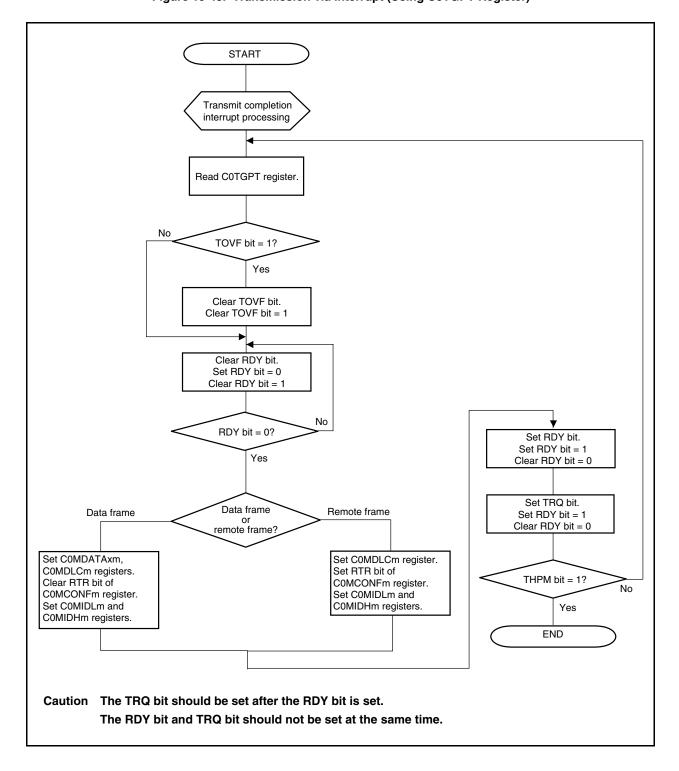

| 19.14                                                                                                                                       | Time Stamp Function                                                                                                                                                                                                                     | 806               |

|                                                                                                                                             | 19.14.1 Time stamp function                                                                                                                                                                                                             | 806               |

| 19.15                                                                                                                                       | Baud Rate Settings                                                                                                                                                                                                                      | 808               |

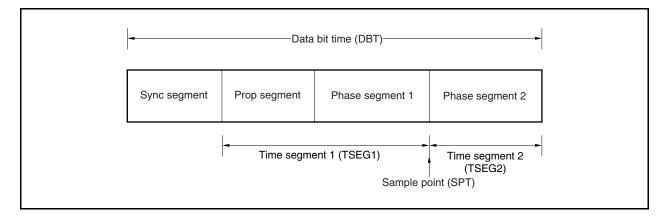

|                                                                                                                                             | 19.15.1 Baud rate setting conditions                                                                                                                                                                                                    | 808               |

|                                                                                                                                             | 19.15.2 Representative examples of baud rate settings                                                                                                                                                                                   | 812               |

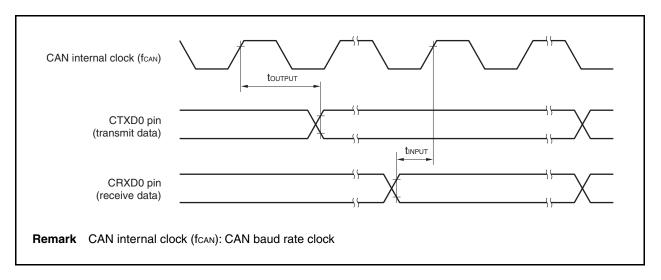

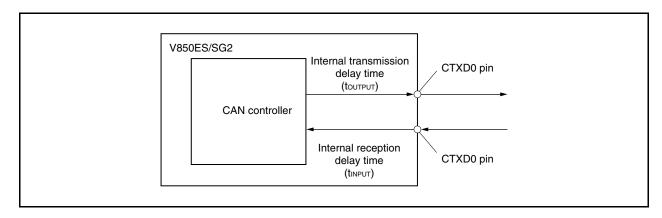

| 19.16                                                                                                                                       | Operation of CAN Controller                                                                                                                                                                                                             | 816               |

|                                                                                                                                             |                                                                                                                                                                                                                                         |                   |

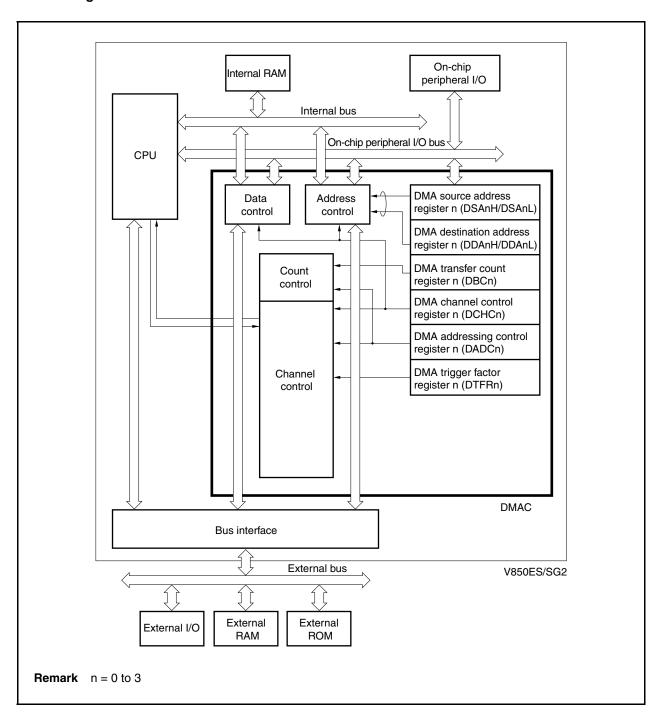

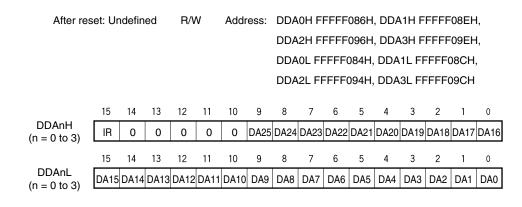

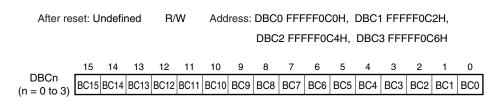

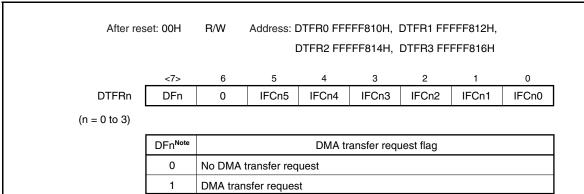

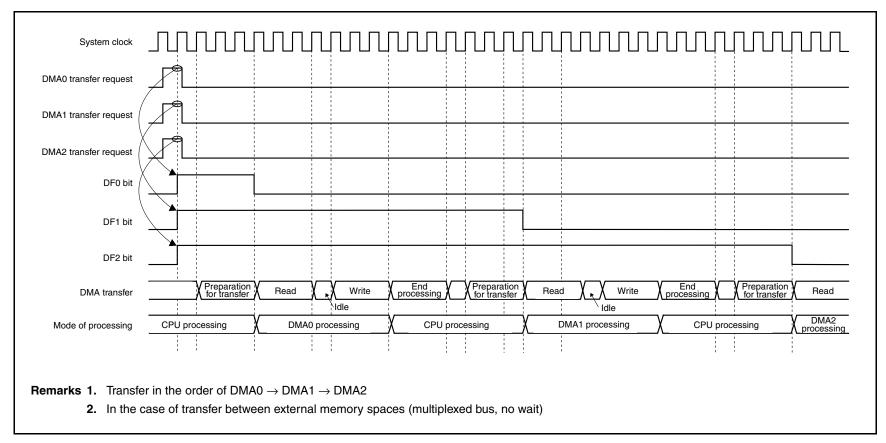

| CHAPTER                                                                                                                                     | R 20 DMA FUNCTION (DMA CONTROLLER)                                                                                                                                                                                                      | 841               |

| 20.1                                                                                                                                        | Features                                                                                                                                                                                                                                | 841               |

|                                                                                                                                             |                                                                                                                                                                                                                                         |                   |

| 20.2                                                                                                                                        | Configuration                                                                                                                                                                                                                           | 842               |

| 20.2<br>20.3                                                                                                                                | ConfigurationRegisters                                                                                                                                                                                                                  |                   |

| _                                                                                                                                           | _                                                                                                                                                                                                                                       | 843               |

| 20.3                                                                                                                                        | Registers                                                                                                                                                                                                                               | 843<br>850        |

| 20.3<br>20.4                                                                                                                                | Registers Transfer Targets                                                                                                                                                                                                              | 843<br>850<br>850 |

| 20.3<br>20.4<br>20.5                                                                                                                        | Registers  Transfer Targets  Transfer Modes                                                                                                                                                                                             | 843<br>850<br>850 |

| 20.3<br>20.4<br>20.5<br>20.6                                                                                                                | Registers  Transfer Targets  Transfer Modes  Transfer Types                                                                                                                                                                             |                   |

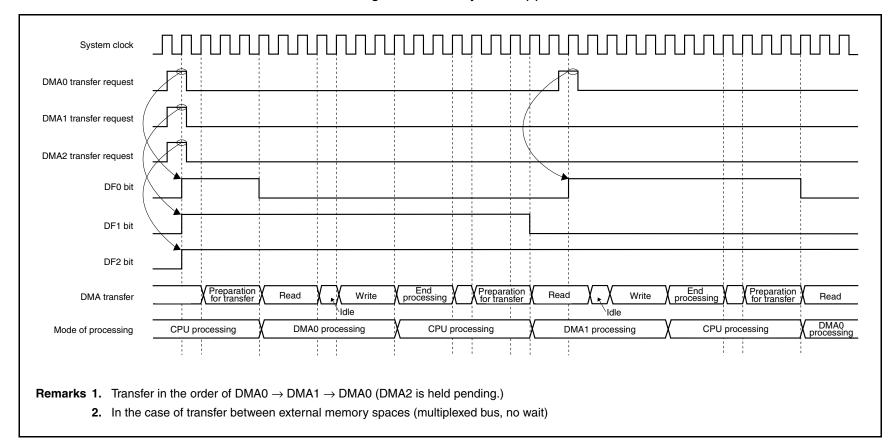

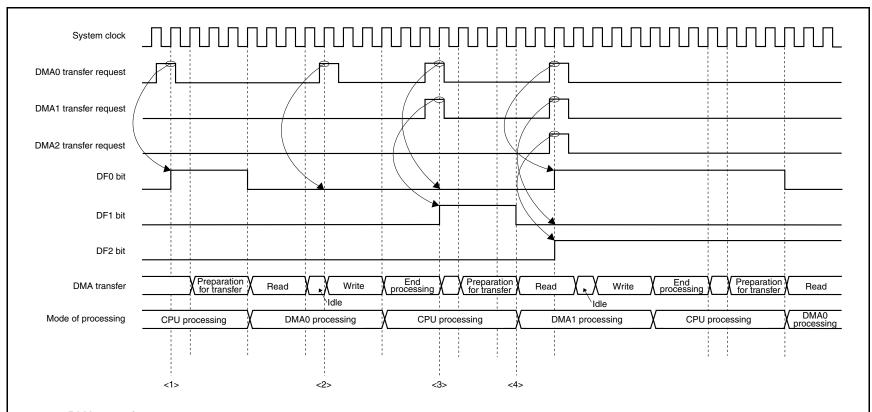

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7                                                                                                        | Registers  Transfer Targets  Transfer Modes  Transfer Types  DMA Channel Priorities                                                                                                                                                     |                   |

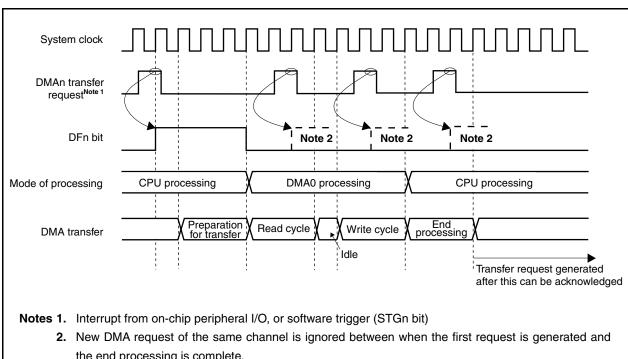

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9                                                                                        | Registers  Transfer Targets  Transfer Modes  Transfer Types  DMA Channel Priorities  Time Related to DMA Transfer                                                                                                                       |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10                                                                               | Registers  Transfer Targets  Transfer Modes  Transfer Types  DMA Channel Priorities  Time Related to DMA Transfer  DMA Transfer Start Factors                                                                                           |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11                                                                      | Registers  Transfer Targets  Transfer Modes  Transfer Types  DMA Channel Priorities  Time Related to DMA Transfer  DMA Transfer Start Factors  DMA Abort Factors                                                                        |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12                                                             | Registers  Transfer Targets  Transfer Modes  Transfer Types  DMA Channel Priorities  Time Related to DMA Transfer  DMA Transfer Start Factors  DMA Abort Factors  End of DMA Transfer                                                   |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12                                                             | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13                                                    | Registers                                                                                                                                                                                                                               |                   |

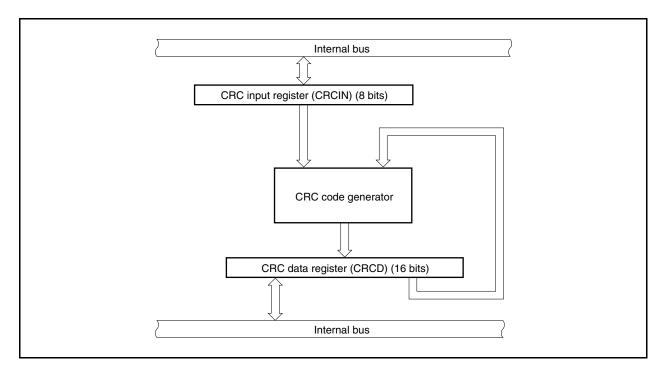

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER                                         | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2                         | Registers Transfer Targets Transfer Modes Transfer Types  DMA Channel Priorities Time Related to DMA Transfer  DMA Transfer Start Factors  DMA Abort Factors  End of DMA Transfer  Operation Timing  Cautions  Punctions  Configuration |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2<br>21.3                 | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2<br>21.3<br>21.4         | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2<br>21.3                 | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2<br>21.3<br>21.4<br>21.5 | Registers                                                                                                                                                                                                                               |                   |

| 20.3<br>20.4<br>20.5<br>20.6<br>20.7<br>20.8<br>20.9<br>20.10<br>20.11<br>20.12<br>20.13<br>CHAPTER<br>21.1<br>21.2<br>21.3<br>21.4<br>21.5 | Registers                                                                                                                                                                                                                               |                   |

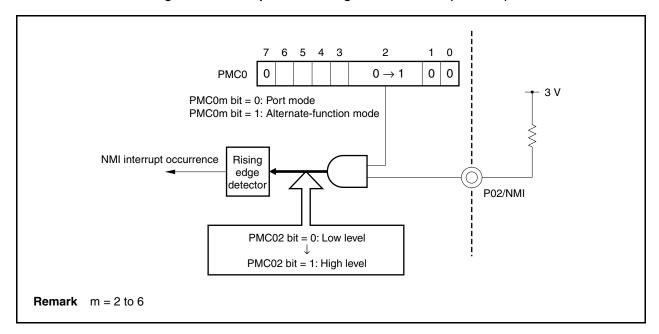

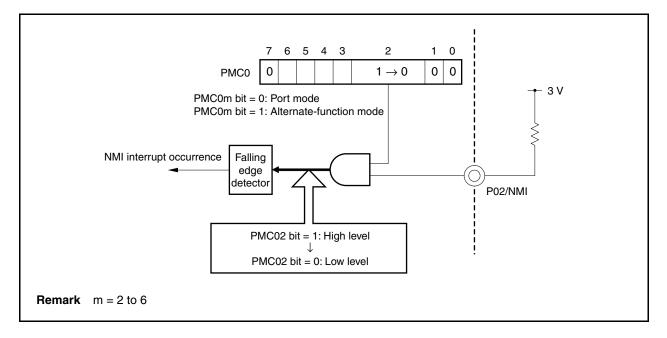

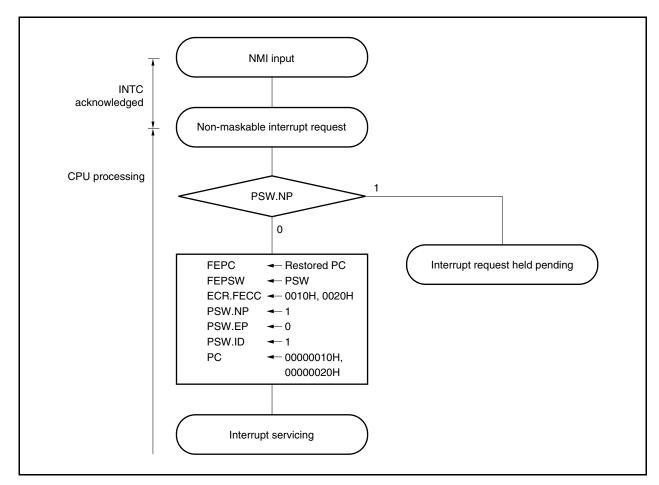

| 22.2    | Non-Maskable Interrupts                                        | 873 |

|---------|----------------------------------------------------------------|-----|

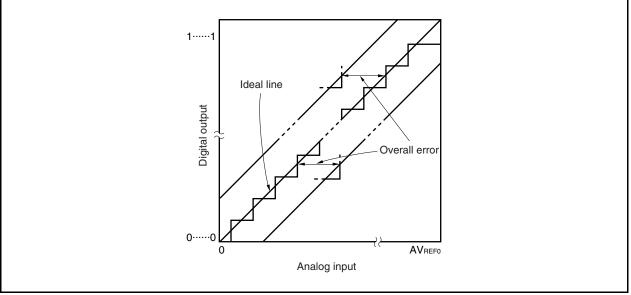

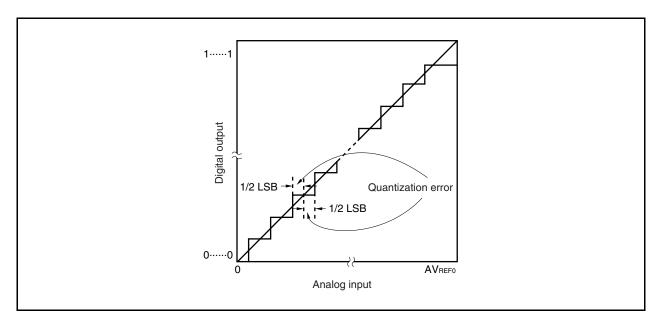

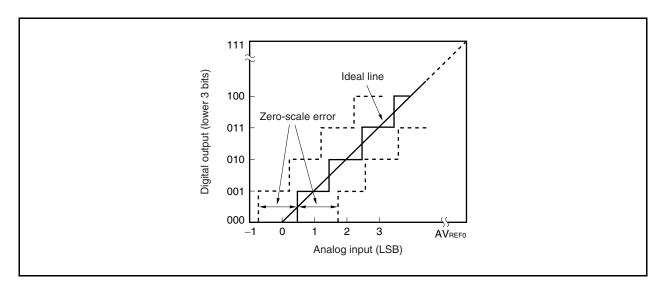

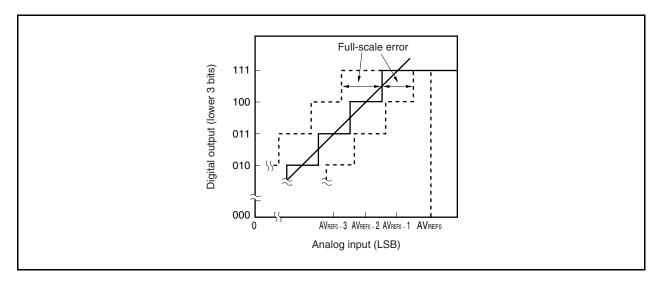

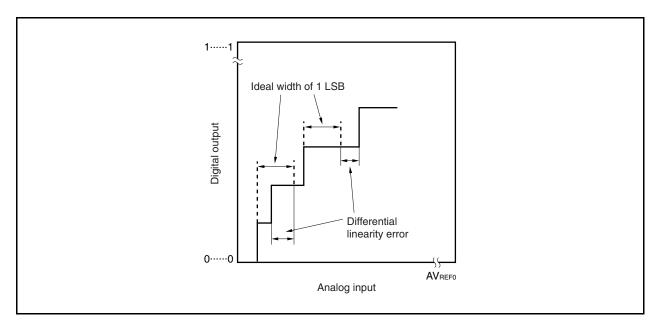

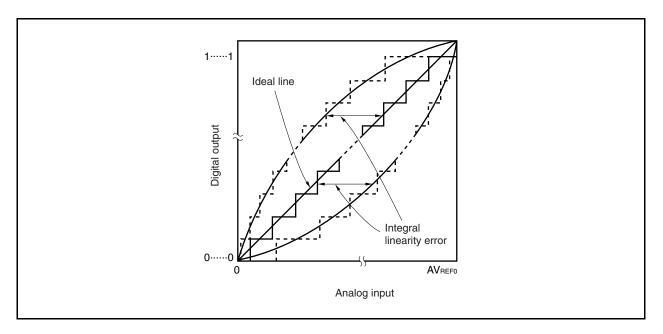

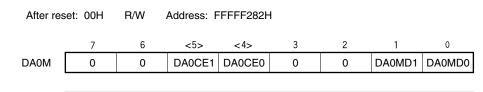

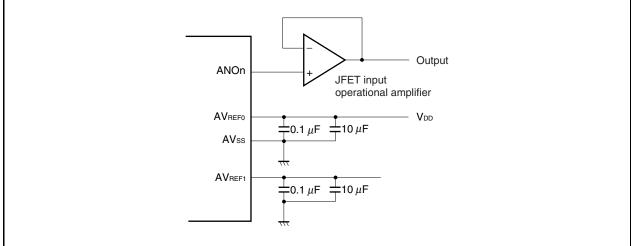

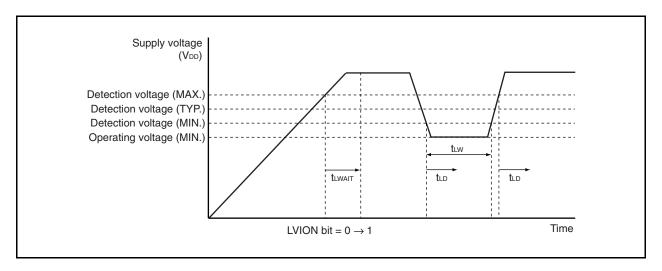

|         | 22.2.1 Operation                                               | 875 |