HYB18RL25632AC HYB18RL25616AC

# Graphics & Speciality DRAMs

256 Mbit DDR Reduced Latency DRAM

Version 1.42

Nov. 2002

Edition Jun. 2002

This edition was realized using the software system FrameMaker®.

Published by Infineon Technologies, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Infineon Technologies 6/30/2002.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of Infineon Technologies, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of Infineon Technologies.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| HYB18RL25<br>Revision His |              | t Version 1.42                                                                                                                  |

|---------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

|                           | 1            | Subjects (major changes since last revision)                                                                                    |

| Previous Ve               | rsion: 1.34  |                                                                                                                                 |

|                           |              | New formating of the specification document                                                                                     |

|                           | 16           | Elimination of 4mA Driver Strength in MRS                                                                                       |

|                           | 17           | Elimination of Configurations 5 and 6 in Configuration Table.                                                                   |

|                           | 23           | tCKDQS (max) changed to 3.7ns for all speed sorts tCKDQS (min) changed from 2.3ns to 2.7ns for all speed sorts                  |

|                           | 25, 26       | Introduction of "Read followed by Write, Write data on bus prior to Read data" timings.                                         |

|                           | 35           | Reference Voltage range changed to 0.49 * VDDQ to 0.51 * VDDQ AC Operation : HSTL strong : VIH and VIL changed to Vref +/- 0.3V |

| Previous Ve               | ersion: 1.4  |                                                                                                                                 |

|                           | 15           | Power up sequence modified: Addresses may be applied with specified setup and hold timings during MRS commands.                 |

| Previous Ve               | ersion: 1.41 |                                                                                                                                 |

| 22,23                     | 22,23        | t <sub>DQSQ</sub> changed back to t <sub>QSQ</sub> (typo)                                                                       |

| 22                        | 22           | Data Window = min(t <sub>DQSH</sub> , t <sub>DQSL</sub> ) - 2 * t <sub>QSQ</sub> max                                            |

| 23                        | 23           | Note 4 : tQSQ and tQSQHZ are absolute values                                                                                    |

| 1 | Overv   | 1ew                                    |      |

|---|---------|----------------------------------------|------|

|   | 1.1     | Features                               | 5    |

|   | 1.2     | General Description                    |      |

|   | 1.3     | Ball Configuration Package and Ballout |      |

|   | 1.3.1   | Ball Description                       |      |

|   | 1.4     | Functional Block Diagram               |      |

|   | 1.5     | Commands                               | .12  |

|   | 1.5.1   | Command Table                          | .12  |

|   | 1.5.2   | Description of Commands                | .13  |

| 2 | Funct   | ional Description                      | 15   |

| _ | 2.1     | Clocks, Commands and Addresses         | 15   |

|   | 2.2     | Initialization                         |      |

|   | 2.3     | Mode Register Set Command (MRS)        |      |

|   | 2.4     | Configuration Table                    |      |

|   | 2.5     | Writes (WR)                            |      |

|   | 2.5.1   | Write - Basic Information              |      |

|   | 2.5.1   | Write - Cyclic Bank Access             |      |

|   |         | Burst Length (BL) = 2                  |      |

|   |         |                                        |      |

|   | 2.5.2.2 | Burst Length (BL) = 4                  |      |

|   |         |                                        |      |

|   |         | Burst Length (BL) = 2                  |      |

|   |         | Burst Length (BL) = 4                  |      |

|   | 2.5.4   | Write followed by Read                 |      |

|   |         | Burst Length (BL) = 2                  |      |

|   |         | Burst Length (BL) = 4                  |      |

|   | 2.6     | Reads (RD)                             |      |

|   | 2.6.1   | Read - Basic Information               |      |

|   | 2.6.2   | Read - Cyclic Bank Access              |      |

|   |         | Burst Length (BL) = 2                  |      |

|   |         | Burst Length (BL) = 4                  |      |

|   | 2.6.3   | Read followed by Write                 | . 26 |

| 3 | IEEE '  | 1149.1 Serial Boundary Scan (JTAG)     | 29   |

|   | 3.1     | Test Access Port (TAP)                 |      |

|   | 3.1.1   | Test Clock (TCK)                       |      |

|   | 3.1.2   | Test Mode Select (TMS)                 | .29  |

|   | 3.1.3   | Test Data-In (TDI)                     |      |

|   | 3.1.4   | Test Data-Out (TDO)                    | .29  |

|   | 3.2     | TAP Registers                          | .29  |

|   | 3.2.1   | Instruction Register                   | .29  |

|   | 3.2.2   | Bypass Register                        | .29  |

|   | 3.2.3   | Boundary Scan Register                 | .30  |

|   | 3.2.4   | Identification (ID) Register           | .30  |

|   | 3.3     | TAP Instructions                       | .30  |

|   | 3.4     | Boundary Scan Exit Order               | .31  |

|   | 3.4.1   | x16 Configuration                      | .31  |

|   | 3.4.2   | x32 Configuration                      |      |

|   | 3.5     | TAP Operation                          |      |

|   | 3.6     | JTAG TAP Block Diagram                 |      |

|   | 3.7     | JTAG TAP Controller State Diagram      |      |

|   | 3.8     | JTAG DC Operating Conditions           |      |

|   | 3.9     | JTAG AC Operating Conditions           |      |

|   | 3.10    | JTAG AC Electrical Characteristics     |      |

|   | 3.11    | JTAG Timing Diagram                    |      |

|   |         |                                        |      |

| 4 | Flec | trical Characteristics                   | 31 |

|---|------|------------------------------------------|----|

|   | 4.1  | Absolute Maximum Ratings                 | 37 |

|   | 4.2  | Recommended Power & DC Operation Ratings | 37 |

|   | 4.3  | AC Operation Ratings                     |    |

|   | 4.4  | Output Test Conditions                   | 38 |

|   | 4.5  | Pin Capacitances                         |    |

|   | 4.6  | Operating Currents                       |    |

#### 1 Overview

#### 1.1 Features

- 256 Megabit (256M)

- 0.17µm process technology

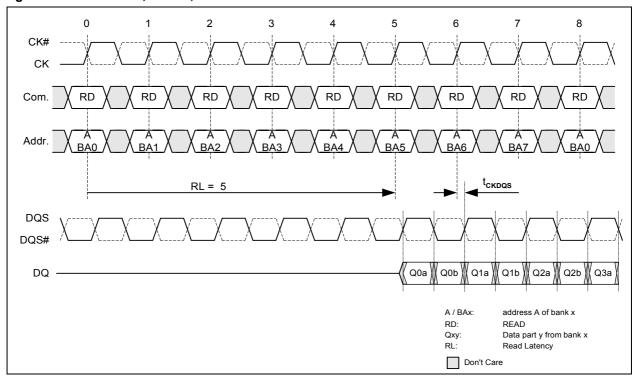

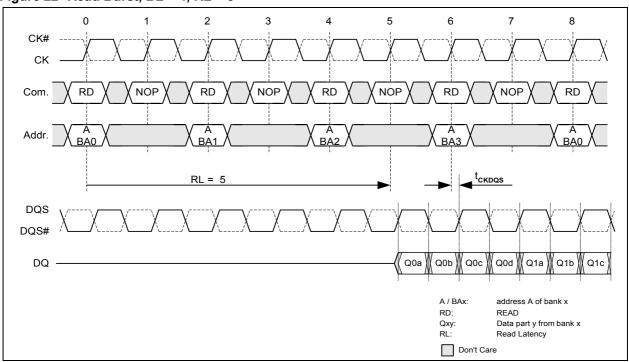

- Cyclic bank addressing for maximum data out bandwidth

- Organization 8M x 32, 16M x 16 in 8 banks

- Non-multiplexed addresses

- Non-interruptible sequential bursts of 2 (2-bit prefetch) and 4 (4-bit prefetch), DDR

- Up to 600Mb/sec/pin data rate

- Programmable Read Latency (RL) of 5..6

- Data valid signal (DVLD) activated as Read Data is available

- Data Mask signals (DM0 / DM1) to mask first and second part of write data burst

- IEEE 1149.1 compliant JTAG Boundary Scan

- Pseudo-HSTL 1.8V IO Supply

- · Internal autoprecharge

- Refresh requirements: 32ms at 100°C junction temperature (8k refresh for each bank, 64k refresh commands must be issued in total each 32ms)

- Package T-FBGA 144

- 2.5V V<sub>EXT</sub>, 1.8V V<sub>DD</sub>, 1.8V V<sub>DDQ</sub>

Table 1 Key timing parameters (Configuration Example x32, x16 device)

| Speed Sort      | -3.3 | -4.0 | -5.0 | Units  |

|-----------------|------|------|------|--------|

| Frequency       | 300  | 250  | 200  | MHz    |

| tno             | 26.7 | 28.0 | 25.0 | ns     |

| t <sub>RC</sub> | 8    | 7    | 5    | cycles |

| Read latency    | 6    | 5    | 5    | cyles  |

# 1.2 General Description

The Infineon 256M Reduced Latency DRAM (RLDRAM) contains 8 banks x 32 Mb of memory accessible with 32bit or 16bit I/O's in a double data rate (DDR) format where the data is provided and synchronized with a differential echo clock signal. RLDRAM does not require row/column address multiplexing and is optimized for fast random access and high data bandwidth.

RLDRAM is designed for communication data storages like transmit or receive buffers in telecommunication systems as well as data or instruction cache applications requiring large amounts of memory.

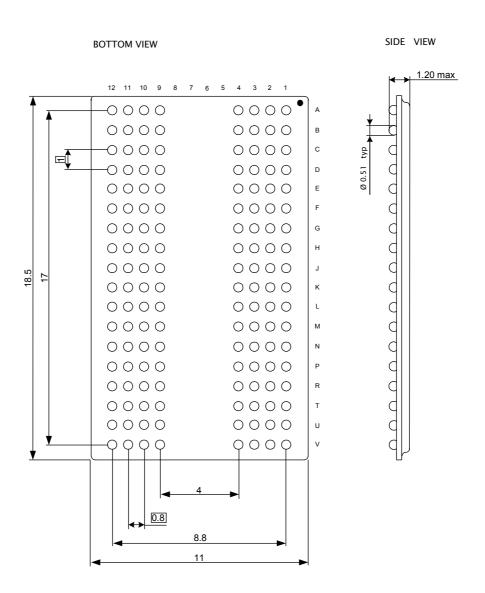

# 1.3 Ball Configuration Package and Ballout

Figure 1 T-FBGA 144 package 256 Mbit DDR Reduced Latency DRAM

Note: All dimensions in mm

Figure 2 Ballout of 256 Mbit Reduced Latency DRAM (x32 configuration)

|   | 1   | 2    | 3     | 4    | 5 | 6 | 7 | 8 | 9    | 10    | 11   | 12   |

|---|-----|------|-------|------|---|---|---|---|------|-------|------|------|

| Α | VSS | VEXT | VREF  | VSS  |   |   |   |   | VSS  | VEXT  | TMS  | тск  |

| В | VSS | DQ8  | DQ9   | VSSQ |   |   |   |   | VSSQ | DQ1   | DQ0  | VSS  |

| С | VSS | DQ10 | DQ11  | VDDQ |   |   |   |   | VDDQ | DQ3   | DQ2  | vss  |

| D | VSS | DQS1 | DQS1# | VSSQ |   |   |   |   | VSSQ | DQS0# | DQS0 | vss  |

| Ε | VSS | DQ12 | DQ13  | VDDQ |   |   |   |   | VDDQ | DQ5   | DQ4  | vss  |

| F | DM0 | DQ14 | DQ15  | VSSQ |   |   |   |   | VSSQ | DQ7   | DQ6  | DVLD |

| G | A5  | A6   | A7    | VDD  |   |   |   |   | VDD  | A2    | A1   | A0   |

| Н | A8  | A9   | vss   | VSS  |   |   |   |   | vss  | VSS   | A4   | АЗ   |

| J | AS# | BA2  | VDD   | VDD  |   |   |   |   | VDD  | VDD   | BA0  | СК   |

| K | WE# | REF# | VDD   | VDD  |   |   |   |   | VDD  | VDD   | BA1  | СК#  |

| L | A18 | CS#  | vss   | VSS  |   |   |   |   | VSS  | VSS   | A14  | A13  |

| M | A15 | A16  | A17   | VDD  |   |   |   |   | VDD  | A12   | A11  | A10  |

| N | DM1 | DQ22 | DQ23  | VSSQ |   |   |   |   | VSSQ | DQ31  | DQ30 | NC   |

| Р | VSS | DQ20 | DQ21  | VDDQ |   |   |   |   | VDDQ | DQ29  | DQ28 | VSS  |

| R | VSS | DQS2 | DQS2# | VSSQ |   |   |   |   | VSSQ | DQS3# | DQS3 | vss  |

| Т | VSS | DQ18 | DQ19  | VDDQ |   |   |   |   | VDDQ | DQ27  | DQ26 | vss  |

| U | vss | DQ16 | DQ17  | VSSQ |   |   |   |   | VSSQ | DQ25  | DQ24 | vss  |

| ٧ | VSS | VEXT | VREF  | VSS  |   |   |   |   | VSS  | VEXT  | TDO  | TDI  |

Figure 3 Ballout of 256Mbit Reduced Latency DRAM (x16 configuration)

| · | 1   | 2    | 3    | 4    | 5 | 6 | 7 | 8 | 9    | 10    | 11   | 12   |

|---|-----|------|------|------|---|---|---|---|------|-------|------|------|

| Α | VSS | VEXT | VREF | VSS  |   |   |   |   | VSS  | VEXT  | TMS  | тск  |

| В | VSS | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQ1   | DQ0  | VSS  |

| С | VSS | NC   | NC   | VDDQ |   |   |   |   | VDDQ | DQ3   | DQ2  | vss  |

| D | VSS | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQS0# | DQS0 | vss  |

| Ε | VSS | NC   | NC   | VDDQ |   |   |   |   | VDDQ | DQ5   | DQ4  | VSS  |

| F | DM0 | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQ7   | DQ6  | DVLD |

| G | A5  | A6   | A7   | VDD  |   |   |   |   | VDD  | A2    | A1   | A0   |

| Н | A8  | A9   | VSS  | VSS  |   |   |   |   | vss  | VSS   | A4   | A3   |

| J | AS# | BA2  | VDD  | VDD  |   |   |   |   | VDD  | VDD   | BA0  | СК   |

| K | WE# | REF# | VDD  | VDD  |   |   |   |   | VDD  | VDD   | BA1  | CK#  |

| L | A19 | CS#  | VSS  | VSS  |   |   |   |   | vss  | VSS   | A14  | A13  |

| М | A15 | A16  | A17  | VDD  |   |   |   |   | VDD  | A12   | A11  | A10  |

| N | DM1 | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQ15  | DQ14 | A18  |

| Р | VSS | NC   | NC   | VDDQ |   |   |   |   | VDDQ | DQ13  | DQ12 | VSS  |

| R | VSS | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQS1# | DQS1 | VSS  |

| Т | VSS | NC   | NC   | VDDQ |   |   |   |   | VDDQ | DQ11  | DQ10 | VSS  |

| U | VSS | NC   | NC   | VSSQ |   |   |   |   | VSSQ | DQ9   | DQ8  | vss  |

| ٧ | VSS | VEXT | VREF | VSS  |   |   |   |   | VSS  | VEXT  | TDO  | TDI  |

Note: NC: No Connect: These signals are internally connected and have parasitic characterisitcs of an IO. They may optionally be connected to ground for improved heat dissipation.

# 1.3.1 Ball Description

# Table 2 Ball description

| Ball              | Туре             | Detailed Function                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK#           | Input            | Input Clock: CK and CK# are differential clock inputs. Addresses and commands are latched on the rising edge of CK, input data is latched on the both edges of CK. CK# is ideally 180 degrees out of phase with CK.                                                                                                                                                      |

| CS#               | Input            | Chip Select: CS# enables the command decoder when low and disables it when high. When the command decoder is disabled new commands are ignored, but internal operations continue.                                                                                                                                                                                        |

| AS#, WE#,<br>REF# | Input            | Command Inputs: Sampled at the positive edge of CK. AS#, WE# and REF# define (together with CS#) the command to be executed.                                                                                                                                                                                                                                             |

| A[19:0]           | Input            | Address Inputs: A[19:0] define the row and column addresses for READ and WRITE operations. During an MODE REGISTER SET the address inputs A[17:0] define the register settings. The addresses are sampled at the rising edge of CK. In the x32 configuration, A[19] is not used. In the x16 configuration with BL2, A[19] is used.                                       |

| BA[0:2]           | Input            | Bank select: Select to which internal bank a command is being applied.                                                                                                                                                                                                                                                                                                   |

| DQ[31:0]          | Input/<br>Output | Data Input / Output: The DQ signals form the 32 bit data bus. During READ commands the data is referenced to both edges of DQS/DQS#. During WRITE commands the data is sampled at both edges of CK.                                                                                                                                                                      |

| DQSx,<br>DQSx#    | Output           | Data read strobes: DQSx and DQSx# are the differential data read strobes. During READs, they are transmitted by the RLDRAM and edge-aligned with data. DQSx is ideally 180 degrees out of phase with DQSx#. DQS0, DQS0# are aligned with DQ0-DQ7. DQS1, DQS1# are aligned with DQ8-DQ15. DQS2, DQS2# are aligned with DQ16-DQ23. DQS3, DQS3# are aligned with DQ24-DQ31. |

| DVLD              | Output           | Data Valid: The DVLD indicates valid output data. DVLD is edge-aligned with DQSx, DQSx#.                                                                                                                                                                                                                                                                                 |

| DM0, DM1          | Input            | Data Mask: DM0 and DM1 are the input masks for WRITE data. The first half of the Input data burst is masked when DM0 is sampled HIGH along with the WRITE command. The second half of the input data burst is masked when DM1 is sampled HIGH along with the WRITE command.                                                                                              |

| TCK               | Input            | IEEE 1149.1 Clock Input: JEDEC standard 1.8V IO levels. These pin must be tied to $V_{SS}$ if the JTAG function is not used in the circuit.                                                                                                                                                                                                                              |

| TMS, TDI          | Input            | IEEE 1149.1 Test Inputs: JEDEC standard 1.8V IO levels. These pins may be left not connected if the JTAG function is not used in the circuit.                                                                                                                                                                                                                            |

| TDO               | Output           | IEEE 1149.1 Test Output: JEDEC standard 1.8V IO level tracking VDDQ.                                                                                                                                                                                                                                                                                                     |

| V <sub>REF</sub>  | Supply           | Input Reference Voltage: Nominally VDDQ/2. Provides a reference voltage for the input buffers.                                                                                                                                                                                                                                                                           |

| VEXT              | Supply           | Power Supply: 2.5V nominal. See DC Electrical Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                        |

| V <sub>DD</sub>   | Supply           | Power Supply: 1.8V nominal. See DC Electrical Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                                                        |

| V <sub>DDQ</sub>  | Supply           | Power Supply: Isolated Output Buffer Supply. 1.8V nominal. See DC Electrical Characteristics and Operating Conditions for range.                                                                                                                                                                                                                                         |

| V <sub>SS</sub>   | Supply           | Power Supply: GND                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SSQ</sub>  | Supply           | Power Supply: Isolated Output Buffer Supply. GND                                                                                                                                                                                                                                                                                                                         |

| NC                | -                | No Connect: These pins may be connected to ground to improve heat dissipation.                                                                                                                                                                                                                                                                                           |

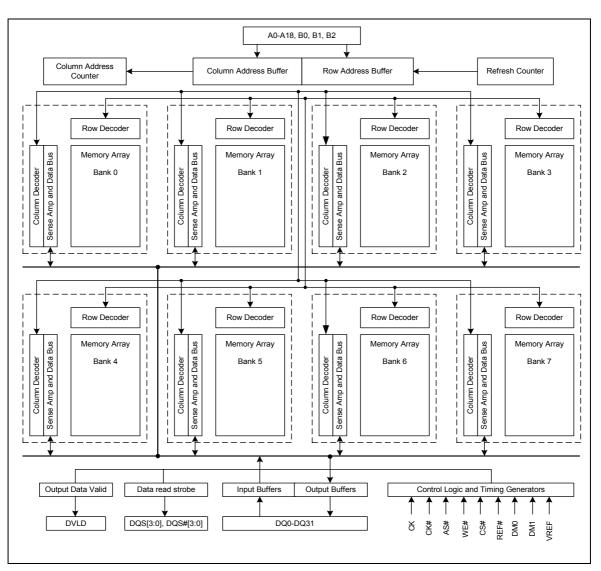

# 1.4 Functional Block Diagram

Figure 4 Functional Block Diagram 8M x 32 Configuration

Note: When the BL4 setting is used, A18 is a "Don't Care"

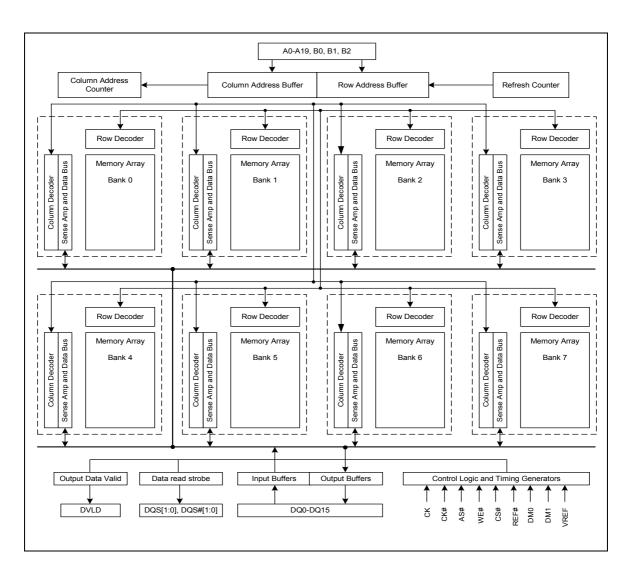

Figure 5 Functional Block Diagram 16M x 16 Configuration

Note: 1 When the BL4 setting is used, A19 is a "Don't Care".

Note: 2 In the 16Mx16 configuration, only DQS[1:0] & DQS#[1:0] are used

#### 1.5 Commands

#### 1.5.1 Command Table

According to the functional signal description the following command sequences are possible. All input states or sequences not shown are illegal or reserved. All command and address inputs must meet setup and hold times around the rising edge of CK.

Table 3 Truth table

| Operation                       | Device<br>State | Code  | CS# | AS# | WE# | REF# | A[19:0] <sup>1)3)</sup> | BA]2:0] | DM]1:0] |

|---------------------------------|-----------------|-------|-----|-----|-----|------|-------------------------|---------|---------|

| No Operation                    | Any             | NOP   | L   | Н   | Н   | Н    | X                       | Х       | Χ       |

| Deselect <sup>4)</sup>          | Any             |       | Н   | Χ   | Х   | Х    | Χ                       | Х       | Х       |

| Mode Register Set <sup>2)</sup> | Idle            | MRS   | L   | L   | L   | L    | Valid                   | Х       | Х       |

| Read                            | Any             | READ  | L   | L   | Н   | Н    | Valid                   | Valid   | Х       |

| Write                           | Any             | WRITE | L   | L   | L   | Н    | Valid                   | Valid   | Valid   |

| Auto Refresh                    | Idle            |       | L   | Н   | Н   | L    | Х                       | Valid   | Х       |

Note: 1: X = "Don't Care"; H = Logic HIGH; L = Logic LOW Note: 2: Only A[17:0] are used for the MRS command.

Note: 3: See Table 4

Table 4 Address Width table

|              | Data Width | 32      | 16      |

|--------------|------------|---------|---------|

| Burst Length |            |         |         |

| BL 2         |            | A[18:0] | A[19:0] |

| BL 4         |            | A[17:0] | A[18:0] |

Note: 1: The x32 and x16 configurations have different ballouts (see Fig. 2 & Fig. 3)

# 1.5.2 Description of Commands

# Table 5 Description of Commands

| Command        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESEL /<br>NOP | The NOP command is used to perform a no operation to the RLDRAM; this is equal to deselecting the chip. Use NOP command to prevent unwanted commands from being registered during idle or wait states. Operations already in progress are not affected. Output values depend on command history.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MRS            | The Mode Register is set via the address inputs A[17:0]. See the mode register description in the register description section. The MRS command can only be issued when all banks are idle and no bursts are in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

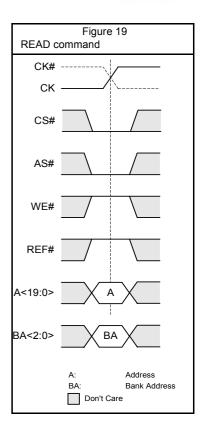

| READ           | The READ command is used to initiate a burst read access to a bank. The value on the BA[2:0] inputs selects the bank, and the address provided on inputs A[19:0] selects the data location within the bank.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WRITE          | The WR command is used to initiate a burst write access to a bank. The value on the BA[2:0] inputs selects the bank, and the address provided on inputs A[19:0] selects the data location within the bank. Input data appearing on the DQs is written to the memory array subject to the DMx input logic levels appearing coincident with the WRITE command. If DM0 is registered LOW, the first half of the burst Write data will be written to the memory array, if registerd HIGH this data will be ignored i.e, this part of the data word will not be written. If DM1 is registered LOW the second half of the burst Write data will be written to the memory array, if registerd HIGH this data will be ignored i.e, this part of the data word will not be written. |

| AREF           | The AREF is used during normal operation of the RLDRAM to refresh the memory content of a bank. The value on the BA[2:0] inputs selects the bank. The refresh address is generated by the internal refresh controller. This makes the address bits "Don't Care" during an AREF command. The RLDRAM requires 64k AREF cycles at an average periodic interval of 0.49 $\mu s^{1)}$ (maximum). To improve efficiency a burst of eight AREF commands (One AREF for each bank) can be posted to the RLDRAM at an average periodic interval of 3.9 $\mu s^{2}$ ).                                                                                                                                                                                                                |

Note: 1: Actual refresh is  $32ms/8K/8 = 0.488\mu s$ Note: 2: Actual refresh is  $32ms/8K = 3.90\mu s$

# 2 Functional Description

# 2.1 Clocks, Commands and Addresses

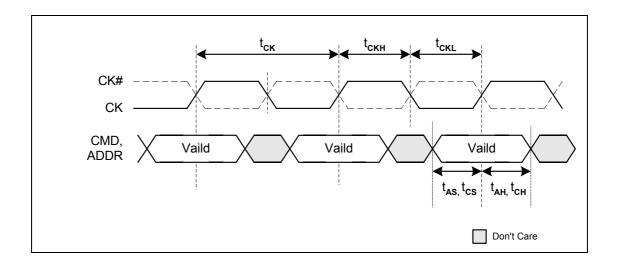

Figure 6 Clock Command/Address Timings

Table 6 General Timing Parameters for -2.5, -3.3 and -5.0 ns speed sorts

|                                  |                                  | -3.3 |      | -4   | l.0  | -5   |      |       |

|----------------------------------|----------------------------------|------|------|------|------|------|------|-------|

| Parameter                        | Symbol                           | min  | max  | min  | max  | min  | max  | Units |

| Clock                            |                                  |      |      |      |      |      | •    |       |

| Clock Cycle Time                 | <sup>‡</sup> CK                  | 3.3  | -    | 4.0  | -    | 5.0  | -    | ns    |

| Clock high level width           | <sup>t</sup> CKH                 | 0.45 | 0.55 | 0.45 | 0.55 | 0.45 | 0.55 | tCK   |

| Clock low level width            | <sup>t</sup> CKL                 | 0.45 | 0.55 | 0.45 | 0.55 | 0.45 | 0.55 | tCK   |

| Setup Times                      |                                  |      |      |      |      |      |      |       |

| Address/Command input setup time | tAS, tCS                         | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

| Hold Times                       |                                  |      |      |      |      |      |      |       |

| Address/Command input hold time  | <sup>t</sup> AH, <sup>t</sup> CH | 1.0  | _    | 1.0  | _    | 1.0  | _    | ns    |

Note: 1. All timings are measured relatively to the crossing point of CK/CK# and to the crossing point with VREF of the Command and Address signals.

Note: 2. The signal imput slew rate must be  $\geq 1V/ns$ .

Note: 3. CK/CK# input slew rate must be  $\geq$  1V/ns (  $\geq$  2V/ns if measured differentially).

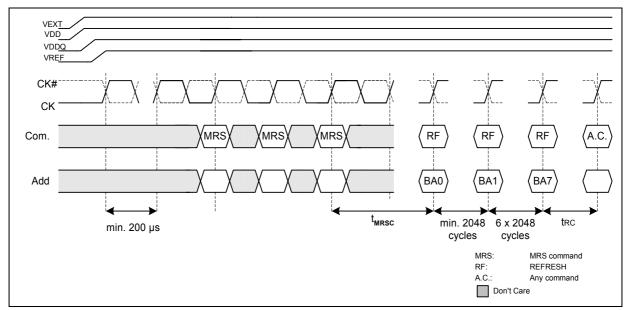

#### 2.2 Initialization

The RLDRAM must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation or permanent damage to the device.

The following sequence is used for Power-Up:

- 1. Apply power (VEXT, VDD, VDDQ, VREF) and start clock as soon as the supply voltages are stable. Apply VDD and VEXT before or at the same time as VDDQ, apply VDDQ before or at the same time as VREF. There is no timing relation between VEXT and VDD, the chip starts the power up sequence only when both voltages are at their nominal level. However, the pad supply must not be applied before the core supplies. Maintain all pins in NOP conditions.

- 2. Maintain stable conditions for 200 µs minimum.

- 3. Issue three Mode Register Set commands 2 dummies plus 1 valid MRS (Figure 7).

- 4. After t<sub>MRSC</sub> issue 8 Auto Refresh commands, one on each bank and separated by 2048 cycles.

- 5. After t<sub>RC</sub> the chip is ready for normal operation.

Figure 7 Power Up Sequence

Note: When the RLDRAM is powered up with the matched impedance mode inactive, the 2048 cycles between the 8 Refresh commands are not required. These cycles are necessary in order to calibrate the Output drivers.

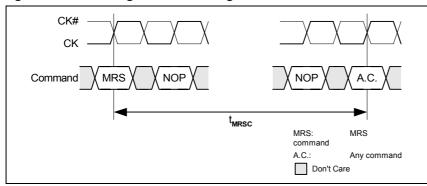

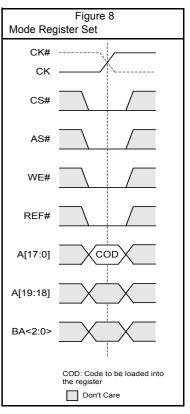

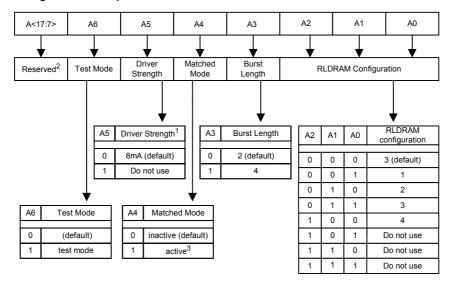

# 2.3 Mode Register Set Command (MRS)

The mode register stores the data for controlling the operating modes of the memory. It programs the RLDRAM configuration, burst length, test mode and IO options. During a Mode Register Set command the address inputs A<17:0> are sampled and stored in the mode register.  $t_{MRSC}$  must be met before any command can be issued to the RLDRAM. The mode register may only be set immediately after power up sequence.

Figure 9 Mode Register Set Timing

Table 7 Timing Parameters MRS

|                              |                   | -3  | 3.3 | -4  | 1.0 | -5  | 5.0 | 11.24 | New   |  |

|------------------------------|-------------------|-----|-----|-----|-----|-----|-----|-------|-------|--|

| Parameter                    | Symbol            | min | max | min | max | min | max | Units | Notes |  |

| Mode Register Set cycle time | <sup>t</sup> MRSC | 4   | _   | 4   | -   | 4   | _   | tCK   |       |  |

Figure 10 Mode Register Bitmap

Note: 1 HSTL compliant current specification Note: 2 Bits A<17:6> must be set to zero

Note: 3 Automatic IO impedance calibration is activated in Matched Mode

# 2.4 Configuration Table

The following table shows, for different operating frequencies, the different RLDRAM configurations that can be programmed into the Mode Register. The Read Latency ( $t_{RL}$ ) and the Write Latency ( $t_{WL}$ ) used by the RLDRAM for the two Burst Lengths (BL) are also indicated. Finally the minimum row cycle time ( $t_{RC}$ ) in clock cycles and in ns are shown as well. The shaded areas correspond to configurations that are not allowed.

Table 8 RLDRAM configuration table

|                   |                       | Configura | tion |      |      |      |

|-------------------|-----------------------|-----------|------|------|------|------|

| Frequency         |                       | Unit      | 1    | 2    | 3    | 4    |

|                   | t <sub>RC</sub>       | cycles    | 5    | 6    | 7    | 8    |

|                   | t <sub>RL</sub>       | cycles    | 5    | 5    | 5    | 6    |

|                   | t <sub>WL</sub> (BL2) | cycles    | 2    | 2    | 2    | 3    |

|                   | t <sub>WL</sub> (BL4) | cycles    | 1    | 1    | 1    | 2    |

|                   | t <sub>RC</sub>       | ns        |      |      |      | 26.7 |

| 300 MHz (-3.3)    | <sup>t</sup> RL       | ns        |      |      |      | 20   |

| 300 WH IZ (-3.3)  | t <sub>WL</sub> (BL2) | ns        |      |      |      | 10   |

|                   | t <sub>WL</sub> (BL4) | ns        |      |      |      | 6.7  |

|                   | t <sub>RC</sub>       | ns        |      |      | 28.0 | 32.0 |

| 250 MHz (-4.0)    | t <sub>RL</sub>       | ns        |      |      | 20.0 | 24.0 |

| 250 WH IZ (-4.0)  | tWL (BL2)             | ns        |      |      | 8.0  | 12.0 |

|                   | tWL (BL4)             | ns        |      |      | 4.0  | 8.0  |

|                   | t <sub>RC</sub>       | ns        | 25.0 | 30.0 | 35.0 | 40.0 |

| 200 MHz (-5.0)    | <sup>t</sup> RL       | ns        | 25.0 | 25.0 | 25.0 | 30.0 |

| 200 WII IZ (-3.0) | t <sub>WL</sub> (BL2) | ns        | 10.0 | 10.0 | 10.0 | 15.0 |

|                   | tWL (BL4)             | ns        | 5.0  | 5.0  | 5.0  | 10.0 |

Note: 1: The speed sort -3.3 provides parts functional up to 300MHz in the configuration 4 only. The functionality of the configurations 1,2 and 3 is not guaranteed for speed sort -3.3.

Note: 2: The speed sort -4.0 provides parts functional up to 250MHz in the configurations 3 and 4 only. The functionality of the configurations 1 and 2 is not guaranteed for speed sort -4.0.

Note: 3: The speed sort -5.0 provides parts functional in all configurations.

### 2.5 Writes (WR)

#### 2.5.1 Write - Basic Information

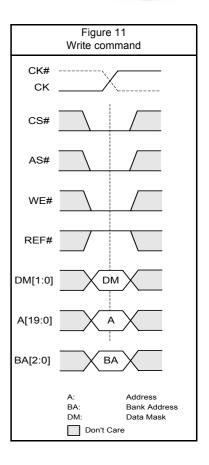

Write accesses are initiated with a WRITE command, as shown in Figure 11. Row and bank addresses are provided together with the WRITE command.

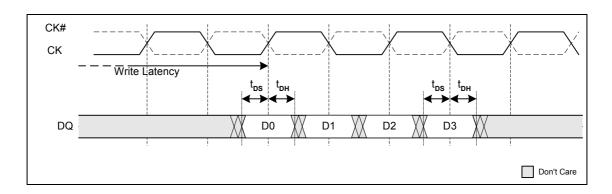

During WRITE commands, data will be registered at both edges of CK according to the programmed burst length BL. The first valid data is registered with the first rising CK edge WL (Write Latency) cycles after the WRITE command has been issued.

Any WRITE burst may be followed by a subsequent READ command. Figure 17 and Figure 18 illustrate the timing requirements for a WRITE followed by a READ for a burst of 2 and 4 respectively.

Setup and hold time for incoming DQs relative to the CK edges are specified as  $t_{DS}$  and  $t_{DH}$ .

The first or the second part of the incoming data burst is masked if the corresponding DMx signal is sampled HIGH along with the WRITE command. Setup and hold time for DM is the same as for addresses and commands.

Figure 12 Basic Write Burst Timing

**Table 9 WRITE Timing Parameters**

|                          |                 | -3  | 3.3 | -4  | 1.0 | -5  | 5.0 |       |       |

|--------------------------|-----------------|-----|-----|-----|-----|-----|-----|-------|-------|

| Parameter                | Symbol          | min | max | min | max | min | max | Units | Notes |

| Data-in to CK Setup Time | t <sub>DS</sub> | 0.5 | ı   | 0.5 | ı   | 0.5 | ı   | ns    |       |

| Data-in to CK Hold Time  | <i>t</i> DH     | 0.5 | ı   | 0.5 | -   | 0.5 | -   | ns    |       |

Note: 1. All timings are measured relatively to the crossing point of CK/CK# and to the crossing point with VREF of the Command and Address signals.

Note: 2. The signal imput slew rate must be  $\geq 1V/ns$ .

Note: 3. CK/CK# input slew rate must be  $\geq$  1V/ns ( $\geq$  2V/ns if measured differentially).

#### 2.5.2 Write - Cyclic Bank Access

#### 2.5.2.1 Burst Length (BL) = 2

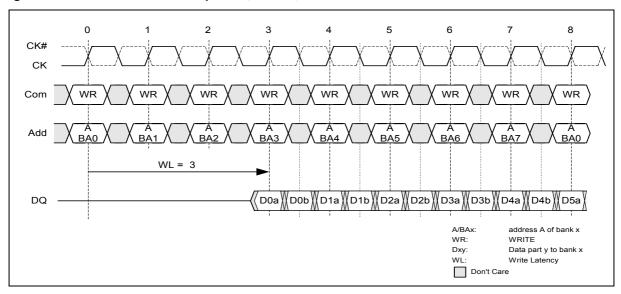

Figure 13 Write Burst Basic Sequence, BL = 2, WL = 3

#### 2.5.2.2 Burst Length (BL) = 4

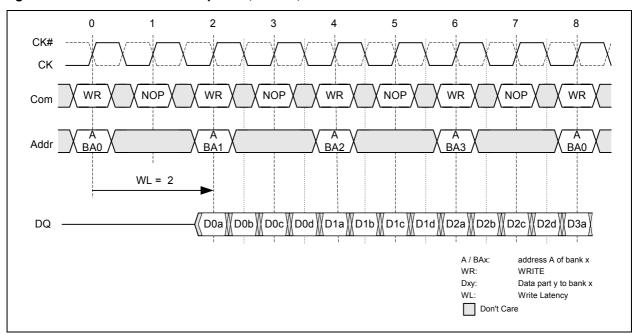

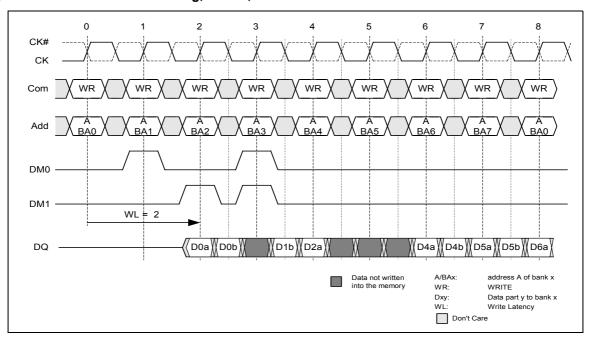

Figure 14 Write Burst Basic Sequence, BL = 4, WL = 2

# 2.5.3 Write Data Mask Timing

#### 2.5.3.3 Burst Length (BL) = 2

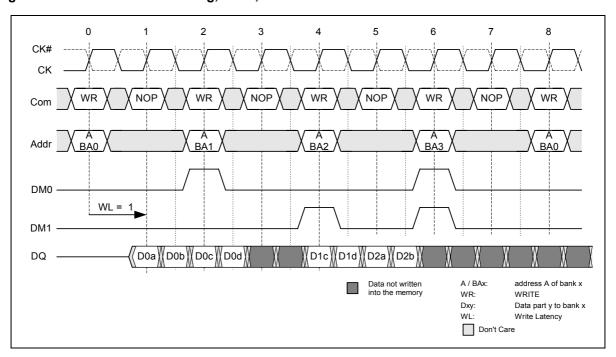

Figure 15 Write Data Mask Timing, BL = 2, WL = 2

#### 2.5.3.4 Burst Length (BL) = 4

Figure 16 Write Data Mask Timing, BL=4, WL = 1

#### 2.5.4 Write followed by Read

#### 2.5.4.5 Burst Length (BL) = 2

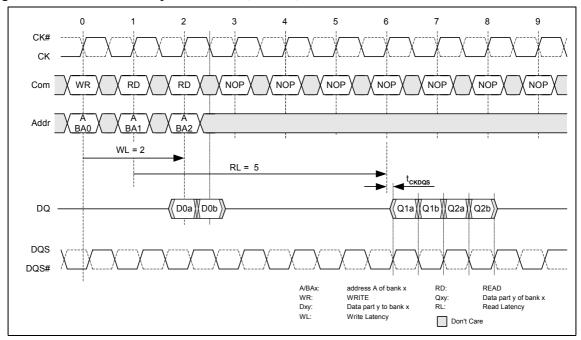

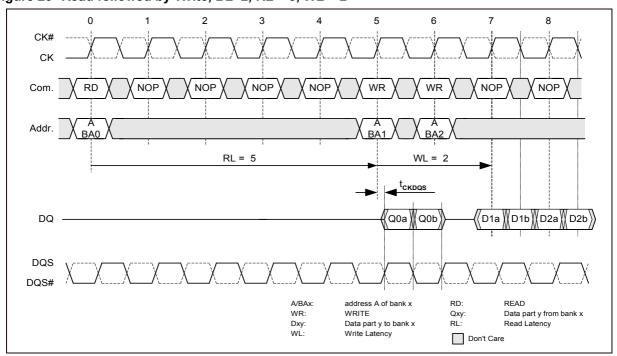

Figure 17 Write followed by Read BL = 2, RL = 5, WL = 2

#### 2.5.4.6 Burst Length (BL) = 4

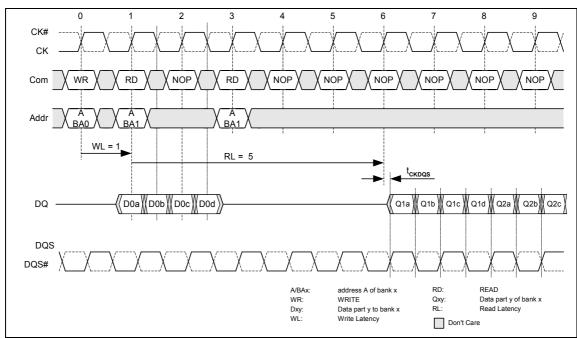

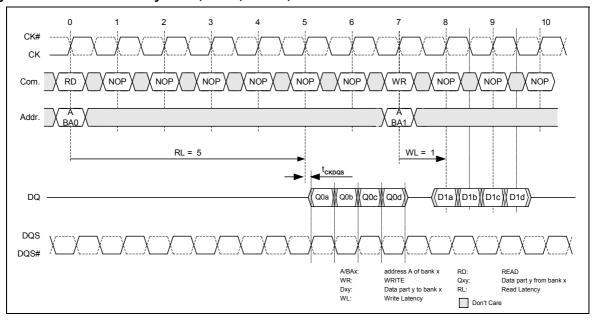

Figure 18 Write followed by Read BL = 4, RL = 5, WL = 1

# 2.6 Reads (RD)

#### 2.6.1 Read - Basic Information

Read accesses are initiated with a READ command, as shown in Figure 19. Row and bank addresses are provided with the READ command.

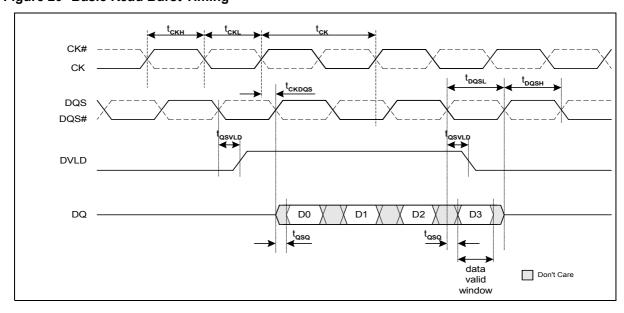

During READ bursts the memory device drives the read data edge aligned with the DQS signal. After a programmable read latency, data is available at the outputs. The data valid signal indicates that valid read data will be present on the bus after 0.5clock cycles.

The skew between DQS and CK is specified as t<sub>CKDQS</sub>.

$t_{\mbox{DQSQ}}$  is the skew between DQS edge and the last valid data edge.  $t_{\mbox{DQSQ}}$  is derived at each DQS clock edge and is not cumulative over time.

After completion of a burst, assuming no other commands have been initiated, output data will go High-Z. Back to back READ commands are possible, producing a continuous flow of output data.

The data valid window is derived for each DQS transition and is defined as:  $min(t_{DQSH}, t_{DQSL}) - 2*t_{QSQmax}$ .

Any READ burst may be followed by a subsequent WRITE command. Figure 23 shows the corresponding timing requirements for a READ followed by a WRITE. A READ to WRITE delay has to be buit in in order to prevent bus contention. Some systems having long line lengths or severe skews may need additional idle cycles inserted.

Figure 20 Basic Read Burst Timing

Table 10 READ Timing Parameters for -2.5, -3-3 and -5.0 speed sorts

| Parameter                                             | Symbol             | -3   | 3.3 | -4   | 1.0 | -5   | 5.0 | Units | Notes |  |  |  |  |

|-------------------------------------------------------|--------------------|------|-----|------|-----|------|-----|-------|-------|--|--|--|--|

|                                                       |                    | min  | max | min  | max | min  | max |       |       |  |  |  |  |

| Read Cycle Timing Parameters for Data and Data Strobe |                    |      |     |      |     |      |     |       |       |  |  |  |  |

| DQS / DQS# high pulse width                           | <sup>t</sup> DQSH  | 0.4  | 0.6 | 0.4  | 0.6 | 0.4  | 0.6 | tCK   |       |  |  |  |  |

| DQS / DQS# low pulse width                            | <sup>t</sup> DQSL  | 0.4  | 0.6 | 0.4  | 0.6 | 0.4  | 0.6 | tCK   |       |  |  |  |  |

| DQS edge to Clock edge skew                           | tCKDQS             | 2.7  | 3.7 | 2.7  | 3.7 | 2.7  | 3.7 | ns    |       |  |  |  |  |

| DQS edge to output data edge                          | <sup>t</sup> QSQ   |      | 0.3 |      | 0.3 |      | 0.3 | ns    | 4     |  |  |  |  |

| DQS edge to Data Out HiZ                              | <sup>t</sup> QSQHZ |      | 0.4 |      | 0.4 |      | 0.4 | ns    | 4     |  |  |  |  |

| DQS edge to DVLD edge                                 | <sup>t</sup> QSVLD | -0.4 | 0.4 | -0.4 | 0.4 | -0.4 | 0.4 | ns    |       |  |  |  |  |

Note: 1 All timings are measured relatively to the crossing point of CK/CK# (DQSx/DQSx#), and to the crossing point with VREF of the Command and Address signals.

Note: 2. The signal imput slew rate must be  $\geq 1V/ns$ .

Note: 3. CK/CK# input slew rate must be  $\geq$  1V/ns ( $\geq$  2V/ns if measured differentially).

Note: 4. tDQSQ and tQSQHZ are absolute values.

# 2.6.2 Read - Cyclic Bank Access

#### 2.6.2.1 Burst Length (BL) = 2

#### Figure 21 Read Burst, BL = 2, RL = 5

#### 2.6.2.2 Burst Length (BL) = 4

# Figure 22 Read Burst, BL = 4, RL = 5

# 2.6.3 Read followed by Write

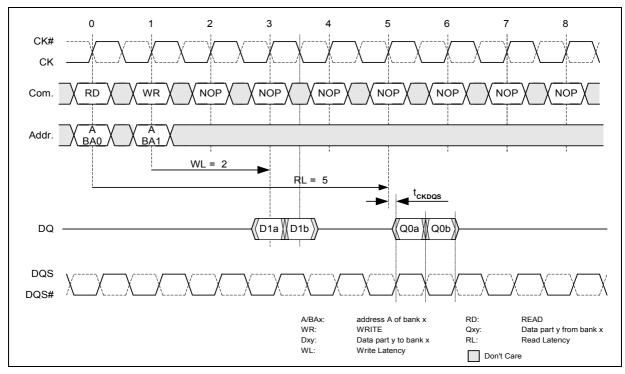

Figure 23 Read followed by Write, BL=2, RL = 5, WL = 2

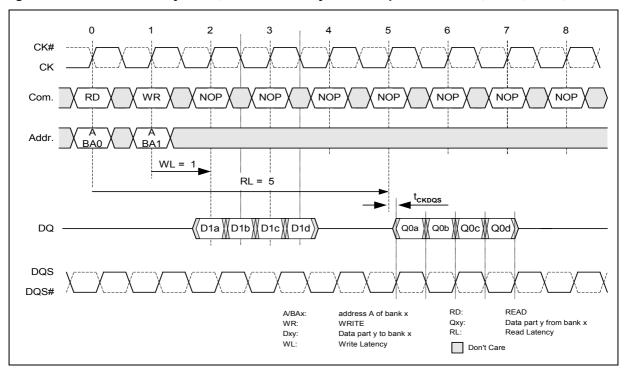

Figure 24 Read followed by Write, Write data on bus prior Read data, BL=2, RL=5, WL=2

Figure 25 Read followed by Write, BL=4, RL = 5, WL = 1

Figure 26 Read followed by Write, write data on system bus prior read data, BL=4, RL=5, WL=1

# 3 IEEE 1149.1 Serial Boundary Scan (JTAG)

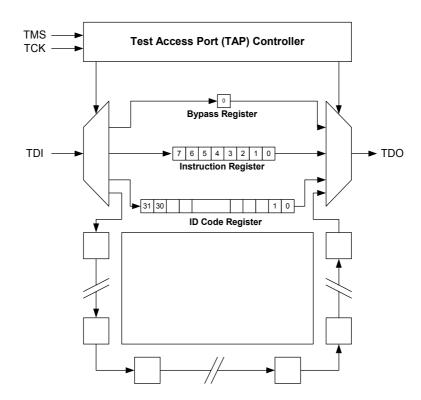

The RLDRAM incorporates a serial boundary scan Test Access Port (TAP). This port operates fully complient with IEEE Standard 1149.1-1990. It contains a TAP controller, instruction register, boundary scan register, bypass register, and ID code register.

It is possible to operate the RLDRAM without using the JTAG feature. To disable the TAP controller, TCK must be tied low while TDI, TMS and TDO may be left unconnected. Upon power-up, the TAP will come up in a reset state which will not interfere with the normal operation of the device.

#### 3.1 Test Access Port (TAP)

#### 3.1.1 Test Clock (TCK)

The test clock is used only with the TAP controller. The pin must be tied low if the TAP is not used.

#### 3.1.2 Test Mode Select (TMS)

The TMS input is used to give commands to the TAP controller and is sampled on the rising edge of TCK. This pin may be left unconnected if the TAP is not used.

#### 3.1.3 Test Data-In (TDI)

The TDI pin is used to serially input information into the registers. The register between TDI and TDO is chosen by the instruction that is loaded into the TAP instruction register. TDI is connected to the most significant bit (MSB) of any register (see Figure 27). This pin may be left unconnected if the TAP is not used.

#### 3.1.4 Test Data-Out (TDO)

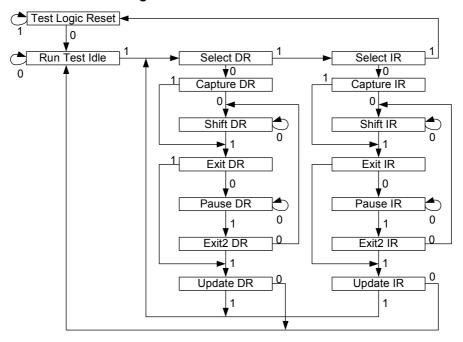

The TDO output pin is used to serially clock data-out from the registers. The output is active depending upon the current state of the TAP state machine (see Figure 28). The output changes on the falling edge of TCK. TDO is connected to the least significant bit (LSB) of any register (see Figure 27). This pin may be left unconnected if the TAP is not used.

#### 3.2 TAP Registers

Registers are connected between the TDI and TDO pins and allow data to be scanned into and shifted out of the RLDRAM test circuitry (see Figure 27). Only one register is selected at a time through the instruction register. Data is serially loaded into the TDI pin on the rising edge of TCK. Data is output on the TDO pin on the falling edge of TCK.

#### 3.2.1 Instruction Register

Eight-bit instructions can be serially loaded into the instruction register. This register is loaded when it is placed between the TDI and TDO pins as shown in Figure 27. Upon power-up, the instruction register is internally preloaded with the IDCODE instruction.

When the TAP controller is in the Capture-IR state, the two least significant bits are loaded with a binary "01" pattern to allow for fault isolation of the board-level serial test data path.

# 3.2.2 Bypass Register

The bypass register is a single-bit register that can be placed between the TDI and TDO pins. This allows data to be shifted through the RLDRAM with minimal delay.

The bypass register is set LOW during the Capture-DR state when the BYPASS instruction is loaded in the instruction register.

### 3.2.3 Boundary Scan Register

The boundary scan register is connected to all the IO pins on the RLDRAM. It allows to observe and control the data flowing into and out of the device, depending on the instruction being loaded in the instruction register.

The boundary scan register is 104 bits long. The register is the same for the x16 and x32 configurations of the RLDRAM. Pins not used in the x16 configurations read a HIGH into the boundary scan register in the Capture-DR controller state.

Differential inputs (CK/CK#) and outputs (DQSx/DQSx#) are equipped with two boundary scan cells each. Thus, the differential nature of these pins is not visible to the test circuitry. However, it is recommended that during testing differential signals are always applied to these pin pairs.

### 3.2.4 Identification (ID) Register

The ID register is loaded with a hardwired, vendor-specific, 32-bit code during the Capture-DR state when the IDCODE instruction is loaded in the instruction register. The code can be shifted out when the TAP controller is in the Shift-DR state. Two different codes are implemented for the x16 and x32 configurations of the RLDRAM (see Table 11).

**Table 11 ID Register Definition**

|            | Revision Part Number<br>Number |    |    |    |    | Infineon JEDEC Code |    |    |    |    | L<br>S |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|------------|--------------------------------|----|----|----|----|---------------------|----|----|----|----|--------|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Bit #      | 31                             | 30 | 29 | 28 | 27 | 26                  | 25 | 24 | 23 | 22 | 21     | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| x16<br>x32 | 0                              | 0  | 0  | 1  | 0  | 0                   | 0  | 0  | 0  | 0  | 0      | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

### 3.3 TAP Instructions

The TAP implements the 6 instructions BYPASS, EXTEST, SAMPLE/PRELOAD and IDCODE for user access (see Table 12). The implementation of these instructions fully complies with the IEEE standard. All other instructions are reserved and should not be used.

**Table 12 JTAG Instruction Register**

|     | on Register<br>Code | Instruction      | Description                                                                                                                                                                                                                                                                                                                     |

|-----|---------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hex | x7 x0               |                  |                                                                                                                                                                                                                                                                                                                                 |

| 00  | 0000 0000           | EXTEST           | Selects the boundary scan register to be connected between TDI and TDO. Data received at input pins are sampled and loaded into the boundary scan register. Data driven by output pins are determined from values contained in the boundary scan register.                                                                      |

| 05  | 0000 0101           | SAMPLE / PRELOAD | Selects the boundary scan register to be connected between TDI and TDO. Data receivedat input pins are sampled and loaded int the boundary scan register. initial ouput data are shifted into the boundary scan register prior to an EXTEST intruction. Instruction does not interfere with the normal operation of the device. |

| 21  | 0010 0001           | IDCODE           | Selects the ID code register to be connected to TDI and TDO. Instructin does not interfere with the normal operation of the device.                                                                                                                                                                                             |

| FF  | 1111 1111           | BYPASS           | Selects the bypass register to be connected between TDI and TDO. Instruction does not interfere with the normal operation of the device.                                                                                                                                                                                        |

#### 3.4 **Boundary Scan Exit Order**

#### 3.4.1 x16 Configuration

| Scan     | Reg         | Pin   | Pin   |        |        | Pin   | Pin   | Reg         | Scan     |

|----------|-------------|-------|-------|--------|--------|-------|-------|-------------|----------|

| Reg#     | Content     | Descr | Name  | Ball # | Ball # | Name  | Descr | Content     | Reg#     |

| 27<br>28 | Data<br>Enb | I/O   | DQ1   | B10    | В3     | DQ9   | I/O   | Enb<br>Data | 26<br>25 |

| 29<br>30 | Data<br>Enb | I/O   | DQ0   | B11    | B2     | DQ8   | I/O   | Enb<br>Data | 24<br>23 |

| 31<br>32 | Data<br>Enb | I/O   | DQ3   | C10    | СЗ     | DQ11  | I/O   | Enb<br>Data | 22<br>21 |

| 33<br>34 | Data<br>Enb | I/O   | DQ2   | C11    | C2     | DQ10  | I/O   | Enb<br>Data | 20<br>19 |

| 35       | Data        | 0     | DQS0# | D10    | D3     | DQS1# | 0     | Data        | 18       |

| 36       | Data        | 0     | DQS0  | D11    | D2     | DQS1  | 0     | Data        | 17       |

| 37<br>38 | Data<br>Enb | I/O   | DQ4   | E11    | E2     | DQ12  | I/O   | Enb<br>Data | 16<br>15 |

| 39<br>40 | Data<br>Enb | I/O   | DQ5   | E10    | E3     | DQ13  | I/O   | Enb<br>Data | 14<br>13 |

| 41<br>42 | Data<br>Enb | I/O   | DQ6   | F11    | F2     | DQ14  | I/O   | Enb<br>Data | 12<br>11 |

| 43<br>44 | Data<br>Enb | I/O   | DQ7   | F10    | F3     | DQ15  | I/O   | Enb<br>Data | 10<br>9  |

| 45       | Data        | 0     | DVLD  | F12    | F1     | DM0   | Ι     | Data        | 8        |

| 46       | Data        | Ţ     | A1    | G11    | G2     | A6    | -     | Data        | 7        |

| 47       | Data        | Ţ     | A2    | G10    | G3     | A7    | -     | Data        | 6        |

| 48       | Data        | ı     | A0    | G12    | G1     | A5    | _     | Data        | 5        |

| 49       | Data        | ı     | A3    | H12    | H1     | A8    | _     | Data        | 4        |

| 50       | Data        | ı     | A4    | H11    | H2     | A9    | _     | Data        | 3        |

| 51       | Data        | ı     | B0    | J11    | J2     | B2    | _     | Data        | 2        |

| 52       | Data        | ı     | CK    | J12    | J1     | AS#   | _     | Data        | 1        |

|          |             |       |       |        |        |       |       |             |          |

| 53       | Data        | ı     | CK#   | K12    | K1     | WE#   | I     | Data        | 104      |

| 54       | Data        | - 1   | B1    | K11    | K2     | REF#  | -     | Data        | 103      |

| 55       | Data        | - 1   | A14   | L11    | L2     | CS#   | -     | Data        | 102      |

| 56       | Data        | - 1   | A13   | L12    | L1     | A19   | -     | Data        | 101      |

| 57       | Data        | - 1   | A10   | M12    | M1     | A15   | -     | Data        | 100      |

| 58       | Data        | ı     | A12   | M10    | M3     | A17   | I     | Data        | 99       |

| 59       | Data        | I     | A11   | M11    | M2     | A16   | - 1   | Data        | 98       |

| 60       | Data        | - 1   | A18   | N12    | N1     | DM1   | - 1   | Data        | 97       |

| 61<br>62 | Data<br>Enb | I/O   | DQ31  | N10    | N3     | DQ23  | I/O   | Enb<br>Data | 96<br>95 |

| 63<br>64 | Data<br>Enb | I/O   | DQ30  | N11    | N2     | DQ22  | I/O   | Enb<br>Data | 94<br>93 |

| 65<br>66 | Data<br>Enb | I/O   | DQ29  | P10    | P3     | DQ21  | I/O   | Enb<br>Data | 92<br>91 |

| 67<br>68 | Data<br>Enb | I/O   | DQ28  | P11    | P2     | DQ20  | I/O   | Enb<br>Data | 90<br>89 |

| 69       | Data        | 0     | DQS3  | R11    | R2     | DQS2  | 0     | Data        | 88       |

| 70       | Data        | 0     | DQS3# | R10    | R3     | DQS2# | 0     | Data        | 87       |

| 71<br>72 | Data<br>Enb | I/O   | DQ26  | T11    | T2     | DQ18  | I/O   | Enb<br>Data | 86<br>85 |

| 73<br>74 | Data<br>Enb | I/O   | DQ27  | T10    | Т3     | DQ19  | I/O   | Enb<br>Data | 84<br>83 |

| 75<br>76 | Data<br>Enb | I/O   | DQ24  | U11    | U2     | DQ16  | I/O   | Enb<br>Data | 82<br>81 |

| 77<br>78 | Data<br>Enb | I/O   | DQ25  | U10    | U3     | DQ17  | I/O   | Enb<br>Data | 80<br>79 |

Note: 1: Input pins are connected to Observe-Only Boundary Scan Register Cells.

Note: 2: Output pins are connected to Force-Only Boundary Scan Register Cells.

Note: 3: IO pins are connected to Control-and-Observe Boundary Scan Register Cells.

Note: 4: For BL 4 the content of the register 101 will be set to 0 if A19 is not connected. Otherwise, the register content will be equal

to the logical value applied to pin A19.

# 3.4.2 x32 Configuration

|              |                | Pin   |             |        |   |        |             | Pin   |                |              |

|--------------|----------------|-------|-------------|--------|---|--------|-------------|-------|----------------|--------------|

| Scan<br>Reg# | Reg<br>Content | Descr | Pin<br>Name | Ball # |   | Ball # | Pin<br>Name | Descr | Reg<br>Content | Scan<br>Reg# |

|              |                |       | Name        |        |   |        | Name        |       |                |              |

| 27<br>28     | Data<br>Enb    | I/O   | DQ1         | B10    |   | В3     | DQ9         | I/O   | Enb<br>Data    | 26<br>25     |

| 29<br>30     | Data<br>Enb    | I/O   | DQ0         | B11    |   | B2     | DQ8         | I/O   | Enb<br>Data    | 24<br>23     |

| 31<br>32     | Data<br>Enb    | I/O   | DQ3         | C10    |   | С3     | DQ11        | I/O   | Enb<br>Data    | 22<br>21     |

| 33<br>34     | Data<br>Enb    | I/O   | DQ2         | C11    |   | C2     | DQ10        | I/O   | Enb<br>Data    | 20<br>19     |

| 35           | Data           | 0     | DQS0#       | D10    | Ī | D3     | DQS1#       | 0     | Data           | 18           |

| 36           | Data           | 0     | DQS0        | D11    | Ť | D2     | DQS1        | 0     | Data           | 17           |

| 37<br>38     | Data<br>Enb    | I/O   | DQ4         | E11    |   | E2     | DQ12        | I/O   | Enb<br>Data    | 16<br>15     |

| 39<br>40     | Data<br>Enb    | I/O   | DQ5         | E10    |   | E3     | DQ13        | I/O   | Enb<br>Data    | 14<br>13     |

| 41<br>42     | Data<br>Enb    | I/O   | DQ6         | F11    |   | F2     | DQ14        | I/O   | Enb<br>Data    | 12<br>11     |

| 43<br>44     | Data<br>Enb    | I/O   | DQ7         | F10    |   | F3     | DQ15        | I/O   | Enb<br>Data    | 10<br>9      |

| 45           | Data           | 0     | DVLD        | F12    | Ī | F1     | DM0         | I     | Data           | 8            |

| 46           | Data           | ı     | A1          | G11    | Ť | G2     | A6          | - 1   | Data           | 7            |

| 47           | Data           | -     | A2          | G10    | Ť | G3     | A7          | - 1   | Data           | 6            |

| 48           | Data           | -     | A0          | G12    | Ť | G1     | A5          | - 1   | Data           | 5            |

| 49           | Data           | - 1   | A3          | H12    | Ť | H1     | A8          | - 1   | Data           | 4            |

| 50           | Data           | - 1   | A4          | H11    | Ť | H2     | A9          | - 1   | Data           | 3            |

| 51           | Data           | - 1   | В0          | J11    | Ť | J2     | B2          | - 1   | Data           | 2            |

| 52           | Data           | ı     | CK          | J12    | Ť | J1     | AS#         | - 1   | Data           | 1            |

|              |                |       |             |        | Ť |        |             |       |                |              |

| 53           | Data           | - 1   | CK#         | K12    | Ť | K1     | WE#         | - 1   | Data           | 104          |

| 54           | Data           | - 1   | B1          | K11    | Ť | K2     | REF#        | - 1   | Data           | 103          |

| 55           | Data           | -     | A14         | L11    | Ť | L2     | CS#         | - 1   | Data           | 102          |

| 56           | Data           | - 1   | A13         | L12    |   | L1     | A18         | - 1   | Data           | 101          |

| 57           | Data           | _     | A10         | M12    | Ĭ | M1     | A15         | -     | Data           | 100          |

| 58           | Data           | - 1   | A12         | M10    |   | М3     | A17         | - 1   | Data           | 99           |

| 59           | Data           | - 1   | A11         | M11    |   | M2     | A16         | - 1   | Data           | 98           |

| 60           | Data           | - 1   | NC          | N12    |   | N1     | DM1         | - 1   | Data           | 97           |

| 61<br>62     | Data<br>Enb    | I/O   | DQ31        | N10    |   | N3     | DQ23        | I/O   | Enb<br>Data    | 96<br>95     |

| 63<br>64     | Data<br>Enb    | I/O   | DQ30        | N11    |   | N2     | DQ22        | I/O   | Enb<br>Data    | 94<br>93     |

| 65<br>66     | Data<br>Enb    | I/O   | DQ29        | P10    |   | P3     | DQ21        | I/O   | Enb<br>Data    | 92<br>91     |

| 67<br>68     | Data<br>Enb    | I/O   | DQ28        | P11    | · | P2     | DQ20        | I/O   | Enb<br>Data    | 90<br>89     |

| 69           | Data           | 0     | DQS3        | R11    | t | R2     | DQS2        | 0     | Data           | 88           |

| 70           | Data           | 0     | DQS3#       | R10    | Ť | R3     | DQS2#       | 0     | Data           | 87           |

| 71<br>72     | Data<br>Enb    | I/O   | DQ26        | T11    |   | T2     | DQ18        | I/O   | Enb<br>Data    | 86<br>85     |

| 73<br>74     | Data<br>Enb    | I/O   | DQ27        | T10    |   | Т3     | DQ19        | I/O   | Enb<br>Data    | 84<br>83     |

| 75<br>76     | Data<br>Enb    | I/O   | DQ24        | U11    | • | U2     | DQ16        | I/O   | Enb<br>Data    | 82<br>81     |

| 77<br>78     | Data<br>Enb    | I/O   | DQ25        | U10    |   | U3     | DQ17        | I/O   | Enb<br>Data    | 80<br>79     |

Note: 1: Input pins are connected to Observe-Only Boundary Scan Register Cells.

Note: 2: Output pins are connected to Force-Only Boundary Scan Register Cells.

Note: 3: IO pins are connected to Control-and-Observe Boundary Scan Register Cells.

Note: 4: For BL 4 the content of the register 101 will be set to 0 if A18 is not connected. Otherwise, the register content will be equal to the logical value applied to pin A18.

# 3.5 TAP Operation

The user must be aware that the TAP controller clock can only operate at a frequency up to 50 MHz, while the RLDRAM clock operates much faster. As a consequence, it is possible that an input or output will undergo a transition right at the moment when the TAP takes the snapshot in the Capture-DR state of the SAMPLE/PRELOAD instruction. The TAP may then try to capture a signal while in transition (metastable state). This will not harm the device, but there is no guarantee as to the value that will be captured. To guarantee that the boundary scan register will capture the correct value of a signal, the signal must meet the TAP's setup and hold time ( tCS plus tCH) around the rising edge of TCK.

# 3.6 JTAG TAP Block Diagram

Figure 27 TAP Block Diagram

# 3.7 JTAG TAP Controller State Diagram

Figure 28 TAP Controller State Diagram

# 3.8 JTAG DC Operating Conditions

| Parameter                                             | Symbol           | Lii                        | mit Valu | es                        | Unit | Notes |

|-------------------------------------------------------|------------------|----------------------------|----------|---------------------------|------|-------|

|                                                       |                  | min.                       | typ.     | max.                      |      |       |

| Input logic high voltage, DC                          | VTIH             | V <sub>REF</sub><br>+ 0.15 | -        | V <sub>DDQ</sub><br>+ 0.3 | V    |       |

| Input logic low voltage, DC                           | V <sub>TIL</sub> | V <sub>SSQ</sub><br>-0.3   | -        | V <sub>REF</sub> - 0.15   | V    |       |

| Output logic high voltage (I <sub>OH</sub> = -tbd mA) | Vтон             | V <sub>REF</sub><br>+ tbd  | -        | -                         | V    |       |

| Output logic low voltage (I <sub>OL</sub> = tbd mA)   | VTOL             | -                          | -        | V <sub>REF</sub>          | V    |       |

# 3.9 JTAG AC Operating Conditions

| Parameter                                  | Symbol           | min.                  | typ.                | max.                  | Unit | Notes |

|--------------------------------------------|------------------|-----------------------|---------------------|-----------------------|------|-------|

| Input logic high voltage, AC               | $V_{TIH}$        | V <sub>REF</sub> +0.3 | -                   | V <sub>DDQ</sub> +0.3 | V    |       |

| Input logic low voltage, AC                | VTIL             | V <sub>SSQ</sub> -0.3 | -                   | V <sub>REF</sub> -0.3 | V    |       |

| Input Slew Rate                            | T <sub>TSL</sub> | 1.0                   | -                   | -                     | V/ns |       |

| Input and Output Timing<br>Reference Level | VREF             |                       | V <sub>DDQ</sub> /2 |                       | V    |       |

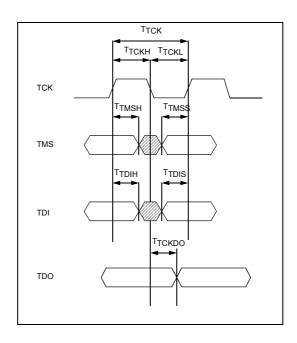

#### 3.10 JTAG AC Electrical Characteristics

| Parameter            | Symbol             | min. | max. | Unit | Notes |

|----------------------|--------------------|------|------|------|-------|

| TCK Cycle Time       | TTCK               | 20   | ı    | ns   |       |

| TCK High Pulse Width | TTCKH              | 10   |      | ns   |       |

| TCK Low Pulse Width  | TTCKL              | 10   | -    | ns   |       |

| TCK Low to TDO Valid | T <sub>TCKDO</sub> | ı    | 10   | ns   |       |

| TDI Set Up Time      | TTDIS              | 5    | -    | ns   |       |

| TMS Set Up Time      | T <sub>TMSS</sub>  | 5    |      | ns   |       |

| TDI Hold Time        | TTDIH              | 5    | -    | ns   |       |

| TMS Hold Time        | T <sub>TMSH</sub>  | 5    | -    | ns   |       |

# 3.11 JTAG Timing Diagram

#### 4 Electrical Characteristics

# 4.1 Absolute Maximum Ratings

| • | Storage temperature range             | – 55 to + 150 °C               |

|---|---------------------------------------|--------------------------------|

| • | Input/output pins voltage             | 0.3 to V <sub>DDQ</sub> + 0.3V |

| • | Inputs and VREF voltage               | 0.3 to V <sub>DDQ</sub> + 0.3V |

| • | Power supply voltage V <sub>DD</sub>  | – 0.3 to + 2.1V                |

| • | Power supply voltage VEXT             | 0.3 to + 2.8V                  |

| • | Power supply voltage V <sub>DDQ</sub> | – 0.3 to + 2.1V                |

| • | Junction Temperature                  | 0°C to 100°C                   |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 4.2 Recommended Power & DC Operation Ratings

All values are recommended operating conditions unless otherwise noted.

**Table 13 Power & DC Operating Conditions**

| Parameter                                            | Symbol    | min.                   | typ. | max.                   | Unit | Notes |

|------------------------------------------------------|-----------|------------------------|------|------------------------|------|-------|

| Power Supply Voltages                                | VEXT      | 2.38                   | 2.5  | 2.63                   | V    |       |

| Fower Supply Voltages                                | $V_{DD}$  | 1.75                   | 1.8  | 1.85                   | ٧    |       |

| Power Supply Voltage for I/O                         | $V_{DDQ}$ | 1.7                    | 1.8  | 1.9                    | V    |       |

| Reference Voltage                                    | Vref      | 0.49*                  | 0.9  | 0.51*                  | ٧    | 1,2,3 |

| Telefolioc Voltage                                   | VICI      | $V_{\mathrm{DDQ}}$     |      | $V_{DDQ}$              |      |       |

| Input leakage current                                | $I_{IL}$  | -5                     |      | +5                     | μΑ   |       |

| CLK Input leakage current                            | $I_{ILC}$ | -5                     |      | +5                     | μА   |       |

| Output leakage current                               | IOL       | -5                     |      | +5                     | μА   |       |

| V <sub>REF</sub> Current                             | IREF      | -5                     |      | +5                     | μА   |       |

| Matched Impedance 1.8V  Input logic high voltage, DC | $V_{IH}$  | Vref + 0.15            | _    | V <sub>DDQ</sub> + 0.3 | V    |       |

| Input logic low voltage, DC                          | $V_{IL}$  | V <sub>SSQ</sub> - 0.3 | _    | Vref - 0.15            | V    |       |

| Output high voltage                                  | VOH       | VDDQ                   | -    | -                      | V    |       |

| Output low voltage                                   | VOL       | -                      | -    | 0                      | V    |       |

| HSTL strong                                          |           |                        |      |                        |      |       |

| Input logic high voltage, DC                         | $V_{IH}$  | Vref + 0.1             | _    | V <sub>DDQ</sub> + 0.3 | V    |       |

| Input logic low voltage, DC                          | $V_{IL}$  | V <sub>SSQ</sub> - 0.3 | -    | Vref - 0.1             | V    |       |

| Output high voltage                                  | VOH       | VDDQ-0.4               | -    | -                      | V    |       |

| Output low voltage                                   | VOL       | -                      | -    | 0.4                    | ٧    |       |

Note: 1. Typically the value of Vref is expected to be 0.5  $^*$  V<sub>DDQ</sub> of the transmitting device. Vref is expected to track variations in V<sub>DDQ</sub>

Note: 2. Peak to peak AC noise on Vref may not exceed 2% Vref (DC)

Note: 3. Vtt of the transmitting device must track Vref of the receiving device.

Note: 4. Recommanded on board decouping capacitors : VDDQ:  $2 \times 0.1 \mu F$  / device, VDD:  $2 \times 0.1 \mu F$  / device, VEXT:  $0.1 \mu F$  / device.

# 4.3 AC Operation Ratings

Table 14 AC Operation Conditions for Matched Impedance mode

| Parameter                                    | Symbol    | min.                   | typ. | max.                   | Unit | Notes |  |  |  |

|----------------------------------------------|-----------|------------------------|------|------------------------|------|-------|--|--|--|

| Matched Impedance 1.8V                       |           |                        |      |                        |      |       |  |  |  |

| Input logic high voltage, AC DDR             | $V_{IH}$  | Vref + 0.3             | _    | V <sub>DDQ</sub> + 0.3 | V    |       |  |  |  |

| Input logic low voltage, AC DDR              | $V_{IL}$  | V <sub>SSQ</sub> - 0.3 | _    | Vref - 0.3             | V    |       |  |  |  |

| Clock Differential Input Voltage (CLK/ CLK#) | $V_{ID}$  | 0.6                    | _    | V <sub>DDQ</sub> + 0.6 | V    |       |  |  |  |

| Clock Input Crossing Point (CLK/ CLK#)       | $V_{IX}$  | Vref - 0.15            | Vref | Vref + 0.15            | V    |       |  |  |  |

| I/O Reference Voltage                        | $V_{ref}$ | 0.49*V <sub>DDQ</sub>  |      | 0.51*V <sub>DDQ</sub>  | V    |       |  |  |  |

| HSTL strong                                  |           |                        |      |                        |      |       |  |  |  |

| Input logic high voltage, AC DDR             | $V_{IH}$  | Vref + 0.3             | _    | V <sub>DDQ</sub> + 0.3 | V    |       |  |  |  |

| Input logic low voltage, AC DDR              | $V_{IL}$  | V <sub>SSQ</sub> - 0.3 | _    | Vref - 0.3             | V    |       |  |  |  |

| Clock Differential Input Voltage (CLK/ CLK#) | $V_{ID}$  | 0.6                    | -    | V <sub>DDQ</sub> + 0.6 | V    |       |  |  |  |

| Clock Input Crossing Point (CLK/ CLK#)       | $V_{IX}$  | Vref - 0.15            | Vref | Vref + 0.15            | V    |       |  |  |  |

| I/O Reference Voltage                        | $V_{ref}$ | 0.49*V <sub>DDQ</sub>  |      | 0.51*V <sub>DDQ</sub>  | V    |       |  |  |  |

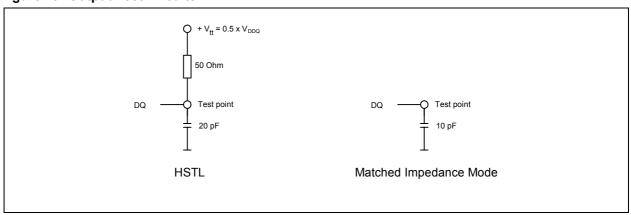

# 4.4 Output Test Conditions

# Figure 29 Output Test Circuits

Note:  $VDDQ=1.8V \pm 0.1V$ , TJ = 0 °C to 100 °C

# 4.5 Pin Capacitances

**Table 15 Pin Capacitances**

| Pin                                          |     | Тур. | Max | Unit |

|----------------------------------------------|-----|------|-----|------|

| A<19:0>, BA<2:0>, CS#, AREF#, WE#            | 2.0 | 3.0  | 4.0 | pF   |

| CLK, CLK#                                    | 2.0 | 3.0  | 4.0 | pF   |

| DQ<31:0>, DQS0, DQS0#, DQS1, DQS1#, DVLD, DM |     | 3.0  | 4.0 | pF   |

# 4.6 Operating Currents

# Table 16 I<sub>DD</sub> Specifications and Conditions

| Parameter                                                  | Symbol/ |             | Limit Values |            | Unit     | Notos                                                                 |  |  |

|------------------------------------------------------------|---------|-------------|--------------|------------|----------|-----------------------------------------------------------------------|--|--|

|                                                            | Freq    |             | x16          | x32        | Ullit    | Notes                                                                 |  |  |

| IDD1 (*) Operating Current (Average Power Supply Current)  | 300MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | Burst Length = 2<br>t <sub>CK</sub> =min, t <sub>RC</sub> =min,       |  |  |

|                                                            | 250MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | 1 bank active, Address change one time during min t <sub>RC</sub> ,   |  |  |

|                                                            | 200MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | Read/Write command cycling <sup>1.)</sup>                             |  |  |

| IDD4R (*) Operating Current (Average Power Supply Current) | 300MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | Burst Length = 4<br>t <sub>CK</sub> =min, t <sub>RC</sub> =min,       |  |  |

|                                                            | 250MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | 4 banks interleave,<br>address change with<br>each bank activation,   |  |  |

|                                                            | 200MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | continuous read operation 1.)                                         |  |  |

| IDD8 (*) Operating Current (Average Power Supply Current)  | 300MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | Burst Length = 2<br>t <sub>CK</sub> =min, t <sub>RC</sub> =min,       |  |  |

|                                                            | 250MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | 8banks interleave,<br>address change with<br>each bank activation,    |  |  |

|                                                            | 200MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | continuous read operation 1.)                                         |  |  |

|                                                            | 300MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA |                                                                       |  |  |

| Standby Current                                            | 250MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | t <sub>CK</sub> =min<br>All banks idle, CS=1<br>address/data toggling |  |  |

|                                                            | 200MHz  | VDD<br>VEXT | tbd<br>tbd   | tbd<br>tbd | mA<br>mA | one time/4 clk clock<br>inputs                                        |  |  |