T-75-07-07

# LR40981A Pulse Dialer CMOS LSI

# Description

The LR40981A is a CMOS LSI for pulse dialer with redial which integrates a ceramic resonator as a frequency reference.

### **Features**

- Make ratio: 33/39% pin-selectable

- Pulse output: "1" true

- Mute output: "0" true 3

- 17-digit redial with either \* or # input

- Uses a ceramic oscillator as a frequency refer-

- Direct telephone line operation

- Uses either a standard 2-of-7 matrix keyboard or a single contact keyboard

- Mute signal generated on pulse signal

- 16-pin dual-in-line package

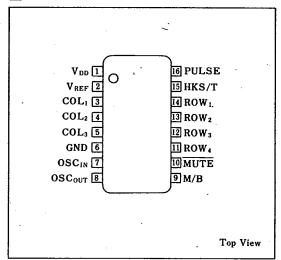

# Pin Connections

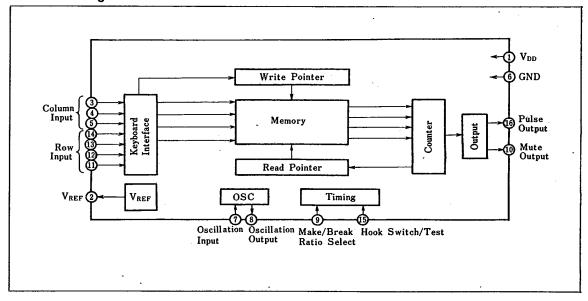

# **Block Diagram**

# Pulse Dialer CMOS LSI

LR40981A

# **Absolute Maximum Ratings**

T-75-07-07

| Parameter                 | Symbol           | Rating                       | Unit | Note |

|---------------------------|------------------|------------------------------|------|------|

| Supply voltage            | V <sub>DD</sub>  | -0.3 to $+6.2$               | V    | 1    |

| Operating temperature     | Topr             | -30 to +60                   | c    |      |

| Storage temperature       |                  | T <sub>stg</sub> -55 to +150 |      |      |

| Maximum power dissipation | P <sub>D</sub>   | 500                          | mW   | 2    |

|                           | V <sub>IN1</sub> | -0.3                         | V    | 3    |

| Maximum pin voltage       | V <sub>IN2</sub> | +0.3                         | V    | 4    |

Note 1: Referenced to GND.

Note 2: Ta=25℃.

Note 3: The maximum applicable voltage on any pin with respect to GND. Note 4: The maximum applicable voltage on any pin with respect to  $V_{\rm DD}$ .

# **Recommended Operating Conditions**

| Parameter      | Symbol            | Specified value | Unit |

|----------------|-------------------|-----------------|------|

| Supply voltage | $V_{\mathrm{DD}}$ | 2.5 to 6.0      | V    |

# **DC Characteristics**

(Ta=-30 to +60℃)

| Parameter                               | Symbol             | Conditions                                     | MIN.        | TYP.  | MAX.            | Unit | Note |

|-----------------------------------------|--------------------|------------------------------------------------|-------------|-------|-----------------|------|------|

| Key contact resistance                  | R <sub>KI</sub>    |                                                |             |       | 1               | kΩ   |      |

| Keyboard capacitance                    | C <sub>KI</sub>    |                                                |             |       | 30              | рF   |      |

| Input voltage                           | K <sub>1H</sub>    | 2-of-7 input mode                              | $0.8V_{DD}$ |       | V <sub>DD</sub> | V    | 1    |

|                                         | K <sub>IL</sub>    |                                                | GND         |       | $0.2V_{DD}$     | V    | 1    |

| Key pull-up resistance                  | K <sub>IRU</sub>   | V -COV V 40V                                   |             | 4     |                 | kΩ   |      |

| Key pull-down resistance                | K <sub>IRD</sub>   | $V_{DD} = 6.0 \text{V}, V_{IN} = 4.8 \text{V}$ |             | 100   | -1              | kΩ   |      |

| MUTE sink current                       | I <sub>M</sub>     | $V_{DD} = 2.5V, V_{OUT} = 0.5V$                | 500         |       |                 | μA   | 2    |

| Pulse output sink current               | I <sub>P</sub>     | $V_{DD} = 2.5 V, V_{OUT} = 0.5 V$              | 1.0         |       |                 | mA   | 3    |

| V <sub>DD</sub> -V <sub>RFF</sub> value | V <sub>REF</sub>   | $I_{SUPPLY} = 150 \mu A$                       | 1.5         | 2.5   | 3.5             | V    | 4    |

| Memory retention current                | I <sub>MR</sub>    | All outputs in no-load state                   |             | 0.7   |                 | μA   |      |

| Operating current                       | I <sub>OP</sub>    | All outputs in no-load state                   |             | 100   | 150             | μΑ   |      |

| MUTE, PULSE<br>leakage                  | I <sub>LKG</sub> . | V <sub>DD</sub> =6.0V, V <sub>OUT</sub> =6.0V  |             | 0.001 | 1               | μΑ   | 2,3  |

Note 1: Applies to key input pins (ROW<sub>1</sub>-ROW<sub>4</sub>, COL<sub>1</sub>-COL<sub>3</sub>).

Note 2: Applies to MUTE output pin.

Note 3: Applies to PULSE output pin.

Note 4: Applies to VREF pin.

# **AC Characteristics**

| Parameter                | Symbol           | MIN. | TYP. | MAX. | Unit | Notes |

|--------------------------|------------------|------|------|------|------|-------|

| Oscillator frequency     | f <sub>osc</sub> |      | 480  |      | kHz  | 1     |

| Keyboard debounce time   | t <sub>DB</sub>  |      | 10   |      | ms   |       |

| Time for valid key entry | t <sub>KD</sub>  | 40   |      |      | ms   | ]     |

| Oscillator start-up time | t <sub>os</sub>  |      | 6    |      | ms   | 2     |

| Pulse rate               | P <sub>R</sub>   |      | 10   |      | pps  |       |

| Break Pin 9 tied to V+   | t <sub>B</sub>   |      | 61   |      | ms   |       |

| Time Pin 9 tied to V-    | t <sub>B</sub>   |      | 67   |      | ms   |       |

| Inter-digital pause      | t <sub>IDP</sub> |      | 800  |      | ms   |       |

Note 1: Typical values are exact with a nominal 480 kHz frequency reference (except

for oscillator start-up time). Note 2: Ceramic resonator should have the following equivalent values:  $R<20\Omega$ ,  $RA\geq 70k\Omega$ ,  $C_0\leq 500pF$ .

SHARP

T-75-07-07

# **Pin Functions**

# V<sub>DD</sub> (Pin 1)

This is the positive supply input and is measured relative to GND (pin 6). The voltage on this pin must be regulated to less than 6 volts, using either the on-chip reference circuitry or an external form of regulation.

### V<sub>REF</sub> (Pin 2)

The V<sub>REF</sub> output provides a reference voltage that tracks internal parameters of the LR40981A. V<sub>REF</sub> provides a negative voltage reference to the V<sub>DD</sub> supply. Its magnitude will be approximately 0.6 volts greater than the minimum operating voltage of each particular LR40981A.

The typical application would be to connect the V<sub>REF</sub> pin to the GND pin (pin 6). The supply to the  $V_{DD}$  pin (pin 1) should then be regulated to 150  $\mu$  A (I<sub>OP</sub> max). With this amount of supply current, proper operation of the LR40981A is guaranteed.

The internal circuit of the V<sub>REF</sub> function is shown in Figure 1 with its associated I-V characteristics.

Q V<sub>DD</sub> (Pin 1)

# mA IREF [mA] 7.0 6.0 5.0 V<sub>REF</sub> (Pin 2) 4.0 2.0 1.0 2.0 1.0 3.0 4.0 5.0 [Volts] $(V_{DD}-V_{REF})$

Fig. 1 V<sub>REF</sub> typical I-V characteristics

# **Functional Description**

The LR40981A is a monolithic CMOS integrated circuit that converts keyboard inputs into pulse signal outputs which simulate a rotary telephone dial. It is designed to operate with a telephone line and can be interfaced so as to meet specifications of systems utilizing loop-disconnect signalling. Two outputs, one to pulse the telephone line and one to mute the receiver, are provided to implement the pulse dialer function. Accurate timing is accomplished by using a ceramic resonator as the frequency reference for the on-chip oscillator.

Keyboard logic is totally static so that the LR40981A will not introduce noise into the telephone system. Two outputs, one to pulse the telephone line and one to mute the receiver, are provided to implement the pulse dialer function.

When Off-Hook, the LR40981A senses a key down condition, verifies that only one key is depressed and then enters the key's code into an onchip memory.

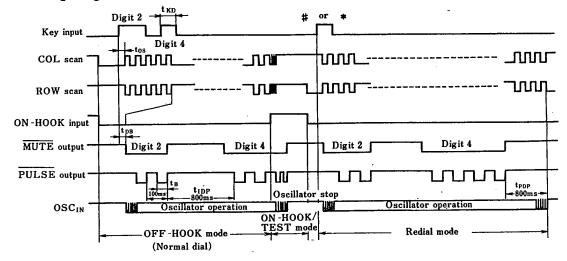

The FIFO (First In First Out) memory will store up to 17 digits, and allows keystrokes to be entered at rates comparable to tone dialing telephones. Entering the first digit starts a pre-digital pause counter and clears the memory buffer. At the end of the pre-digital pause, outpulsing begins. As digits are entered during the outpulsing period they will also be stored in the memory. Outpulsing will continue until all entered digits have been dialed. The first 17 digits entered will be stored in the on-chip redial memory and can be redialed by pressing either # or \*, provided that the receiver has been On-Hook for the minimum toH (refer to the AC Characteristics section).

When On-Hook, key inputs will not be recognized because the oscillator is disabled. This oscillator inhibit prevents the circuit from drawing excessive current when On-Hook.

An on-chip "Power-Up-Clear" circuit ensures reliable operation of the LR40981A. If the circuit power weakens, causing a possible loss of memory data integrity (see the electrical specifications), a "Power-Up-Clear" will occur when the proper supply level is restored. This function prevents "Redial" and the spontaneous outpulsing of incorrect data. A new number sequence may then be reentered in normal fashion.

T-75-07-07

# Keyboard Inputs (Pins 3, 4, 5, 11, 12, 13, 14)

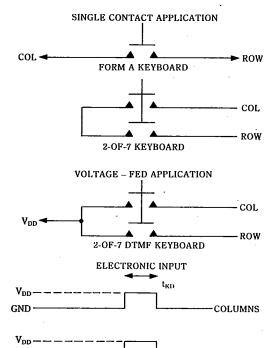

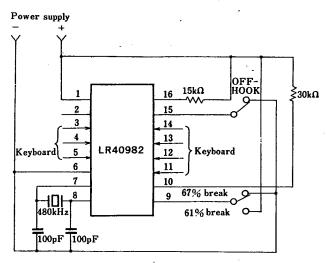

The LR40981A incorporates an innovative keyboard scheme that allows either the standard 2-of-7 keyboard with positive true common or the inexpensive single-contact (Form A) keyboard to be used, as shown in Figure 2.

A valid key entry is defined by either a single row being connected to a single column, or by  $V_{\rm DD}$  being simultaneously presented to both a row and a column.

When in the On-Hook mode, the row and column inputs are held high and no keyboard inputs are accepted, thus preventing any accidental key contacts from causing excessive current flow.

When Off-Hook, the keyboard is completely static until the initial valid key input is sensed. The oscillator is then enabled and the row and columns are alternately scanned (pulled high, then low) to verify that the input is valid. To be accepted, the input must remain valid continuously for 10ms of debounce time.

Fig. 2 Keyboard configuration

# Oscillator (Pins 7 and 8)

The LR40981A contains an on-chip inverter with sufficient gain to provide oscillation when used with a low-cost 480kHz ceramic resonator (anti-resonant mode). In addition to the resonator, two external capacitors are required. Suggested equivalent values for the resonator are given in the AC Characteristics section. These values will insure proper oscillator operation in the specified voltage range. The LR40981A may be driven externally with a 480 kHz signal on pin 7.

### GND (Pin 6)

This is the negative supply pin to which  $V_{\text{REF}}$  is normally tied (see  $V_{\text{REF}}$  paragraph).

# Make/Break Select (Pin 9)

The Make/Break ratio may be selected by connecting pin 9 to either the  $V_{DD}$  or GND supply. Table 1 indicates the two popular ratios from which the user can choose.

Table 1 Make/Break ratio selection

| Input to Make/Break Pin                | Pulse Output         |                     |  |

|----------------------------------------|----------------------|---------------------|--|

| V <sub>DD</sub> (Pin 1)<br>GND (Pin 6) | · MAKE<br>39%<br>33% | BREAK<br>61%<br>67% |  |

# Mute Output (Pin 10)

The Mute output consists of an open-drain N-channel transistor. It provides the logic necessary to mute the receiver while the telephone line is being pulsed. A typical method of interfacing this output pin is shown in the System Configuration diagram.

# On-Hook/Test (Pin 15)

The "Test" or "On-Hook" input of the LR40981A has a pull-up to the positive supply. A  $V_{\rm DD}$  input or allowing the pin to float puts the circuit into On-Hook or test mode, while a GND input puts it into Off-Hook or normal Mode. Any digits to be tested while in On-Hook/Test mode, however, must be entered while the circuit is Off-Hook.

When Off-Hook, the LR40981A will accept key inputs and outpulse the digits in normal fashion. When the last digit has been outpulsed, the oscillator is disabled and the circuit stands by for additional inputs.

Switching the LR40981A to On-Hook while it is outpulsing causes the remaining digits to be outpulsed at 100 times the normal rate (the M/B ratio is then 50/50). This feature provides a means of

T-75-07-07

rapidly testing the device and is also an efficient way to reset the circuitry. When the outpulsing in this mode, which can take up to 300ms, is completed, the circuit is de-activated and will require only the current necessary to sustain the memory and Power-Up-Clear detect circuitry (refer to the DC Characteristics).

Upon returning to Off-Hook mode, a negative transistion on the Mute Output will insure that the speech network is connected to the line. If the first key entry is either a \* or #, the number sequence stored on-chip will be outpulsed. Any other valid key entries will clear the memory and outpulse the new number sequence.

# Pulse Output (Pin 16)

The Pulse Output is an open-drain N-channel transistor designed to drive an external bipolar transistor. These transistors would normally be used to pulse the telephone line by controlling the loop current through the network.

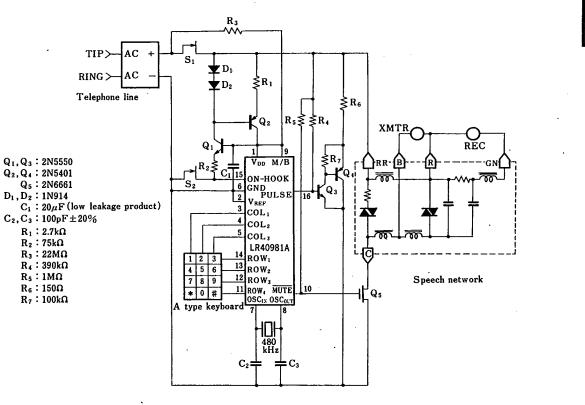

# Typical Application

The System Configuration schematic diagram shows one method which can be used to interface the pulse dialer with a telephone line. In the approach shown, the pulse dialer circuitry is in series with the speech network.

Some type of current source is needed that will provide a high impedance to the telephone line and deliver sufficient current to power the LR40981A  $(>150\mu\text{A})$ . The current source shown is constructed with two components, Q2 and R1. The current is regulated by the negative feedback provided by R1 to the gate of Q2. Several other implementations can be considered, such as a constant current diode or a configuration using bipolar transistors

The purpose of transistor Q1 is to take the place of an additional hookswitch contact. When S1 closes, Q1 is turned on and HKS/T (Pin 15) is pulled to  $V_{DD}$ . This puts the LR40981A into normal mode so that it is ready to accept key inputs.

When going On-Hook, S1 is opened, causing Q1 to be turned off. An on-chip resistor pulls pin 15 to V<sub>DD</sub> and the current source is disabled. The purpose of D1 is to limit any reverse current flow through the current source. A large-value resistor, R3, permits the small amount of current needed to maintain the LR40981A memory.

To return to Off-Hook mode, S1 is closed, causing Q1 to be turned on and the HKS/T pin to be tied to GND. The Pulse and Mute outputs drive external transistors to perform the outpulsing function. The receiver is connected through transistor Q6 to the speech network. Mute causes the transistor to be held on until outpulsing begins. When Mute goes low, the receiver is removed from the speech network. The pops caused by breaking the line are then isolated from the receiver. The Pulse output drives transistors Q3 and Q5 to make and break the line until the digit has been completely outpulsed. Mute then goes high again, returning the receiver to the speech network.

# **Timing Diagram**

154

LR40981A

**Test Circuit**

T-75-07-07

# System Configuration Example

SHARP

155