# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

#### **Advance Information**

## DUAL TUNABLE LINEAR PHASE LOW-PASS SAMPLED DATA FILTERS

The MC145415 is sampled data, switched capacitor filter IC intended to provide band limiting and signal restoration filtering. It is capable of operating from either a single or split power supply and can be powered-down when not in use. Included on the IC are two uncommitted comparators for use elsewhere in the system.

- Two Linear Phase 5th Order Low-Pass Filters

- Low Operating Power Consumption 20 mW (Typical)

- CMOS Compatible Inputs Using VDG Pin

- Two Comparators Available to Reduce Component Count

- Useful in High Speed Data Modern Applications

- Pass-Band Edges Tunable With Clock Frequency from 1.25 kHz to 10 kHz

##

This document contains information on a new product. Specifications and information herein are subject to change without notice

### MC145415

#### **CMOS LSI**

(LOW-POWER COMPLEMENTARY MOS)

DUAL TUNABLE LINEAR PHASE LOW-PASS SAMPLED DATA FILTERS

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{OUI}$  be constrained to the range  $V_{SS} \leq (V_{in}$  or  $V_{OUI}) \leq V_{DD}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either VSS or VDD).

#### MAXIMUM RATINGS (VSS=0)

| Rating                                        | Symbol                           | Value                        | Unit |

|-----------------------------------------------|----------------------------------|------------------------------|------|

| DC Supply Voltage                             | V <sub>DD</sub> -V <sub>SS</sub> | -0.5 to 18                   | ٧    |

| Input Voltage, All Pins                       | V <sub>in</sub>                  | -0.5 to V <sub>DD</sub> +0.5 | V    |

| DC Current Drain per Pin (Excluding VDD, VSS) | 1                                | 10                           | mΑ   |

| Operating Temperature Range                   | TA                               | - 40 to 85                   | °C   |

| Storage Temperature Range                     | T <sub>stg</sub>                 | - 65 to 150                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter         |                                  | Min | Тур | Max | Unit |

|-------------------|----------------------------------|-----|-----|-----|------|

| DC Supply Voltage | V <sub>DD</sub> -V <sub>SS</sub> | 4.5 | 5   | 16  | V    |

| Clock Frequency*  | CLK                              | 50  | 128 | 400 | kHz  |

<sup>\*</sup>Filter frequency response may degrade slightly as clock frequency is increased above 200 kHz.

#### DIGITAL ELECTRICAL CHARACTERISTICS ( $V_{DD} = 10 \text{ V}, V_{SS} = 0 \text{ V}, V_{AG} = V_{DD}/2, T_{A} = -40 \text{ to } 85^{\circ}\text{C}$ )

| Characteristic                            | Symbol          | Min                                                        | Max                                                        | Unit |

|-------------------------------------------|-----------------|------------------------------------------------------------|------------------------------------------------------------|------|

| Operating Current                         | DD <sup>I</sup> | _                                                          | 4                                                          | mΑ   |

| Input Capacitance                         | C <sub>in</sub> | _                                                          | 10                                                         | pF   |

| Input Low Voltage (Pins 10, 11)           | V <sub>IL</sub> | -                                                          | V <sub>DG</sub> + 0.3 (V <sub>DD</sub> - V <sub>DG</sub> ) | ٧    |

| Input High Voltage (Pins 10, 11)          | ViH             | V <sub>DD</sub> = 0.3 (V <sub>DD</sub> = V <sub>DG</sub> ) | -                                                          | V    |

| Input Leakage Current (Pins 10, 11)       | l <sub>IL</sub> | _                                                          | 2.5                                                        | μΑ   |

| V <sub>DG</sub> Reference Voltage (Pin 9) | V <sub>DG</sub> | V <sub>SS</sub>                                            | V <sub>DD</sub> -4.5                                       | ٧    |

ANALOG ELECTRICAL CHARACTERISTICS (VDD = 12 V, VSS = 0, VAG = VDD/2,  $T_A = -40$  to 85°C)

| Characteristic                                                                                                                                                                                                                                                                                  |                                                                            | Symbol           | Min               | Тур           | Max                | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|-------------------|---------------|--------------------|----------|

| Input Current                                                                                                                                                                                                                                                                                   | A <sub>in</sub> , B <sub>in</sub>                                          | lin              |                   | ±0.00001      | ± 10               | μA       |

| Input Current                                                                                                                                                                                                                                                                                   | V <sub>AG</sub>                                                            | l <sub>in</sub>  | -                 | ±0.00001      | ± 50               | μA       |

| AC Input Impedance (1 kHz)                                                                                                                                                                                                                                                                      | A <sub>in</sub> , B <sub>in</sub>                                          | Z <sub>in</sub>  | -                 | 2             | -                  | MΩ       |

| Input Common Mode Voltage Range                                                                                                                                                                                                                                                                 | A <sub>in</sub> , B <sub>in</sub> , + A, - A, + B, - B                     | V <sub>ICR</sub> | 2.0               | -             | 10.0               | V        |

| Input Offset Current                                                                                                                                                                                                                                                                            | + A to - A, + B to - B                                                     | l <sub>ID</sub>  | -                 | ± 10          | -                  | nA ·     |

| Input Bias Current                                                                                                                                                                                                                                                                              | + A, - A, + B, - B                                                         | Iв               | _                 | ± 0.10        | ± 1.0              | nA       |

| Input Offset Voltage + A to - A, + B to - B                                                                                                                                                                                                                                                     |                                                                            | VID              | -                 | ± 10          | ± 70               | mV       |

| Output Voltage Range (R <sub>L</sub> = 20 kΩ to V <sub>AG</sub> , R <sub>B</sub> = $\infty$ ) (R <sub>L</sub> = 800 $\Omega$ to V <sub>AG</sub> , R <sub>B</sub> = 1.8 kΩ to V <sub>DD</sub> ) (R <sub>L</sub> = 600 $\Omega$ to V <sub>AG</sub> , R <sub>B</sub> = 1.6 kΩ to V <sub>DD</sub> ) | A <sub>out</sub> , B <sub>out</sub>                                        | VOR              | 1.5<br>2.5<br>3.0 |               | 10.5<br>9.0<br>8.3 | V        |

| Small Signal Output Impedance (1 kHz)                                                                                                                                                                                                                                                           | A <sub>out</sub><br>B <sub>out</sub>                                       | Z <sub>o</sub>   | -                 | 50<br>50      | -<br>-             | Ω        |

| Output Current<br>(V <sub>O</sub> = 10.5 V)<br>(V <sub>O</sub> = 1.5 V)                                                                                                                                                                                                                         | A <sub>out</sub> , B <sub>out</sub><br>A <sub>out</sub> , B <sub>out</sub> | loh<br>lor       | - 200<br>5        | - 400<br>7.5  | _                  | μA<br>mA |

| Comparator Output Current ( $V_Q = 9.5 \text{ V}$ ) ( $V_Q = 0.5 \text{ V}$ )                                                                                                                                                                                                                   | A0, B0                                                                     | IOH<br>IOL       | - 1.1<br>3.0      | - 2.25<br>8.8 | _<br>_             | mA       |

#### $\textbf{FILTER A SPECIFICATIONS} \text{ ($V_{DD} - V_{SS} = 12$ V, Clock = 153.6$ kHz, $V_{in} = 0$ dBm0, full scale = +3$ dBm0, 0.875$ V p-p, $T_{A} = -40$ to $85°C1$ and $T_{A} = -40$ to $85°C1$ a$

| Characteristic                                               | Min  | Тур    | Max    | Unit  |

|--------------------------------------------------------------|------|--------|--------|-------|

| Gain (300 Hz)                                                | 17   | 18     | 19     | dB    |

| Responses (Ref. 300 Hz)                                      |      |        |        | dВ    |

| 2400 Hz                                                      | -3.6 | - 3.0  | -2.4   |       |

| 4800 Hz                                                      | - 16 | - 13.8 | - 12.8 |       |

| Idle Noise (Ain = V <sub>AG</sub> , Ref. to 600 Ω)           |      | 13     | 24     | dBrnc |

| Dynamic Range (Full Scale Output/Idle Noise)                 | 76   | 87     | _      | dB    |

| Deviation From Linear Phase dc to 2400 Hz                    | -    | 2.5    | _      | deg   |

| Power Supply Rejection Ratio (VDD=12 V +0.1 VRMS @ 1 kHz)    |      | 36     | _      | dB    |

| Crosstalk (Ain = VAG, Bin = 0 dBm0, Output at Aout at 3 kHz) | -    | 76     | _      | dB    |

#### $\textbf{FILTER B SPECIFICATIONS} \ \, (V_{DD} - V_{SS} = 12 \ \, V, \ \, \text{Clock} = 153.6 \ \, \text{kHz}, \ \, V_{in} = 0 \ \, \text{dBm0}, \ \, \text{full scale} = +3 \ \, \text{dBm0}, \ \, 7 \ \, \text{V p-p, T}_{A} = -40 \ \, \text{to } 85^{\circ}\text{C})$

| Characteristic                                                 | Min  | Тур    | Max    | Unit  |

|----------------------------------------------------------------|------|--------|--------|-------|

| Gain (300 Hz)                                                  | -0.7 | ± 0.15 | +0.7   | dB    |

| Response (Ref. 300 Hz)                                         |      |        |        | ₫B    |

| 2400 Hz                                                        | -3.6 | - 3.0  | - 2.4  |       |

| 4800 Hz                                                        | - 16 | - 14.1 | - 12.8 |       |

| Idle Noise (B <sub>in</sub> = V <sub>AG</sub> , Ref. to 600 Ω) |      | 9      | 24     | dBrnc |

| Dynamic Range (Full Scale Output/Idle Noise)                   | 76   | 91     | _      | dB    |

| Deviation From Linear Phase (dc to 2400 Hz)                    |      | 2.5    | _      | deg   |

| Power Supply Rejection Ratio (VDD = 12 V + 0.1 VRMS @ 1 kHz)   | _    | 36     |        | dB    |

| Crosstalk (Bin = VAG, Ain = 0 dBm0 @ 2 kHz, Output at Bout)    | _    | 76     | _      | dB    |

SWITCHING CHARACTERISTICS (VDD - VSS = 12 V, TA = -40 to 85°C)

| Characteristics                | Symbol           | Min | Тур | Max | Units |

|--------------------------------|------------------|-----|-----|-----|-------|

| Input Rise Time (Pin 10)       | <sup>†</sup> TLH | -   | _   | 4   | μS    |

| Input Fall Time (Pin 10)       | tTHL             | _   | _   | 4   | μS    |

| Pulse Width (Pin 10)           | twH              | 200 | _   |     | ns    |

| Clock Pulse Frequency (Pin 10) | fCL              | 50  | _   | 400 | kHz   |

| Clock Duty Cycle (Pin 10)      | _                | 40  | -   | 60  | %     |

#### **FUNCTIONAL DESCRIPTION OF PINS**

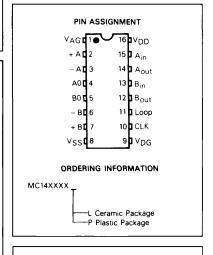

#### **VDD (PIN 16)**

Positive supply pin.

#### VSS (PIN 8)

This is the most negative supply pin.

#### VAG, ANALOG GROUND (PIN 1)

This pin should be held at approximately (VDD - VSS)/2. All analog inputs and outputs are referenced to this pin.

#### + A (PIN 2)

Non-inverting input of comparator A.

#### - A (PIN 3)

Inverting input of comparator A.

#### A0 (PIN 4)

Output of comparator A. This is a standard 'B' series CMOS output.

#### B0 (PIN 5)

Output of comparator B. This is a standard 'B' series CMOS output.

#### - B (PIN 6)

Inverting input of comparator B.

#### + B (PIN 7)

Non-inverting input of comparator B.

#### VDG, DIGITAL GROUND (PIN 9)

This pin is logic ground reference for the CLK and LOOP pins.

#### CLK, CLOCK (PIN 10)

This is the clock input that determines the location of the cutoff frequency of the filters as given below:

-3 dB frequency = fCLK ÷ 64

#### LOOP (PIN 11)

When this pin is high, the input to filter A is disconnected from the pad and shorted to the filter B output pin. With this pin low, the loop back mode is disabled.

#### Bout, LOW-PASS FILTER B OUTPUT (PIN 12)

This is the output from Filter B.

#### Bin, LOW-PASS FILTER B INPUT (PIN 13)

This is the input to filter B.

#### A<sub>out</sub>, LOW-PASS FILTER A OUTPUT (PIN 14)

This pin is the output from Filter A.

#### Ain, LOW-PASS FILTER A INPUT (PIN 15)

This is the input to Filter A.

NOTE: VAG is a high-impedance input.

#### FILTER DESCRIPTION

#### FILTER A DESCRIPTION

Filter A of the MC145415 is a 5-pole tunable linear phase low-pass filter operation at a sampling rate determined by the clock. The break frequency, which is a function of the clock, is calculated by dividing the input clock frequency by 64. With a 128 kHz clock, the band limiting frequency is 2 kHz. By dividing the clock in half to 64 kHz the band limiting frequency is cut in half to 1 kHz. Likewise, by doubling the clock, the cutoff point with double in frequency. The clock frequency can be varied from 50 kHz to 400 kHz. Filter A, unlike filter B, has a gain of 18 dB. Because the MC145415 is a switch capacitance filter, the sampled output signal will have switching components present near multiples of the switching frequency and inputs to these filters should be band-limited to under ~ 3/4 fCLK to prevent aliasing.

#### FILTER B DESCRIPTION

Filter B in the MC145415 consists of a 5-pole tunable linear phase low-pass filter operating at a sampled rate determined by the clock. Filter B is functionally similar to filter A, except filter B has unity gain.

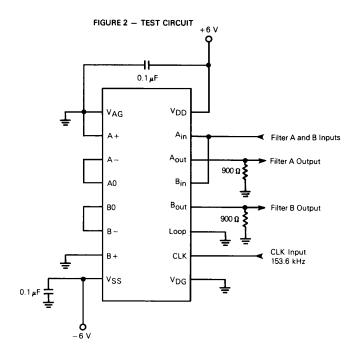

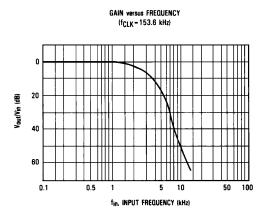

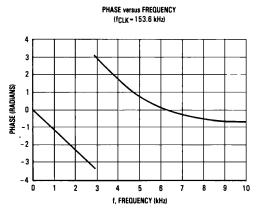

FIGURE 1 - FILTER A AND B LOW-PASS CHARACTERISTICS

NOTES: 1. Break frequency is equal to the clock frequency + 64.

2. Figure 1 illustrates Filter B performance.

Filter A would be 18 dB higher.