MT8920B ST-BUS Parallel Access Circuit

S Parallel Access Circuit

Data Sheet

August 2005

#### **Features**

- High speed parallel access to the serial ST-BUS

- Parallel bus optimized for 68000  $\mu P$  (mode 1)

- Fast dual-port RAM access (mode 2)

Access time: 120 nsec

- Parallel bus controller (mode 3) no external controller required

- Flexible interrupt capabilities two independent/programmable interrupt sources with auto-vectoring

- Selectable 24 and 32 channel operation

- Programmable loop-around modes

- Low power CMOS technology

### Applications

- Parallel control/data access to T1/CEPT digital trunk interfaces

- Digital signal processor interface to ST-BUS

- Computer to Digital PABX link

- · Voice store and forward systems

- Interprocessor communications

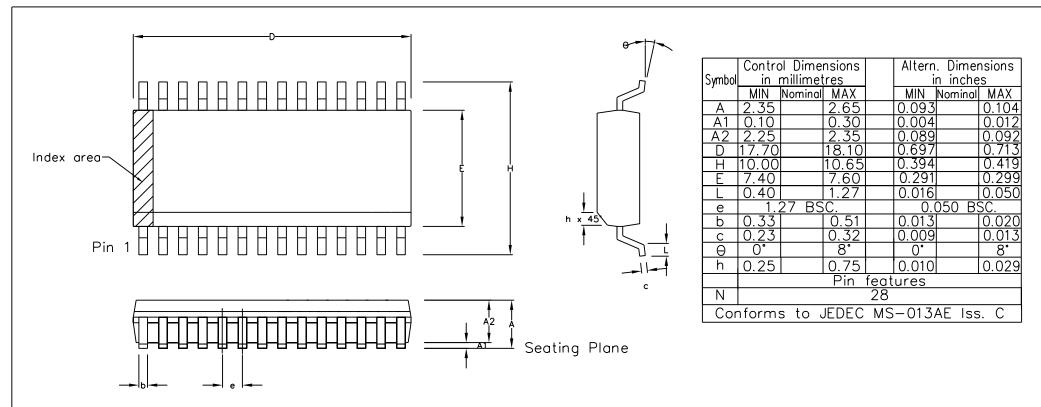

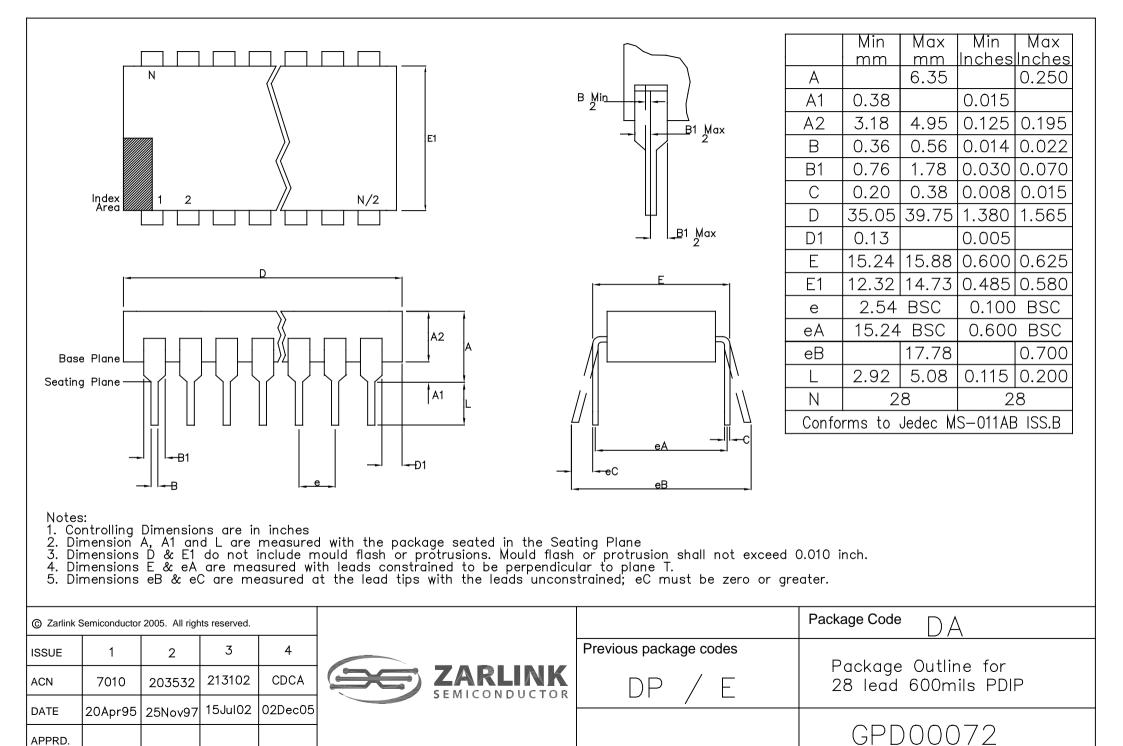

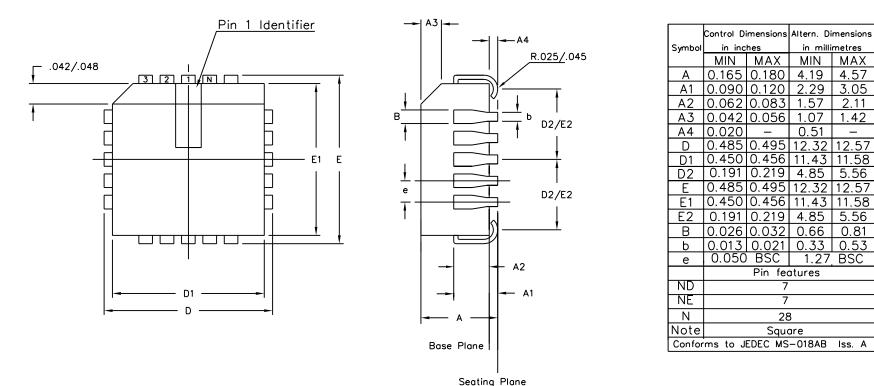

| Ordering Information |              |             |  |  |  |  |  |

|----------------------|--------------|-------------|--|--|--|--|--|

| MT8920BE             | 28 Pin PDIP  | Tubes       |  |  |  |  |  |

| MT8920BP             | 28 Pin PLCC  | Tubes       |  |  |  |  |  |

| MT8920BS             | 28 Pin SOIC  | Tubes       |  |  |  |  |  |

| MT8920BE1            | 28 Pin PDIP* | Tubes       |  |  |  |  |  |

| MT8920BP1            | 28 Pin PLCC* | Tubes       |  |  |  |  |  |

| MT8920BS1            | 28 Pin SOIC* | Tubes       |  |  |  |  |  |

| MT8920BPR1           | 28 Pin PLCC* | Tape & Reel |  |  |  |  |  |

| *PB Free Matte Tin   |              |             |  |  |  |  |  |

| -                    | 40°C to 85°C |             |  |  |  |  |  |

# Description

The ST-BUS Parallel Access Circuit (STPA) provides a simple interface between Zarlink's ST-BUS and parallel system environments.

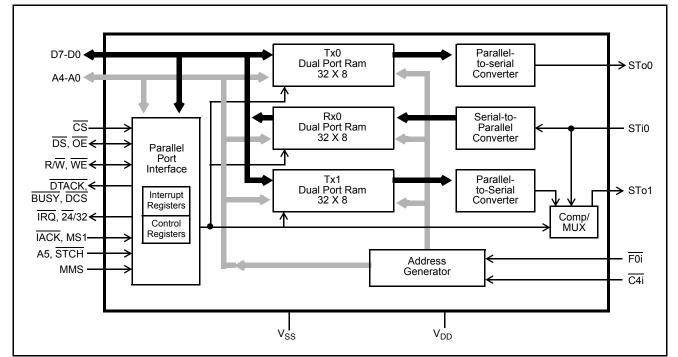

#### Figure 1 - Functional Block Diagram

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2002-2005, Zarlink Semiconductor Inc. All Rights Reserved.

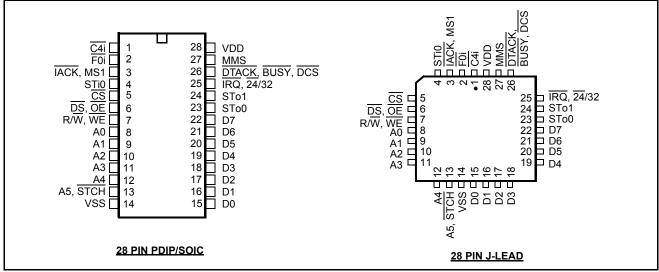

#### Figure 2 - Pin Connections

# **Pin Description**

| Pin # | Name  | Description <sup>‡</sup>                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

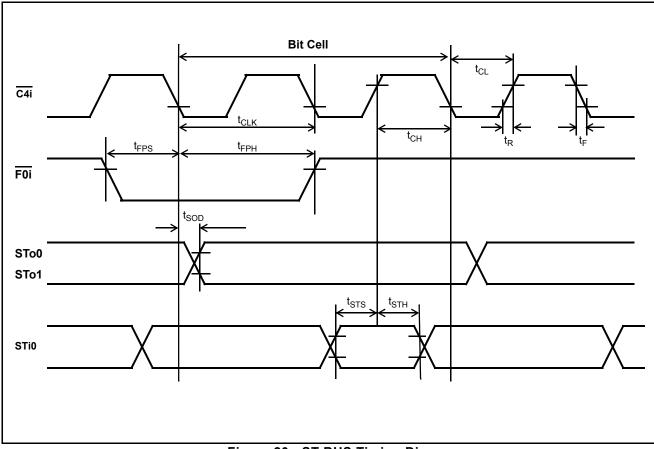

| 1     | C4i   | <b>4.096 MHz Clock.</b> The ST-BUS timing clock used to establish bit cell boundaries for the serial bus.                                                                                                                                                                           |  |  |  |  |  |

| 2     | F0i   | <b>Framing Pulse.</b> A low going pulse used to synchronize the STPA to the 2048 kbit/s ST-BUS stream. The first falling edge of C4i subsequent to the falling edge of F0i identifies the start of a frame.                                                                         |  |  |  |  |  |

| 3     | IACK  | <b>nterrupt Acknowledge (Mode 1).</b> This active low input signals that the current bus cycle is an interrupt vector fetch cycle. Upon receiving this acknowledgement, the STPA will butput a user-programmed vector number on $D_0 - D_7$ indicating the source of the interrupt. |  |  |  |  |  |

|       | MS1   | <b>Mode Select 1 (Mode 2,3).</b> This input is used to select the device operating modes. A low applied to this pin will select mode 3 while a high will select mode 2. (Refer to Table 1.)                                                                                         |  |  |  |  |  |

| 4     | STi0  | ST-BUS Input 0. This is the input for the 2048 kbit/s ST-BUS serial data stream.                                                                                                                                                                                                    |  |  |  |  |  |

| 5     | CS    | Chip Select. This active low input is used to select the STPA for a parallel access .                                                                                                                                                                                               |  |  |  |  |  |

| 6     | DS    | <b>Data Strobe (Mode 1).</b> This active low input indicates to the STPA that valid data is on the data bus during a write operation or that the STPA must output valid data on the data bus during a read operation.                                                               |  |  |  |  |  |

|       | OE    | Output Enable (Mode 2). This active low input enables the data bus driver outputs.                                                                                                                                                                                                  |  |  |  |  |  |

|       | OE    | <b>Output Enable (Mode 3).</b> This active low output indicates that the selected device is to be read and that the data bus is available for data transfer.                                                                                                                        |  |  |  |  |  |

| 7     | R/W   | <b>Read/Write (Mode 1,2).</b> This input defines the data bus transfer as a read ( $R/\overline{W} = 1$ ) or a write ( $R/W= 0$ ) cycle.                                                                                                                                            |  |  |  |  |  |

|       | WE    | Write Enable (Mode 3). This active low output indicates the data on the data bus is to be written into the selected location of an external device.                                                                                                                                 |  |  |  |  |  |

| 8-12  | A0-A4 | Address Bus (Mode 1,2). These inputs are used to select the internal registers and two-port memories of the STPA.                                                                                                                                                                   |  |  |  |  |  |

|       | A0-A4 | Address Bus (Mode 3). These address outputs are generated by the STPA and reflect the position in internal RAM where the information will be fetched from or stored in. Addresses generated in this mode are used to access external devices for direct memory transfer.            |  |  |  |  |  |

# Pin Description (continued)

| Pin # | Name            | Description <sup>‡</sup>                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 13    | A5              | Address Bit A5 (Mode 1). This input is used to extend the address range of the STPA. A5 selects internal registers when high and Tx/Rx RAM's when low.                                                                                                                                                                                                                                    |  |  |  |  |  |

|       | A5              | Address Bit A5 (Mode 2). This input is used to extend the address range of the STPA. A5 selects Tx0/Rx0 RAM's when low and Tx1/Rx0 RAM's when high.                                                                                                                                                                                                                                       |  |  |  |  |  |

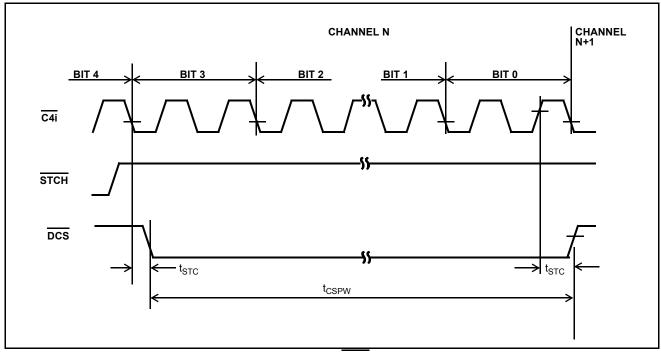

|       | STCH            | <b>Start of Channel (Mode 3).</b> This signal is a low going pulse which indicates the start of an ST-BUS channel. The pulse is four bits wide and begins at the start of each valid channel.                                                                                                                                                                                             |  |  |  |  |  |

| 14    | V <sub>SS</sub> | Ground.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 15-22 | D0-D7           | <b>Bidirectional Data Bus.</b> This bus is used to transfer data to or from the STPA during a write or read operation.                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 23    | STo0            | <b>ST-BUS Output 0.</b> This output supplies the output ST-BUS 2048 kbit/s serial data stream from Tx0 two-port RAM.                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| 24    | STo1            | <b>ST-BUS Output 1.</b> In modes 1 and 2 this output supplies the output ST-BUS 2048 kbit/s serial lata stream from Tx1 two-port RAM. In mode 3, information arriving at STi0 is output here with one frame delay.                                                                                                                                                                        |  |  |  |  |  |

| 25    | IRQ             | <b>Interrupt Request (Mode 1).</b> This open drain output, when low, indicates when an interrupt condition has been raised within the STPA.                                                                                                                                                                                                                                               |  |  |  |  |  |

|       | 24/32           | <b>24 Channel/32 Channel Select (Mode 2,3).</b> This input is used to select the channel configuration in modes 2 and 3. A low applied to this pin will select a 24 (T1) channel mode while a high will select a 32 (CEPT) channel mode.                                                                                                                                                  |  |  |  |  |  |

| 26    | DTACK           | <b>Data Transfer Acknowledge (Mode 1).</b> This open drain output is supplied by the STPA to acknowledge the completion of data transfers back to the $\mu$ P. On a read of the STPA, DTACK low indicates that the STPA has put valid data on the data bus. On a write, DTACK low indicates that the STPA has completed latching the $\mu$ P's data from the data bus.                    |  |  |  |  |  |

|       | BUSY            | <b>BUSY (Mode 2).</b> This open drain output signals that the controller and the ST-BUS are accessing the same location in the dual-port RAM's. It is intended to delay the controller access until after the ST-BUS completes its access.                                                                                                                                                |  |  |  |  |  |

|       | DCS             | <b>Delayed Chip Select (Mode 3).</b> This low going pulse, which is four bit cells long, is active during the last half of a valid channel. This signal is used to daisy-chain together two STPA's in mode 3 that are accessing devices on the same parallel data bus.                                                                                                                    |  |  |  |  |  |

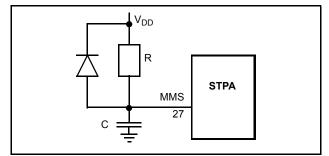

| 27    | MMS             | <b>Master Mode Select (Reset).</b> This Schmitt trigger input selects between either mode 1 (MMS = 1), or modes 2and 3 (MMS = 0). If MMS is pulsed low in Mode 1 operation the control and interrupt registers will be reset. (Refer to Table 1.) During power-up, the time constant of the reset circuit (see Fig. 8) must be a minimum of five times the rise time of the power supply. |  |  |  |  |  |

| 28    | V <sub>DD</sub> | Power Supply Input. (+5V).                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Mode | MMS | MS1 | Mode of<br>Operation      | Function                                                                                                                                                                                                                                                                                                                                                  |

|------|-----|-----|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 1   | N/A | μΡ<br>Peripheral<br>Mode  | The STPA provides parallel-to-serial and serial-to-parallel conversions through a 68000-type interface. Two Tx RAMs and one Rx RAM are available along with full interrupt capability. 32 channel or 24 channel support is available. Control Register 1, bit $D_5$ (RAMCON) = 0 for 32 channel operation and $D_5$ (RAMCON)= 1 for 24 channel operation. |

| 2    | 0   | 1   | Fast RAM<br>Mode          | The STPA provides a fast access interface to Tx0, Tx1 and Rx0 RAMs. This mode is intended for full parallel support of 24 channel T1/ESF trunks and 32 channel CEPT trunks. Input 24/32 (pin 25) = 0 for 24 channel operation, input 24/32 (pin 25) = 1 for 32 channel operation.                                                                         |

| 3    | 0   | 0   | Bus<br>Controller<br>Mode | The STPA will synchronously drive the parallel bus using the address generator and provide all data transfer signals. This mode is intended to support 24 or 32 channel devices in the absence of a parallel bus controller. Input 24/32 (pin 25) = 0 for 24 channel operation, input $\frac{24}{32}$ (pin 25) = 1 for 32 channel operation.              |

Table 1. STPA Modes of Operation

# **Functional Description**

The STPA (ST-BUS Parallel Access) device provides a simple interface between Zarlink's ST-BUS and parallel system environments. The ST-BUS is a synchronous, time division, multiplexed serial bussing scheme with data streams operating at 2048 kbit/s. The ST-BUS is the primary means of access for voice, data and control information to Zarlink's family of digital telecommunications components, including North American and European digital trunk interfaces, ISDN U and S digital line interfaces, filter codecs, rate adapters, etc. The STPA provides several modes of operation optimized according to the type of information being handled.

For interfacing parallel data and control information to the ST-BUS, such as signalling and link control for digital trunks, the STPA provides a  $\mu$ P access mode (Mode 1), and looks like a 68000 type peripheral. In this mode, the device provides powerful interrupt features, useful in monitoring digital trunk or line status (i.e., synchronization, alarms, etc.) or for setting up message communication links between microprocessors.

To interface high speed data or multi-channel voice/ data to the ST-BUS for switching or transmission, the STPA has a high speed synchronous access mode (Mode 2) and acts like a fast RAM. For voice storage and forward, bulk data transfer, data buffering and other similar applications, the STPA has a controllerless mode (Mode 3) in which it provides address and control signals to the parallel bus This is useful for performing direct transfers to the ST-BUS from external devices such as a RAM buffer.

The STPA is a two port device as shown in the functional block diagram in Figure 1. The parallel port provides direct access to three dual port RAM's, two transmit and one receive. The address, data

and control busses are used to communicate between the RAM's and a parallel environment.

Two parallel-to-serial converters, and one serial-to-parallel converter interface the dual port RAM's to the ST-BUS port of the STPA. This port consists of two serial output streams and one serial input stream operating at 2048 kbit/s. This configuration of two outputs and one input was designed to allow a single STPA to form a complete control interface to Zarlink's digital trunk interfaces (MT8976, MT8978 and MT8979) which have two serial input and one serial output control streams.

ST-BUS clocking circuitry, address generator and various control and interrupt registers complete the STPA's functionality.

#### Modes of Operation

The three basic modes of operation,  $\mu P$  Peripheral Mode (Mode 1), Fast RAM Mode (Mode 2) and Bus Controller Mode (Mode 3) are selected using two external input pins. These inputs are MMS and MS1 and are decoded as shown in Table 1. Whenever MMS=1 the device resides in Mode 1. In this mode, MS1 pin is unavailable and is used for a different function.

When MMS=0, Modes 2 or 3 are selected as determined by input MS1. If MS1=1, Mode 2 is selected and if MS1=0, Mode 3 is selected.

Each of the modes of the STPA provides a different pinout to ease interfacing requirements of different parallel environments. These are shown in Figure 3 below. In  $\mu$ P Peripheral Mode the device uses interface signals consistent with a 68000-type  $\mu$ P bus. Mode 2, Fast RAM Mode, uses signals typical of standard RAM type interfaces. Mode 3 interface signals are very similiar to Mode 2 signals except that the address and control signals are supplied as outputs by the STPA.

| μP Peripheral Mode #1                                                               | Fast RAM Mode #2                                                                                                 | Bus Controller Mode #3                                                             |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

|                                                                                     |                                                                                                                  | <u>C4i</u> □ 1 28 □ VDD<br>F0i □ 2 27 □ <u>MMS</u>                                 |

| <u>F0i</u> 2 27 <u>MMS</u><br>IACK 3 26 <u>DTA</u> CK<br>S <u>Ti0</u> 4 25 □ IRQ    | F0i       2       27       MMS         MS1       3       26       BUSY         STi0       4       25       24/32 | F0i □ 2 27 □ <u>MMS</u><br>MS1 □ 3 26 □ <u>DC</u> S<br>S <u>Ti0</u> □ 4 25 □ 24/32 |

| CS         5         24         STo1           DS         6         23         STo0 | CS         5         24         STo1           OE         6         23         STo0                              | <u>CS</u> ☐ 5 24 ☐ STo1<br><u>OE</u> ☐ 6 23 ☐ STo0                                 |

| R/W 7 22 D7<br>A0 8 21 D6<br>A1 9 20 D5                                             | R/W 7 22 D7<br>A0 8 21 D6<br>A1 9 20 D5                                                                          | WE 7 22 D7<br>A0 8 21 D6<br>A1 9 20 D5                                             |

| A1 9 20 D5<br>A2 10 19 D4<br>A3 11 18 D3                                            | A1 9 20 05<br>A2 10 19 04<br>A3 11 18 03                                                                         | A1 9 20 D5<br>A2 10 19 D4<br>A3 11 18 D3                                           |

| A4 12 17 D2<br>A5 13 16 D1                                                          | A4 12 17 D2<br>A5 13 16 D1                                                                                       | A4 12 17 D2<br>STCH 13 16 D1                                                       |

| VSS 14 15 D0                                                                        | VSS 14 15 D0                                                                                                     | VSS 14 15 D0                                                                       |

Figure 3 - Modes 1, 2, 3 Pin Connections

#### 24/32 Channel Operation

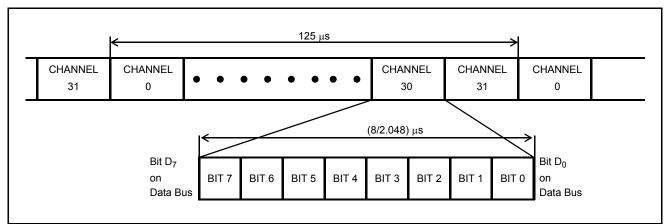

The STPA may be configured to operate as a 32 channel or 24 channel device. This feature, which is available in all three modes of operation, is particularly useful in applications involving data access to CEPT and T1 digital trunk interfaces.

When used as a data interface to Zarlink's CEPT digital trunks, the STPA maps the 32 consecutive bytes of each dual port memory directly to ST-BUS channels 0-31. This is performed by the address generator shown in the functional block diagram (see Figure 1). Figures 4 c & d show the relationship between relative dual port RAM locations and corresponding ST-BUS channels, for both input and output serial streams, when the STPA is configured as a 32 channel device.

When used as a data interface to Zarlink's T1 trunk devices, however, only the first 24 consecutive RAM locations are mapped to 24 of the 32 ST-BUS channels. This mapping follows a specific pattern which corresponds with the data streams used by Zarlink's T1 products. Instead of a direct correlation (as in 32 channel operation), the 24 consecutive RAM locations are mapped to the ST-BUS with every fourth channel, beginning at channel 0, set to FF<sub>16</sub> (ie. channel 0, 4, 8, 12, 16, 20, 24 and 28). Figures 4 a & b show the relationship between RAM locations and ST-BUS channel configuration. This feature allows the STPA to be interfaced directly to Zarlink's T1 trunk family.

When the STPA is operated in Mode 1, 24 and 32 channel configurations are selected using bit  $D_5$  (RAMCON) in Control Register 1.  $D_5 = 0$  selects 32 channel operation and  $D_5 = 1$  selects 24 channel operation. When the STPA is operated in Modes 2 or 3, however, the channel configuration is done using input 24/32 (pin 25). When 24/32 = 1 the device uses all 32 channels and when 24/32 = 0 it uses 24.

#### **Dual Port RAMS**

Each of the three serial ST-BUS streams is interfaced to the parallel bus through a 32 byte dual port RAM. This allows parallel bus accesses to be performed asynchronously while accesses at the ST-BUS port are synchronous with ST-BUS clock. As with any dual port RAM interface between two asynchronous systems, the possibility of access contention exists. The STPA minimizes this occurrence by recognizing contention only when accesses are performed at the same time for the same 8-bit cell within the dual port RAM's. Furthermore, the probability of contention is lessened since ST-BUS accesses require only the last half cycle of  $\overline{C4i}$  of every channel. When contention does occur, priority is always given to the ST-BUS access.

The STPA indicates this contention situation in a different manner for Modes 1 and 2. In Mode 1, the contention is masked by virtue of the "handshaking" method used to transfer data on this 68000-type interface. Data Strobe (DS) and Data Transfer Acknowledge (DTACK) control the exchange. If contention should occur the device will delay returning DTACK and thus stretch the bus cycle until the  $\mu$ P access can be completed.

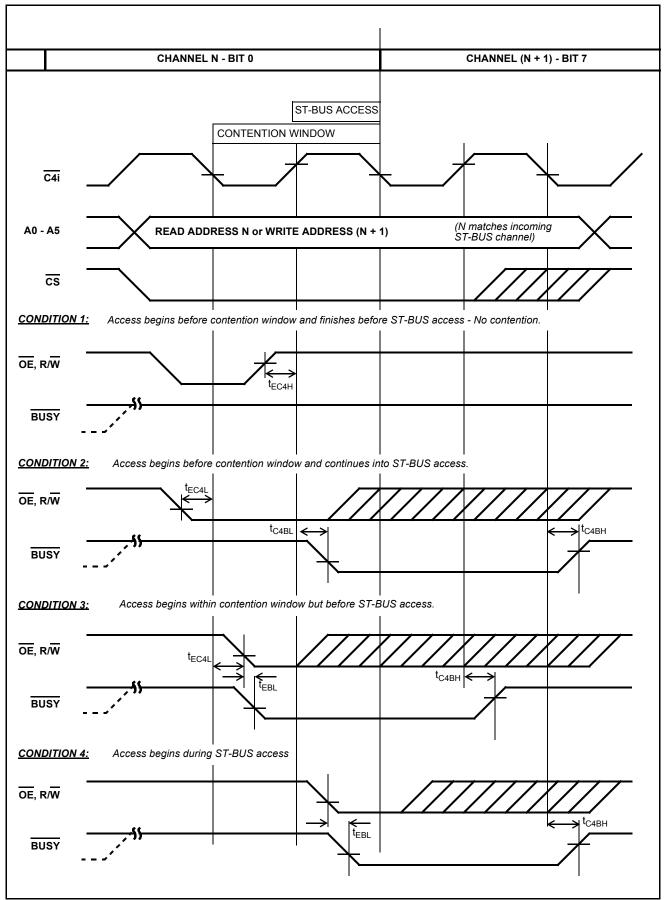

In Mode 2, if access is attempted during a "contention window" the STPA will supply the BUSY signal to delay the start of the bus cycle. This "contention window" is defined as shown in Figure 16. The window exists during the last cycle of C4i clock in each channel timeslot. Although ST-BUS access is only required during the last half of this clock period, the "contention window" exists for the entire clock period since a parallel access occurring just prior to an ST-BUS access will not complete before the ST-BUS access begins. Figure 16 further shows four possible situations that may occur when parallel accesses are attempted in and around the "contention window". Condition 1 indicates that an access occurring prior to the contention window but lasting into the first half of it will complete normally with no contention arbitration. If the access should extend past the first half of the contention window and into the ST-BUS access period, the BUSY signal will be generated. Conditions 3 and 4 show accesses occurring inside the contention window. These accesses will result in BUSY becoming active immediately after the access is initiated and remaining active as shown in Figure 16.

Access contention is non-existent in Mode 3 since the parallel bus signals, driven by the STPA, are synchronized to the ST-BUS clocks.

#### Mode 1 - µP Peripheral Mode

In Mode 1, the STPA operates as an asynchronous 68000-type microprocessor peripheral. All three dual-port RAMS (Tx0, Tx1, Rx0) are made available and may be configured as 32 or 24 byte RAM's. Also available are the full complement of control and interrupt registers. The address map for Mode 1 is shown in Table 2.

The STPA, in Mode 1, uses signals  $\overline{CS}$ , R/W,  $\overline{DS}$  (Data Strobe),  $\overline{DTACK}$  (Data Acknowledge) IRQ, and IACK (Interrupt Acknowledge) at the parallel interface. The pinout of the device is shown in Figure 3.

# MT8920B

| 1103                   | 12VD |                                                  |                        |    |                 |    |    |             |    |    |                 |

|------------------------|------|--------------------------------------------------|------------------------|----|-----------------|----|----|-------------|----|----|-----------------|

|                        |      | 7                                                |                        |    | 1               | r  |    | 1           |    | 1  | 1               |

| 31                     | 23   |                                                  | 31                     | 23 |                 | 31 | 31 |             | 31 | 31 | ļ               |

| 30                     | 22   | _                                                | 30                     | 22 |                 | 30 | 30 |             | 30 | 30 |                 |

| 29                     | 21   |                                                  | 29                     | 21 |                 | 29 | 29 |             | 29 | 29 |                 |

| $\times$ <sup>28</sup> |      |                                                  | $\times$ <sup>28</sup> |    |                 | 28 | 28 |             | 28 | 28 |                 |

| 27                     | 20   |                                                  | 27                     | 20 |                 | 27 | 27 |             | 27 | 27 |                 |

| 26                     | 19   |                                                  | 26                     | 19 |                 | 26 | 26 |             | 26 | 26 |                 |

| 25                     | 18   | DE                                               | 25                     | 18 | DE              | 25 | 25 | MODE        | 25 | 25 | DE              |

| $\times$ <sup>24</sup> |      | ž                                                | 24<br>×                |    | Σ.              | 24 | 24 | Σ.          | 24 | 24 | Σ<br>MO         |

| 23                     | 17   | INE                                              | 23                     | 17 | NEL             | 23 | 23 | NEL         | 23 | 23 | NEL             |

| 22                     | 16   | HAN                                              | 22                     | 16 | HAN             | 22 | 22 | HAN         | 22 | 22 | CHANNEL MODE    |

| 21                     | 15   | RAM ADDRESS vs. ST-BUS CHANNEL - 24 CHANNEL MODE | 21                     | 15 | 24 CHANNEL MODE | 21 | 21 | 32 CHANNEL  | 21 | 21 | 32 CI           |

| $\times ^{20}$         |      |                                                  | × 20                   |    |                 | 20 | 20 |             | 20 | 20 | -               |

| 19                     | 14   | NNE                                              | 19                     | 14 | CHANNEL         | 19 | 19 | CHANNEL     | 19 | 19 | CHANNEL - 32    |

| 18                     | 13   | СНА                                              | 18                     | 13 | ЯНС             | 18 | 18 | SHA         | 18 | 18 | SHA             |

| 17                     | 12   | NS (                                             | 17                     | 12 |                 | 17 | 17 |             | 17 | 17 |                 |

| $^{16}_{6} \times$     |      | 3T-B                                             | 16<br>16               |    | ST-BUS          | 16 | 16 | ST-BUS      | 16 | 16 | ST-BUS          |

| 15                     | 11   | vs. S                                            | 15                     | 11 |                 | 15 | 15 |             | 15 | 15 |                 |

| 14                     | 10   | SS                                               | 14                     | 10 | SS \            | 14 | 14 | ADDRESS vs. | 14 | 14 | SS \            |

| 13                     | 6    | DRE                                              | 13                     | 6  | ORE             | 13 | 13 | DRE         | 13 | 13 | DRE             |

| $\stackrel{2}{\sim}$   |      | AD                                               | × <del>1</del> 2       |    | ADI             | 12 | 12 | ADI         | 12 | 12 | ADI             |

| 1                      | œ    | RAM                                              | 1                      | ω  | RAM ADDRESS vs. | 11 | 1  | RAM         | 1  | 1  | RAM ADDRESS vs. |

| 10                     | 7    | Ř                                                | 10                     | 7  | T X F           | 10 | 10 | RX          | 10 | 10 | T×F             |

| 6                      | 9    | IVE                                              | 6                      | 9  |                 | 6  | 6  |             | ი  | 6  | ∃VI             |

| ∞×                     |      | RELATIVE                                         | ∞×                     |    | RELATIVE        | ω  | ø  | RELATIVE    | ω  | ω  | RELATIVE        |

| 7                      | 5    |                                                  | 7                      | 5  |                 | 7  | 7  |             | 7  | 7  |                 |

| 9                      | 4    | 4 a)                                             | 9                      | 4  | 4 b)            | 9  | 9  | 4 c)        | 9  | 9  | 4 d)            |

| 5                      | с    | Figure 4                                         | 5                      | e  | Figure          | 5  | 5  | Figure      | 5  | 5  | Figure          |

| 4 X                    |      | Fig                                              | 4 X                    |    | Fig             | 4  | 4  | Fig         | 4  | 4  | Fig             |

| З                      | 7    |                                                  | ю                      | N  |                 | 3  | с  |             | ю  | e  |                 |

| Р                      | -    |                                                  | 2                      | -  |                 | 2  | 7  |             | 2  | N  |                 |

| -                      | 0    |                                                  | -                      | 0  |                 | -  | ~  |             | -  | -  |                 |

X- unused channels marked X transmit FF<sub>16</sub>

0

STo0 STo1 0

RELATIVE RAM LOCATION

0

RELATIVE RAM LOCATION

0

STi0

ο×

STi0

RELATIVE RAM LOCATION ο×

STo0 STo1 RELATIVE RAM LOCATION

|                |                             | ADD            | RESS           | BITS           |                       |                                   | REGISTERS                         |                             |  |

|----------------|-----------------------------|----------------|----------------|----------------|-----------------------|-----------------------------------|-----------------------------------|-----------------------------|--|

| A <sub>6</sub> | A <sub>5</sub>              | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub>                    | READ                              | WRITE                       |  |

| 0              | 0                           | 0              | 0              | 0              | 0                     | 0                                 | 0 Rx0 - Channel 0 Tx0 - Channel 0 |                             |  |

| •              | •                           | •              | •              | •              | •                     | •                                 | •                                 | •                           |  |

| •              | •                           | •              | •              | •              | ٠                     | •                                 | •                                 | •                           |  |

| •              | •                           | •              | •              | •              | •                     | •                                 | •<br>Rx0 - Channel 31             | •<br>Tx0 - Channel 31       |  |

| 0              | •                           |                |                |                |                       | 1                                 |                                   |                             |  |

| Х              | 1                           | 0              | 0              | 0              | 0                     | 0                                 | Control Register 1                | Control Register 1          |  |

| Х              | 1                           | 0              | 0              | 0              | 0                     | 1                                 | Control Register 2                | Control Register 2          |  |

| Х              | 1                           | 0              | 0              | 0              | 1                     | 0                                 | Interrupt Vector Register         | Interrupt Vector Register   |  |

| Х              | 1                           | 0              | 0              | 1              | 0                     | 0                                 | Interrupt Flag Register 1         | -                           |  |

| Х              | 1                           | 0              | 0              | 1              | 0                     | 1                                 | Interrupt Flag Register 2         | -                           |  |

| Х              | 1                           | 0              | 0              | 1              | 1                     | 0 Image Register 1 -              |                                   | -                           |  |

| Х              | 1                           | 0              | 0              | 1              | 1                     | 1                                 | Image Register 2                  | -                           |  |

| Х              | 1                           | 0              | 1              | 0              | 0                     | 0                                 | Interrupt Mask Register 1         | Interrupt Mask Register 1   |  |

| Х              | 1                           | 0              | 1              | 0              | 0                     | 1                                 | Interrupt Mask Register 2         | Interrupt Mask Register 2   |  |

| Х              | 1                           | 0              | 1              | 0              | 1                     | 0                                 | Match Byte Register 1             | Match Byte Register 1       |  |

| Х              | 1                           | 0              | 1              | 0              | 1                     | 1                                 | Match Byte Register 2             | Match Byte Register 2       |  |

| Х              | 1                           | 0              | 1              | 1              | 0                     | 0                                 | Interrupt Channel Address 1       | Interrupt Channel Address 1 |  |

| Х              | 1                           | 0              | 1              | 1              | 0                     | 1                                 | Interrupt Channel Address 2       | Interrupt Channel Address 2 |  |

| 1              | 0                           | 0              | 0              | 0              | 0                     | 0 Rx0 - Channel 0 Tx1 - Channel 0 |                                   | Tx1 - Channel 0             |  |

| •              | •                           | •              | •              | •              | •                     | •                                 | •                                 | •                           |  |

| •              | •                           | •              | •              | •              | •                     | •                                 | •                                 | •                           |  |

| •              | •                           | •              | •              | •              | •                     | •                                 | •<br>Decl. Observat 24            | •<br>Tert Observal 04       |  |

| 1              | 0                           | 1              | 1              | 1              | 1                     | 1                                 | Rx0 - Channel 31                  | Tx1 - Channel 31            |  |

|                | Table 2. Mode 1 Address Map |                |                |                |                       |                                   |                                   |                             |  |

| Bit | Name           | Description                                                                                                                                                                                                                                             |

|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | (Unused)       |                                                                                                                                                                                                                                                         |

| 6   | IRQRST         | <b>Interrupt Reset.</b> This bit, when set high, automatically clears the Interrupt Flag Register and the Interrupt Image Register without these registers being serviced. This bit automatically resets to zero after the register clear is completed. |

| 5   |                | <b>RAM Configuration.</b> This bit configures Tx0, Tx1 and Rx0 RAMS for 32 or 24 byte operation. $D_5 = 0$ for 32 channel; $D_5 = 1$ for 24 channel.                                                                                                    |

| 4   | A <sub>6</sub> | Address Bit A6. This bit extends the addressing range for access to Tx1 memory.                                                                                                                                                                         |

| 3   |                | <b>Interrupt Source 2 Mode Select.</b> This bit configures the source 2 interrupt generator.<br>$D_3 = 0$ selects "static" interrupt mode; $D_3 = 1$ selects "dynamic" interrupt mode.                                                                  |

| 2   |                | <b>Interrupt Source 1 Mode Select.</b> This bit configures the source 1 interrupt generator.<br>$D_2 = 0$ selects "static" interrupt mode; $D_2 = 1$ selects "dynamic" interrupt mode.                                                                  |

| 1   | IRQ2EN         | Interrupt Source 2 Enable. IRQ2EN = 1 enables interrupts to occur from source 2.                                                                                                                                                                        |

| 0   | IRQ1EN         | Interrupt Source 1 Enable. IRQ1EN = 1 enables interrupts to occur from source 1.                                                                                                                                                                        |

Table 3.

Control Register 1 Bit Definitions

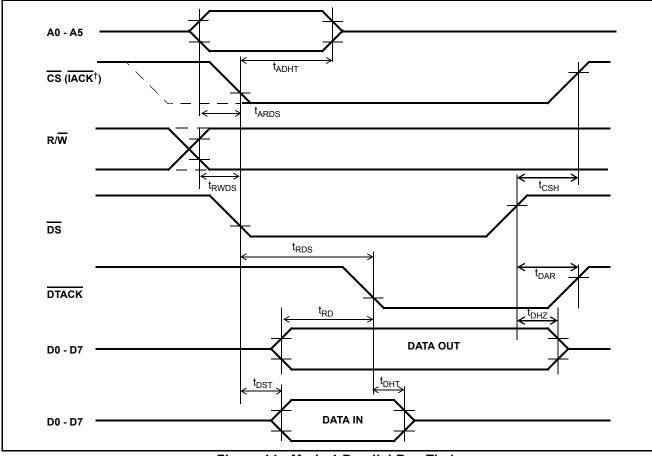

Timing information for data transfers on this interface is shown in Figure 14. The Mode 1 interface is designed to operate directly with a 68000-type asynchronous bus but can easily accommodate most other popular microprocessors as well.

#### **Control Registers**

Two control registers allow control of Mode 1 features. Control Register 1 provides bits to select the type of interrupt, to enable interrupts from two different and independent sources and to reset the interrupt registers. Also contained in Control Register 1 are bits to configure the device for 24 or 32 channel operation and to expand the address range for convenient access to the second transmit RAM Tx1. A description of the bit functions in Control Register 1 is shown in Table 3.

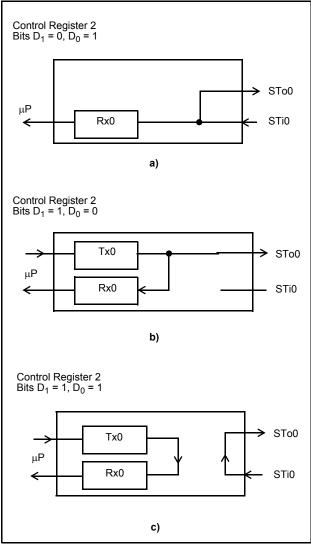

Mode 1 provides various loopback paths and output configuration options which are controlled by bits in Control Register 2. Bits  $D_0$ ,  $D_1$  of Control Register 2 configure loopbacks using input and output streams STi0, STo0 as described in Table 4. The input stream STi0 can be looped back to source the output stream STo0 as well as receive RAM Rx0. The transmit RAM Tx0 can be looped to source the receive RAM Rx0, as well as STo0 and, the transmit RAM Tx0 can be looped to the receive RAM Rx0 while STi0 sources STo0. The function of these loopback configurations is shown in Figure 5.

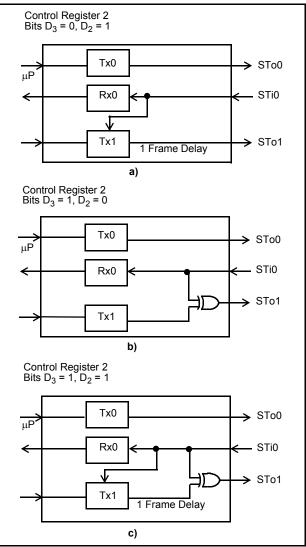

In a similar way, the output STo1 can be reconfigured for different functionality. Bits  $D_2$  and  $D_3$  of Control Register 2 allow STo1 to be sourced, with a one frame delay via Tx1 from receive stream STi0. STo1 can also output the result of a comparison of the contents of Tx1 ram with input stream STi0. These output configurations of STo1 are shown in Figure 6 a and b. Figure 6 c shows the effect of combining these two features.

#### Interrupt Registers

Interrupts can be generated in Mode 1 only. Two channels of the ST-BUS input stream, STi0, can be selected to provide an interrupt to the system. Interrupts can be of two types: Static or Dynamic. Static interrupts are caused when data within a selected channel matches a given pattern. Dynamic interrupts occur when bits in a selected channel change state (1 to 0, 0 to 1 or toggle). Interrupts are controlled through two identical paths (1 and 2) consisting of the following registers:

**Interrupt Channel Address (1/2):** The address (0-31) of the channel which will generate the interrupt is stored in this register.

**Image Register (1/2):** The contents of the channel causing the interrupt is stored in this register. Reading this register will clear its contents.

**Match Byte Register (1/2):** In static mode this register is used to store the byte which will be compared with the contents of the selected channel causing the interrupt.

In dynamic mode, the bits in this register and the corresponding bit in the Interrupt Mask Register define the type of dynamic interrupt (i.e., 0 to 1, 1 to 0, toggle). (Refer to Table 5.)

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | (Unused) |                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3-2 | CONFIG   | STo1 Output Configuration Bits:D3D2 = 00-<br>01-Normal operation. ST-BUS stream from Tx1 is output on STo1 pin.<br>STi0 stream is output on STo1 pin delayed one frame (Figure 6 a).10-STi0 is compared through XOR (exclusive OR) with ST-BUS stream<br>from Tx1 and output at STo1 (Figure 6 b).11-STi0 stream, delayed one frame (via Tx1), is compared (XOR) with the<br>next frame arriving at STi0 and the result output at STo1 (Figure 6 c). |

| 1-0 |          | Internal Loopback Configuration Bits:D1D0= 00-Normal operation. No internal loops.01-Loop STi0 to STo0 while still receiving STi0 in Rx0 (Figure 5 a).10-Loop Tx0 output ST-BUS stream to Rx0 input ST-BUS stream while<br>outputting Tx0 output to STo0. STi0 is not received (Figure 5 b).11-Loop Tx0 output ST-BUS stream to Rx0 input ST-BUS stream. Loop<br>STi0 to STo0 (Figure 5 c).                                                          |

Table 4. Control Register 2 Bit Definitions

Figure 5 - Loopback Configurations

**Interrupt Mask Register (1/2):** In static mode the contents of this register masks bits in the Match Byte Register that are 'don't care' bits

- 1 bit masked

- 0 bit not masked

In dynamic mode, each bit in this register and the corresponding bit in the Match Byte Register define what type of dynamic interrupt is selected. (Refer to Table 5.)

**Interrupt Flag Register (1/2):** In static mode the least significant bit in this register is set to 1 to flag the corresponding path in which the interrupt occurs.

In dynamic mode this register sets the bits which reflect the position of the bits in the corresponding Interrupt Register which caused the interrupt.

Figure 6 - STo1 Configurations

#### Interrupt Vector Register

This register shown in Figure 7 is common to both interrupt paths and stores an 8 bit vector number which will be output <u>on</u> the data bus when Interrupt Acknowledge (IACK) is asserted. Bits labelled  $V_2 - V_7$  are stored by the controlling  $\mu P$ . Bits IRQ1 and IRQ2 are set by the STPA to indicate which path caused the interrupt. This creates unique vectors which are used by the  $\mu P$  to vector to interrupt service routines. This feature may be bypassed by simply not asserting IACK during interrupt acknowledged.

| D7             | D6             | D5    | D4    | D3    | D2             | D1   | D0   |

|----------------|----------------|-------|-------|-------|----------------|------|------|

| V <sub>7</sub> | V <sub>6</sub> | $V_5$ | $V_4$ | $V_3$ | V <sub>2</sub> | IRQ2 | IRQ1 |

Figure 7 - Interrupt Vector Registers

### Static Interrupt Mode

A static interrupt is caused when an incoming byte matches a predefined byte. The incoming byte from a selected channel is stored in Interrupt Image Register (1/2) where it is compared with the contents of the corresponding Match Byte Register. The result of the comparison of individual bits is masked by the contents of the <u>Mask</u> Register (1/2) before it is used to generate an IRQ. After a static interrupt occurs, information in the Interrupt Image Register is frozen until the  $\mu$ P performs a read operation on this register.

When servicing static interrupts assertion of IACK will cause the contents of the Vector Register, with the IRQ1 or IRQ2 bit set, to be output on the data bus. The service routine can subsequently clear IRQ by reading the Interrupt Image Register. Alternatively, the IRQRST bit in Control Register 1 can be set to clear the associated interrupt registers.

Static Interrupts are selected using IRQ1MODE and IRQ2MODE bits in Control Register 1. Interrupts are then enabled to the IRQ pin with IRQ1EN and IRQ2EN bits of the same register.

### Dynamic Interrupt Mode

A dynamic interrupt is generated by a change of state of bits in a selected channel. A 0 to 1 transition or a 1 to 0 transition or a simple change of state from the previous state (toggle) can be detected. The type of transition to be detected is selected using two bits, one from the Match Byte Register (1/2) and one from the Interrupt Mask Register (1/2), in the corresponding bit positions. Table 5 shows how the two registers are programmed.

| Match<br>Byte<br>Register<br>bit D <sub>X</sub> | Mask<br>Byte<br>Register<br>bit D <sub>X</sub> | Transition Type Detected<br>on Incoming bit D <sub>X</sub><br>(x = 07) |

|-------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------|

| 0                                               | 0                                              | Mask Bit D <sub>X</sub>                                                |

| 0                                               | 1                                              | 0 to 1 transition                                                      |

| 1                                               | 0                                              | 1 to 0 transition                                                      |

| 1                                               | 1                                              | Toggle                                                                 |

Table 5 - Dynamic Interrupt Types

For example, the following steps are required to generate an interrupt when bit  $D_3$  of channel 4 changes state from 0 to 1 (all other bits are masked):

### $D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$

Channel Address Register 1 = 0 0 0 0 0 1 0 0 (channel 4 of STi0 selected)

| Match Byte Register 1 =                  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

|------------------------------------------|---|---|---|---|---|---|---|---|--|

| Interrupt Mask Register 1 =              | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |  |

| (When bit D <sub>3</sub> toggles 0 to 1) |   |   |   |   |   |   |   |   |  |

Dynamic interrupts from interrupt path 1 would then be enabled using the Control Register 1.

Control Register 1 = 0 0 0 0 0 1 0 1

This would cause interrupt 1 path to be enabled while interrupt 2 path is disabled.

As with static interrupts, upon serving a dynamic interrupt, assertion of IACK will cause the contents of the Vector Register, with the appropriate path bit set, to be output on the data bus. The information contained in the channel is frozen in the Interrupt Image Register. To clear a dynamic interrupt, however, the  $\mu$ P must read the Interrupt Flag Register of the path responsible for the interrupt to determine which bit caused the interrupt. The bit in the corresponding position will be set to 1 and reading this register will clear its contents.

Alternatively, as with static interrupts, the IRQRST bit in Control Register 1 can be set to clear the Image Interrupt Register, Flag Register and path bits in the Vector Register.

Dynamic Interrupts are selected using IRQ1MODE and IRQ2MODE bits in Control Register 1 and are enabled using IRQ1EN and IRQ2EN in the same register.

### **MMS Pin Reset**

The STPA can be RESET in Mode 1 using the MMS pin (27). Applying a low pulse (0V) to MMS after power is applied to the device will reset all control and interrupt registers to  $00_{16}$ . This can be accomplished on power up with a simple R-C circuit as shown in Figure 8.

Figure 8 - MMS Reset Function

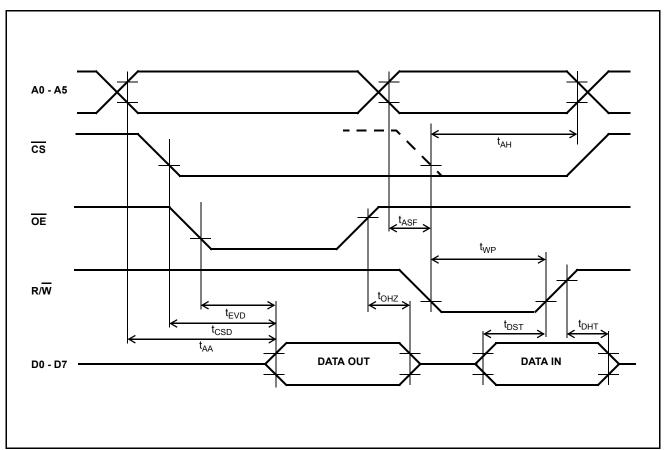

# Mode 2 - Fast RAM Mode

Mode 2 operates as a high speed dual port RAM interface to the ST-BUS. Only the two transmit RAM's, Tx0 and Tx1, and the receive RAM, Rx0 are active in this mode (i.e., control registers and interrupt registers are inactive).

The main feature of this mode is fast access to the dual-port RAM's. Fast access allows high-speed controllers to use this device as a data interface to T1 and CEPT digital links. Timing information is shown in Figure 15.

Mode 2 can also support 24 channel and 32 channel operation. The channel configuration is selected using 24/32 pin. When 24/32=0 the device operates in 24 channel mode and when 24/32=1, it operates in 32 channel mode.

The physical interface in this mode resembles that of a simple RAM device. The signals used to read and write the device are CS, OE, R/W. The pinout of the STPA in this mode is shown in Figure 3. Address decoding for Tx0, Tx1, Rx0 is shown in Table 6.

Contention can arise for access to the dual port RAMS. The occurrence of this is minimized since the ST-BUS serial-to-parallel and parallel-to-serial converters require RAM access for only <u>1/32</u> of a channel time (i.e., last half cycle of C4i for each channel). For contention to occur the high speed controller must access the same RAM location as that of the ST-BUS. For a parallel read operation this corresponds to the current ST-BUS channel and for a write operation, the next ST-BUS channel. Access contention in Mode 2 is arbitrated with the BUSY signal. BUSY is intended to hold off any parallel access cycle until it again goes inactive. Figure 16 shows how the access is arbitrated for accesses near the contention window.

Applications using high speed access can easily avoid generating BUSY by co-ordinating channel

reads and writes with framing and channel boundary information.

# Mode 3 - Parallel Bus Controller

In this mode the STPA outputs all necessary signals required to drive devices attached to the parallel port. The STPA can be used to drive devices such as RAM's, FIFO's, latches, A/D and D/A converters, and CODECS, directly from the ST-BUS without an intervening  $\mu$ P. As with the other modes, Mode 3 can operate from 32 channels or 24 channels by connecting 24/32 high or low, respectively. This allows devices to be driven remotely via a T1 or CEPT digital trunk link when used with Zarlink's trunk products.

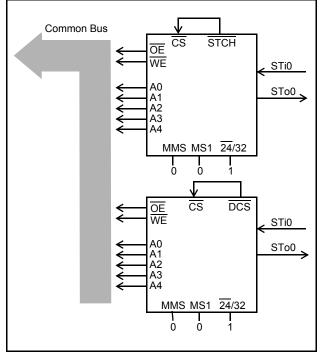

Referring to Figure 1, the Address Generator block generates and drives the external address lines A4-A0. The <u>STPA</u> also generates OE (output enable) and WE (write enable) to facilitate data transfers from Rx0 RAM and to Tx0 RAM. Tx1 RAM is unavailable in this mode.

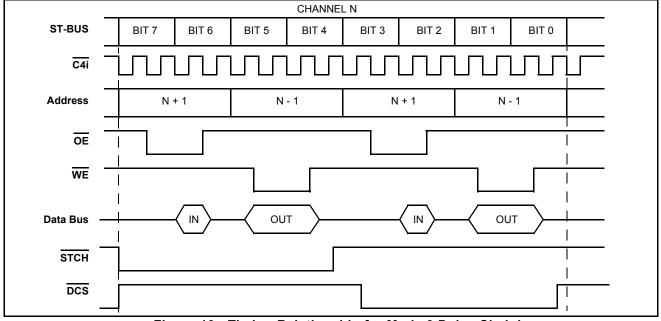

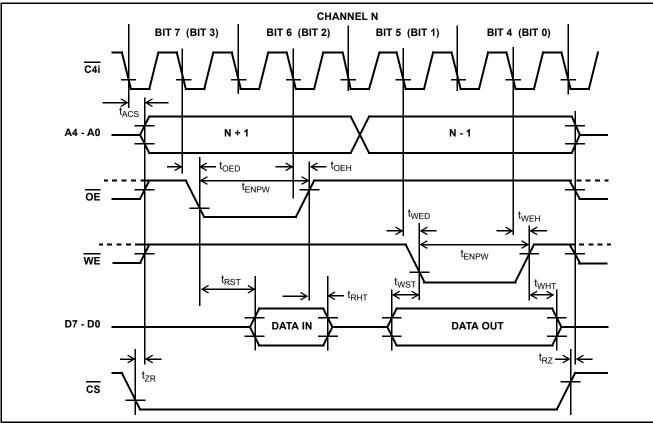

The STPA, in Mode 3, generates external addresses in a particular sequence that minimizes throughput delay through the device. When channel N is present on the ST-BUS, the STPA generates address N+1 on the address bus and asserts OE to output data from an external device and latch it into the STPA. During the same channel N, the STPA will generate address N-1 with WE asserted to write from the STPA to an external device. Timing for Mode 3 transfers is shown in Figure 17. All parallel bus signals are synchronized to the ST-BUS clock.

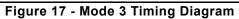

The device must be selected using  $\overline{CS}$  in order for the parallel bus drivers to be enabled.  $\overline{CS}$  should remain active for four ST-BUS bit periods (8 x  $\overline{C4i}$ cycles) since a read and a write operation require 2 bit periods each. The STPA generates a signal STCH (start of channel) which becomes active at the start of each channel and remains active for 1/2 of the channel time (Figure 18). This signal may be

|                | Α              | DDRE           | SS BIT         | S                     |                | REGIS            | STERS            |  |  |  |  |

|----------------|----------------|----------------|----------------|-----------------------|----------------|------------------|------------------|--|--|--|--|

| A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | <b>A</b> <sub>1</sub> | A <sub>0</sub> | READ             | WRITE            |  |  |  |  |

| 0              | 0              | 0              | 0              | 0                     | 0              | Rx0 - Channel 0  | Tx0 - Channel 0  |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| 0              | 1              | 1              | 1              | 1                     | 1              | Rx0 - Channel 31 | Tx0 - Channel 31 |  |  |  |  |

| 1              | 0              | 0              | 0              | 0                     | 0              | Rx0 - Channel 0  | Tx1 - Channel 0  |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| •              | •              | •              | •              | •                     | •              | •                | •                |  |  |  |  |

| 1              | 1              | 1              | 1              | 1                     | 1              | Rx0 - Channel 31 | Tx1 - Channel 31 |  |  |  |  |

Table 6. Mode 2 Address Map

connected directly to  $\overline{\text{CS}}$  to enable the device appropriately.

Figure 9 - "Daisy-chained" STPA's in 32 Channel Parallel Bus Controller Mode (Mode 3)

In order to facilitate efficient use of the parallel bus another signal, similar to STCH, is supplied by the STPA. Delayed Chip Select (DCS) becomes active for the last half of each channel (Figure 19). This may be connected to a second STPA, residing on the same physical parallel bus, enabling it to perform its read/write operations in the second half of each channel. This allows a large number of devices, connected on a common bus, to be driven by two ST-BUS streams. Figure 9 shows how this "daisy chaining" of STPA's is implemented while Figure 10 illustrates the timing on the shared parallel bus.

## **Applications**

#### Parallel PBX to Digital Trunk Interface

The STPA is an ideal component for interfacing parallel PBX environments to Zarlink's family of digital trunk devices.

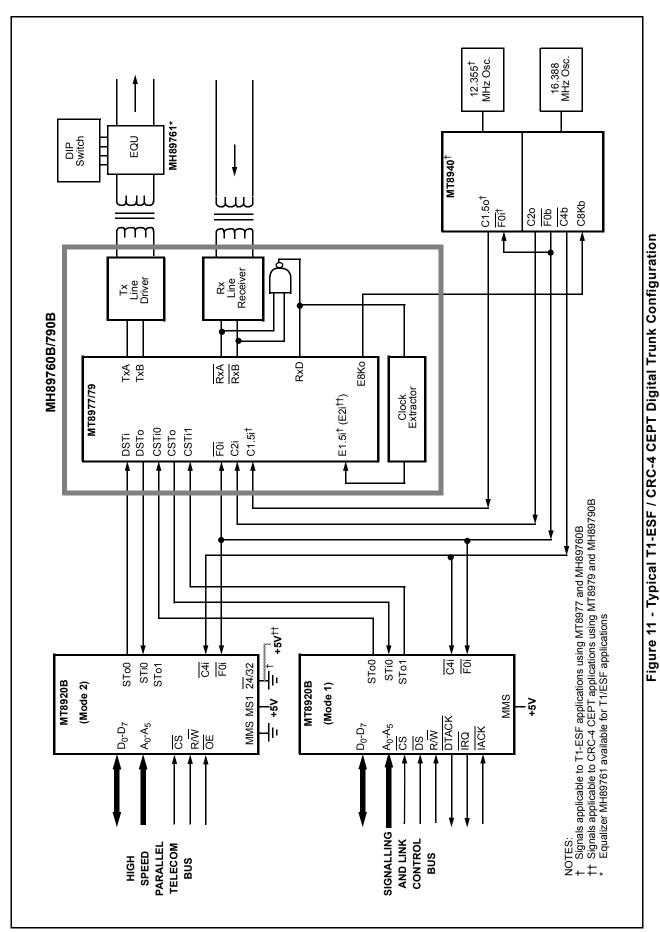

Figure 11 shows a typical interface for both T1/ESF and CRC-4 CEPT digital trunks to a system utilizing a parallel bus architecture. Both the MH89760B T1/ESF and the MH89790B CRC-4 CEPT trunk modules are shown interfaced to a parallel bus structure using two STPAs operating in modes 1 and 2.

The first STPA operating in mode 2 (MMS=0, MS1=1, 24/32=0), routes data and/or voice information between the parallel telecom bus and the T1 or CEPT link via DSTi and DSTo. The second STPA, operating in mode 1 (MMS=1) provides access from the signalling and link control bus to the MH89760B or MH89790B status and control channels. All signalling and link functions may be controlled easily through the STPA transmit RAM's Tx0, Tx1, while status information is read at receive RAM Rx0. In addition, interrupts can be set up to notify the system in case of slips, loss of sync, alarms, violations, etc.

Figure 10 - Timing Relationship for Mode 3 Daisy Chaining

13

# MT8920B

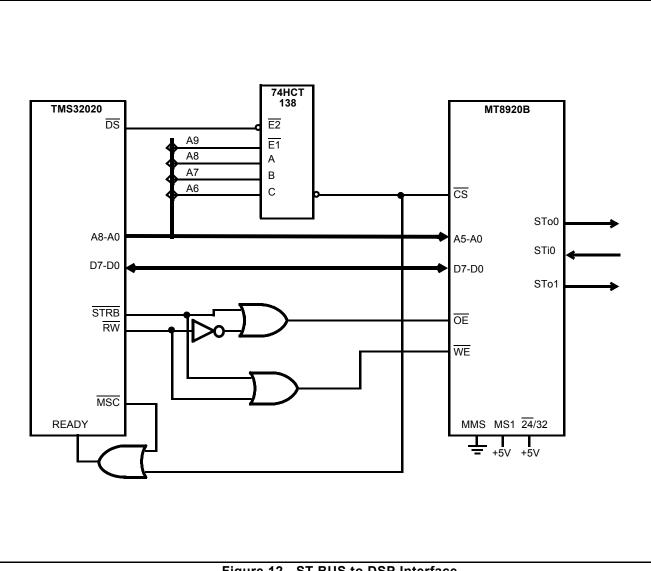

### **Digital Signal Processor to ST-BUS Interface**

Mode 2 allows many high speed devices to be easily connected to the ST-BUS. Figure 12 shows a TMS32020 digital signal processor interfaced to the ST-BUS through the STPA. This simple interface allows complex functions to be implemented in such systems as PBX's and computer systems. Some of the possible functions include:

- Digital Filtering

- Voice Conferencing

- Speech/Data Compression

- Encryption

- Tone Detection and Generation

- Frequency Spectrum Analysis

- Image Processing

- μ-Law to A-Law Conversion

- Echo Cancellation

- Modulation

- Speech Synthesis and Recognition

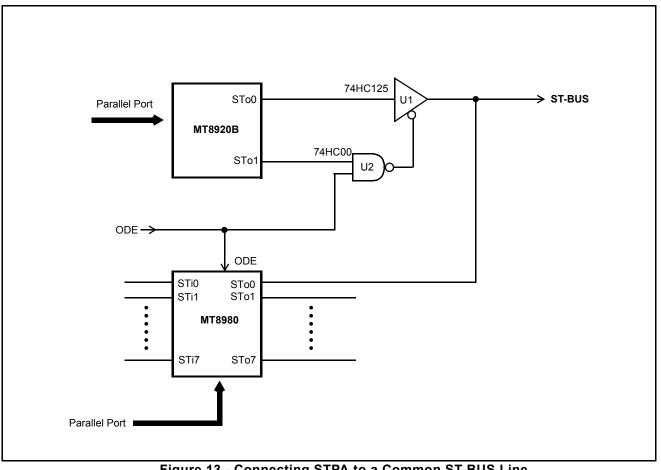

# Connecting the STPA to a shared ST-BUS Line

The STPA's STo0 and STo1 outputs cannot be directly forced into a high impedance state. However, with some external logic, the STo0 output can be buffered by a three-state device, controlled by the STo1 output. This application is only possible if the Tx1 RAM and associated STo1 output are not required for some other purpose.

Figure 13 shows an external buffer U1 controlled by the STo1 output and an external Output Data Enable (ODE) signal. When FF (hex) is written to the Tx1 RAM, the corresponding STo1 output channel goes to logic high. This signal, AND-ed together with a logic high at ODE, enables U1, resulting in the STo0 signal transparently passed to the output of U1. When 00 (hex) is written to the Tx1 RAM, the STo1 output goes logic low. This disables U1, resulting in

a high impedance state at the output of U1, corresponding to the selected channel.

This method of three-state buffering permits output control on a per-channel or per-bit basis.

The ODE input is used to enable the ST-BUS outputs after all ST-BUS devices are properly configured by software. This eliminates the possibility of contention on the ST-BUS lines during the power-up state.

Figure 13 - Connecting STPA to a Common ST-BUS Line

|   | Parameter                         | Symbol           | Min. | Max.                  | Units |  |  |  |  |  |  |  |  |

|---|-----------------------------------|------------------|------|-----------------------|-------|--|--|--|--|--|--|--|--|

| 1 | Supply Voltage                    | V <sub>DD</sub>  | -0.3 | 7.0                   | V     |  |  |  |  |  |  |  |  |

| 2 | Voltage on any I/O pin            |                  | -0.3 | V <sub>DD</sub> + 0.3 | V     |  |  |  |  |  |  |  |  |

| 3 | Current on any I/O pin            | I <sub>I/O</sub> |      | ±25                   | mA    |  |  |  |  |  |  |  |  |

| 4 | Storage Temperature               | T <sub>ST</sub>  | -55  | 125                   | °C    |  |  |  |  |  |  |  |  |

| 5 | Package Power Dissipation Plastic | PD               |      | 600                   | mW    |  |  |  |  |  |  |  |  |

# Absolute Maximum Ratings\* - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

# Recommended Operating Conditions - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|   | Characteristics           | Sym.            | Min. | Typ.‡ | Max.     | Units | Test Conditions        |

|---|---------------------------|-----------------|------|-------|----------|-------|------------------------|

| 1 | Supply Voltage            | V <sub>DD</sub> | 4.75 | 5.0   | 5.25     | V     |                        |

| 2 | Input High Voltage        | V <sub>IH</sub> | 2.4  |       | $V_{DD}$ | V     | for 400mV noise margin |

| 3 | Input Low Voltage         | V <sub>IL</sub> | 0    |       | 0.4      | V     | for 400mV noise margin |

| 4 | Operating Temperature     | T <sub>A</sub>  | -40  | 25    | 85       | °C    |                        |

| 5 | Operating Clock Frequency | f <sub>CK</sub> |      | 4.096 |          | MHz   |                        |

<sup>‡</sup> Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# **DC Electrical Characteristics** - Voltages are with respect to ground (V<sub>SS</sub>) unless otherwise stated.

|    | Characteristics                                                             | Sym.                                 | Min. | Тур.<br>‡ | Max. | Units    | Test Conditions                                                  |

|----|-----------------------------------------------------------------------------|--------------------------------------|------|-----------|------|----------|------------------------------------------------------------------|

| 1  | Supply Current Static<br>Dynamic                                            | I <sub>CCS</sub><br>I <sub>CCD</sub> |      | 10<br>5   | 10   | μA<br>mA | outputs unloaded<br>@f <sub>CK</sub> = 4.096 MHz                 |

| 2  | Input High Voltage                                                          | V <sub>IH</sub>                      | 2.0  |           |      | V        |                                                                  |

| 3  | Input Low Voltage                                                           | V <sub>IL</sub>                      |      |           | 0.8  | V        |                                                                  |

| 4  | Input Leakage Current                                                       | Ι <sub>Ζ</sub>                       |      |           | ±10  | μΑ       | $V_{DD}$ =5.25V,<br>$V_{IN}$ =V <sub>SS</sub> to V <sub>DD</sub> |

| 5  | Input capacitance                                                           | C <sub>IN</sub>                      |      |           | 10   | pF       |                                                                  |

| 6  | Schmitt trigger input high (MMS)                                            | $V_{T+}$                             | 3.8  | 3.0       |      | V        |                                                                  |

| 7  | Schmitt trigger input low (MMS)                                             | V <sub>T-</sub>                      |      | 2.0       | 1.0  | V        |                                                                  |

| 8  | Schmitt trigger hysteresis (MMS)                                            | $V_{H}$                              | 0.8  | 1.0       |      | V        |                                                                  |

| 9  | Output high current (except IRQ)                                            | I <sub>OH</sub>                      | 10   | 15        |      | mA       | V <sub>OH</sub> = 2.4V, V <sub>DD</sub> = 4.75V                  |

| 10 | Output low current (except IRQ)                                             | I <sub>OL</sub>                      | 5    | 10        |      | mA       | V <sub>OL</sub> = 0.4V, V <sub>DD</sub> = 4.75V                  |

| 11 | IRQ, DTACK, BUSY Sink Current                                               | I <sub>OL</sub>                      | 10   | 15        |      | mA       | V <sub>OL</sub> = 0.4V, V <sub>DD</sub> = 4.75V                  |

| 12 | Tristate Leakage $A_4$ - $A_0$ , $\overline{OE}$ , $\overline{WE}$ (mode 3) | I <sub>OZ</sub>                      |      | ±1        | ±10  | μΑ       | $V_{DD}$ = 5.25V<br>$V_{OUT}$ = $V_{SS}$ to $V_{DD}$             |

| 13 | Open drain off-state current<br>IRQ, DTACK, BUSY                            | I <sub>OFF</sub>                     |      | ±1        | ±20  | μΑ       | V <sub>DD</sub> = 5.25V<br>V <sub>OUT</sub> = V <sub>DD</sub>    |

| 14 | Output capacitance                                                          | CO                                   |      |           | 15   | pF       |                                                                  |

‡ Typical figures are at 25°C and are for design aid only: not guaranteed and not subject to production testing.

# AC Electrical Characteristics<sup>†</sup>- Mode 1 Parallel Bus Timing (see Fig. 14) $(V_{CC}=5.0V \pm 5\%, T_A=-40 \text{ to } 85^{\circ}C)$

|    | Characteristics                                                                                      | Sym.                            | Min.                    | Typ.‡            | Max.                    | Units | Test Conditions                                             |

|----|------------------------------------------------------------------------------------------------------|---------------------------------|-------------------------|------------------|-------------------------|-------|-------------------------------------------------------------|

| 1  | Address to $\overline{\text{DS}}$ ( $\overline{\text{CS}}$ ) Low <sup>††</sup>                       | t <sub>ARDS</sub>               | 0                       |                  |                         | ns    |                                                             |

| 2  | $R/\overline{W}$ to $\overline{DS}$ ( $\overline{CS}$ ) Low <sup>††</sup>                            | t <sub>RWDS</sub>               | 20                      |                  |                         | ns    |                                                             |

| 3  | $\overline{\text{DS}}$ ( $\overline{\text{CS}}$ ) Low to $\overline{\text{DTACK}}$ Low <sup>††</sup> | t <sub>RDS</sub> <sup>1,2</sup> | t <sub>cwm</sub>        | t <sub>CLK</sub> | 2*t <sub>CLK</sub>      | ns    | Load C                                                      |

| 4  | Valid Data to DTACK Low (Read)                                                                       | t <sub>RD</sub>                 | t <sub>cwm</sub><br>-30 |                  |                         | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> =740 $\Omega$ |

| 5  | DS High to DTACK High                                                                                | t <sub>DAR</sub>                |                         |                  | 65                      | ns    | Load C, C <sub>L</sub> =50pF                                |

| 6  | DS High to Data High Imped.(Read)                                                                    | t <sub>DHZ</sub>                | 0                       |                  | 45                      | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> =740 $\Omega$ |

| 7  | $\overline{\text{DS}}$ High to $\overline{\text{CS}}$ High                                           | t <sub>CSH</sub>                | 0                       |                  |                         | ns    |                                                             |

| 8  | Data Hold Time (Write)                                                                               | t <sub>DHT</sub>                | 0                       |                  |                         | ns    |                                                             |

| 9  | Input Data Valid after $\overline{\text{DS}}$                                                        | t <sub>DST</sub>                |                         |                  | t <sub>cwm</sub><br>-30 | ns    |                                                             |

| 10 | Address Hold Time <sup>††</sup>                                                                      | t <sub>ADHT</sub>               | 50                      |                  |                         | ns    |                                                             |

† Timing is over recommended temperature & power supply voltages.

‡ Typical figures are at 25°C, V<sub>DD</sub>=5V, t<sub>CLK</sub>=244 ns, t<sub>CH</sub>=t<sub>CL</sub>=122 ns and are for design aid only: not guaranteed and not subject to production testing.

††The cycle is initiated by the falling edge of  $\overline{\text{CS}}$  or  $\overline{\text{DS}}$ , whichever occurs last. Timing is relative to the last falling edge which initiates the cycle.

(1)  $t_{cwm}$  is equal to  $t_{CH}$  or  $t_{CL}$  whichever is smaller (some ST-BUS compatible transceivers may generate  $\overline{C4}$  clock having  $t_{CHmin}$ =70ns or  $t_{CLmin}$ =70ns.

(2) Worst case access when memory contention occurs.

#### Figure 14 - Mode 1 Parallel Bus Timing † During Interrupt Acknowledge cycle IACK replaces CS. R/W must remain high.

|    | Characteristics                                     | Sym.              | Min. | Typ.‡ | Max. | Units | Test Conditions                                              |

|----|-----------------------------------------------------|-------------------|------|-------|------|-------|--------------------------------------------------------------|

| 1  | OE Low to Valid Data                                | t <sub>EVD</sub>  |      |       | 60   | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> =740 $\Omega$  |

| 2  | Address Access Time                                 | t <sub>AA</sub>   |      |       | 120  | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> = 740 $\Omega$ |

| 3  | CS Low to Valid Data                                | t <sub>CSD</sub>  |      |       | 60   | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> =740 $\Omega$  |

| 4  | Output Disable                                      | t <sub>OHZ</sub>  |      |       | 50   | ns    | Load A, C <sub>L</sub> =130pF, R <sub>L</sub> =740 $\Omega$  |

| 5  | Address Setup Time                                  | t <sub>ASF</sub>  | 20   |       |      | ns    |                                                              |

| 6  | Data Setup Time                                     | t <sub>DST</sub>  | 30   |       |      | ns    |                                                              |

| 7  | Data Hold Time                                      | t <sub>DHT</sub>  | 5    |       |      | ns    |                                                              |

| 8  | Address Hold Time                                   | t <sub>AH</sub>   | 50   |       |      | ns    |                                                              |

| 9  | Write Pulse Width                                   | t <sub>WP</sub>   | 50   |       |      | ns    |                                                              |

| 10 | $\overline{OE}$ , R/W High to $\overline{C4i}$ High | t <sub>EC4H</sub> |      | -10   |      | ns    |                                                              |

| 11 | $\overline{OE}$ , R/W Low to $\overline{C4i}$ Low   | t <sub>EC4L</sub> |      | 10    |      | ns    |                                                              |

| 12 | C4i High to Busy Low                                | t <sub>C4BL</sub> |      | 50    |      | ns    | Load C                                                       |

| 13 | C4i Low to Busy High                                | t <sub>C4BH</sub> |      | 50    |      | ns    | Load C                                                       |

| 14 | OE, R/W High to Busy Low                            | t <sub>EBL</sub>  |      | 40    |      | ns    | Load C                                                       |

# AC Electrical Characteristics<sup>†</sup> - Mode 2 Parallel Bus Timing - (see Figures 15 and 16) $(V_{CC}=5.0V \pm 5\%, T_A=-40 \text{ to } 85^{\circ}C)$

† Timing is over recommended temperature & power supply voltages.

Typical figures are at 25°C, V<sub>DD</sub>=5V, t<sub>CLK</sub>=244 ns, t<sub>CH</sub>=t<sub>CL</sub>=122 ns and are for design aid only: not guaranteed and not subject to production testing.

Figure 16 - Mode 2 Access Contention Resolution

# AC Electrical Characteristics<sup>†</sup> - Mode 3 Timing (see Fig.17, 18 and 19) $((V_{CC}=5.0V \pm 5\%, TA=-40 \text{ to } 85^{\circ}C)$

|    | Characteristics                                                         | Sym.              | Min. | Typ.‡              | Max.                         | Units | Test Conditions                                                |

|----|-------------------------------------------------------------------------|-------------------|------|--------------------|------------------------------|-------|----------------------------------------------------------------|

| 1  | CS to OE, WE, Address<br>Enabled                                        | t <sub>ZR</sub>   |      |                    | 50                           | ns    | Load A, C <sub>L</sub> = 130pF, R <sub>L</sub> = 740 $\Omega$  |