ANALOGIC.I

**Highly Stable, Low Power**

Sampling A/D Converters

ADAM-824B/

825B

14- and 15-Bit

T-51-07-01

#### Description

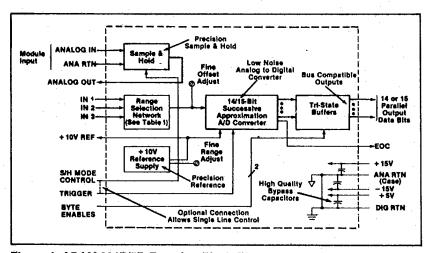

The ADAM-824B and -825B analog-todigital converters (ADCs), with their integral sample-and-hold amplifiers, are complete data acquisition subsystems that provide overall accuracies better than many ADCs alone. This high level of accuracy is accompanied by improved stability and reduced power dissipation over previous converters of similar architecture. For example, with a differential linearity tempco of ±3 ppm, the 14-bit accuracy of the ADAM-824B is maintained over a full 20°C temperature rise! Due to the integral sample-and-hold (S/H) circuits, the ADAM-824B and 825B give the system designer optimized system performance and eliminate the potential difficulties in integrating the S/H and A/D of precision data acquisition systems.

Both the ADAM-824B and ADAM-825B provide guaranteed endto-end performance in a small 2" x 4" modular package. Their accuracy, along with features such as tri-state output, low power dissipation, and low cost, make them an excellent choice for a variety of data acquisition systems, automatic test equipment, and analytical instrumentation.

## **Features**

- **■** High Throughput Rate 20 kHz (Includes both sampling and conversion time)

- Low Power 0.9W

- S/H Feedthrough Rejection

- Low Differential Nonlinearity ± 1/2 LSB maximum

- Low Tempco Differential nonlinearity ±2 ppm/°C FSR maximum (825B)

- **Low Noise** 50 μV rms (ADC)

- Byte-Selectable HCT Tri-State **Buffered Outputs**

- Pin-Programmable Input Voltage Range  $0V \text{ to } + 5V, 0V \text{ to } + 10V, \pm 5V,$ ± 10V

#### **Applications**

- Automatic Test Equipment

- Analytical Instrumentation

- **Precision Data Acquisition Systems**

- Materials Testing

Figure 1. ADAM-824B/5B Function Block Diagram.

SAMPLING ANALOG-TO-DIGITAL CONVERTERS

#### **SPECIFICATIONS**

T-51-07-01

(Includes combined S/H and A/D performance, and applies to both ADAM-824B and ADAM-825B except where noted)

(All specifications guaranteed at 25°C unless otherwise noted)

**ANALOG INPUT** Full Scale Range (FSR) 0V to +5V, 0V to +10V, ±5V, ±10V Maximum Input Without Damage Impedance 100 Megohm // 5 pF

**ACCURACY** Absolute Accuracy<sup>2</sup>

Calibrated to ±0.006% FSR Relative Accuracy³

±0.005% FSR maximum (ADAM-824B),

±0.003% FSR maximum (ADAM-825B) Differential Nonlinearity ±0.003% FSR maximum (ADAM-824B), ±0.0015% FSR maximum (ADAM-825B) Quantizing Error ± 1/2 LSB Noise (S/H plus A/D) 75 µV rms Noise (A/D only)

#### Guaranteed STABILITY

50 μV rms

Monotonicity

Bias Current<sup>1</sup>

1 nA maximum

Tempco of Differential Nonlinearity ±3 ppm/°C FSR maximum (ADAM-824B), ±2 ppm/°C FSR maximum (ADAM-825B) Gain Tempco ±8 ppm/°C FSR maximum Offset Tempco  $\pm$  30  $\mu$ V/°C typical,  $\pm$  80  $\mu$ V/°C maximum Clock Stability ± 0.03%/°C **Power Supply Sensitivity** ±0.001% FSR per 1% change in supply voltage Warm-up Time to Specified Accuracy 5 minutes **Recommended Recalibration Interval** 6 months

**DYNAMIC PERFORMANCE** Maximum Throughput Rates 20,000 measurements/second S/H Aperture Delay 50 ns S/H Aperture Uncertainty S/H Hold Mode Feedthrough Rejection 90 dB, measured with 20V p-p 10 kHz sinewave input S/H Droop Rate<sup>1</sup> 0.2 μV/μs S/H Dielectric Absorption Error<sup>5</sup> ±0.005% of input voltage change

**DIGITAL OUTPUTS** General Tri-state CMOS HCT **Parallel Data** Positive true; unipolar binary, offset binary, or two's complement (see Table 1) End of Conversion (EOC) Positive true

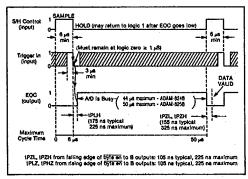

**DIGITAL INPUTS** General Standard TTL compatible, one unit load/line S/H Mode Control Logic 1 = SAMPLE (6 µs minimum) Logic 0 = HOLD (conversion time minimum); logic 1 to logic 0 transition time 10 ns maximum A/D Trigger Negative-going edge; logic 1 to logic 0 transition 50 ns maximum Low/High Byte Enable Logic 0 = enable Logic 1 = 3.5V min. @  $1 \mu A$ , HCT Logic 0 = 1.5V max. @ 1  $\mu$ A, HCT

#### **POWER REQUIREMENTS** +15V, ±3% 37 mA maximum -15V, ±3% 35 mA maximum $+5V, \pm 5\%$ 9 mA maximum **Power Dissipation** 0.9W

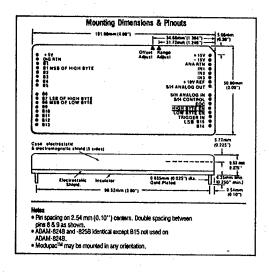

**ENVIRONMENTAL AND MECHANICAL Operating Temperature** 0°C to +70°C Storage Temperature -25°C to +85°C **Relative Humidity** 5% to 95% noncondensing to 40°C Shielding Electrostatic (RFI) 6 sides; Electrostatic (EMI) 5 sides Package Size 2.0" x 4.0" x 0.375" (50.8 x 101.6 x 9.53 mm)

#### Notes:

Doubles every 10°C, Traceable to NBS, calibrated on ± 10V range. Worst-case summation of S/H and A/D nonlinearity

Includes 6  $\mu$ s maximum for S/H acquisition and 44  $\mu$ s maximum for A/D.

At maximum throughput rate. The error decreases as sampling time is decreased.

5-10

SAMPLING ANALOG-TO-DIGITAL CONVERTERS

### Operation

The ADAM-824B and -825B interface directly to most commonly available input devices (multiplexers, amplifiers, etc.). The high impedance of the fast, fully buffered, unity gain S/H input amplifier minimizes source loading errors. Excellent hold-mode feedthrough performance is provided even at 10 kHz—the maximum information frequency of data that can be digitized at the module's 20 kHz sampling rate (single-channel application). For multichannel inputs, excellent feedthrough rejection is maintained by switching the multiplexer channels coincident with either edge of the S/H mode control.

Parallel data bits are driven by tri-state buffers and may be enabled in one or two bytes. (If the tri-state feature is not needed, normal binary outputs can be obtained by connecting the enable pins to ground.) To obtain two's complement, use B1 instead of B1 (the MSB). Maximum system throughput rate is attained by reading the output of an A/D conversion while the S/H is acquiring the next sample.

To operate with a single control pulse, connect the S/H mode control input to the A/D trigger, and observe the timing requirements for the S/H mode control (Figure 2).

Operating range is established by connecting the S/H output to the appropriate A/D input pins (see Table 1). These pins provide access to the S/H output (a low-impedance buffer amp) for arbitrary signal processing prior to A/D conversion. The S/H can be bypassed for applications requiring direct input to a low noise A/D converter.

Figure 2. ADAM-824B/5B Timing.

In most high accuracy applications the S/H, A/D, and related interfaces constitute the key subsystem of the data conversion process. By using an ADAM-series module that has been "worst-case" designed, the system engineer avoids the problems that commonly occur when transforming a 15-bit breadboard into a finished product.

End-to-end performance is not subject to the surprises that usually result from S/H output spikes, ground loops, timing problems, and so on. Offset is specified (and trimmed) as a single characteristic. The signal path from the S/H to the A/D is very short, minimizing noise pick-up, cross-talk, etc.; trim potentiometers and the bypass capacitors that filter power supply noise are in the module, not on the PC board. The module is EMI/RFI shielded.

The Integral S/H is a precision circuit similar to Analogic's model MP260, so the total S/H error is very small. Due to the module's low power dissipation, errors induced by self-heating of the module are negligible. Internal temperature rise is only 12.5°C above external ambient, much less than in many other A/D converters.

The resulting performance is exceptional. Figure 3 shows a dynamic crossplot taken for the ADAM-824B with worst-case inputs (small signals). This crossplot allows visual detection of very small errors (approaching 1/8 LSB). The unit displays differential nonlinearity that is well within the specified ± 1/2 LSB.

#### RANGE PROGRAMMING AND OUTPUT CODING A/D Input Connections Full Scale Input Range 0 to +5V Impedence 1.25kΩ IN 1 to IN 2 to IN 3 to S/H ANA OUT SIH ANA SIH ANA 0 (0 +10) ANA RTN SIH ANA ANA RTN -5V to +5V Ş/H ANA + 10V REF 2.5kΩ - 10V to +10V ANA RTN + 10V REF S/H ANA 5.QkΩ **Output Codes** ADAM-8248 (14 Bits) Unipolar Binary Unipolar Binar

\*For +5V FSR, divide voltage by two †For ±5V FSR, divide voltage by two

5-11

Calibration

Due to excellent long-term stability, these modules will rarely require re-calibration. They should, however, be re-adjusted when the selected FSR is changed. Offset should be zeroed prior to trimming the range.

- Offset Zeroing Procedure

1. Provide the S/H analog input voltage shown in the accompany-

- ing table.

2. Adjust the Offset pot until the module output code corresponds to 0V, with the LSB alternating equally between 0 and 1.

- Range Trimming Procedure (Gain Adjust)

1. Provide the S/H analog Input voltage shown in the accompanying table.

2. Adjust the Gain pot until the module output code is all 1's with the LSB alternating equally between 0 and 1.

#### Input Voltagest for Calibration

| Nominal FSR                                         | ADAM-8248 (14 BHs)                   |                                                  | ADAM-8258 (14 8ks)                  |                                                  |

|-----------------------------------------------------|--------------------------------------|--------------------------------------------------|-------------------------------------|--------------------------------------------------|

|                                                     | Offset                               | Range                                            | Offset                              | Range                                            |

| 0 to + 5V<br>0 to + 10V<br>-5 to + 5V<br>-10 to 10V | 153 μV<br>305 μV<br>305 μV<br>610 μV | +4.99954V<br>+9.99909V<br>+4.99909V<br>+9.99817V | 76 μV<br>153 μV<br>153 μV<br>305 μV | +4.99977V<br>+9.99954V<br>+4.99954V<br>+9.99909V |

# S/H ANALOG IN 111 111 111 111 Theoretical Code A/D Output Center 5ms/div.

The upper trace shows an input that ramps repetively from  $-9.77 \, \mathrm{mV}$  to  $+9.77 \, \mathrm{mV}$  and back very slowly in relation to the module's 20 kHz sampling rate. The module output is used to drive a digital-brainage converter, whose output is then shown on the lower trace. Thus each level on this staircase corresponds to a set of conversions made around a code center voltage, and the transitions show when the module togelse its LSB. This type of plot may be used to measure differential non-linearity (the most significant ATO performance parameter for most applications) and to determine by Inspection the existence of errors such as wide code, narrow code, missing code, non-monotolicity, etc. Because the input is dynamically changing, this type of test simulates actual operation very well.

Figure 3. ADAM-824B Crossplot Shows Highly Linear Performance.

#### **Ordering Guide**

Simply Specify

☐ ADAM-824B ☐ ADAM-825B 14-Bit Resolution 15-Bit Resolution

5-12

SAMPLING ANALOG-TO-DIGITAL CONVERTERS