# CMOS MICROCYCLE LENGTH CONTROLLER

IDT49C25 IDT49C25A

## **FEATURES:**

- Similar function to AMD's Am2925 bipolar controller with improved speeds and output drive over full temperature and voltage supply extremes

- Four microcode-controlled clock outputs allow clock cycle length control for 15 to 30% increase in system throughput. Microcode selects one of eight clock patterns from 3 to 10 oscillator cycles in length

- System controls for RUN/HALT and Single Step

- Switch-debounced inputs provide flexible halt controls

- · Low input/output capacitance

- 6pF inputs (typ.)

- 8pF outputs (typ.)

- CMOS power levels (1mW typ. static)

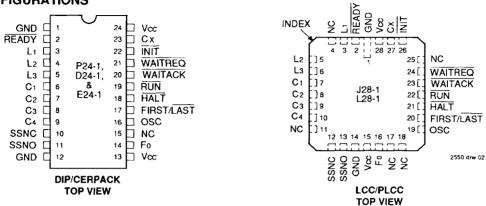

- Available in 300 mil 24-pin plastic and ceramic THINDIP, 28-pin LCC and PLCC packages and CERPACK

- · Both CMOS and TTL output compatible

- · Military product compliant to MIL-STD-883, Class B

## **DESCRIPTION:**

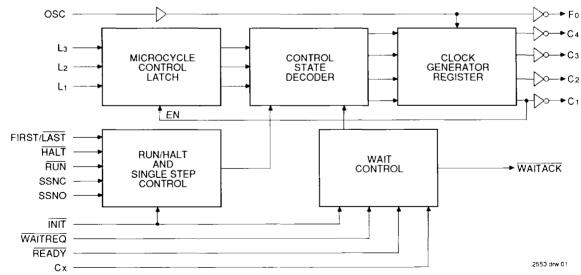

The IDT49C25/A are single-chip general purpose clock generator/drivers built using IDT's advanced CEMOS $^{\text{TM}}$ , a dual metal CMOS technology. It has microprogrammable clock cycle length to provide significant speed-up over fixed clock cycle approaches and meets a variety of system speed requirements.

The IDT49C25/A generate four different simultaneous clock out-put waveforms tailored to meet the needs of the IDT3900 CMOS family and other MOS and bipolar microprocessor-based systems. One of eight cycle lengths may be generated under microprogram control using the cycle length inputs, L1, L2 and L3.

A buffered oscillator output, Fo, is provided for external system timing in addition to the four microcode controlled clock outputs, C1, C2, C3 and C4.

System control functions include RUN, HALT, Single-Step, Initialize and Ready/Wait controls. In addition, the FIRST/LAST input determines where a halt occurs and the Cx input determines the end point timing of wait cycles. WAITACK indicates that the IDT49C25/A are in a wait state.

## **FUNCTIONAL BLOCK DIAGRAM**

CEMOS and MICROSLICE are trademarks of integrated Device Technology, Inc.

**APRIL 1990**

## PIN CONFIGURATIONS

## PIN DESCRIPTIONS

| Pin Names      | 1/0 | Description                                                                                                                                                                                                                                                 |

|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1, C2, C3, C4 | 0   | System clock outputs. These outputs are all active during every system clock cycle. Their timing is determined by clock cycle length controls: L1, L2 and L3.                                                                                               |

| L1, L2, L3     | ١   | Clock cycle length control inputs. These inputs receive the microcode bits that select the microcycle lengths. They form a control word which selects one of the eight microcycle waveform patterns F3 through F10.                                         |

| F <sub>0</sub> | 0   | The buffered oscillator output. Fo internally generates all of the timing edges for outputs C1, C2, C3, C4 and WAITACK. Fo rises just prior to all of the C1, C2, C3, C4 transitions.                                                                       |

| HALT and RUN   | 1   | Debounced inputs to provide HALT control. These inputs determine whether the output clocks run or not. A LOW input on HALT (RUN = HIGH) will stop all clock outputs.                                                                                        |

| FIRST/LAST     | ١   | HALT time control input. A HIGH input in conjunction with a HALT command will cause a halt to occur when $C_4 = LOW$ and $C_1 = C_2 = C_3 = HIGH$ (see clock waveforms). A LOW input causes a HALT to occur when $C_1 = C_2 = C_3 = LOW$ and $C_4 = HIGH$ . |

| SSNO and SSNC  | 1   | Single Step control inputs. These debounced inputs allow system clock cycle single stepping while HALT is activated LOW.                                                                                                                                    |

| WAITREQ        | 1   | The Wait Request active LOW input. When LOW, this input will cause the outputs to halt during the next oscillator cycle after the Cx input goes LOW.                                                                                                        |

| Сх             | ł   | Wait cycle control input. The clock outputs respond to a wait request one oscillator clock cycle after Cx goes LOW. Cx is normally tied to any one of C1, C2, C3 or C4.                                                                                     |

| WAITACK        | 0   | The Wait Acknowledge active LOW output. When LOW, this output indicates that all clock outputs are in the "WAIT" state.                                                                                                                                     |

| READY          | 1   | The READY active LOW input is used to continue normal clock output patterns after a wait state.                                                                                                                                                             |

| INIT           | 1   | The Initialize active LOW input. This input is intended for use during power-up initialization of the system. When LOW, all clock outputs run free regardless of the state of the Halt, Single Step, Wait Request and Ready inputs.                         |

| OSC            | I   | External oscillator input (TTL level input).                                                                                                                                                                                                                |

2550 toi 01

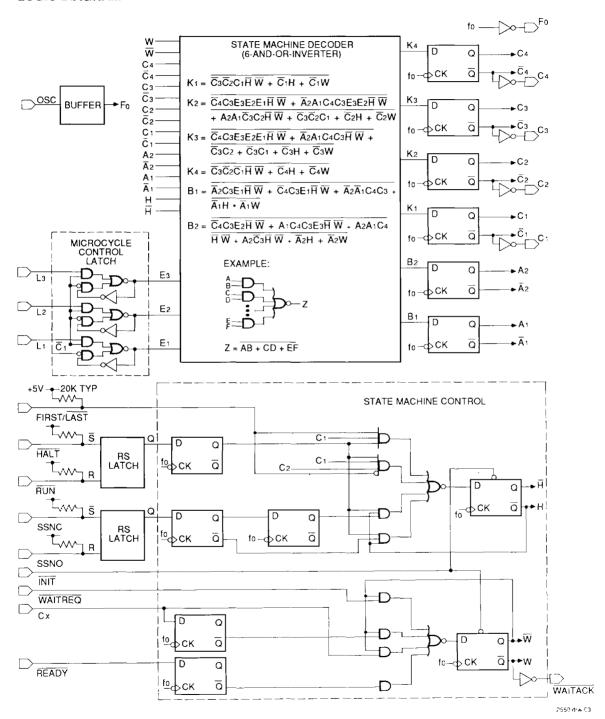

## **LOGIC DIAGRAM**

## 6

## ABSOLUTE MAXIMUM BATINGS(1)

| Symbol               | Rating                                     | Commercial   | Military     | Unit |

|----------------------|--------------------------------------------|--------------|--------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | -0.5 to +7.0 | ٧    |

| VTERM <sup>(3)</sup> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to Vcc  | -0.5 to Vcc  | ٧    |

| Та                   | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | ô    |

| Тѕтс                 | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| Рт                   | Power Dissipation                          | 0.5          | 0.5          | W    |

| lout                 | DC Output Current                          | 120          | 120          | mA   |

## NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability. No terminal voltage may exceed Vcc by +0.5V unless otherwise noted.

- 2. Inputs and Vcc terminals only.

- 3. Outputs and I/O terminals only

## CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Symbol Parameter <sup>(1)</sup> |           | Тур. | Max. | Unit |  |

|--------|---------------------------------|-----------|------|------|------|--|

| CIN    | Input Capacitance               | VIN = OV  | 6    | 10   | pF   |  |

| Cout   | Output Capacitance              | Vout = 0V | 8    | 12   | рF   |  |

#### NOTE:

2550 tol 03

1. This parameter is guaranteed by characterization data and not tested.

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: VLC = 0.2V; VHC = VCC - 0.2V

Commercial: TA = 0°C to +70°C, Vcc =  $5.0V \pm 5\%$ ; Military: TA = -55°C to +125°C, Vcc =  $5.0V \pm 10\%$

| Symbol | Parameter              | Test Condit                             | Min.                  | Typ. <sup>(2)</sup> | Max. | Unit               |    |

|--------|------------------------|-----------------------------------------|-----------------------|---------------------|------|--------------------|----|

| Vін    | Input HIGH Level       | Guaranteed Logic HIGH Level             |                       |                     | _    | _                  | ٧  |

| VIL    | Input LOW Level        | Guaranteed Logic LOW Level              |                       |                     |      | 0.8                | ٧  |

| iн     | Input HIGH Current     | Vcc = Max., Vin = Vcc                   | Vcc = Max., Vin = Vcc |                     |      |                    | μА |

| liL    | Input LOW Current      | Vcc = Max. SSNO, SSNC, RUN, HALT        |                       |                     |      | -1.0               | mA |

|        |                        | Vin = GND                               | FIRST/LAST            |                     |      | -1.5               |    |

|        |                        |                                         | Other Inputs          |                     | _    | -5                 | μА |

| Vik    | Clamp Diode Voltage    | Vcc = Min., IN = -18mA                  |                       | -0.7                | -1.2 | mA                 |    |

| Isc    | Short Circuit Current  | Vcc = Max. <sup>(3)</sup> , Vo = GN     | -60                   | -120                | _    | mA                 |    |

| Voн    | Output HIGH Voltage    | Vcc = 3V, VIN = VLc or VHc, IOH = -32μA |                       |                     | Vcc  | _                  | V  |

|        | Vcc = Min. IοH= -300μA |                                         | VHC                   | Vcc                 | _    |                    |    |

|        |                        | VIN = VIH or VIL                        | IOH = -3.0mA MIL.     | 2.4                 | 4.0  | _                  | 1  |

|        |                        |                                         | IOH= -5.0mA COM'L     | 2.4                 | 4.0  | -                  |    |

| Vol    | Output LOW Voltage     | VCC = 3V, VIN = VLC or VHC, IOL = 300µA |                       | -                   | GND  | VLC                | V  |

|        | Vcc = Min. IoL = 300μA |                                         | IOL = 300μA           |                     | GND  | VLC <sup>(4)</sup> |    |

|        |                        | VIN = VIH or VIL                        | VIN = VIH or VIL      |                     | _    | 0.5                |    |

|        |                        |                                         |                       |                     |      | 0.5                |    |

#### NOTES:

2550 tbi 04

- 1. For conditions shown as Min, or Max., use appropriate value specified under Electrical Characteristics for the applicable device type

- 2. Typical values are at VCC = 5.0V, +25°C ambient and maximum loading.

- Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed one second.

- 4. This parameter is guaranteed but not tested

## **POWER SUPPLY CHARACTERISTICS**

$VIC = 0.2V \cdot VHC = VCC - 0.2V$

| Symbol | Parameter                                                                                                                                                                                | Test Conditions <sup>(1)</sup>                                                              |   |     | Typ. <sup>(2)</sup> | Max. | Unit       |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---|-----|---------------------|------|------------|

| Icc    | Quiescent Power Supply<br>Current                                                                                                                                                        | Vcc = Max., Vin ≥ VHc, Vin ≤VLc                                                             |   |     | 0.2                 | 1.5  | mA         |

| Δlcc   | Quiescent Power Supply<br>Current TTL Inputs HIGH                                                                                                                                        | Vcc = Max., ViN = 3.4V <sup>(3)</sup>                                                       |   |     | 0.5                 | 2.0  | mA         |

| ICCD   | Dynamic Power Supply<br>Current <sup>(4)</sup>                                                                                                                                           | Vcc = Max.         Vin ≥ VHc           Outputs Open         Vin ≤ Vtc                       |   |     | 0.24                | 0.4  | mA/<br>MHz |

| lc     | Total Power Supply Current <sup>(5)</sup> VCC = Max., Outputs Open, fcP = OSC = 5MHz (50% duty cycle) READY, SSNO, WAITREQ, HALT, INIT = Vcc L1, L2, L3, SSNC, FIRST/LAST, RUN, Cx = GND |                                                                                             |   | 6.5 | 9.7                 | mA   |            |

|        |                                                                                                                                                                                          | VCC = Max. Outputs Open fcP = OSC = 5MHz SSNO, HALT = VC READY, WAITREC L1, L2, L3, SSNC, I | - | 8.5 | 16.6                |      |            |

NOTES:

- 2550 tol 35 1 For conditions shown as Max, or Min., use appropriate value specified under Electrical Characteristics for the applicable device type

- 2 Typical values are at Vcc = 5.0V, +25°C ambient.

- 3 Per TTL driven input (VIN = 3 4V); all other inputs at Vcc or GND.

- This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 5 Ic = IQUIESCENT + INPUTS + IDYNAMIC

- IC = ICC + AICC DHNT + ICCD (fCP/2 + fONO)

- Icc = Quiescent Current

- ΔICC = Power Supply Current for a TTL High Input (VIN = 3.4V)

- DH = Duty Cycle for TTL Inputs High

- Nt = Number of TTL Inputs at DH

- ICCD = Dynamic Current Caused by an Output Transition Pair (HLH or LHL)

- fcP = Clock Frequency for Register Devices (Zero for Non-Register Devices)

- fo = Output Frequency

- No = Number of Outputs at fo

- All currents are in milliamps and all frequencies are in megahertz.

## SWITCHING CHARACTERISTICS OVER OPERATING RANGE

|    |         |                                                                    |                        |             | IDT4 | 9Ç25 |      | IDT49C25A |      |      |      |      |

|----|---------|--------------------------------------------------------------------|------------------------|-------------|------|------|------|-----------|------|------|------|------|

|    |         |                                                                    |                        | Com'f. Mil. |      |      | Mil. | Com'l.    |      | Mil. |      | 1    |

|    | Symbol  | Parameter                                                          | Condition              | Min.        | Max. | Min. | Max. | Min.      | Max. | Min. | Max. | Unit |

| 1  | fMAX1   | Fo Frequency<br>(Cx Connected) <sup>(1, 6)</sup>                   | CL = 50pF<br>RL = 500Ω | 31          | _    | 31   | -    | 40        | _    | 40   |      | MHz  |

| 2  | fMAX2   | Fo Frequency<br>(Cx = HIGH) <sup>(6)</sup>                         |                        |             | -    |      | _    | _         | _    | _    |      | MHz  |

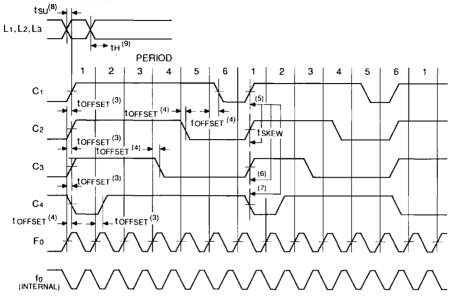

| 3  | toffset | F0 (I) to C1, C2, C3, C4 or WAITACK (I)                            |                        | _           | 8.5  | _    | 8.5  | _         | 6.0  |      | 6.0  | ns   |

| 4  | toffset | Fo (/) to C1, C2, C3, C4<br>or WAITACK ('\)                        |                        | _           | 17   | _    | 18   | _         | 11.5 | 1    | 12   | ns   |

| 5  | tskew   | C1 (1) to C2 (1)                                                   | ]                      | _           | 2    | _    | 2    |           | 1.5  | _    | 1.5  | ns   |

| 6  | tskew   | C1 (1) to C3 (1)                                                   | }                      |             | 2    | _    | 2    | -         | 1.5  | -    | 1.5  | ns   |

| 7  | tskew   | C1 (1) to C4 (N) Opposite Transition                               |                        | _           | 11   | _    | 11   | _         | 8.0  | _    | 8.0  | ns   |

| 8  | tsu     | L1, L2, L3, to C1 (1)                                              | ]                      | 6           |      | 6    |      | 5         | _    | 5    | 1    | ns   |

| 9  | tH      | L1, L2, L3, to C1 (1)                                              | ]                      | 8           | _    | 8    | _    | 6         | _    | 6    | _    | ns   |

| 10 | tsu     | Cx to Fo ( 🖋) <sup>(2)</sup>                                       | ]                      | 18          | _    | 18   | _    | 12        | _    | 12   |      | ns   |

| 11 | tH      | Cx to Fo ( )(2)                                                    | ]                      | 0           | -    | 0    | _    | 0         | _    | 0    | _    | ns   |

| 12 | tsu     | WAITREQ to Fo (1)(3)                                               | ]                      | 18          |      | 18   |      | 12        | 1    | 12   | 1    | ns   |

| 13 | tH      | WAITREQ to Fo (1)(3)                                               |                        | 0           |      | 0    |      | 0         |      | 0    |      | ns   |

| 14 | tsu     | READY to Fo (1)(3)                                                 | j                      | 18          | -    | 18   | _    | 12        | _    | 12   | -    | ns   |

| 15 | tH      | READY to Fo (1)(3)                                                 |                        | 0           |      | 0    | 1    | 0         | -    | 0    |      | ns   |

| 16 | tsu     | RUN, HALT ( $\checkmark$ ) to Fo ( $\checkmark$ ) <sup>(3,4)</sup> |                        | 18          |      | 18   | _    | 12        |      | 12   |      | ns   |

| 17 | tsu     | SSNC, SSNO to Fo $(\sqrt{s})^{(3,4)}$                              |                        | 18          | _    | 18   | -    | 12        | -    | 12   | _    | ns   |

| 18 | tsu     | FIRST/LAST to Fo (1)(5)                                            |                        | 18          | _    | 18   | _    | 12        | _    | 12   | 1    | ns   |

| 19 | tsu     | INIT (1) to Fo (1)(3)                                              |                        | 18          | _    | 18   | _    | 12        | _    | 12   | ì    | ns   |

| 20 | tw      | INIT LOW Pulse Width                                               |                        | 20          | _    | 25   | -    | 18        |      | 23   | 1    | ns   |

| 21 | tPLH    | INIT to WAITACK                                                    |                        | _           | 25   | _    | _27  |           | 16   | -    | 18   | ns   |

| 22 | tPLH    | OSC to Fo                                                          |                        |             | 13   | _    | 16   |           | 8.5  |      | 10.5 | ns   |

| 23 | tPHL    |                                                                    |                        |             | 13   |      | 16   | _         | 8.5  | _    | 10.5 | ns   |

## NOTES:

2550 tbl 06

- 1 The frequency guarantees apply with Cx connected to C1, C2, C3, C4 or HIGH. The Cx input load must be considered part of the 50pt/500Ω clock output loading.

- 2. These set-up and hold times apply to the Fo LOW-to-HIGH transition of the period in which Cx goes LOW.

- These inputs are synchronized internally. Failure to meet its may cause a 1/Fo delay but will not cause incorrect operation

These inputs are synchronized internally. Failure to meet its may cause a 1/Fo delay but will not cause incorrect operation

These inputs are "debounced" by an internal R-S flip-flop and are intended to be connected to manual break-before-make switches.

FIRST/LAST normally wired HIGH or LOW.

- 6 This parameter is guaranteed but not tested.

## **SWITCHING WAVEFORMS**

Figure 2. Normal Cycle Without Wait States (Pattern F6 Shown)

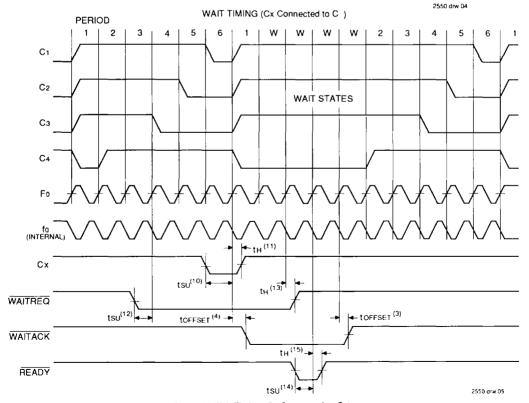

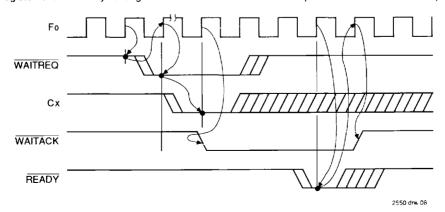

Figure 3. Wait Timing (CX Connected to C1)

## **DETAILED DESCRIPTION**

The IDT49C25/A are dynamically programmable general-purpose clock controllers. They can be logically separated into two parts — a state machine decoder and a state machine control section.

The state machine takes microcode information from the Microcycle Length (L) inputs L1, L2 and L3 and counts the fundamental frequency of the oscillator (OSC) to create the clock outputs F0, C1, C2, C3 and C4.

The clock outputs have a characteristic wave shape

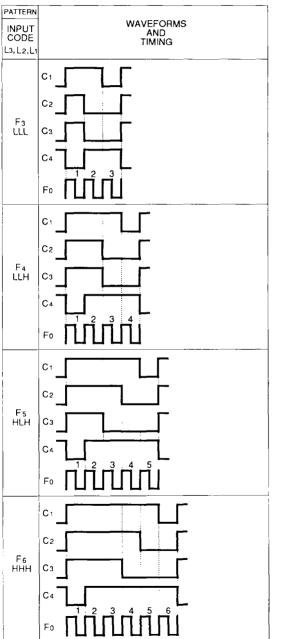

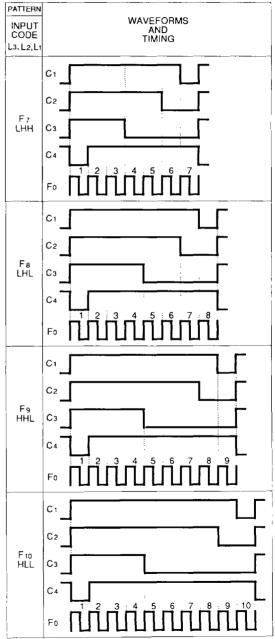

Figure 4. IDT49C25/A Clock Waveforms

2550 drw 06

relationship for each microcycle length. For example, C1 is always LOW only on the last F0 clock period of a microcycle and C4 is always LOW on the first. C3 has an approximate duty cycle of 50% and C2 is HIGH for all but the last two periods (see Figure 4).

The current state of the machine is contained in a register, part of which is the Clock Generator Register. C1, C2, C3 and C4 are the outputs of this register. These outputs and the outputs of the Microcycle Control Latch are fed into combinatorial logic to generate the next state. On each falling edge of the internal clock, the next state is entered into the current state register. The Microcycle Control Latch is latched when C1 is HIGH. This means that it will be loaded during the last state of each microcycle (C1 = C2 = C3 = LOW, C4 = HIGH). This internal latch selects one of eight possible microcycle lengths, F3 to F10.

The state machine control logic, which determines the mode of operation of the state machine, is intended to be connected to a front panel. There are four basic modes of operation of the IDT49C25/A comprised of RUN, HALT, WAIT and SINGLE STEP.

### SYSTEM TIMING

In the typical computer, the time required to execute different instructions varies. However, the time allotted to each instruction is the time that it takes to execute the longest instruction. The IDT49C25/A allows the user to dynamically vary the time allotted for each instruction, thereby allowing the user to realize a higher throughput.

## IDT49C25/A CONTROL INPUTS

The control inputs fall into two categories, microcycle length control and clock control. Microcycle length control is provided via the "L" inputs which are intended to be connected to the microprogram memory. The "L" inputs are used to select one of eight cycle lengths ranging from three oscillator cycles for pattern F3 to ten oscillator cycles for pattern F10. This information is always loaded at the end of the microcycle into the Microcycle Control Latch which performs the function of a pipeline register for the microcycle length microcode bits.

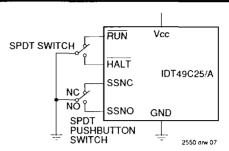

Figure 5. Switch Connection for RUN/HALT and Single Step

Therefore, the cycle length goes in the same microword as the instruction that it is associated with.

The clock control inputs are used to synchronize the microprogram machine with the external world and I/O devices. Inputs like RUN, HALT, SSNO and SSNC, which start and stop execution, are meant to be connected to switches on the front panel of the microprogrammed machine (see Figure 5). These inputs have internal pull-up resistors and are connected to an R-Sflip-flop in order to provide switch debouncing. The FIRST/LAST input is used to determine at what point of the microcycle the IDT49C25/A will halt when HALT or a SINGLE STEP is initiated. In most applications, the user wires this input HIGH or LOW, depending on the design.

When  $\overline{HALT}$  is held low ( $\overline{RUN}$  = HIGH), the state machine will start the halt mode on the last (C1 = LOW) or the first (C4 = LOW) state of the microcycle as determined by the FIRST/LAST input. When  $\overline{RUN}$  goes low ( $\overline{HALT}$  = HIGH), the state machine will resume the run mode.

The WAITREQ, Cx, READY and WAITACK signals are used to synchronize other parts of a computer system (memory, I/O devices) to the CPU by dynamically stretching the microcycle. For example, the CPU may access a slow peripheral that requires the data remain on the date bus for several microseconds. In this case, the peripheral pulls the WAITREQ line LOW. The Cx input lets the design specify when the WAITREQ line is sampled in the microcycle. This has a direct impact on how much time the peripheral has to

Figure 6. WAIT/READY Timing

-

respond in order to request a wait cycle (see Figure 6). The READY line is used by the peripheral to signal when it is ready to resume execution of the rest of the microcycle. The WAITACK line goes LOW on the next oscillator cycle after the Cx input goes LOW and remains LOW until the second oscillator cycle after READY goes LOW.

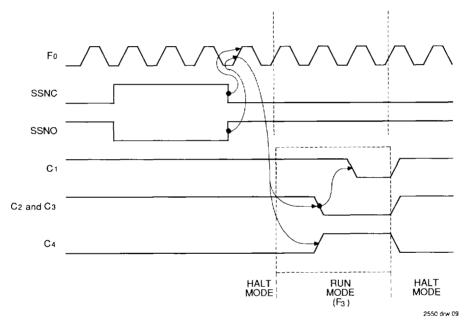

The SSNO and SSNC inputs are used to initiate the SINGLE STEP mode. These debounced inputs allow a single microcycle to occur while in the halt mode. SSNO (normally open) and SSNC (normally closed) are intended to be connected to a momentary SPDT switch. After SSNO has been high for one clock edge, the state machine will change to the next run mode. The microcycle will end on the first or last state of the microcycle, depending on the state of the FIRST/LAST.

## **AC TIMING SIGNAL REFERENCES**

Set-up and hold times in registers and latches are measured relative to the clock signals that drive them. In the IDT49C25/A, the external oscillator provides a free running clock signal that drives all the registers on the devices. This clock is provided for the user through the buffered output of Fo. Therefore, Fo is used as the reference of set-up, hold and clock-to-output times. However, for the Microcycle Control Latch, the set-up and hold times are referenced to the C1 output which is the buffered version of the latch enable. This reference is appropriate for the Microcycle Control Latch because, in a typical application, this latch is considered part of the pipeline register which is also driven by one of the "C" outputs.

Figure 7. Single Step Timing Sequence

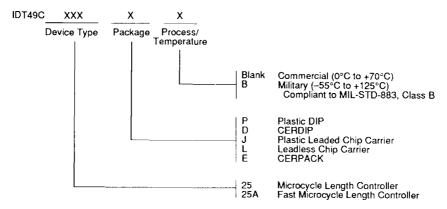

## **ORDERING INFORMATION**

2550 drw 10