### T7275C Quad Differential Line Receiver

#### **Features**

- Four line receivers per package

- Low pulse-width distortion

- CMOS level outputs

- 7 ns minimum input pulse width

- 8.0 ns maximum propagation delay

- 140 Mbits/s data rate at 50% duty cycle

- 0.6 V input sensitivity

- 0.8 V minimum common-mode range

- Single 5 V supply

- Low-power CMOS technology

- -40 ° C to +85 ° C operating temperature available

### **Description**

The T7275C Quad Differential Line Receiver integrated circuit is a quad differential input to CMOS output line receiver. It is functionally an ECL-level-to-CMOS converter. Direct interfacing to ECL signals is possible by ac coupling through a capacitor. The CMOS technology device is similar to the general-trade 26LS32 device; however, it has increased speed and decreased power consumption. By having four receivers in one T7275C device, circuit-board package count is reduced.

The typical propagation delay is 5 ns, and the typical common-mode operating range is 1.5 V. Input dc offset is less than 50 mV. The inputs typically have 10 mV of hysteresis.

The T7275C Line Receiver is compatible with many line drivers, including the AT&T T7274B and 41LG devices, and the general-trade 26LS31 device. The quad differential line receiver is available in a 16-pin, plastic DIP and a 16-pin, plastic SOJ package for surface mounting.

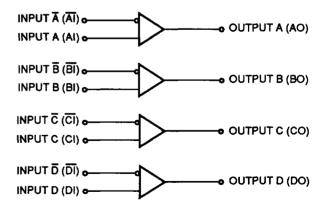

Figure 1. Block Diagram

## **Pin Information**

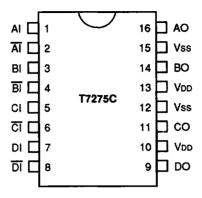

Figure 2. Pin Diagram

Table 1. Pin Descriptions

| Pin | Symbol | Type | Name/Function                 |  |  |  |

|-----|--------|------|-------------------------------|--|--|--|

| 1   | Al     | _    | A-Line Driver Input.          |  |  |  |

| 2   | ĀI     | ı    | Inverted A-Line Driver Input. |  |  |  |

| 3   | Bi     | 1    | B-Line Driver Input.          |  |  |  |

| 4   | BI     | 1    | Inverted B-Line Driver Input. |  |  |  |

| 5   | CI     | I    | C-Line Driver Input.          |  |  |  |

| 6   | CI     | 1    | Inverted C-Line Driver Input. |  |  |  |

| 7   | DI     |      | D-Line Driver Input.          |  |  |  |

| 8   | DI     | ı    | Inverted D-Line Driver Input. |  |  |  |

| 9   | DO     | 0    | D-Line Driver Output.         |  |  |  |

| 10  | Vaa    |      | 5 V Supply Pin.               |  |  |  |

| 11  | CO     | 0    | C-Line Driver Output.         |  |  |  |

| 12  | Vss    |      | Ground Pin.                   |  |  |  |

| 13  | VDD    |      | 5 V Supply Pin.               |  |  |  |

| 14  | во     | 0    | B-Line Driver Output.         |  |  |  |

| 15  | Vss    |      | Ground Pin.                   |  |  |  |

| 16  | AO     | 0    | A-Line Driver Output.         |  |  |  |

### **Absolute Maximum Ratings**

Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to Absolute Maximum Ratings for extended periods can adversely affect device reliability. External leads can be bonded or soldered safely at temperatures up to 300 ° C.

| Parameter                           | Symbol | Min | Max | Unit |

|-------------------------------------|--------|-----|-----|------|

| Power Supply Voltage                | VDD    |     | 7.0 | ٧    |

| Ambient Operating Temperature Range | TA     | -40 | 85  | , C  |

| Storage Temperature Range           | Tstg   | -40 | 125 | °C   |

| Power Dissipation                   | Pdis   | _   | 500 | mW   |

### **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. AT&T employs a human-body model (HBM) and a charged-device model (CDM) for ESD-susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for the CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and therefore can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters:

| HBM ESD Threshold |         |  |  |  |

|-------------------|---------|--|--|--|

| Device            | Voltage |  |  |  |

| T7275C            | >2000 V |  |  |  |

### **Typical Application**

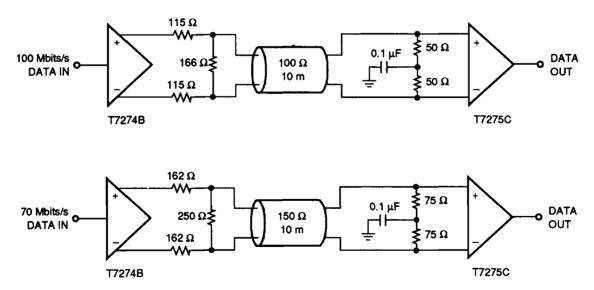

Figure 3. T7274B and T7275C in 100  $\Omega$  and 150  $\Omega$  Systems

#### **Electrical Characteristics**

$T_A = -40$  ° C to +85 ° C, (except as specified), or 0 ° C to 85 ° C (see the Ordering Information section),  $V_{DD} = 5.0 \text{ V} \pm 0.25 \text{ V}$

| Parameter                                                                          | Symbol              | Min  | Тур         | Max          | Unit |

|------------------------------------------------------------------------------------|---------------------|------|-------------|--------------|------|

| Output Voltages:                                                                   |                     |      |             |              |      |

| Low, lot = 12.5 mA                                                                 | Vol                 | _    | _           | 0.5          | V    |

| Low, $lol = 25 \text{ mA}$                                                         | Vol                 |      |             | 0.9          | V    |

| High, Iон = $-12.5$ mA                                                             | Vон                 | 4.25 | _           |              | V    |

| High, IoH = $-25 \text{ mA}$                                                       | Vон                 | 3.85 |             | _            | ٧    |

| Output Impedance                                                                   |                     |      | 15          | 30           | Ω    |

| Differential Input Voltages:                                                       |                     |      |             |              |      |

| Vo = VoL or Voн; 2.1 V < Vсм < 2.9 V*                                              | Vπ <sub>dc†</sub>   | 50   |             |              | mV   |

| 40 - 40E 01 40H, 2.1 4 40M 2.3 4                                                   | V <sub>THac</sub> ‡ | 0.6  | _           |              | ٧    |

| Input Voltages Applied to Any Output:                                              |                     |      |             |              |      |

| Low                                                                                | Vı∟                 | -0.5 | —           |              | V    |

| High                                                                               | ViH                 |      | —           | VDD + 0.5    | ٧    |

| Input Currents ( $-0.5 \text{ V} \le \text{Vin} \le \text{Vdd} + 0.5 \text{ V}$ ): |                     |      |             |              |      |

| Differential                                                                       | lild                |      | <del></del> | ±2.0         | μΑ   |

| Any Input                                                                          | lild                | -    |             | ±10          | μA   |

| Power Supply Current:                                                              |                     |      |             |              |      |

| dc Conditions§ (TA = $-40$ ° C to $+85$ ° C)                                       | loo                 | —    | 12.0        | 23.0         | mA   |

| dc Conditions (TA = 0 ° C to 85 ° C)                                               | loo                 |      | 12.0        | 20.0         | mA   |

| 100 Mbits/s (including load in Figure 4), Data =0101                               | loo                 |      | 80.0        | 95.0         | mA   |

| Power Dissipation Capacitance per Channel                                          | Срр                 |      | 32.0        |              | pF   |

| Input Capacitance                                                                  | Cı                  |      | 5.0         |              | pF   |

| Input Hysteresis                                                                   | VHYST               |      | 10          | <del>-</del> | m۷   |

<sup>\*</sup> Operation with 1 V < VcM < 4 V is possible, but with relaxed propagation delay and pulse-width distortion characteristics.

### **Timing Characteristics**

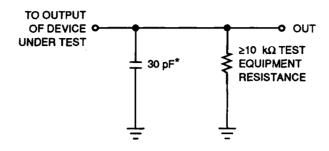

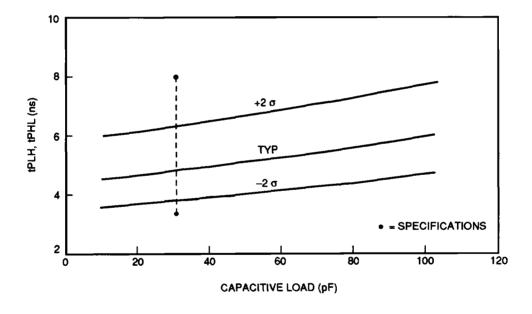

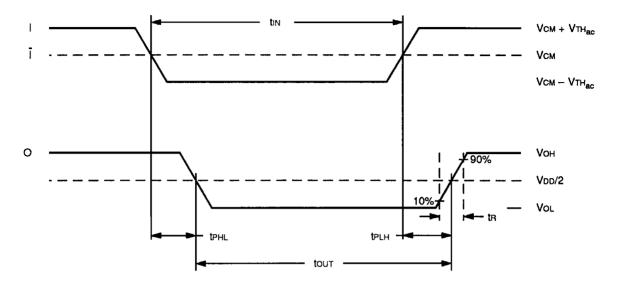

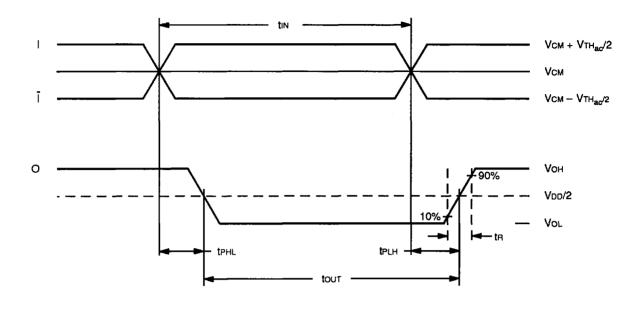

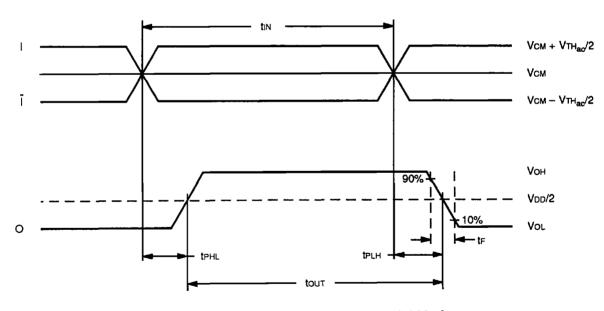

$T_A = -40\,^{\circ}$  C to  $+85\,^{\circ}$  C for T7275C-PL/EL (except as specified),  $V_{DD} = 5.0\,V \pm 0.25\,V$ ,  $0\,^{\circ}$  C to  $85\,^{\circ}$  C for T7275C-PE/EE, Figure 4, test circuit connected to output. The characteristics in this table apply to Figures 6 and 7. Input rise and fall times (10% to 90%) of less than 4 ns are necessary to meet maximum propagation delay and pulse-width distortion specifications.

| Symbol       | Parameter                          | Min      | Тур | Max | Unit | Comments           |

|--------------|------------------------------------|----------|-----|-----|------|--------------------|

|              | Propagation delay input to output  |          |     |     |      |                    |

| tphL<br>tpLH | For all input configurations       | 3.5      | 5.0 | 8.0 | ns   | 0 ° C to 85 ° C    |

|              |                                    |          |     |     |      |                    |

| tphl<br>tplh | For all input configurations       | 2.5      | 5.0 | 8.0 | ns   | -40 ° C to +85 ° C |

| tpwp         | Pulse-width Distortion, tin - tout |          | 100 | 500 | ps   | _                  |

| tr, tr       | Rise and Fall Times (10% to 90%)   | <u> </u> | 1.5 | 3.0 | ns   |                    |

| tin          | Input Pulse Width                  | 7        | _   |     | ns   |                    |

<sup>†</sup> dc threshold voltage. The minimum input differential voltage has zero noise immunity. This should be tested only in a static, noise-free environment.

<sup>‡</sup> To meet timing specifications.

<sup>§</sup> Pulling both differential inputs below 0.6 V powers down the device. The corresponding outputs go high.

## Timing Characteristics (continued)

### **Timing Diagrams**

<sup>\*</sup> Includes jig and measurement equipment capacitance. See Figure 7 for variation in propagation delay with capacitance.

Figure 4. Output Voltage and Propagation Delay Test Circuit

Figure 5. Propagation Delay vs. Loading Capacitance

# Timing Characteristics (continued)

### Timing Diagrams (continued)

Figure 6. Timing Waveforms, Single-Ended Mode

## Timing Characteristics (continued)

### Timing Diagrams (continued)

Figure 7. Timing Waveforms, Differential Mode

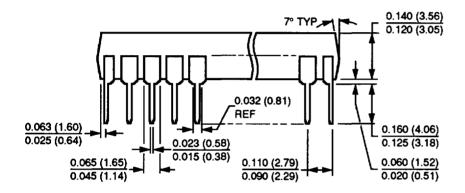

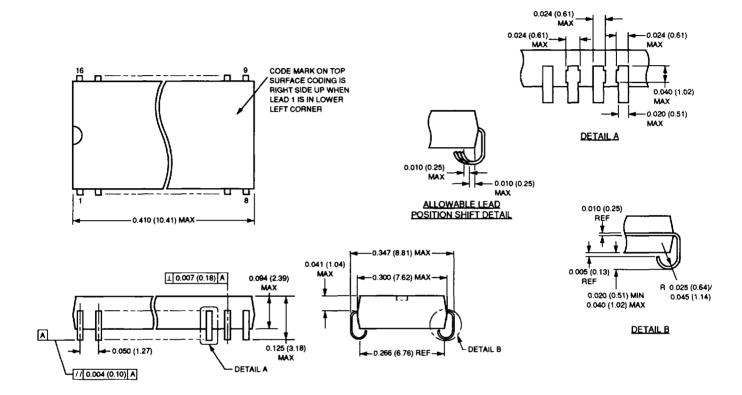

### **Outline Diagrams**

### 16-Pin, Plastic DIP

Dimensions are in inches and (millimeters).

Notes:

Meets JEDEC standards.

Index mark may be semicircular notch or circular dimple located in index area.

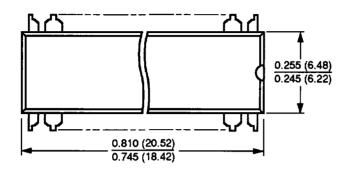

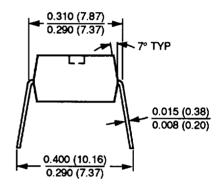

### Outline Diagrams (continued)

### 16-Pin, Plastic SOJ, Surface Mounting

Dimensions are in inches and (millimeters).

# **Ordering Information**

| Device Code | Package             | Temperature      | Comcode   |

|-------------|---------------------|------------------|-----------|

| T7275C-PE   | 16-Pin, Plastic DIP | 0 ° C to 85 ° C  | 106279755 |

| T7275C-EE   | 16-Pin, Plastic SOJ | 0 ° C to 85 ° C  | 106279730 |

| T7275C-PL   | 16-Pin, Plastic DIP | -40 °C to +85 °C | 106601321 |

| T7275C-EL   | 16-Pin, Plastic SOJ | -40 °C to +85 °C | 106279748 |

# Notes

For additional information, contact your AT&T Account Manager or the following:

U.S.A.: AT&T Microelectronics, Dept. 52AL040420, 555 Union Boulevard, Allentown, PA 18103

1-800-372-2447, FAX 215-778-4106 (In Canada: 1-800-553-2448, FAX 215-778-4106)

EUROPE: AT&T Microelectronics, AT&T Deutschland GmbH, Bahnhofstr. 27A, D-8043 Unterfoehring, Germany Tel. 089/950 86-0, Telefax 089/950 86-111

ASIA PACIFIC: AT&T Microelectronics Asia/Pacific, 14 Science Park Drive, #03-02A/04 The Maxwell, Singapore 0511

Tel. (65) 778-8833, FAX (65) 777-7495, Telex RS 42898 ATTM

JAPAN: AT&T Microelectronics, AT&T Japan Ltd., 31-11, Yoyogi 1-chome, Shibuya-ku, Tokyo 151, Japan

Tel. (03) 5371-2700, FAX (03) 5371-3556

SPAIN: AT&T Microelectronica de España, Poligono Industrial de Tres Cantos (Zona Oeste), 28770 Colmenar Viejo, Madrid, Spain

Tel. (34) 1-8071441, FAX (34) 1-8071420

AT&T reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1991 AT&T All Rights Reserved Printed in U.S.A.

December 1991 DS91-149SMOS (replaces DS90-074SMOS)