MAY 1987-REVISED MAY 1988

# TM024HAC4 1.048.576 BY 4-BIT DYNAMIC RAM MODULE

AC SINGLE-IN-LINE PACKAGE

(TOP VIEW)

1.048.576 x 4 Organization

- Single 5-V Supply (10% Tolerance)

- 24-Pin Single-In-line Package (SIP)

- Utilizes Four 1 Megabit Dynamic RAMs in Plastic Small-Outline J-Lead (SOJ) Packages

- Long Refresh Period . . . 8 ms (512 Cycles)

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Outputs

- Performance of Unmounted RAMs:

|              | ACCESS  | ACCESS  | READ   |

|--------------|---------|---------|--------|

|              | TIME    | TIME    | OR     |

|              | ROW     | COLUMN  | WRITE  |

|              | ADDRESS | ADDRESS | CYCLE  |

|              | (MAX)   | (MAX)   | (MIN)  |

| TMS4C1024-10 | 100 ns  | 45 ns   | 190 ns |

| TMS4C1024-12 | 120 ns  | 55 ns   | 220 ns |

| TMS4C1024-15 | 150 ns  | 70 ns   | 260 ns |

- Common CAS Control with Separate **Data-In and Data-Out Lines**

- Low Power Dissipation

- Operating Free-Air Temperature . . . 0 °C to 70°C

#### description

The TM024HAC4 is a 4,096K dynamic randomaccess memory module, organized as  $1,048,576 \times 4$  bits in a 24-pin single-in-line package (SIP). The SIP is composed of four TMS4C1024DJ, 1,048,576 × 1 bit dynamic RAMs, each in a 26/20-lead plastic small outline J-lead package (SOJ), mounted on top of a substrate together with decoupling capacitors mounted beneath the SOJs. The onboard capacitors eliminate the need for bypassing on the motherboard and offer superior performance

|     | 1    | OF VIE | ν,       |         |

|-----|------|--------|----------|---------|

|     |      |        |          |         |

| Α9  | (1)  | =      | ᅻ        |         |

| A8  | (2)  | ==     | ᅻ        |         |

| VCC | (3)  | =      | <b>†</b> |         |

| D1  | (4)  | =      | 7        | !       |

| Q1  | (5)  | =      | 7        |         |

| CAS | (6)  | =      | <b>?</b> |         |

| Α7  | (7)  |        | 7        |         |

| Α5  | (8)  | =      | 7        |         |

| A4  | (9)  | =      | 7        |         |

| D2  | (10) | =      | 7        | i II    |

| Q2  | (11) | =      | 7        | l li    |

| ₩   | (12) | =      | 7.       | <u></u> |

| A1  | (13) | =      | 7        |         |

| А3  | (14) | =      | 7        | l       |

| Α6  | (15) | =      | 7        | l il    |

| G3  | (16) | =      | 7        |         |

| D3  | (17) | =      | 7        |         |

| A2  | (18) | =      | 7        |         |

| _A0 | (19) | =      | 7        |         |

| RAS |      | =      | 7        |         |

| D4  | (21) |        | 7        |         |

| Q4  | (22) | =      | 7        |         |

| ٧ss | (23) | =      | Ť        |         |

| NC  | (24) | =      | Ť        |         |

|     |      |        | ı        | l il    |

|     |      |        | L        | لللللا  |

|       | PIN NOMENCLATURE      |

|-------|-----------------------|

|       | TM024HAC4             |

| A0-A9 | Address Inputs        |

| CAS   | Column-Address Strobe |

| D1-D4 | Data Inputs           |

| NC    | No Connection         |

| Q1-Q4 | Data Outputs          |

| RAS   | Row-Address Strobe    |

| vcc   | 5-V Supply            |

| VSS   | Ground                |

| ₩     | Write Enable          |

over equivalent leaded capacitors due to reduced lead inductance. With the elimination of bypass capacitors on the motherboard, reduced PC board size, and fewer plated through-holes, a cost savings can be realized. Each TMS4C1024DJ is described in its data sheet and is fully electrically tested and processed according to TI MIL-STD-883B flows (as amended for commercial applications) prior to assembly. After assembly onto the SIP, a further set of electrical tests is performed.

The TM024HAC4 features RAS access times of 100 ns, 120 ns, and 150 ns maximum.

The refresh period is extended to 8 milliseconds, and during this period each of the 512 rows must be strobed with RAS in order to retain data. CAS can remain high during the refresh sequence to conserve power.

PRODUCTION DATA decuments contain information

# TM024HAC4 1.048.576 BY 4-BIT DYNAMIC RAM MODULE

#### description (continued)

All inputs and outputs, including clocks, are compatible with Series 74 TTL. All addresses and data-in lines are latched on-chip to simplify system design. Data out is unlatched to allow greater system flexibility.

The TM024HAC4 is rated for operation from 0°C to 70°C.

#### operation

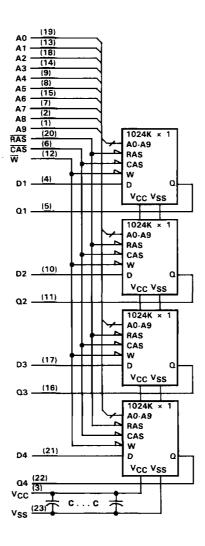

The TM024HAC4 operates as four TMS4C1024s connected as shown in the functional block diagram on the following page. Refer to the TMS4C1024 data sheet for details of its operation.

### specifications

For TMS4C1024DJ electrical specifications, refer to the TMS4C1024 data sheet.

### single-in-line package and components

PC substrate: 1,27 mm (0.05 in) nominal thickness; 0.005 in/in maximum warpage

Bypass capacitors: Multilaver ceramic

Leads: Tin/lead solder coated over phosphor-bronze

### functional block diagram

### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Voltage range on any pin (see Note 1) |

|---------------------------------------|

| Voltage range on VCC (see Note 1)     |

| Short circuit output current          |

| Power dissipation                     |

| Operating free-air temperature range  |

| Storage temperature range             |

<sup>†</sup>Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values in this data sheet are with respect to VSS.

#### recommended operating conditions

|     |                                      | MIN | NOM | MAX | UNIT |

|-----|--------------------------------------|-----|-----|-----|------|

| Vcc | Supply voltage                       | 4.5 | 5   | 5.5 | ٧    |

| VIH | High-level input voltage             | 2.4 |     | 6.5 | ٧    |

| VIL | Low-level input voltage (see Note 2) | - 1 |     | 0.8 | ٧    |

| TA  | Operating free-air temperature       | 0   |     | 70  | °C   |

NOTE 2: The algebraic convention, where the more negative (less positive) limit is designated as minimum, is used in this data sheet for logic voltage levels only.

### electrical characteristics over full ranges of recommended operating conditions (unless otherwise noted)

| PARAMETER |                             | TEST CONDITIONS                                                                                         | TM024HAC4-10 |      | TM024HAC4-12 |      | TMO24HAC4-15 |      | UNIT |

|-----------|-----------------------------|---------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|--------------|------|------|

|           | PARAMETER                   | TEST CONDITIONS                                                                                         | MIN          | MAX  | MIN          | MAX  | MIN          | MAX  | UNIT |

| Vон       | High-level output voltage   | I <sub>OH</sub> = -5 mA                                                                                 | 2.4          |      | 2.4          |      | 2.4          |      | <    |

| VOL       | Low-level output voltage    | I <sub>OL</sub> = 4.2 mA                                                                                |              | 0.4  |              | 0.4  |              | 0.4  | ٧    |

| 11        | Input current (leakage)     | $V_1 = 0 \text{ V to } 6.5 \text{ V}, V_{CC} = 5 \text{ V},$<br>All other pins = 0 V to V <sub>CC</sub> |              | ± 10 |              | ± 10 |              | ± 10 | μΑ   |

| ю         | Output current (leakage)    | $V_O = 0 \text{ V to } V_{CC}, V_{CC} = 5.5 \text{ V},$ CAS high                                        |              | ± 10 |              | ± 10 |              | ±10  | μΑ   |

| ICC1      | Read or write cycle current | Minimum cycle, V <sub>CC</sub> = 5.5 V                                                                  |              | 280  |              | 240  |              | 220  | mΑ   |

| ICC2      | Standby current             | After 1 memory cycle, RAS and CAS high, VIH = 2.4 V                                                     |              | 12   |              | 12   |              | 12   | mA   |

| Іссз      | Average refresh current     | Minimum cycle, V <sub>CC</sub> = 5.5 V,<br>RAS cycling, CAS high                                        |              | 260  |              | 220  |              | 200  | mA   |

| ICC4      | Average page current        | $t_{C(P)} = minimum, V_{CC} = 5.5 V,$<br>RAS low, CAS cycling                                           |              | 180  |              | 140  |              | 120  | mA   |

# capacitance over recommended supply voltage range and operating free-air temperature range, f= 1 MHz

|                    | PARAMETER                             | MIN | MAX | UNIT |

|--------------------|---------------------------------------|-----|-----|------|

| C <sub>i(A)</sub>  | Input capacitance, address inputs     |     | 24  | pF   |

| C <sub>i(D)</sub>  | Input capacitance, data inputs        |     | 5   | pF   |

| C <sub>i(RC)</sub> | Input capacitance, strobe inputs      |     | 28  | pF   |

| C <sub>i(W)</sub>  | Input capacitance, write-enable input |     | 28  | pF   |

| Co                 | Output capacitance                    |     | 7   | ρF   |

NOTE 3: V<sub>CC</sub> equal to 5.0 V  $\pm$  0.5 V and the bias on pins under test is 0.0 V.