# Advance Information

# 256K×4 CMOS Dynamic RAM

The MCM514258 is a  $1.2\mu$  CMOS high-speed, dynamic random access memory. It is organized as 262,144 four-bit words and fabricated with CMOS silicon-gate process technology. Advanced circuit design and fine line processing provide high performance, improved reliability, and low cost.

The MCM514258 requires only nine address lines; row and column address inputs are multiplexed. The device is packaged in standard 300 mil wide packages: dual-in-line package (DIP) and J-lead small outline package.

- Three-State Data Output

- Static Column Mode Capability

- TTL-Compatible Inputs and Output

- RAS Only Refresh

- CS Before RAS Refresh

- Hidden Refresh

- 512 Cycle, 8 ms Refresh

- Unlatched Data Out at Cycle End Allows Two Dimensional Chip Selection

- Fast Access Time (tRAC): MCM514258-85 = 85 ns (Maximum)

MCM514258-10 = 100 ns (Maximum)

MCM514258-12 = 120 ns (Maximum)

Low Active Power Dissipation: MCM514258-85 = 413 mW (Maximum)

MCM514258-10 = 358 mW (Maximum)

MCM514258-12 = 303 mW (Maximum)

Low Standby Power Dissipation: 11 mW (Maximum, TTL Levels)

5.5 mW (Maximum, CMOS Levels)

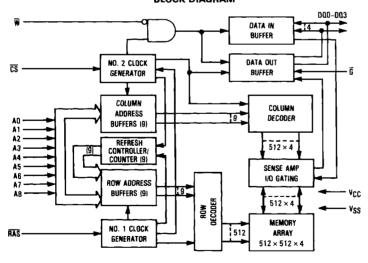

# BLOCK DIAGRAM

# MCM514258

P PACKAGE PLASTIC CASE 738A

J PACKAGE SMALL OUTLINE CASE 822

|                   | ASSIGN   |      |                  |

|-------------------|----------|------|------------------|

| ו                 | UAL-IN-I | -117 | =                |

| 000 E             | 1 •      | 20   | ]v <sub>SS</sub> |

| 001 <b>[</b>      | 2        | 19   | 3003             |

| ₩d                | 3        | 18   | 002              |

| RAS E             | 4        | 17   | ] <u>cs</u>      |

| NC E              | 5        | 16   | ) š              |

| A0 [              | 8        | 15   | ] A8             |

| A1 [              | 7        | 14   | ] A7             |

| A2 [              | 8        | 13   | ] A6             |

| A3 E              | 9        | 12   | ] A5             |

| v <sub>cc</sub> C | 10       | 11   | ] A4             |

| SN                | ALL OU   | TLI  | NE               |

| Dao E             | 1        | 26   | ov <sub>ss</sub> |

| DQ 1 [            | 2        | 25   | 003              |

| wd                | 3        | 24   | <b>D</b> 02      |

| RAS [             | 4        | 23   | I cs             |

| NC E              | 5        | 22   | Dē               |

| •                 |          |      |                  |

|                   |          |      | ł                |

| A0 [              |          |      | ] A8             |

| A1 [              | 10       | 17   | D A7             |

| A2 [              |          | 16   | ] A6             |

| A3 [              | 12       | 15   | ] A5             |

| v <sub>cc</sub> C | 13       | 14   | <b>A</b> 4       |

| PIN NAMES                    |

|------------------------------|

| A0-A8 Address Input          |

| DQ0-DQ3 Data Input/Output    |

| G Output Enable              |

| W Read/Write Input           |

| RAS Row Address Strobe       |

| CS Chip Select               |

| V <sub>CC</sub> Power (+5 V) |

| Vss Ground                   |

| NC No Connection             |

This document contains information on a new product. Specifications and information herein are subject to change without notice.

### **ABSOLUTE MAXIMUM RATINGS (See Note)**

| Rating                                         | Symbol                             | Value       | Unit |

|------------------------------------------------|------------------------------------|-------------|------|

| Power Supply Voltage                           | Vcc                                | ~1 to +7    | V    |

| Voltage Relative to VSS for Any Pin Except VCC | V <sub>in</sub> , V <sub>out</sub> | -1 to +7    | ٧    |

| Data Out Current                               | lout                               | 50          | mA   |

| Power Dissipation                              | PD                                 | 1           | W    |

| Operating Temperature Range                    | TA                                 | 0 to +70    | °C   |

| Storage Temperature Range                      | T <sub>stg</sub>                   | -55 to +150 | °C   |

NOTE: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to RECOMMENDED OPERATING CONDITIONS. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

### DC OPERATING CONDITIONS AND CHARACTERISTICS

$(V_{CC} = 5.0 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ Unless Otherwise Noted})$

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                | Symbol          | Min  | Тур | Max | Unit | Notes |

|------------------------------------------|-----------------|------|-----|-----|------|-------|

| Supply Voltage (Operating Voltage Range) | v <sub>cc</sub> | 4,5  | 5.0 | 5.5 | V    | 1     |

|                                          | VSS             | 0    | 0   | 0   |      |       |

| Logic High Voltage, All Inputs           | VIH             | 2.4  | -   | 6.5 | V    | 1     |

| Logic Low Voltage, All Inputs            | VIL             | -1.0 | -   | 0.8 | ٧    | 1     |

### DC CHARACTERISTICS

| Characteristic                                                                      | Symbol           | Min  | Max | Unit     | Notes |

|-------------------------------------------------------------------------------------|------------------|------|-----|----------|-------|

| V <sub>CC</sub> Power Supply Current                                                | lcc1             |      |     | mA       | 2     |

| MCM514258-85, t <sub>RC</sub> = 165 ns                                              |                  | -    | 75  |          | ì     |

| MCM514258-10, t <sub>RC</sub> = 190 ns                                              |                  | -    | 65  | 1        |       |

| MCM514258-12, t <sub>RC</sub> = 220 ns                                              | 1                |      | 55  | <u></u>  |       |

| V <sub>CC</sub> Power Supply Current (Standby) (RAS = CS = V <sub>IH</sub> )        | lcc2             |      | 2.0 | mA       |       |

| VCC Power Supply Current During RAS only Refresh Cycles (CS = VIH)                  | 1CC3             |      |     | mA       | 2     |

| MCM514258-85, $t_{RC} = 165$ ns                                                     |                  | -    | 75  | ļ        | ļ     |

| MCM514258-10, $t_{RC} = 190 \text{ ns}$                                             |                  | -    | 65  |          |       |

| MCM514258-12, t <sub>RC</sub> = 220 ns                                              |                  |      | 55  |          |       |

| VCC Power Supply Current During Static Column Mode Cycle (RAS = VIL)                | ICC4             | l    |     | mA       | 2     |

| MCM514258-85, $t_{SC} = 50 \text{ ns}$                                              |                  | -    | 75  |          |       |

| MCM514258-10, $t_{SC} = 55$ ns                                                      |                  | -    | 65  |          |       |

| MCM514258-12, t <sub>SC</sub> ≈ 70 ns                                               |                  |      | 55  | <u> </u> |       |

| V <sub>CC</sub> Power Supply Current (Standby) (RAS = CS = V <sub>CC</sub> - 0.2 V) | _ lcc5_          |      | 1.0 | mA       |       |

| VCC Power Supply Current During CS Before RAS Refresh Cycle                         | 1 <sub>CC6</sub> |      |     | mA       | 2     |

| MCM514258-85, t <sub>RC</sub> = 165 ns                                              |                  | -    | 75  |          | l     |

| MCM514258-10, t <sub>RC</sub> = 190 ns                                              |                  | -    | 65  |          | į     |

| MCM514258-12, $t_{RC} = 220 \text{ ns}$                                             |                  | -    | 55  |          |       |

| Input Leakage Current (0 V≤Vin≤6.5 V)                                               | likg(I)          | - 10 | 10  | μА       |       |

| Output Leakage Current (CS = V <sub>IH</sub> , 0 V ≤ V <sub>OUT</sub> ≤ 5.5 V)      | likg(0)          | - 10 | 10  | μΑ       |       |

| Output High Voltage (IOH = -5 mA)                                                   | ∨он              | 2.4  | _   | ٧        |       |

| Output Low Voltage (I <sub>OL</sub> = 4.2 mA)                                       | VOL              | -    | 0.4 | V        |       |

# $\textbf{CAPACITANCE} \ \, (\text{f} = 1.0 \ \text{MHz}, \ \text{T}_{\mbox{A}} = 25 \ ^{\circ}\text{C}, \ \ \text{V}_{\mbox{CC}} = 5 \ \text{V}, \ \ \text{Periodically Sampled Rather Than 100\% Tested})$

| Parameter                                                         | Symbol             | Max | Unit | Notes |

|-------------------------------------------------------------------|--------------------|-----|------|-------|

| Input Capacitance A0-                                             | 48 C <sub>in</sub> | 5   | ρF   | 3     |

| G, RAS, CS,                                                       | ₩                  | 7   | pF   | 3     |

| Output Capacitance (CS = V <sub>IH</sub> to Disable Output) DQ0-D | D3 Cout            | 7   | ρF   | 3     |

### NOTES:

- 1. All voltages referenced to VSS.

- 2. Current is a function of cycle rate and output loading; maximum current is measured at the fastest cycle rate with the output open.

- 3. Capacitance measured with a Boonton Meter or effective capacitance calculated from the equation: C=IΔt/ΔV.

# **AC OPERATING CONDITIONS AND CHARACTERISTICS**

$(V_{CC} = 5.0 \text{ V} \pm 10\%, T_A = 0 \text{ to } 70^{\circ}\text{C}, \text{ Unless Otherwise Noted})$

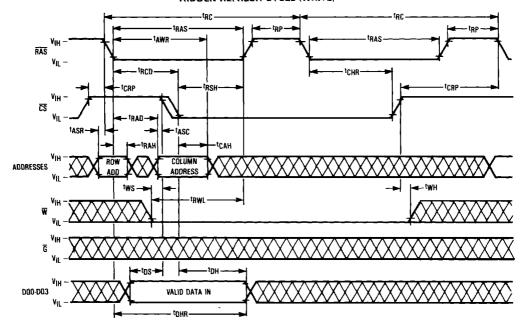

### READ, WRITE, AND READ-MODIFY-WRITE CYCLES (See Notes 1, 2, 3, and 4)

| Doromotov                                       | Syr               | Symbol            |     | MCM514258-85 |      | 14258-10 | MCM514258-12 |         |      | Ī     |

|-------------------------------------------------|-------------------|-------------------|-----|--------------|------|----------|--------------|---------|------|-------|

| Parameter                                       | Standard          | Alternate         | Min | Max          | Min  | Max      | Min          | Max     | Unit | Notes |

| Random Read or Write Cycle Time                 | TRELREL           | tRC               | 165 | -            | 190  | _        | 220          | -       | กร   | 5     |

| Read-Modify-Write Cycle Time                    | TRELREL           | tRMW              | 225 | -            | 255  | _        | 295          | _       | ns   | 5     |

| Static Column Mode Cycle Time                   | †AVAV             | †SC               | 50  |              | 55   | -        | 65           | -       | ns   |       |

| Static Column Mode Read-Modify-Write Cycle Time | <sup>†</sup> AVAV | <sup>t</sup> SRMW | 110 | -            | 115  | -        | 135          |         | ns   |       |

| Access Time from RAS                            | †RELQV            | <sup>1</sup> RAC  | _   | 85           | _    | 100      | _            | 120     | ns   | 6, 7  |

| Access Time from CS                             | †CELQV            | tCAC              | _   | 30           | _    | 30       | _            | 35      | ns   | 6, 8  |

| Access Time from Column Address                 | tAVQV             | tAA               | _   | 45           |      | 50       |              | 60      | ns   | 6, 9  |

| Access Time from Last Write                     | tWLQV             | tALW              |     | 85           |      | 95       |              | 115     | ns   | 6, 10 |

| CS to Output in Low-Z                           | tCELQX            | tCLZ              | 5   |              | 5    |          | 5            | -       | ns   | 6     |

| Output Buffer and Turn-Off Delay                | †CEHQZ            | _tOFF_            | 0   | 30           | 0    | 30       | 0            | 35      | ns   | 11    |

| Output Data Hold Time from Column Address       | tAXQX             | tAOH              | 5   | _            | 5    | _        | 5            | ~       | ns   |       |

| Output Data Enable Time from Write              | twhqv             | tow               | -   | 30           | _    | 30       |              | 35      | ns   |       |

| Transition Time (Rise and Fall)                 | tŢ                | tī                | 3   | 50           | 3    | 50       | 3            | 50      | ns   |       |

| RAS Precharge Time                              | †REHREL           | tRP               | 70  |              | 80   |          | 90           | -       | ns   |       |

| RAS Pulse Width                                 | †RELREH           | tRAS              | 85  | 10,000       | 100  | 10,000   | 120          | 10,000  | ns   |       |

| RAS Pulse Width (Static Column Mode)            | tRELREH           | tRASC             | 85  | 100,000      | 100  | 100,000  | 120          | 100,000 | ns   |       |

| CS to RAS Hold Time                             | †CELREH           | †RSH              | 30  | _            | 30   | -        | 35           | ~       | ns   |       |

| RAS to CS Hold Time                             | †RELCEH           | †CSH              | 85  | -            | 100  | -        | 120          | -       | ns   |       |

| CS Pulse Width                                  | †CELCEH           | tcs               | 30  | 10,000       | 30   | 10,000   | 35           | 10,000  | ns   |       |

| CS Pulse Width (Static Column Mode)             | †CELCEH           | tcsc              | 30  | 100,000      | 30   | 100,000  | 35           | 100,000 | ns   |       |

| RAS to CS Delay Time                            | TRELCEL           | †RCD              | 25  | 55           | 25   | 70       | 25           | 85      | ns   | 12    |

| RAS to Column Address Delay Time                | tRELAV            | tRAD              | 20  | 40           | 20   | 50       | 20           | 60      | ns   | 13    |

| CS to RAS Precharge Time                        | tCEHREL           | tCRP              | 10  |              | 10   |          | 10           |         | ns   |       |

| CS Precharge Time                               | *CEHCEL           | tCPN              | 15  | -            | 15   |          | 20           |         | ns   |       |

| CS Precharge Time (Static Column Mode)          | †CEHCEL           | <sup>t</sup> CP   | 10  |              | 10   | -        | 15           |         | ns   |       |

| Row Address Setup Time                          | tAVREL            | tasr.             | 0   | -            | 0    | -        | 0            | _       | ns   |       |

| Row Address Hold Time                           | tRELAX            | tRAH              | 15  |              | 15   |          | 15           |         | ns   |       |

| Column Address Setup Time                       | †AVCEL_           | _tASC_            | 0   |              | _ D_ | l        | 0            |         | ns   |       |

| Column Address Hold Time                        | †CELAX            | <sup>t</sup> CAH  | 20  |              | 20   |          | 25           | -       | ns   |       |

| Write Address Hold Time Referenced to RAS       | tRELAX            | t <sub>AWR</sub>  | 65  |              | 75   |          | 90           | ~       | ns   |       |

| Column Address Hold Time Referenced to RAS      | tRELAX            | tAR               | 100 |              | 115  |          | 140          | -       | ns   |       |

| Column Address to RAS Lead Time                 | †AVREH            | tRAL              | 45  |              | 50   |          | 60           | ~       | ns   |       |

(continued)

# NOTES:

- 1. VIH min and VIL max are reference levels for measuring timing of input signals. Transition times are measured between VIH and VIL.

- 2. An initial pause of 200 µs is required after power-up followed by 8 RAS cycles before proper device operation is guaranteed.

- 3. The transition time specification applies for all input signals. In addition to meeting the transition rate specification, all input signals must transmit between V<sub>IH</sub> and V<sub>IL</sub> (or between V<sub>IH</sub> and V<sub>IH</sub>) in a monotonic manner.

- 4. AC measurements  $t_T \approx 5.0$  ns.

- The specifications for t<sub>RC</sub> (min) and t<sub>RMW</sub> (min) are used only to indicate cycle time at which proper operation over the full temperature range (0°C ≤ T<sub>A</sub> ≤70°C) is assured.

- Measured with a current load equivalent to 2 TTL (-200 μA, +4 mA) loads and 100 pF with the data output trip points set at VOH = 2.0 V and VOL = 0.8 V.

- Assumes that t<sub>RCD</sub>≤t<sub>RCD</sub> (max).

- Assumes that t<sub>RCD</sub>≥t<sub>RCD</sub> (max).

- Assumes that t<sub>RAD</sub>≥t<sub>RAD</sub> (max).

- Assumes that t<sub>LWAD</sub> ≤ t<sub>LWAD</sub> (max).

- tOFF (max) and/or tGZ define the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 12. Operation within the t<sub>RCD</sub> (max) limit ensures that t<sub>RAC</sub> (max) can be met. t<sub>RCD</sub> (max) is specified as a reference point only; if t<sub>RCD</sub> is greater than the specified t<sub>RCD</sub> (max) limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 13. Operation within the t<sub>RAD</sub> (max) limit ensures that t<sub>RAD</sub> (max) can be met. t<sub>RAD</sub> (max) is specified as a reference point only; if t<sub>RAD</sub> is greater than the specified t<sub>RAD</sub> (max), then access time is controlled exclusively by t<sub>AA</sub>.

### READ, WRITE, AND READ-MODIFY-WRITE CYCLES (Continued)

|                                                     | Syn                 | nbol             | MCM5 | 14258-85 | MCM514258-10 |     | MCM514258-12 |     |      | Notes |

|-----------------------------------------------------|---------------------|------------------|------|----------|--------------|-----|--------------|-----|------|-------|

| Parameter                                           | Standard            | Aiternate        | Min  | Max      | Min          | Max | Min          | Max | Unit | MOTES |

| Column Address Hold Time Referenced to RAS          | †REHAX              | †AH              | 10   |          | 10           |     | 15           |     | ns   | 14    |

| Last Write to Column Address Delay Time             | †WLAV               | tLWAD            | 25   | 40       | 25           | 45  | 30           | 55  | ns   | 15    |

| Last Write to Column Address Hold Time              | †WLAX               | tAHLW            | 85   | _        | 95           | _   | 115          | _   | ns   |       |

| Read Command Setup Time Referenced to CS            | *WHCEL              | tRCS             | 0    |          | 0            |     | 0            | -   | ns   |       |

| Read Command Hold Time Referenced to CS             | †CEHWX              | †RCH             | 0    |          | 0            | _   | 0            | _   | ns   | 16    |

| Read Command Hold Time Referenced to RAS            | <sup>t</sup> REHWX  | tRRH             | 0    | _        | 0            | _   | 0            | -   | ns   | 16    |

| Write Command Hold Time (Output Data Disable)       | <sup>‡</sup> CEHWH  | t₩H              | 0    |          | 0            | _   | 0            | _   | ns   | 17    |

| Write Command Hold Time Referenced to RAS           | †RELWH              | †WCR             | 65   |          | 75           |     | 90           |     | ns   |       |

| Write Command Pulse Width                           | tWLWH               | twp              | 20   | _        | 20           | _   | 25           | _   | ns   |       |

| Write Inactive Time                                 | ¹WHWL               | tWI              | 10   | _        | 10           | -   | 15           | _   | ns   |       |

| Write Command to RAS Lead Time                      | tWLREH              | tRWL             | 20   | _        | 25           | _   | 30           | -   | ns   |       |

| Write Command to CS Lead Time                       | †WLCEH              | tCWL             | 20   | _        | 25           | _   | 30           | -   | ns   |       |

| Data in Setup Time                                  | †DVCEL              | tos              | 0    |          | 0            | _   | 0            | -   | ns   | 18    |

| Data in Hold Time                                   | tCELDX              | †DH              | 20   |          | 20           |     | 25           |     | ns   | 18    |

| Data in Hold Time Referenced to RAS                 | †RELDX              | †DHR             | 65   | _        | 75           | _   | 90           | -   | ns   |       |

| Refresh Period                                      | †RVRV               | tRFSH            | -    | 8        | -            | 8   | _            | 8   | ms   |       |

| Write Command Setup Time (Output Data Disable)      | †WLCEL              | tws              | 0    |          | 0            |     | 0            |     | ns   | 17    |

| CS to Write Delay (RMW Cycle)                       | †CELWL              | tCWD             | 65   | _        | 65           | -   | 75           |     | ns   | 17    |

| RAS to Write Delay (RMW Cycle)                      | †RELWL              | tRWD             | 120  |          | 135          | _   | 160          | -   | ns   | 17    |

| Column Address to Write Delay Time                  | †AVWL               | †AWD             | 80   |          | 85           |     | 100          | -   | ns   | 17    |

| CS Setup Time for CS Before RAS Refresh             | <sup>t</sup> CELREL | tCSR             | 10   | -        | 10           |     | 10           | _   | ns   |       |

| CS Hold Time for CS Before RAS Refresh              | <sup>t</sup> RELCEH | tCHR             | 30   |          | 30           | _   | 30           |     | ns   |       |

| RAS Precharge to CS Active Time                     | TREHCEL             | tRPC             | 0    |          | 0            |     | 0            |     | ns   |       |

| CS Precharge Time for CS Before RAS Counter<br>Test | <sup>†</sup> CEHCEL | <sup>‡</sup> CPT | 50   | _        | 50           |     | 60           | -   | ns   |       |

| RAS Hold Time Referenced to G                       | tGLREH              | tROH             | 20   |          | 20           | _   | 20           | _   | ns   |       |

| G Access Time                                       | tGLQV               | †GA              | _    | 30       |              | 30  | _            | 35  | ns   |       |

| G to Data Delay                                     | tGHDX               | †GD              | 25   |          | 25           | -   | 30           | -   | ns   |       |

| Output Buffer Turn-Off Delay Time from G            | tGHQZ               | †GZ              | 0    | 25       | 0            | 25  | 0            | 30  | ns   | 11    |

| G Command Hold Time                                 | tWLGL               | <sup>t</sup> GH  | 25   | _        | 25           |     | 30           | _   | ns   |       |

### NOTES:

- 14. tan is the condition to latch the column address when RAS transitions from low to high.

- 15. Operation within the specified tLWAD (max) limit ensures that tALW (max) can be met. tLWAD (max) is specified as a reference point only; if tLWAD is greater than the specified tLWAD (max) limit, then access time is controlled exclusively by tAA.

- 16. Enter tRRH or tRCH must be satisfied for a read cycle.

- 17. tWH. tWS, tRWD, tcWD, and tAWD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only; if tWS≥tWS (min) and tWH≥tWH (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if tcWD≥tcWD (min), tRWD≥tRWD (min), and tAWD≥tAWD (min), the cycle is a read-modify-write cycle and the data out will contain data read from the selected cell. If neither of these sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- These parameters are referenced to CS leading edge in random write cycles and to W leading edge in delayed write or read-modify-write cycles.

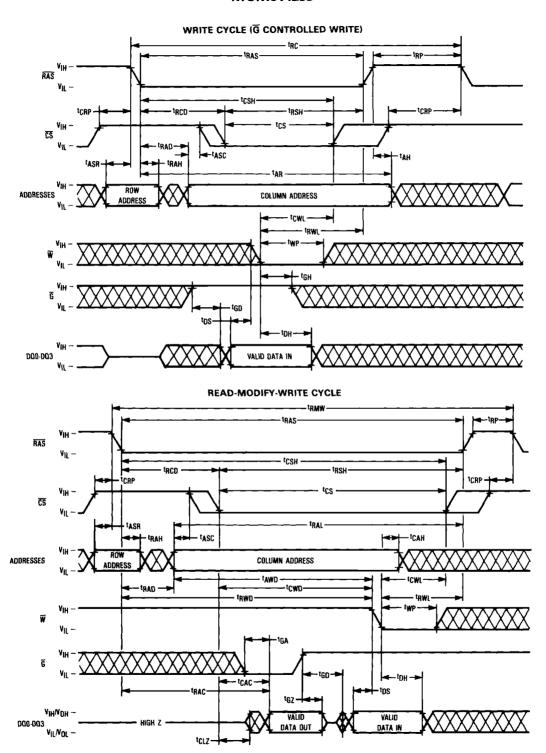

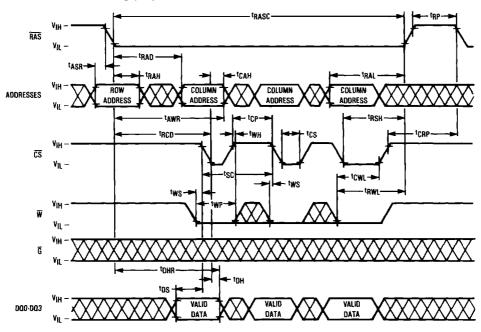

# STATIC COLUMN MODE READ CYCLE

# STATIC COLUMN MODE WRITE CYCLE (EARLY WRITE)

### STATIC COLUMN MODE READ-MODIFY-WRITE CYCLE RAS V<sub>IL</sub> -COLUMN COLUMN ADDRESSES ADDRESS ADDRESS **≠**-tasc ¹CAH-➤ -tRAL--tsrmw tCRP--trad --€-†LWAD -<sup>t</sup>RWL CS · trcd tcwp-·tawD tawdtga-VIH/VOH -VALID VALID 000 003 DATA IN AITNOT -VALIB VALID tCLZ→ DATA OUT DATA OUT STATIC COLUMN MODE READ/WRITE MIXED CYCLE VIH-RAS COLUMN COLUMN COLUMN ADDRESSES ADDRESS ADDRESS ADDRESS - tasc LWAD. VIH -CS VIL-1AWD YIH ~ VIL tALW 1GA tGA -tCAC-< HOA<sup>‡</sup>> HOA ¹GD → VIHNOH -VALID VALIŌ 000-003 DATA OUT AIFWOF -

# RAS ONLY REFRESH CYCLE (W and G are Don't Care)

# CS BEFORE RAS REFRESH CYCLE (W, G, and A0-A8 are Don't Care)

### HIDDEN REFRESH CYCLE (READ)

# HIDDEN REFRESH CYCLE (WRITE)

# CS BEFORE RAS REFRESH COUNTER TEST CYCLE RAS VIH ~ READ CYCLE COLUMN **ADDRESS** ← tclz-> VALID DATA OUT ADDRESS D00-D03 VII - -VALID DATA IN READ-MODIFY WRITE CYCLE COLUMN + trcs D00-D03 VIL/VOH --

#### **DEVICE INITIALIZATION**

On power-up an initial pause of 200 microseconds is required for the internal substrate generator pump to establish the correct bias voltage. This is to be followed by a minimum of eight active cycles of the row address strobe (clock) to initialize the various dynamic nodes internal to the device. During an extended inactive state of the device (greater than 4 milliseconds with device powered up), the wake up sequence (8 active cycles) will be necessary to assure proper device operation.

### ADDRESSING THE RAM

The nine address pins on the device are time multiplexed with two separate 9-bit address fields that are strobed at the beginning of the memory cycle by two clocks (active negative) called the row address strobe (RAS) and the column address strobe (CS). A total of 18 address bits will decode one of the 262, 144 cell locations in the device. The column address strobe follows the row address strobe by a specified minimum and maximum time called "tRCD," which is the row to column strobe delay. This time interval is also referred to as the multiplex window which gives flexibility to a system designer to set up his external addresses into the RAM. These conditions have to be met for normal read or write cycles. This initial portion of the cycle accomplishes the normal addressing of the device. There are, however, other variations in addressing the RAM, the refresh modes (RAS only refresh; CS before RAS refresh; hidden refresh), another mode called static column mode allows the user to column access the 512 bits within a selected row. The refresh mode and static column mode operations are described in more detail later on.

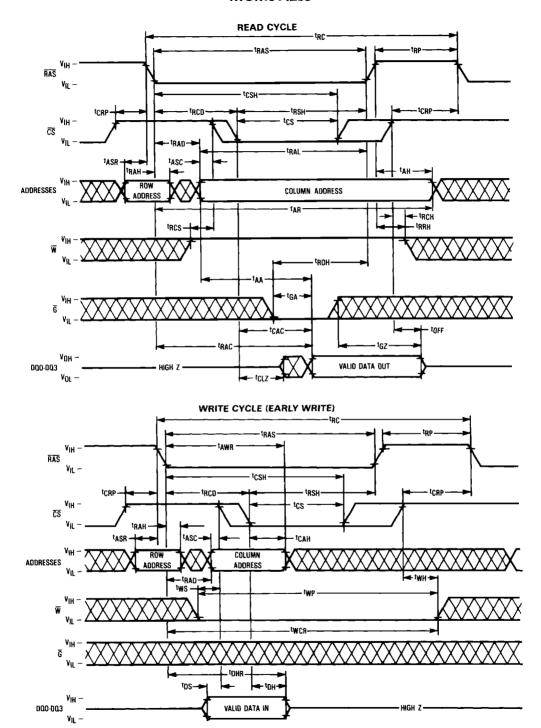

# READ CYCLE

A read cycle is referred to as a normal read cycle to differentiate it from a static column mode read cycle, a read-whilewrite cycle, and read-modify-write cycle which are covered in a later section.

The memory read cycle begins with the row addresses valid and the RAS clock transitioning from VIH to the VIL level. The CS clock must also make a transition from VIH to the VIL level at the specified tRCD timing limits when the column addresses are latched. Both the RAS and CS clocks trigger a sequence of events which are controlled by several delayed internal clocks. Also, these clocks are linked in such a manner that the access time of the device is independent of the address multiplex window. The only stipulation is that the CS clock must be active before or at the tRCD maximum specification for an access (data valid) from the RAS clock edge to be guaranteed (tRAC). If the tRCD maximum condition is not met, the access (tCAC) from the CS clock active transition will determine read access time. The external CS signal is ignored until an internal RAS signal is available. This gating feature on the CS clock will allow the external CS signal to become active as soon as the row address hold time (tRAH) specification has been met and defines the tRCD minimum specification. The time difference between tRCD minimum and tRCD maximum can be used to absorb skew delays in switching the address bus from row to column addresses and in generating the CS clock.

Once the clocks have become active, they must stay active for the minimum (tpAS) period for the  $\overline{RAS}$  clock and the minimum (tpS) period for the  $\overline{CS}$  clock. The  $\overline{RAS}$  clock must stay inactive for the minimum (tpp) time. The former is for the completion of the cycle in progress, and the latter is for the device internal circuitry to be precharged for the next active cycle.

Data out is not latched and is valid as long as the  $\overline{CS}$  and  $\overline{G}$  clocks are active; the output will switch to the three-state mode when either the  $\overline{CS}$  or  $\overline{G}$  clock goes inactive. To perform a read cycle, the write  $(\overline{W})$  input must be held at the  $V_{IH}$  level from the time the  $\overline{CS}$  clock makes its active transition ( $t_{RCS}$ ) to the time when it transitions into the inactive ( $t_{RCH}$ ) mode.

#### WRITE CYCLE

A write cycle is similar to a read cycle except that the Write  $\overline{(W)}$  clock must go active  $(V_{|L|}$  level) at or before the  $\overline{CS}$  clock goes active at a minimum twcs time. If the above condition is met, then the cycle in progress is referred to as an early write cycle. In an early write cycle, the write clock and the data in are referenced to the active transition of the  $\overline{CS}$  clock edge. There are two important parameters with respect to the write cycle: the column strobe to write lead time  $(t_{CWL})$  and the row strobe to write lead time  $(t_{RWL})$ . These define the minimum time that  $\overline{RAS}$  and  $\overline{CS}$  clocks need to be active after the write operation has started  $(\overline{W}$  clock at  $V_{|L|}$  level).

It is also possible to perform a late write cycle. For this cycle the write clock is activated after the  $\overline{\text{CS}}$  goes low which is beyond twcs minimum time. Thus the parameters tcwl and trwl must be satisfied before terminating this cycle. The difference between an early write cycle and a late write cycle is that in a late write cycle the write  $\overline{\text{W}}$  clock can occur much later in time with respect to the active transition of the  $\overline{\text{CS}}$  clock. This time could be as long as 10 microseconds—ltrwl+trp+2trl.

In a late write or a ready-modify-write cycle,  $\overline{G}$  must be at the VIH level to bring the output buffers to high impedance prior to data-in being valid.

At the start of an early write cycle, the data out is in a high impedance condition and remains inactive throughout the cycle. The data out remains three-state because the active transition of the write  $(\overline{W})$  clock prevents the  $\overline{CS}$  clock from enabling the data-out buffers. The three-state condition (high impedance) of the data out pin during a write cycle can be effectively utilized in systems that have a common input/out-put bus. The only stipulation is that the system use only early write mode operations for all write cycles to avoid bus contention.

### **READ-MODIFY-WRITE CYCLE**

As the name implies, both a read and a write cycle are accomplished at a selected bit during a single access. The read-modify-write cycle is similar to the late write cycle discussed above.

For the read-modify-write cycle a normal read cycle is initiated with the write  $(\overline{W})$  clock at the  $V_{IH}$  level until the read data occurs at the device access time  $(t_{RAC})$ . At this time the write  $(\overline{W})$  clock is asserted. The data in is setup and held with respect to the active edge of the write clock. The cycle described assumes a zero modify time between read and write.

### STATIC COLUMN MODE CYCLES

Output buffers are always on when the device is in the static column mode and  $\overline{CS}$  clock is not cycled, resulting in fewer transients and simpler operation. The static column mode allows faster access (tAA) to any of the 512 column addresses on a given row, typically at half the standard (tRAC) rate for randomly performed operations. Static column mode operation consists of changing column addresses while holding the  $\overline{RAS}$  and  $\overline{CS}$  clocks active. A new column location can be accessed with each static column cycle (tSC).

Static column mode operation is initiated with a standard read or write cycle. The row address is latched by the  $\overline{RAS}$  clock transition to active, followed by column addresses and  $\overline{CS}$  clock. Performing an address cycle (tsC) while  $\overline{RAS}$  and  $\overline{CS}$  clocks remain active constitutes the first static column cycle. Subsequent static column cycles can be performed as long as the  $\overline{RAS}$  and  $\overline{CS}$  clocks are held active. The first access (data out) occurs at the standard (trAC) rate. All of the read operations in static column mode following the initial operation are measured at the faster rate (tAA), provided all other timing minimums are maintained. Static column cycle time determines how fast successive bits are read.

Any combination of read, write, or read-modify-write operations can be performed in the static column mode. The conditions normal to each operation apply when the device is operated in this mode.

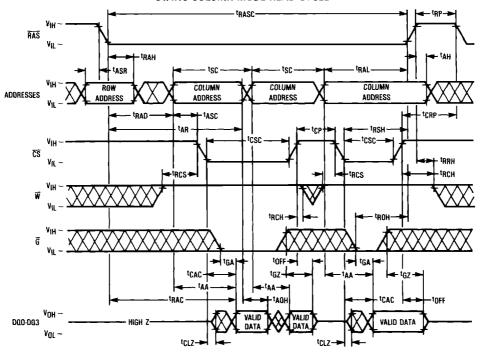

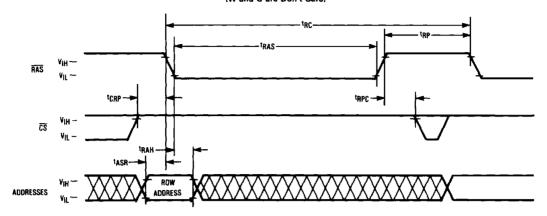

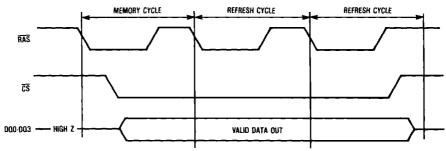

### REFRESH CYCLES

The dynamic RAM design is based on capacitor charge storage for each bit in the array. This charge will tend to degrade with time and temperature. Therefore, to retain the correct information, the bits need to be refreshed at least once every 8 milliseconds. This is accomplished by sequentially cycling through the 512 row address locations every 8 milliseconds, (i.e., at least one row every 15.6 microseconds). A normal read or write operation to the RAM will serve to refresh all the bits associated with the particular rows decoded.

### **RAS-Only Refresh**

In this refresh method, the system must perform a RASonly cycle on 512 row addresses every 8 milliseconds. The row addresses are latched in with the RAS clock, and the associated internal row locations are refreshed. As the heading implies, the  $\overline{\text{CS}}$  clock is not required and must be inactive or at a VIH level.

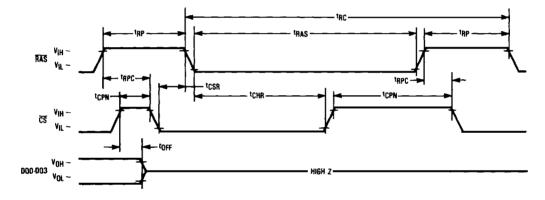

### CS Before RAS Refresh

$\overline{\text{CS}}$  before  $\overline{\text{RAS}}$  refreshing available on the MCM514258 offers an alternate refresh method. If  $\overline{\text{CS}}$  is held on low for the specified period (t<sub>CSR</sub>) before  $\overline{\text{RAS}}$  goes to low, on chip refresh control clock generators and the refresh address counter are enabled, and an internal refresh operation takes place.

After the refresh operation is performed, the refresh address counter is automatically incremented in preparation for the next  $\overline{CS}$  before  $\overline{RAS}$  refresh operation.

### Hidden Refresh

An optional feature of the MCM514258 is that refresh cycle may be performed while maintaining valid data at the output pin. This is referred to as Hidden Refresh. Hidden Refresh is performed by holding  $\overline{CS}$  at  $V_{IL}$  and taking  $\overline{RAS}$  high and after a specified precharge period (tpp), executing a  $\overline{CS}$  before  $\overline{RAS}$  refresh cycle. (see Figure 1 below)

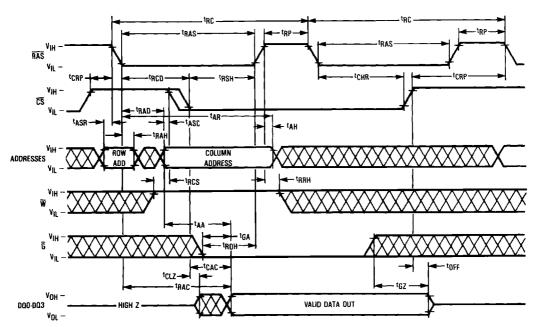

### **CS BEFORE RAS REFRESH COUNTER TEST**

The internal refresh operation of MCM514258 can be tested by  $\overline{\text{CS}}$  before  $\overline{\text{RAS}}$  refresh counter test. This cycle performs read/write operation taking the internal counter address as row address and the input address as column address.

The test is performed after a minimum of 8  $\overline{\text{CS}}$  before  $\overline{\text{RAS}}$  cycles as initialization cycles. The test procedure is as follows.

- 1. Write a "0" into all memory cells.

- Select any column address and read the "0"s written in step 1. Write a "1" into each cell of the selected column by performing CS before RAS Refresh Counter Test Read-Write Cycle (see timing diagram). Repeat 512 times.

- Read the "1"s (use a normal read mode) written in step 2.

- Select the same column address as step 2, read the "1"s and write a "0" into each cell by performing CS before RAS Refresh Counter Test Read-Write Cycle (see timing diagram). Repeat 512 times.

- Read the "0"s (use a normal read mode) written in step

- 6. Repeat steps 1 through 5 using complement data.

Figure 1. Hidden Refresh Cycle

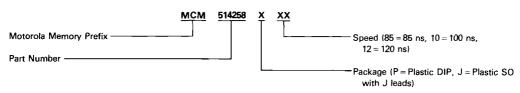

# **ORDERING INFORMATION** (Order by Full Part Number)

Full Part Numbers - MCM514258P85

MCM514258P10

MCM514258P12

MCM514258J85

MCM514258J10

MCM514258J12

**MOTOROLA MEMORY DATA**